JP4632018B2 - 強誘電体膜、強誘電体膜の製造方法、および強誘電体キャパシタ、ならびに強誘電体メモリ - Google Patents

強誘電体膜、強誘電体膜の製造方法、および強誘電体キャパシタ、ならびに強誘電体メモリ Download PDFInfo

- Publication number

- JP4632018B2 JP4632018B2 JP2003355046A JP2003355046A JP4632018B2 JP 4632018 B2 JP4632018 B2 JP 4632018B2 JP 2003355046 A JP2003355046 A JP 2003355046A JP 2003355046 A JP2003355046 A JP 2003355046A JP 4632018 B2 JP4632018 B2 JP 4632018B2

- Authority

- JP

- Japan

- Prior art keywords

- ferroelectric

- film

- electrode

- particles

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/22—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using ferroelectric elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/06—Solid dielectrics

- H01G4/08—Inorganic dielectrics

- H01G4/12—Ceramic dielectrics

- H01G4/1209—Ceramic dielectrics characterised by the ceramic dielectric material

- H01G4/1236—Ceramic dielectrics characterised by the ceramic dielectric material based on zirconium oxides or zirconates

- H01G4/1245—Ceramic dielectrics characterised by the ceramic dielectric material based on zirconium oxides or zirconates containing also titanates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/33—Thin- or thick-film capacitors (thin- or thick-film circuits; capacitors without a potential-jump or surface barrier specially adapted for integrated circuits, details thereof, multistep manufacturing processes therefor)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G7/00—Capacitors in which the capacitance is varied by non-mechanical means; Processes of their manufacture

- H01G7/06—Capacitors in which the capacitance is varied by non-mechanical means; Processes of their manufacture having a dielectric selected for the variation of its permittivity with applied voltage, i.e. ferroelectric capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

- H10D1/682—Capacitors having no potential barriers having dielectrics comprising perovskite structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/69—Inorganic materials

- H10P14/692—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses

- H10P14/6938—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides

- H10P14/69398—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses the material containing at least one metal element, e.g. metal oxides, metal oxynitrides or metal oxycarbides the material having a perovskite structure, e.g. BaTiO3

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/63—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the formation processes

- H10P14/6326—Deposition processes

- H10P14/6342—Liquid deposition, e.g. spin-coating, sol-gel techniques or spray coating

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Computer Hardware Design (AREA)

- Inorganic Chemistry (AREA)

- Semiconductor Memories (AREA)

- Semiconductor Integrated Circuits (AREA)

- Formation Of Insulating Films (AREA)

Description

第1強誘電体原料の粒子を、水熱電着法により電極に電着させて強誘電体初期核層を形成する工程と、

第2強誘電体原料の粒子を帯電させる工程と、

帯電させた前記第2強誘電体原料の粒子を、泳動電着法により前記強誘電体初期核層の上に電着させて強誘電体材料膜を形成する工程と、

前記強誘電体材料膜を熱処理する工程と、を含む。

前記第2強誘電体原料の粒子の表面が多孔質層で覆われたコーティング粒子を形成する工程と、

前記多孔質層にイオンを吸着させる工程と、を含むことができる。

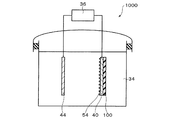

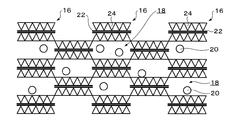

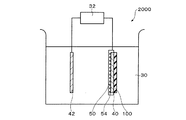

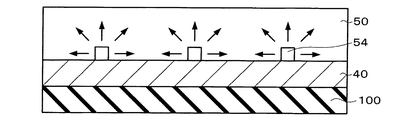

本実施の形態にかかる強誘電体膜の製造方法について説明する。図1〜5は、実施の形態にかかる強誘電体膜の製造方法を模式的に示す図である。強誘電体膜としては、特に限定されず、たとえば、ペロブスカイト構造を有する強誘電体膜(たとえば、PbZrTiO系)や層状ペロブスカイト構造を有する強誘電体膜(たとえば、BiLaTiO系、BiTiO系、SrBiTaO系)などがあげられる。

本実施例では、PbZrTiO系(以下、PZT系という)強誘電体膜を作製した。

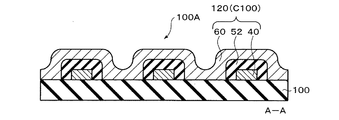

図6は、強誘電体メモリを模式的に示す図であり、図7は、メモリセルアレイの一部を拡大して示す平面図であり、図8は、図7のA−A線に沿った断面図である。平面図において、( )内の数字は最上層より下の層を示す。

Claims (8)

- 第1強誘電体原料の溶液を用いて、水熱電着法により電極に電着させて強誘電体初期核層を形成する工程と、

第2強誘電体原料の粒子を帯電させる工程と、

帯電させた前記第2強誘電体原料の粒子を、泳動電着法により前記強誘電体初期核層の上に電着させて強誘電体材料膜を形成する工程と、

前記強誘電体材料膜を熱処理することにより、結晶化する工程と、を含む、強誘電体膜の製造方法。 - 請求項1において、

前記強誘電体初期核層は島状に形成される、強誘電体膜の製造方法。 - 請求項1または2において、

前記第2強誘電体原料はアモルファス状である、強誘電体膜の製造方法。 - 請求項1〜3のいずれかにおいて、

前記第2強誘電体原料の粒子を帯電させる工程は、

前記第2強誘電体原料の粒子の表面が多孔質層で覆われたコーティング粒子を形成する工程と、

前記多孔質層にイオンを吸着させる工程と、を含む、強誘電体膜の製造方法。 - 請求項4において、

前記多孔質層はシリケートである、強誘電体膜の製造方法。 - 請求項1〜5のいずれかに記載の強誘電体膜の製造方法により形成された、強誘電体膜。

- 請求項6に記載の強誘電体膜を有する、強誘電体キャパシタ。

- 請求項6に記載の強誘電体膜を有する、強誘電体メモリ。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003355046A JP4632018B2 (ja) | 2003-10-15 | 2003-10-15 | 強誘電体膜、強誘電体膜の製造方法、および強誘電体キャパシタ、ならびに強誘電体メモリ |

| US10/960,001 US7056750B2 (en) | 2003-10-15 | 2004-10-08 | Ferroelectric film, method of manufacturing ferroelectric film, ferroelectric capacitor, and ferroelectric memory |

| CNB2004100841060A CN100364065C (zh) | 2003-10-15 | 2004-10-15 | 强电介质膜的制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003355046A JP4632018B2 (ja) | 2003-10-15 | 2003-10-15 | 強誘電体膜、強誘電体膜の製造方法、および強誘電体キャパシタ、ならびに強誘電体メモリ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005123310A JP2005123310A (ja) | 2005-05-12 |

| JP2005123310A5 JP2005123310A5 (ja) | 2006-11-24 |

| JP4632018B2 true JP4632018B2 (ja) | 2011-02-16 |

Family

ID=34612779

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003355046A Expired - Fee Related JP4632018B2 (ja) | 2003-10-15 | 2003-10-15 | 強誘電体膜、強誘電体膜の製造方法、および強誘電体キャパシタ、ならびに強誘電体メモリ |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7056750B2 (ja) |

| JP (1) | JP4632018B2 (ja) |

| CN (1) | CN100364065C (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3937174B2 (ja) | 2004-03-22 | 2007-06-27 | セイコーエプソン株式会社 | 強誘電体膜、強誘電体膜の製造方法、強誘電体キャパシタ、強誘電体メモリおよび圧電素子 |

| JP4983633B2 (ja) * | 2008-02-07 | 2012-07-25 | セイコーエプソン株式会社 | 誘電体膜の成膜方法および誘電体デバイスの製造方法 |

| KR101928438B1 (ko) * | 2012-08-08 | 2019-02-26 | 삼성전자주식회사 | 대전 입자의 진동을 이용한 전자기파 발생기 및 비트 생성기 |

| CN106683882B (zh) * | 2017-01-19 | 2018-07-06 | 广州天极电子科技有限公司 | 一种制备薄膜电容器的方法 |

| US10332687B2 (en) | 2017-10-23 | 2019-06-25 | Blackberry Limited | Tunable coplanar capacitor with vertical tuning and lateral RF path and methods for manufacturing thereof |

| US10497774B2 (en) | 2017-10-23 | 2019-12-03 | Blackberry Limited | Small-gap coplanar tunable capacitors and methods for manufacturing thereof |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5818916A (ja) * | 1981-07-27 | 1983-02-03 | ソニー株式会社 | 焦電体の製造方法 |

| JP3254750B2 (ja) * | 1992-09-28 | 2002-02-12 | セイコーエプソン株式会社 | 強誘電体薄膜素子、インクジェット記録装置および強誘電体薄膜素子の製造方法 |

| JP3206454B2 (ja) * | 1996-10-21 | 2001-09-10 | 東海ゴム工業株式会社 | 複合酸化物薄膜及びその製造方法 |

| US6120846A (en) * | 1997-12-23 | 2000-09-19 | Advanced Technology Materials, Inc. | Method for the selective deposition of bismuth based ferroelectric thin films by chemical vapor deposition |

| JP2000150295A (ja) * | 1998-11-17 | 2000-05-30 | Hokuriku Electric Ind Co Ltd | コンデンサ及びその製造方法 |

| JP2000328223A (ja) * | 1999-05-25 | 2000-11-28 | Agency Of Ind Science & Technol | 積層構造体及びその原料粉、及び、圧電アクチュエータ |

| JP4200639B2 (ja) * | 2000-06-13 | 2008-12-24 | 宇部興産株式会社 | Pzt系結晶膜素子の実装方法 |

| EP1195603B1 (en) * | 2000-10-04 | 2006-06-07 | Seiko Epson Corporation | Electrophoretic device and method of manufacturing it |

| EP1213745A1 (en) * | 2000-12-05 | 2002-06-12 | Sony International (Europe) GmbH | Method of producing a ferroelectric memory and memory device |

| KR20030025671A (ko) * | 2001-09-22 | 2003-03-29 | 주식회사 하이닉스반도체 | 커패시터의 제조방법 |

| JP2003218102A (ja) * | 2002-01-23 | 2003-07-31 | Komatsu Ltd | 誘電体膜の処理装置及び誘電体膜の処理方法 |

-

2003

- 2003-10-15 JP JP2003355046A patent/JP4632018B2/ja not_active Expired - Fee Related

-

2004

- 2004-10-08 US US10/960,001 patent/US7056750B2/en not_active Expired - Lifetime

- 2004-10-15 CN CNB2004100841060A patent/CN100364065C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005123310A (ja) | 2005-05-12 |

| CN100364065C (zh) | 2008-01-23 |

| CN1607650A (zh) | 2005-04-20 |

| US7056750B2 (en) | 2006-06-06 |

| US20050117439A1 (en) | 2005-06-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3258899B2 (ja) | 強誘電体薄膜素子、それを用いた半導体装置、及び強誘電体薄膜素子の製造方法 | |

| US10192972B2 (en) | Semiconductor ferroelectric storage transistor and method for manufacturing same | |

| JPH07502150A (ja) | 集積回路メモリー | |

| JP2001511600A (ja) | 層状超格子材料を製造し、かつ酸素に曝さずに層状超格子材料を含む電子装置を作製するための工程 | |

| JP2008028228A (ja) | 可変抵抗素子および抵抗変化型メモリ装置 | |

| JP4632018B2 (ja) | 強誘電体膜、強誘電体膜の製造方法、および強誘電体キャパシタ、ならびに強誘電体メモリ | |

| KR100737636B1 (ko) | 금속 박막 및 그 형성 방법, 유전체 캐패시터 및 그 제조방법과 반도체 장치 | |

| JPH1012832A (ja) | 強誘電体キャパシタの作製方法及び強誘電体メモリ装置の製造方法 | |

| JP4811551B2 (ja) | 強誘電体膜の製造方法および強誘電体キャパシタの製造方法 | |

| CN1319256A (zh) | 减少四方性的铁电薄膜 | |

| JP4596117B2 (ja) | 強誘電体膜の製造方法 | |

| JPH02154389A (ja) | 強誘電体メモリ | |

| JP2007318018A (ja) | 強誘電体メモリセル及び強誘電体メモリセルの製造方法 | |

| KR20010109957A (ko) | 엘비티 용액, 엘비티 용액의 제조방법 및 이를 이용한엘비티 박막과 전자 소자의 제조방법 | |

| JP3937174B2 (ja) | 強誘電体膜、強誘電体膜の製造方法、強誘電体キャパシタ、強誘電体メモリおよび圧電素子 | |

| JP3924928B2 (ja) | 強誘電体材料及び強誘電体メモリ | |

| JP2004319995A (ja) | 強誘電体膜およびその製造方法ならびに半導体装置 | |

| JPH10270646A (ja) | 強誘電体薄膜素子の製造方法及び半導体装置 | |

| JP3764650B2 (ja) | 強誘電体キャパシタとその製造方法およびその強誘電体キャパシタを備えた半導体装置 | |

| JP4349293B2 (ja) | 強誘電体薄膜の製造方法、圧電素子、強誘電体メモリ | |

| JP4655019B2 (ja) | 可変抵抗素子 | |

| JPH08249876A (ja) | 強誘電体デバイス | |

| JPH0778944A (ja) | 不揮発性メモリ | |

| TW200409369A (en) | A fabrication method for a ferroelectric capacitor applied in a low driving voltage | |

| JP2006120513A (ja) | 強誘電体膜の形成方法および強誘電体膜 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060112 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061005 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061005 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100723 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100728 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100922 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101020 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101102 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131126 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313532 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |