JP4615631B2 - 面内に熱膨張率勾配を設計する方法 - Google Patents

面内に熱膨張率勾配を設計する方法 Download PDFInfo

- Publication number

- JP4615631B2 JP4615631B2 JP52141598A JP52141598A JP4615631B2 JP 4615631 B2 JP4615631 B2 JP 4615631B2 JP 52141598 A JP52141598 A JP 52141598A JP 52141598 A JP52141598 A JP 52141598A JP 4615631 B2 JP4615631 B2 JP 4615631B2

- Authority

- JP

- Japan

- Prior art keywords

- chip

- thermal expansion

- coefficient

- package

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000013461 design Methods 0.000 title description 2

- 239000000463 material Substances 0.000 claims abstract description 88

- 238000000034 method Methods 0.000 claims description 25

- 238000009826 distribution Methods 0.000 claims description 8

- 238000000059 patterning Methods 0.000 claims description 2

- 239000000758 substrate Substances 0.000 abstract description 119

- 239000003990 capacitor Substances 0.000 abstract description 4

- 239000010410 layer Substances 0.000 description 180

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 108

- 239000000853 adhesive Substances 0.000 description 82

- 230000001070 adhesive effect Effects 0.000 description 82

- 238000005452 bending Methods 0.000 description 65

- 239000000203 mixture Substances 0.000 description 56

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 53

- 239000010949 copper Substances 0.000 description 50

- 229910052802 copper Inorganic materials 0.000 description 46

- 239000011159 matrix material Substances 0.000 description 35

- 239000002245 particle Substances 0.000 description 35

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 33

- 229910052782 aluminium Inorganic materials 0.000 description 31

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 31

- 239000000945 filler Substances 0.000 description 30

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 28

- 229910010271 silicon carbide Inorganic materials 0.000 description 27

- 229920000295 expanded polytetrafluoroethylene Polymers 0.000 description 24

- 239000011148 porous material Substances 0.000 description 24

- 239000000243 solution Substances 0.000 description 24

- 229910000679 solder Inorganic materials 0.000 description 22

- 230000035882 stress Effects 0.000 description 21

- 239000006185 dispersion Substances 0.000 description 20

- 239000004020 conductor Substances 0.000 description 18

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 18

- 239000004810 polytetrafluoroethylene Substances 0.000 description 18

- 229910052751 metal Inorganic materials 0.000 description 17

- 239000002184 metal Substances 0.000 description 17

- 239000012792 core layer Substances 0.000 description 16

- 239000007787 solid Substances 0.000 description 16

- -1 2,4,6-tribromophenyl Chemical group 0.000 description 14

- IISBACLAFKSPIT-UHFFFAOYSA-N bisphenol A Chemical compound C=1C=C(O)C=CC=1C(C)(C)C1=CC=C(O)C=C1 IISBACLAFKSPIT-UHFFFAOYSA-N 0.000 description 14

- 229920005989 resin Polymers 0.000 description 14

- 239000011347 resin Substances 0.000 description 14

- 230000000694 effects Effects 0.000 description 13

- 238000004519 manufacturing process Methods 0.000 description 12

- 239000000377 silicon dioxide Substances 0.000 description 12

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 10

- 239000002131 composite material Substances 0.000 description 10

- 238000005470 impregnation Methods 0.000 description 10

- 239000011521 glass Chemical class 0.000 description 9

- 239000011800 void material Substances 0.000 description 9

- 239000011572 manganese Substances 0.000 description 8

- 238000002156 mixing Methods 0.000 description 8

- 239000002966 varnish Substances 0.000 description 8

- 229920002844 BT-Epoxy Polymers 0.000 description 7

- 229910010413 TiO 2 Inorganic materials 0.000 description 7

- 239000011889 copper foil Substances 0.000 description 7

- 239000003989 dielectric material Substances 0.000 description 7

- 230000001965 increasing effect Effects 0.000 description 7

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- 229910004298 SiO 2 Inorganic materials 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 6

- 230000015556 catabolic process Effects 0.000 description 6

- 239000003054 catalyst Substances 0.000 description 6

- 238000006731 degradation reaction Methods 0.000 description 6

- 238000011049 filling Methods 0.000 description 6

- 230000002093 peripheral effect Effects 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 5

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- BGYHLZZASRKEJE-UHFFFAOYSA-N [3-[3-(3,5-ditert-butyl-4-hydroxyphenyl)propanoyloxy]-2,2-bis[3-(3,5-ditert-butyl-4-hydroxyphenyl)propanoyloxymethyl]propyl] 3-(3,5-ditert-butyl-4-hydroxyphenyl)propanoate Chemical compound CC(C)(C)C1=C(O)C(C(C)(C)C)=CC(CCC(=O)OCC(COC(=O)CCC=2C=C(C(O)=C(C=2)C(C)(C)C)C(C)(C)C)(COC(=O)CCC=2C=C(C(O)=C(C=2)C(C)(C)C)C(C)(C)C)COC(=O)CCC=2C=C(C(O)=C(C=2)C(C)(C)C)C(C)(C)C)=C1 BGYHLZZASRKEJE-UHFFFAOYSA-N 0.000 description 5

- 239000012790 adhesive layer Substances 0.000 description 5

- 239000000919 ceramic Substances 0.000 description 5

- 239000007822 coupling agent Substances 0.000 description 5

- 238000003475 lamination Methods 0.000 description 5

- 239000007788 liquid Substances 0.000 description 5

- 229920000642 polymer Polymers 0.000 description 5

- 239000000047 product Substances 0.000 description 5

- 230000002787 reinforcement Effects 0.000 description 5

- 229910000077 silane Inorganic materials 0.000 description 5

- 239000002904 solvent Substances 0.000 description 5

- 229920001187 thermosetting polymer Polymers 0.000 description 5

- RTZKZFJDLAIYFH-UHFFFAOYSA-N Diethyl ether Chemical compound CCOCC RTZKZFJDLAIYFH-UHFFFAOYSA-N 0.000 description 4

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 4

- 230000002411 adverse Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 239000003795 chemical substances by application Substances 0.000 description 4

- 229920001577 copolymer Polymers 0.000 description 4

- 230000006378 damage Effects 0.000 description 4

- 229920002313 fluoropolymer Polymers 0.000 description 4

- 239000004811 fluoropolymer Substances 0.000 description 4

- 238000009472 formulation Methods 0.000 description 4

- 229910052500 inorganic mineral Inorganic materials 0.000 description 4

- 229910052748 manganese Inorganic materials 0.000 description 4

- 239000011707 mineral Substances 0.000 description 4

- 229920003192 poly(bis maleimide) Polymers 0.000 description 4

- 229910021426 porous silicon Inorganic materials 0.000 description 4

- 239000000523 sample Substances 0.000 description 4

- BPSIOYPQMFLKFR-UHFFFAOYSA-N trimethoxy-[3-(oxiran-2-ylmethoxy)propyl]silane Chemical compound CO[Si](OC)(OC)CCCOCC1CO1 BPSIOYPQMFLKFR-UHFFFAOYSA-N 0.000 description 4

- JYEUMXHLPRZUAT-UHFFFAOYSA-N 1,2,3-triazine Chemical compound C1=CN=NN=C1 JYEUMXHLPRZUAT-UHFFFAOYSA-N 0.000 description 3

- XQUPVDVFXZDTLT-UHFFFAOYSA-N 1-[4-[[4-(2,5-dioxopyrrol-1-yl)phenyl]methyl]phenyl]pyrrole-2,5-dione Chemical compound O=C1C=CC(=O)N1C(C=C1)=CC=C1CC1=CC=C(N2C(C=CC2=O)=O)C=C1 XQUPVDVFXZDTLT-UHFFFAOYSA-N 0.000 description 3

- 239000004593 Epoxy Substances 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 230000001066 destructive effect Effects 0.000 description 3

- 239000003822 epoxy resin Substances 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 239000010408 film Substances 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 230000017525 heat dissipation Effects 0.000 description 3

- PYGSKMBEVAICCR-UHFFFAOYSA-N hexa-1,5-diene Chemical group C=CCCC=C PYGSKMBEVAICCR-UHFFFAOYSA-N 0.000 description 3

- RAXXELZNTBOGNW-UHFFFAOYSA-N imidazole Natural products C1=CNC=N1 RAXXELZNTBOGNW-UHFFFAOYSA-N 0.000 description 3

- 230000001939 inductive effect Effects 0.000 description 3

- 229920000647 polyepoxide Polymers 0.000 description 3

- 230000003014 reinforcing effect Effects 0.000 description 3

- 235000015096 spirit Nutrition 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- 229920001169 thermoplastic Polymers 0.000 description 3

- 239000004416 thermosoftening plastic Substances 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- MYRTYDVEIRVNKP-UHFFFAOYSA-N 1,2-Divinylbenzene Chemical compound C=CC1=CC=CC=C1C=C MYRTYDVEIRVNKP-UHFFFAOYSA-N 0.000 description 2

- RNFJDJUURJAICM-UHFFFAOYSA-N 2,2,4,4,6,6-hexaphenoxy-1,3,5-triaza-2$l^{5},4$l^{5},6$l^{5}-triphosphacyclohexa-1,3,5-triene Chemical compound N=1P(OC=2C=CC=CC=2)(OC=2C=CC=CC=2)=NP(OC=2C=CC=CC=2)(OC=2C=CC=CC=2)=NP=1(OC=1C=CC=CC=1)OC1=CC=CC=C1 RNFJDJUURJAICM-UHFFFAOYSA-N 0.000 description 2

- KXGFMDJXCMQABM-UHFFFAOYSA-N 2-methoxy-6-methylphenol Chemical compound [CH]OC1=CC=CC([CH])=C1O KXGFMDJXCMQABM-UHFFFAOYSA-N 0.000 description 2

- OWYWGLHRNBIFJP-UHFFFAOYSA-N Ipazine Chemical compound CCN(CC)C1=NC(Cl)=NC(NC(C)C)=N1 OWYWGLHRNBIFJP-UHFFFAOYSA-N 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- 238000010521 absorption reaction Methods 0.000 description 2

- 238000013019 agitation Methods 0.000 description 2

- 150000004645 aluminates Chemical class 0.000 description 2

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 125000000484 butyl group Chemical group [H]C([*])([H])C([H])([H])C([H])([H])C([H])([H])[H] 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000002485 combustion reaction Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- VTIXMGZYGRZMAW-UHFFFAOYSA-N ditridecyl hydrogen phosphite Chemical compound CCCCCCCCCCCCCOP(O)OCCCCCCCCCCCCC VTIXMGZYGRZMAW-UHFFFAOYSA-N 0.000 description 2

- 238000005553 drilling Methods 0.000 description 2

- 238000005538 encapsulation Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 229920006332 epoxy adhesive Polymers 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 239000003063 flame retardant Substances 0.000 description 2

- 239000006260 foam Substances 0.000 description 2

- 239000006232 furnace black Substances 0.000 description 2

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 230000010365 information processing Effects 0.000 description 2

- 239000011344 liquid material Substances 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 239000012528 membrane Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 230000035699 permeability Effects 0.000 description 2

- 229920001568 phenolic resin Polymers 0.000 description 2

- 239000005011 phenolic resin Substances 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 239000000843 powder Substances 0.000 description 2

- 239000002243 precursor Substances 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 239000002002 slurry Substances 0.000 description 2

- 239000003381 stabilizer Substances 0.000 description 2

- 230000000087 stabilizing effect Effects 0.000 description 2

- VXUYXOFXAQZZMF-UHFFFAOYSA-N titanium(IV) isopropoxide Chemical compound CC(C)O[Ti](OC(C)C)(OC(C)C)OC(C)C VXUYXOFXAQZZMF-UHFFFAOYSA-N 0.000 description 2

- 238000011144 upstream manufacturing Methods 0.000 description 2

- WGGNJZRNHUJNEM-UHFFFAOYSA-N 2,2,4,4,6,6-hexamethyl-1,3,5,2,4,6-triazatrisilinane Chemical compound C[Si]1(C)N[Si](C)(C)N[Si](C)(C)N1 WGGNJZRNHUJNEM-UHFFFAOYSA-N 0.000 description 1

- FCMUPMSEVHVOSE-UHFFFAOYSA-N 2,3-bis(ethenyl)pyridine Chemical compound C=CC1=CC=CN=C1C=C FCMUPMSEVHVOSE-UHFFFAOYSA-N 0.000 description 1

- XMNIXWIUMCBBBL-UHFFFAOYSA-N 2-(2-phenylpropan-2-ylperoxy)propan-2-ylbenzene Chemical compound C=1C=CC=CC=1C(C)(C)OOC(C)(C)C1=CC=CC=C1 XMNIXWIUMCBBBL-UHFFFAOYSA-N 0.000 description 1

- KTXWGMUMDPYXNN-UHFFFAOYSA-N 2-ethylhexan-1-olate;titanium(4+) Chemical compound [Ti+4].CCCCC(CC)C[O-].CCCCC(CC)C[O-].CCCCC(CC)C[O-].CCCCC(CC)C[O-] KTXWGMUMDPYXNN-UHFFFAOYSA-N 0.000 description 1

- FHRAKXJVEOBCBQ-UHFFFAOYSA-L 2-ethylhexanoate;manganese(2+) Chemical compound [Mn+2].CCCCC(CC)C([O-])=O.CCCCC(CC)C([O-])=O FHRAKXJVEOBCBQ-UHFFFAOYSA-L 0.000 description 1

- LXBGSDVWAMZHDD-UHFFFAOYSA-N 2-methyl-1h-imidazole Chemical compound CC1=NC=CN1 LXBGSDVWAMZHDD-UHFFFAOYSA-N 0.000 description 1

- VEORPZCZECFIRK-UHFFFAOYSA-N 3,3',5,5'-tetrabromobisphenol A Chemical compound C=1C(Br)=C(O)C(Br)=CC=1C(C)(C)C1=CC(Br)=C(O)C(Br)=C1 VEORPZCZECFIRK-UHFFFAOYSA-N 0.000 description 1

- BVKZGUZCCUSVTD-UHFFFAOYSA-L Carbonate Chemical compound [O-]C([O-])=O BVKZGUZCCUSVTD-UHFFFAOYSA-L 0.000 description 1

- 229910001374 Invar Inorganic materials 0.000 description 1

- 229920000877 Melamine resin Polymers 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- YKFRUJSEPGHZFJ-UHFFFAOYSA-N N-trimethylsilylimidazole Chemical group C[Si](C)(C)N1C=CN=C1 YKFRUJSEPGHZFJ-UHFFFAOYSA-N 0.000 description 1

- 239000005062 Polybutadiene Substances 0.000 description 1

- 239000004698 Polyethylene Substances 0.000 description 1

- 239000004743 Polypropylene Substances 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 239000004840 adhesive resin Substances 0.000 description 1

- 229920006223 adhesive resin Polymers 0.000 description 1

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 1

- 238000000149 argon plasma sintering Methods 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- 230000002902 bimodal effect Effects 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- SIOVKLKJSOKLIF-UHFFFAOYSA-N bis(trimethylsilyl)acetamide Chemical compound C[Si](C)(C)OC(C)=N[Si](C)(C)C SIOVKLKJSOKLIF-UHFFFAOYSA-N 0.000 description 1

- 239000006229 carbon black Substances 0.000 description 1

- 229920002301 cellulose acetate Polymers 0.000 description 1

- 229910010293 ceramic material Inorganic materials 0.000 description 1

- 239000013522 chelant Substances 0.000 description 1

- 230000002301 combined effect Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 238000007906 compression Methods 0.000 description 1

- 230000006835 compression Effects 0.000 description 1

- 239000011231 conductive filler Substances 0.000 description 1

- 230000008602 contraction Effects 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- XLJMAIOERFSOGZ-UHFFFAOYSA-M cyanate Chemical compound [O-]C#N XLJMAIOERFSOGZ-UHFFFAOYSA-M 0.000 description 1

- 230000000254 damaging effect Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000000593 degrading effect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- VELFFNYFZHVFNA-UHFFFAOYSA-N dioctyl phosphono phosphate Chemical compound CCCCCCCCOP(=O)(OP(O)(O)=O)OCCCCCCCC VELFFNYFZHVFNA-UHFFFAOYSA-N 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 230000008030 elimination Effects 0.000 description 1

- 238000003379 elimination reaction Methods 0.000 description 1

- 125000002534 ethynyl group Chemical group [H]C#C* 0.000 description 1

- 238000001125 extrusion Methods 0.000 description 1

- 239000012467 final product Substances 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- LNEPOXFFQSENCJ-UHFFFAOYSA-N haloperidol Chemical class C1CC(O)(C=2C=CC(Cl)=CC=2)CCN1CCCC(=O)C1=CC=C(F)C=C1 LNEPOXFFQSENCJ-UHFFFAOYSA-N 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 230000002209 hydrophobic effect Effects 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 238000003780 insertion Methods 0.000 description 1

- 230000037431 insertion Effects 0.000 description 1

- UPRXAOPZPSAYHF-UHFFFAOYSA-N lithium;cyclohexyl(propan-2-yl)azanide Chemical compound CC(C)N([Li])C1CCCCC1 UPRXAOPZPSAYHF-UHFFFAOYSA-N 0.000 description 1

- 238000003754 machining Methods 0.000 description 1

- JDSHMPZPIAZGSV-UHFFFAOYSA-N melamine Chemical compound NC1=NC(N)=NC(N)=N1 JDSHMPZPIAZGSV-UHFFFAOYSA-N 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- 125000001971 neopentyl group Chemical group [H]C([*])([H])C(C([H])([H])[H])(C([H])([H])[H])C([H])([H])[H] 0.000 description 1

- 238000009828 non-uniform distribution Methods 0.000 description 1

- JFNLZVQOOSMTJK-KNVOCYPGSA-N norbornene Chemical compound C1[C@@H]2CC[C@H]1C=C2 JFNLZVQOOSMTJK-KNVOCYPGSA-N 0.000 description 1

- 229920003986 novolac Polymers 0.000 description 1

- JRZJOMJEPLMPRA-UHFFFAOYSA-N olefin Natural products CCCCCCCC=C JRZJOMJEPLMPRA-UHFFFAOYSA-N 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 239000005416 organic matter Substances 0.000 description 1

- 150000001451 organic peroxides Chemical class 0.000 description 1

- 125000001181 organosilyl group Chemical group [SiH3]* 0.000 description 1

- 238000013021 overheating Methods 0.000 description 1

- 239000005022 packaging material Substances 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 238000012536 packaging technology Methods 0.000 description 1

- 238000012856 packing Methods 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 229920000636 poly(norbornene) polymer Polymers 0.000 description 1

- 229920000058 polyacrylate Polymers 0.000 description 1

- 229920002857 polybutadiene Polymers 0.000 description 1

- 239000004644 polycyanurate Substances 0.000 description 1

- 229920000573 polyethylene Polymers 0.000 description 1

- 229920001228 polyisocyanate Polymers 0.000 description 1

- 239000005056 polyisocyanate Substances 0.000 description 1

- 229920000098 polyolefin Polymers 0.000 description 1

- 229920001955 polyphenylene ether Polymers 0.000 description 1

- 229920001155 polypropylene Polymers 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 238000004663 powder metallurgy Methods 0.000 description 1

- 239000012254 powdered material Substances 0.000 description 1

- 239000012255 powdered metal Substances 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 238000003908 quality control method Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000010992 reflux Methods 0.000 description 1

- 230000000452 restraining effect Effects 0.000 description 1

- 150000003839 salts Chemical group 0.000 description 1

- 238000001878 scanning electron micrograph Methods 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000010008 shearing Methods 0.000 description 1

- FZHAPNGMFPVSLP-UHFFFAOYSA-N silanamine Chemical class [SiH3]N FZHAPNGMFPVSLP-UHFFFAOYSA-N 0.000 description 1

- 150000004756 silanes Chemical class 0.000 description 1

- 150000004819 silanols Chemical class 0.000 description 1

- 238000004513 sizing Methods 0.000 description 1

- 239000002893 slag Substances 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 239000012453 solvate Substances 0.000 description 1

- 238000000527 sonication Methods 0.000 description 1

- 238000003756 stirring Methods 0.000 description 1

- 230000008646 thermal stress Effects 0.000 description 1

- 239000012815 thermoplastic material Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- ZNOCGWVLWPVKAO-UHFFFAOYSA-N trimethoxy(phenyl)silane Chemical compound CO[Si](OC)(OC)C1=CC=CC=C1 ZNOCGWVLWPVKAO-UHFFFAOYSA-N 0.000 description 1

- YUYCVXFAYWRXLS-UHFFFAOYSA-N trimethoxysilane Chemical compound CO[SiH](OC)OC YUYCVXFAYWRXLS-UHFFFAOYSA-N 0.000 description 1

- AATYKEFFPLPLST-UHFFFAOYSA-N trimethylsilylurea Chemical compound C[Si](C)(C)NC(N)=O AATYKEFFPLPLST-UHFFFAOYSA-N 0.000 description 1

- 238000009827 uniform distribution Methods 0.000 description 1

- 229920002554 vinyl polymer Polymers 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/4857—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49822—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5383—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5386—Geometry or layout of the interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01004—Beryllium [Be]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01019—Potassium [K]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0102—Calcium [Ca]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01025—Manganese [Mn]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01057—Lanthanum [La]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01087—Francium [Fr]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/06—Polymers

- H01L2924/078—Adhesive characteristics other than chemical

- H01L2924/0781—Adhesive characteristics other than chemical being an ohmic electrical conductor

- H01L2924/07811—Extrinsic, i.e. with electrical conductive fillers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/1615—Shape

- H01L2924/16195—Flat cap [not enclosing an internal cavity]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24802—Discontinuous or differential coating, impregnation or bond [e.g., artwork, printing, retouched photograph, etc.]

- Y10T428/24917—Discontinuous or differential coating, impregnation or bond [e.g., artwork, printing, retouched photograph, etc.] including metal layer

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24942—Structurally defined web or sheet [e.g., overall dimension, etc.] including components having same physical characteristic in differing degree

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Geometry (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Wire Bonding (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Description

本発明は、広くは、マイクロエレクトロニクスの製造と組み立ての分野に関するものであり、より詳しくは、種々システムの構成部分及び/又は組み立ての際の接着剤硬化に由来する熱膨張率(CTE)の不一致によって生じる、集積回路チップ/パッケージシステムにおいて、曲げモーメントを低下させる又は解消し応力を低下させる方法と装置に関する。より具体的には、本発明は、種々の構成部分の熱膨張率をマッチさせる、構成部分の間で異なる熱膨張率のコントロールを提供する、及び/又は曲げモーメントをゼロにして熱膨張率による曲げモーメントを相殺することによって、半導体チップ/パッケージのシステムを安定化・形成するアセンブリ技術に関する。

発明の背景

多数の電子回路部品が、例えばシリコンやゲルマニウムの1〜4cm2のチップの表面上に散りばめられる電子マイクロ回路又は「チップ」は、現在の工業技術における不可欠で必須なパーツになっている。この技術の工業的重要性は非常に大きいため、チップの性能、信頼性、使用寿命を改良するため、絶えず努力がなされている。

しかしながら、これらのチップのデリケートな構造と非常に小さいサイズは、格別に新しくて難しい技術的問題を生じさせた。熱膨張率(CTE)、放熱、接着剤の収縮、曲げ弾性率などの巨視的スケールでは周知の物理的現象によって一般に生じるこれらの問題は、電子チップの微視的領域で顕在化する全く新しくて多くは不都合な一連の作用をもたらしている。

詳しくは、一般的なチップが、支持基材に装着されてそれに電気接続される。次いで基材がプリント回路ボードに固定される。即ち、基材は、情報処理のためにプリント回路ボード上の導体から得られた電気信号をチップに伝達する中間的機能をするだけでなく、チップから出力信号を受け、さらなる情報処理のため、これらの出力信号を別なプリント回路ボードの導体に伝える。

チップは、励起されるとかなりの熱量を発生し、これは1〜4cmの面積を有するチップから50〜100ワットのオーダーの放熱になることがあり、チップの熱膨張とその基材の熱膨張はいくつかの極めて破壊的な作用をもたらすことがある。このような狭い領域で発生した熱を、過熱によるチップ損傷を避ける仕方でコントロールすることは、未だ十分に満足できる方法では解決されていない問題である。

例えば、熱に関係するチップ損傷の1つの原因は、拡散その他でチップに付与される回路部品の電気特性が、チップの寸法の変化とともに非常に顕著に変化し得ることにある。例えば、チップの熱膨張によって生じるこれらのチップ寸法の変化は、膨張したチップ製品を役立たないものにし、場合により、出力信号を狂わせることがある。また、これらの不都合な熱膨張作用は、基材にその周囲が固定されたチップの中央部を湾曲、屈曲、又は弓曲させ得る。この湾曲は、多くは、チップとその下地基材の間の電気接続の少なくとも一部を離れさせ、互いに分断させる。主としてこれらの理由により、チップの性能が駄目になる。

言うまでもなく、熱膨張が引き起こす電気接続の故障による回路連結の破損は、完全には回避できないにせよ少なくとも最小限にされる必要のある熱膨張の作用によるものである。

熱的に引き起こされる湾曲に原因するもう1つの破損作用に、クラックと破壊がある。この条件下において、チップは大きな範囲でクラックや破壊を起こすが、これは、チップが曲げられるとチップの最も外側の表面に引張応力が生じるためである。これらの応力は、チップの破壊強度を上回ると、チップにクラックや破壊を生じさせる。熱的作用は、チップに限られず、基材やその他のチップパッケージ用材料にも現われる。

基材は、基材材料の2〜15枚又はそれ以上の層を積み重ねることによって形成される構造体であり、これらの層の少なくとも2つは異なる組成である。これらの層の各々が形成される材料は、極めて異なる傾向にあり、いくつかの層は例えば金属であり(例えば、銅、ニッケル、又は金)、その他の例示の層はエポキシ樹脂やガラス配合物である。これらの個々の層の熱膨張率は、それぞれかなり相異し、コントロールできない湾曲や熱による基材表面の変形を招き、これは、回路使用の際にチップに及ぼされるだけでなく、基材の製造に必要な高温によっても基材に及ぼされる。

好ましくは、チップを支持してチップとプリント回路ボードの間に電気接触を形成する基材表面は、全ての使用条件下で「平滑」であるべきである。事実として、基材そのものが十分に「平滑」でなければ、チップと基材の間に電気接触を形成できないことが示されている。

また、熱膨張が関係する作用とは別に、所望の程度の基材平滑性が損なわれる他の原因もある。これらの熱膨張が関与しない平滑性低下の1つは、層を形成するプロセスにおいて、個々の層の厚さを完全にはコントロールできないことで現われる。これらの個々の層の厚さの変動は、別な製造ロット間だけでなく、同じ層の異なる部分又は領域でも、標準的又は好ましい厚さから逸脱する。個々の層の厚さのこれらの変動は、基材内の熱膨張率(CTE)の局所的変化に帰因し、基材のひずみに結びつくこともある。

これらの微視的条件下での平滑性の評価基準を確立し、それによって、工業的に受け入れられる平滑性の変動と受け入れられないものとを区別するため、いくつかの基準が確立されている。第1に、チップの装着とパッケージのための「平滑性」は、単位面積あたりの最大高さと下側偏差の比として定義され、工業的に実施されており、平面からの最大許容偏差は2.5μmである。さらに、全体のチップパッケージやチップパッケージ構成部分についての平滑性のひずみ又は低下のその他の工業的に受け入れられた基準があり、全体のチップパッケージについて6〜8ミルを超えるひずみは工業的に受け入れられない。これは達成が難しい目標であるが、所方の基材層の厚さの変動が±15%にも及ぶことがあるにもかかわらずチップパッケージ工業が満たさなければならない目標である。

これらの曲がりや屈曲の問題を解決する又は少なくとも対処する検討において、チップパッケージ工業は2つの全く相対する方向に動いてきた。厚さが約40ミル以上のセラミック基材が使用されている。これらの厚さの基材は、支持された基材に対して非常に大きいため、チップの曲がりは生じない。

もう1つの相対する工業的アプローチは、本質的に非常に薄い、例えば厚さ約2ミル以下のフィルムである基材を使用することであった。これらの薄い基材フィルムは変形し、圧縮応力、表面不規則性などの殆ど全てを吸収し、「ブリスター」又は「シュリンクラップ」パッケージがパッケージされる物の形状に自ら一致すると同様な仕方で、チップを本質的に平滑で変形されていない状態のままにする。

ちなみに、上記のもの以外のチップ曲がりの原因もあることに留意すべきである。1つの例示としての熱に関与せずに製造に関係する曲がりの原因は、チップを基材に固定してチップとその表面の間の電気接続を安定化させるための、チップとその対応基材の相対する表面の間に施される接着剤アンダフィルによるものである。チップの直ぐ下のこの基材領域(ダイ区域と称されることが多い)の電気接続は、一般に、ハンダ付けされた接続である。この点において、これらの接続のハンダは、ダイ区域内の電気接続を弱くし破壊する経時的な劣化を受ける。ハンダ接続におけるこの劣化には多くの原因があり、これらの原因の1つは、チップとその基材の間の相対的運動によって引き起こされる疲労である。ハンダ付け接続の間のダイ区域の中の空間に接着剤(通常はエポキシ樹脂接着剤)を充填することは、チップを基材に結合させ、ハンダ付け接続の劣化の原因としての相対的運動を低下させるが、接着剤はある不都合な副作用をもたらす。例えば、硬化又は剛直化するとき、接着剤は不都合な構造的応力のさらなる箇所になる。硬化した接着剤は収縮し、ハンダ付け接続を圧縮下に置き、これらの圧縮力により、チップや基材にさらに別の曲がり運動を与える。

曲がりや曲げモーメントに対処するためのこれらの技術は、いろいろな原因の中で大なり小なりの成功を収めていることは明らかであり、それらは厚さ約40ミル以上の大きい基材又は厚さ約2ミル以下の薄いフィルムの基材であり、2ミルを上回る厚さで40ミルよりも薄い中間範囲の基材についての同様な問題を解決する示唆はしていない。

この中間範囲の基材は、チップに適度の平滑性を維持させるには薄過ぎる。また、これらの中間範囲の基材は、いろいろな原因による曲げモーメントの全てを吸収し、割合に厚いチップがその組み合わせを構造的に支配して全ての重要なチップを平滑に維持するには厚過ぎる。事実として、この中間範囲の基材は、曲げ応力をそれらのそれぞれのチップに伝達し、それによって、上記に概説したチップ曲げ応力の困難性を増大するには格好の基材である。しかしながら、これらの構造的制約にもかかわらず、この中間的な厚さの範囲のチップ基材に対して大きな商業的要論がある。

チップパッケージを完成させるため、チップは通常基材の中央に取り付けられる。チップと基材の組み合わせを強化するためのリングが、多くの場合、接着剤によって基材に接着又は固定され、接着剤は基材の縁に施され、チップを取り付ける前又は後でリング中央の中でチップを本質的に包囲する。リングは、チップの周りにフレームを形成し、リングの内側周辺はチップの対応エッジから間隔を設けられ、リングの高さはチップのそれよりも若干高い。この仕方において、基材に結合されるリング表面の反対のリング表面に接着されるリッド又はカバーは、チップの対応するダイ区域の上に間隔を設けられて位置し、チップの上側表面とリッドの相対するダイ区域表面の間にギャップを残し、これは後に熱伝導性材料で充填される。

熱膨張率、接着剤の収縮、平滑性の不規則さ、及び上記に考察したひずみ、反り、変形のその他の原因は、リングとリッドに本質的に同様な力を与える。従って、市場性のあるチップパッケージを製造するためには、問題とされる工業的実情や標準で規定される許容できる平滑度の中にチップとチップ部品の平滑度を維持するように、とりわけ2ミル〜40ミル、中でも5ミル〜25ミルの厚さの基材を有するチップについてのこれらの不都合な応力や曲げ作用が回避され、又は少なくともコントロールされ抑えられるべきである。

発明の要旨

本発明は、熱的に安定で、高い構造的完全性を有し、種々のパッケージ構成部分の間に生じる熱応力を相殺するアセンブリ技術とその得られた生産品に関する。このことは、一部においては、パッケージ基材上に取り付けられる強化リングの熱膨張率が基材と随意のリッドの熱膨張率にマッチするようにパッケージを設計することによって達成される。また、強化リングを接着するために使用される特定の接着剤が、その熱膨張率が基材、リング、リッドのそれにマッチするように選択される。さらに、基材は、その熱膨張率がチップのそれと、また、強化リングのそれとも少なくともある程度マッチするように設計される。

1.接着剤の封入

例えば、チップパッケージの曲がりは、リッドに1以上のスロット又は孔を形成することにより、大きく低下させることができる。この1つ以上のスロットは、チップ、基材、リッドの間のダイ区域、及びチップエッジとリング内壁の間の空間に形成されるチップを囲む空隙と流体との連絡を形成する。接着剤が、孔を通してこの空隙に注入される。この仕方によって、チップは注封又は封入され、同時に接着剤は下部を満たす。チップを全支持構造体に接着することは、チップ構造体をより大きい基材、リング、及びリッドの組み合わせに効果的に一体化させる。即ち、大きい規模で、上記の熱的又は機械的影響の1つ以上の下での曲げから、結合されたチップが保護される。

同様に、リッド中のスロットと独立して又は組み合わせて、基材もしくはリング又はその双方に1つ以上のスロット又は孔が形成され、チップを囲む空隙と連通させることができる。基材又はリングの孔を通して導入された接着剤は、リッドのスロットを通して入れられた接着剤と同じ仕方で、チップの曲がりの問題を軽減させる。ここで、1つ又は2つだけのスロットから空隙に接着剤を流入させるのが好ましいことが分っている。2つより多いスロットから空隙に接着剤を流入させると、特にチップの下の接着剤に泡を生じさせ、最も不都合な結果をもたらすことがある。

2.選択的に積み重ねられた基材の層

次に基材に関して、先に、基材は2〜15枚の層又はそれ以上の層を積み重ねることによって形成されることができ、これらの層の少なくとも2つは異なる材料であると述べた。この点において、曲がりに影響する主な層は、基材の外側表面である。ここで、本発明の顕著な特徴により、例えば銅の層のような厚さと平滑度が最も慎重にコントロールされ得る材料を外側層に使用し、さらに、次第に大きい製造公差を示す層を中心の方に漸次内側に付加することによって、曲がり作用が顕著に低下され、例えば、ある例における曲がりは、本発明のこの特徴の実施により約400μmから150μm未満まで低下した。

この仕方で基材層を積み重ねることにより、基材の全体的な曲がりは回避され、少なくともチップ使用において通常現われる温度範囲で、不都合な曲がり現象は概ね解消される。

さらに、本発明のこの原理は、基材に用途を有するだけでなく、リングやリッドの構造にも適切に適用されることができる。

3.単位面積あたりの構成のコントロール

個々の層の厚さのコントロールは、所望の厚さから±15%にも及んで変動し得ることを前述した。これらの厚さの変動は、基材の、又は上記のような他のチップパッケージの構成部分のさらなる曲がりを生じさせる。また、種々の層が、層の異なる箇所で異なる組成を有することがある。このことは、別個な伝導性(conductive)経路を形成するための、金属層のパターン化の結果として生じることがある。ここで、本発明をさらに特徴づけるプロセスによって製造されたチップは、曲げ応力の価値ある低下を提供することができる。本発明のこの特徴にしたがうと、チップパッケージの構成部分(基材は例示のもの)が、小さな単位の領域に分割される。構成部分の外側表面の方に次第に近づく各層の単位面積構成から分析され、各単位面積下の基材の対称面から同じ距離の層の部分の全てが、同じ材料の実質的に同じ量を含むかどうかを測定する。それぞれの層が調節・制御され、単位面積内の各相対する層に存在する同じ材料の量がほぼ同じ量のチップパッケージ構造部分を作成し、それにより、全体的に低い曲がりを有する構造を提供する。

4.ダイ区域の熱膨張率コントロール

チップパッケージ技術のマイクロコスムにおける熱膨張率メカニズムの慎重な分析と、本発明のもう1つの特徴によると、予想される作動温度の範囲でチップ平滑性を維持する見地から、ダイの直ぐ下の基材の熱膨張率が非常に重要なことが分った。基材と上部チップのダイ区域の中で熱膨張率の不一致があると、不都合で潜在的な破壊をもたらす曲げ又は電気接触の剪断応力が、チップとチップ−基材電気接続に加わるであろう。ここで、本発明の明確な特徴が、基材ダイ区域の熱膨張率をチップのそれに近づける一方で、チップパッケージの平均熱膨張率、より具体的には基材の平均熱膨張率を、パッケージされたマイクロチップが取り付けられる回路ボードの熱膨張率にマッチさせることにより、この問題を解決する。

本発明のこの特徴は、基材とチップの間の熱膨張率の相対的相違を低下させ、それによって、チップの曲げ応力、ハンダ接続の剪断、疲労を生じさせる熱膨張の差異を回避する。即ち、チップと基材のダイ区域は、ほぼ同じ熱膨張率を享有し、温度が変化しても一緒に膨張・収縮する。一緒に膨張・収縮することにより、従来、チップに曲げや反りを生じさせ、ハンダ接続に剪断力を与えていたチップと基材ダイ区域の間の相対的動きは解消される。さらに、基材と付帯チップパッケージの平均熱膨張率をプリント回路ボードの熱膨張率にマッチさせることにより、チップパッケージとプリント回路ボードの間の相対的運動、付随の曲げ応力、剪断力もまた抑えられる。

5.選択的な熱膨張率の調節

熱に帰因する曲げ応力にさらに対処するため、本発明は、材料の1つの層の熱膨張率を別な層のほぼそれに選択的に調節する新規な技術をさらに提供する。この特徴ある構造は、マトリックス層に形成された任意の予め決められた所望の形状の2つ以上の溝、窪み、又は孔を有する。これらの孔又は箇所は、マトリックス層の熱膨張率とかなり異なる熱膨張率を有する別な材料で満たされる。加熱すると、孔の中の材料は、その箇所が設けられた周囲マトリックスと異なる速度と範囲で膨張する。この異なる膨張は、少なくともそれぞれの箇所の付近でマトリックス層に応力を生じさせるが、マトリックスの周囲部分を押している膨張した孔のフィラー材料の合計の作用は、マトリックス層の実際の熱膨張率を高める。マトリックスに形成されるその箇所の数と配置を適切に選択し、ある制限の中で1種以上のフィラー材料を選ぶことによって、マトリックス層又は層の一部が、所定の熱膨張率を呈するように調節されることができる。

また、孔の表面に接着する適当な材料でマトリックスの孔を満たすことによって、本発明の実施によりこの逆の結果を得ることもできる。即ち、マトリックスの孔を満たす材料が縮む(マトリックスに比較して)程度の適当な温度を与えると、その材料によってマトリックスに及ぼされる力は、本発明にしたがって処理されていないマトリックスよりも、大きい程度でマトリックスを引き締める。この結果、このように処理されたマトリックスは、ベースのマトリックス材料の熱膨張率と大きく異なることができる熱膨張率による収縮性を収得する。

チップパッケージに本発明のこの特徴を与えると、基材層は、ダイ区域に選択された数と分布の孔が提供されることができる。周囲マトリックスと異なる熱膨張を有する材料で満たされたこれらの孔は、上に位置するチップの熱膨張率に近づける目的で、ダイ区域のマトリックスの全体的熱膨張率に近い。ここで、マトリックスの周囲の近くとリングの下に、マトリックス孔とフィラー材料の異なる組み合わせを選択し、マトリックス層のこの部分の全体的熱膨張率が、上に位置するリングの熱膨張率に近いことを可能にさせる。孔の数、層の中でのそれらの分布、これらの孔のフィラー材料を適切に選択することにより、本発明の実施によって、マトリックスの熱膨張率を調節することができ、それによって、チップ曲がりと曲げ応力の双方をほぼ無くすることができる。

6.チップパッケージのリッドの熱膨張率の調節

言うまでもないが、チップは、チップを適切に機能させ続けるためには熱が放散される必要がある非常に集中した熱源であり、極端な場合には、全く機能しなくなる。リッドの表面積の大部分にわたってチップで発生した熱を放散させる目的で、チップからリッドのダイ区域に熱を伝えるための熱伝導性インターフェイスを、チップと上部リッドの間のダイ区域に適用することができる。本発明に使用するのに適当な典型的なインターフェイスは、米国特許第5545473号(発明者J.G.Ameenら、発明の名称「熱伝導性インターフェイス」、1996年8月13日発行)に記載されている。

リッドのダイ区域にチップが結合されるべきこれらの態様において、チップの熱膨張率とリッドの熱膨張率の差によって生じる応力と曲がり作用が、ここでも重要になる。通常、チップパッケージのリッドは、銅又はアルミニウムで形成される。あるいは、アルミニウムと炭化ケイ素、又は銅と炭化ケイ素その他の低熱膨張率強化材の組み合わせが使用可能であった。本発明のもう1つの大きな特徴によると、例えば、アルミニウムは23PPM/℃の熱膨張率を有することが認識される。このため、リッドの異なる部分でアルミニウムと炭化ケイ素の比を調整することにより、純アルミニウムの23PPM/℃から純炭化ケイ素の3.7PPM/℃までの範囲の所定の熱膨張率が調整可能である。

この知識に基づき、リッドの隣接部分に結合されるチップの熱膨張率にマッチさせる目的で、高い炭化ケイ素と低いアルミニウムの濃度組成がダイ区域に形成されることができる。ここで、リングに結合されるリッドの周辺部分は、異なるアルミニウム/炭化ケイ素の割合である。この場合、リッドの周辺部分におけるアルミニウムと炭化ケイ素の相対的濃度は、リッドの平均熱膨張率が、基材/ダイの組み合わせの平均熱膨張にマッチするように選択される。この技術により、チップとリッドのダイ区域の間、リングとリッドのリングに結合される部分の間の相対的運動、及び熱膨張の関数としての結果的な曲がりは回避され、各チップパッケージの構成部分が本質的に平滑性を維持しながら、ダイ又は接着剤の境界の応力を下げることを可能にする。

アルミニウムと炭化ケイ素の所望の濃度(即ち、2つだけのあり得る材料)は、いくつかの仕方で調節可能である。本発明をさらに特徴づけるこれらの技術の1つは、リングの外側寸法と同じ寸法の多孔質体を用意する。この成形体は、ダイ区域とほぼ同じ寸法を有する多孔質炭化ケイ素の厚みのある中央コアを有する。この成形体の縁における1つ以上の周囲の窪みは、リングの熱膨張率にある程度マッチする炭化ケイ素の濃度を確立する。溶融アルミニウムは、本質的に多孔質炭化ケイ素マトリックスの中に拡散し、アルミニウムと炭化ケイ素の相対的割合は、それぞれの下に位置する構成部分の各熱膨張率にマッチするように、成形体の端から端までで変化する。この仕方において、リッドの周辺の熱膨張率は、所定の値(例えば、リングの熱膨張率)に近い。このように、本発明のこの特徴の実施によって、リッドに非常に様々の熱膨張特性が与えられ、これらの特性は、リッドのダイ区域の熱膨張率をチップの熱膨張率に、また、リッドの周辺の熱膨張率をリングのそれにマッチさせる。

7.熱膨張率の相殺

本発明のさらなる特徴は、基材からチップに及ぼされ得る曲げモーメントを打ち消し又は相殺し、それによって、基材とチップの間の相対的運動を解消し、従って、この相対的運動が生じさせ得るチップのそれに関係する曲げを回避する。本発明のこの特徴のある態様において、活性チップと同じ熱膨張率又は類似の熱膨張率を有する電気的に不活性の構成部分又は受動的な電気部品(例えば、キャパシタ、抵抗体、誘導子)が、電気的活性チップが接続される側と反対の基材の側で、基材の露出したダイ区域表面に接続される。電気的活性チップと、電気的受動又は不活性エレメントは、双方とも本質的に同じ熱膨張率を含有するため、双方のチップの熱膨張はほぼ同じである。基材に対するこれらのチップの相対的運動は、同じであっても基材の反対側であり、それによって、そうしなければ生じるであろう何らかのチップに関係する曲げモーメントを効果的に打ち消す。この態様において、電気的活性チップは、適度に平滑なままである。

本発明のこの特徴のもう1つの態様は、基材のダイ区域に強化材を挿入し、デバイスの作動温度範囲にわたって、基材のその部分が、基材のその部分の上に直接装着されたチップに対して曲がることを防ぐ。このように装着されると、強化材は、一般に、チップのダイ区域における不都合な基材の曲がりを克服する。

このように、本発明の原理にしたがうと、チップのパッケージ部品の間の相対的運動による起こり得る破壊作用を解決する方法と装置が提供される。ここで、本発明の範囲は、本願の請求の範囲によってのみ限定される。

【図面の簡単な説明】

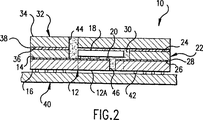

図1は、本発明の原理を採用したチップ/パッケージシステムの平面図である。

図2は、図1の線II−IIにそって得られた、図1のチップ/パッケージシステムの断面図である。

図3は、図1のチップ/パッケージシステムのパッケージ構成部分の縦断面図である。

図4は、パッケージの各層の各格子内の材料含有率を分析するための格子パターンを示すパッケージの一部の平面図である。

図5は、図3の線V−Vにそって得た水平断面図である。

図6は、図3の線VI−VIにそって得た水平断面図である。

図7は、多数の予めラミネートされた孔を示す、パッケージを作成するために使用される層の縦断面図である。

図8は、誘導性層と外側伝導性層(conductive layer)を備えた、予めラミネートされた積層の有孔層の縦断面図である。

図9は、誘導性層からの材料が多数の孔に流入してそれらを満たす、ラミネート後の図8の積層の縦断面図である。

図10は、穿孔の代わりに層に溝を入れられ、ラミネート前にフィラー材料を充填された、別な態様の縦断面図である。

図11は、孔が所望のパターンで形成された有孔層の平面図である。

図12は、熱膨張率の異なる領域を有するリッドを作成するために使用されるプレフォームの側面図である。

図13は、溶融金属を図12のセラミックプレフォームの中に圧力浸透させるための、型の中のプレフォームを示す断面図である。

図14は、成形後の完成したリッドの側面図である。

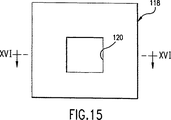

図15は、リッドの残部と異なる熱膨張率を有するインサートを受け入れるための、中央に開口部を有するリッドの側面図である。

図16は、図15のXVI−XVIにそって得られた図15のリッドの縦断面図である。

図17は、図15と16に示されたリッドを完成するために使用されるインサートの側面図である。

図18は、チップと反対のパッケージの下側に取り付けられた膜擬ダイを示す断面図である。

図19は、本発明の1つの態様に使用されるePTFEマトリックスの結節とフィブリルの下部組織を示す走査型電子顕微鏡(SEM)写真である。

図20は、本発明のもう1つの態様に使用されるePTFEマトリックスの結節とフィブリルの下部組織を示すSEM像である。

1.接着剤の封入

本発明のより完全な理解のために、図1と2を参照すると、チップ/パッケージシステム10は、第1と第2の相対する平面14と16を有するパッケージ12を備える。集積回路チップ18は、ハンダバンプ又はボール20によって、パッケージ12の表面14に接続可能である。ハンダボール20は、パッケージ12とチップ18との機械的及び電気的接続を形成する。

相対する表面24と26を有する束縛リング22が、接着剤層28によって、パッケージ12に結合される。束縛リングは、チップ装着キャビティ30を画定する中央に配置された四角い開口部を有する。一般に、束縛リングは、パッケージを強化し、チップ取付の前後でのパッケージの取扱いを容易にさせ、パッケージ12の熱膨張率(CTE)がチップ18のそれと一致しない場合に生じる熱的に引き起こされた曲げモーメントを抑える。束縛リング22の厚さは、チップ18の対応寸法よりも若干大きい。

相対する表面34と36を有するリッド32は、接着剤層38によって束縛リング22に結合される。リッド32の内側表面38は、チップ18の上側表面から間隔を設けられる。リッド32、束縛リング22、及びパッケージ12の外側周辺は同じところにあり、四角形を形成する。特定の態様において、四角形は各辺が33mmである。ここで、四角形の構造が使用されることが多いが、パッケージが四角形の形状であることは必須ではない。また、33mmのサイズは1つの態様であり、別なサイズが採用されてもよい。

電子デバイスに装着されるとき、チップ/パッケージシステム10は、ハンダボール42によってプリント回路ボード(PWB)40に装着される。ハンダボール20と同様に、ハンダボール42は、パッケージとプリント回路ボード40の間の電気的・機械的接続を提供する。

好ましくは、パッケージ12とプリント回路ボード40の双方が、交互に配置された誘導性層と導電性層の多層ラミネートからなる。有機物の好ましい誘電性材料と、好ましい導電性材料は、下記により詳しく説明する。

パッケージ12とチップ18の間の機械的接続を強化するために、チップ18の下側表面とパッケージ12の上側表面の間に接着剤アンダーフィルが施された場合、チップ/パッケージのアセンブリに問題が生じる。接着剤が硬化して縮むとき、パッケージ12はひずみやすく、チップ18はパッケージ12に接続されているため、曲げモーメントがチップ18に加わることがある。この曲げモーメントは、十分に大きければ、チップを破損させ、チップに形成された回路や部品を壊し、及び/又はチップとパッケージの間のハンダボール接続を損なうことがある。

本発明の1つの局面は、リッド32をチップ18の上側表面に機械的に接続する接着剤でチップ装着キャビティ30を充填することによって、曲げモーメントに対処する又は解消することである。接着剤は、リッド32が束縛リング22に適所に結合された後、チップ装着キャビティ30に導入される。

接着剤は、開口部44を通して液体状態で施され、この開口部は、好ましくは、チップ/パッケージシステム10の4辺の1つに平行に形成された細長いスロットである。適用技術の1つの例として、開口部44の中に延ばした針によって液体接着剤が施されることができる。針の先端をハンダボールの近くに置き、スロットのある開口部44にそって先端を前進させながら、先端からアンダーフィル接着剤を出す。接着剤は毛管作用によって移動し、チップ18の下側表面とパッケージ12の上側表面の間の領域を覆う。

アンダーフィル接着剤が施された後、アプリケーター又は針の先端が、リッド32の下側表面38とチップ18の上側表面の間のスペースの近くに置かれ、再度、スロットのある開口部にそって先端を前進させることにより、毛管作用が接着剤をこのスペースに引き込むことができる。

図2に示すように、全体のチップ装着キャビティが接着剤で充填され、又は単に、チップ18と、リッド32及びパッケージ12の表面の間のスペースが充填されることもできる。開口部44の代わりに、又はそれに付加して、パッケージに開口部46が形成されることもできる。全キャビティ30が充填されるべき場合、開口部44又は46が、チップ18の外辺のいずれか1つに平行である必要はない。

開口部46は、スロットではなく、孔が妥当である。また、接着剤の充填の際に空気を逃がすために、キャビティに接着剤を充填するときに2つの開口部があることが一般に好ましい。2つの孔はリッドに形成されることができ、又は、図2に示したように、1つがリッドに形成されてもう1つがパッケージに形成されてもよい。

チップの結合面に接触する接着剤は同時に硬化するため、また、接着剤はチップ18をその反対側で構造体に接続するため、接着剤収縮とチップ片面の熱膨張率の不一致によって生じる曲げモーメントは、熱収縮と他面の熱膨張率の不一致によって生じる曲げモーメントによって相殺される。

曲げモーメントの相殺と解消に併せて、パッケージ12とリッド32は、相対する曲げモーメントが同等で逆ではないように、2つの構成部分の熱膨張率がほぼマッチすべく選択された材料からなる。

キャビティ30に導入される接着剤は、熱伝導性であることが好ましく、チップ18で発生した熱がキャビティ30からリッド32(同様に、熱伝導性材料からなることが好ましい)に移動することを保証するためである。

接着剤層28と38は、任意の適切な接着剤からなることができ、例えば、限定されるものではないが、エポキシ接着剤、耐湿性で150℃を上回る温度に耐え得る接着剤で含浸された多孔質基材、耐湿性で150℃を上回る(好ましくは200℃を上回る)温度に耐え得る接着剤−フィラーの混合物で含浸された多孔質基材、耐湿性で150℃を上回る(好ましくは200℃を上回る)温度に耐え得る接着剤−導電性粒子の混合物で含浸された多孔質基材(例えば、Ablestik▲R▼)が挙げられる。接着剤層28と38は、同じ材料又は異なる材料からなることができる。Ablestik ECF564とECF564A導電性エポキシ、GoreBond M6など、いくつかが市販されている。オーバーフィルとアンダーフィルの接着剤は、Hyso145260のようなSiO2含有液体エポキシであることもできる。また、アンダーフィル接着剤は、ハンダその他の金属系結合剤であることもできる。接着剤として使用されるその他の適切な材料は、下記に説明する。

接着剤層28と38に使用される接着剤は、好ましくは、シート状であるが、キャビティ30に充填される接着剤は、好ましくは、液体状である。ここで、シート状接着剤は、液体材料で置き換えることができ、キャビティ30の液体材料は、少なくともチップ18とリッド32の間の領域については、シート状材料で置き換えることができる。

2.選択的に重ねられた基材層

図3は、図1のチップ/パッケージシステムに使用されることができる、パッケージ12のラミネート構造の縦断面図である。本発明の特徴にしたがうと、外側層56と78に例えば各層が厚さ約20μmの金属層を用い(これらの材料は、メーカーの厚さ許容公差が最少限であり、通常金属層である)、製造許容公差が次第に大きくなる材料(通常、誘電性層)を外側層48と50から中央又はコア層52(例えば、厚さ35μmの銅)を段階的に(progressively)付加することにより、熱膨張の観点から全基材がバランスする。また、バランスはこのようなものであり、このため、曲がり、チップへのその破壊的作用(図3に示していない)、又はチップと電気接触を形成する可能性は大きく克服される。

チップ作動の通常範囲内で有意な熱的曲がりを呈しない適切な基材を形成するための層の組み合わせは、図3に示すように、ハンダマスク層48からの順序で、対称面が通るコア層52の導電性銅中央の方に内側に、

a)20μmのCu/Ni/Au層56の導体、

b)44μmのシアネートエステル−エポキシ−ePTFE(CE/E−ePTFE)層58の誘電体、

c)9μmのCu層60の導体、

d)50μmのビスマレイミド−トリアジン(BT)−エポキシ/ガラス層62の誘電体、

e)18μmのCu層64の導体、

f)44μmのCE/E−ePTFE層66の誘電体、

を備える。

例えは、CE/E−エポキシ−ePTFE層58は、次のようにして調製し、即ち、5.95ポンドのM−30(チバガイギー社)、4.07ポンドのRSL1462(シェルレジンズ社)、4.57ポンドの2,4,6-トリブロモフェニルを末端とするテトラブロモビスフェノールAカーボネートオリゴマー(BD−58)(グレートレイクス社)、136gのビスフェノールA(アルドリッチ社)、23.4gのIrganox1010、ミネラルスピリット中のMn HEX−CEMの10%溶液の18.1g、及び8.40kgのMEKを混合することによってワニス溶液を作成した。このワニス溶液を2つの別な容器の中で20重量%と53.8重量%にさらに希釈した。この2つのワニス溶液を別な含浸槽に注ぎ入れ、ePTFEウェブを、1つの含浸槽に通して直ぐ後に別な含浸槽に続けて通した。均一性を保証するため、ワニスを絶えず攪拌した。含浸させたウェブを、直ちに加熱オーブンに通し、全て又は殆ど全ての溶媒を除去し、接着剤を部分的に硬化させ、ロール上に回収した。このePTFEウェブは、図11に示したように、例えば、25μm、40μmのような任意の所望の厚さを有することができる。25μmの厚さの材料は、単位面積あたり11.2〜13.8g/m2の重さを有した。

図3に示すように、層の同じ対応する列が、外側層50とコア層52の間に提供される。これらは、誘電性層68、伝導性層70、誘電性層72、伝導性層74、誘電性層76、伝導性層78を備える。銅層60と、対称面54の反対側の対応する銅層74は、CE/E−ePTFE層(銅層よりもかなり大きい製造上の厚さの公差を有する)とBT−エポキシ/ガラス層の間に挿入されていることに注意すべきであり、これは、装置、即ち、導体用の回路(CE/E−ePTFE層よりも大きい製造上の厚さの公差を有する)トレースが、真の銅層ではなくて、銅導体のパターンだからである。本発明のこの局面での原理、即ち、より良好にコントロールされた厚さの材料は、パッケージ12の外側の方に配置され、厚さのコントロールの程度が比較的少ない層はコア52の近くに配置されるという原理は、場合により破られるが、これは、CE/E−ePTFE層66について理解できるように、ミクロチップパッケージの主要な電気的ニーズを満たすためである。

銅層54、70、64の厚さは慎重にコントロールされることができ、BT−エポキシ/ガラス層とCE/E−ePTFE層の厚さも、銅層と同等ではないが慎重にコントロールされることができるため、BT−エポキシ/ガラスとCE/E−ePTFEの間に銅を挿入することは、基材12の熱膨張応答を悪化せず、基材12の合計としての熱膨張を抑えるのにより役に立つ。従って、本発明のこの局面の原理的特徴は、製造許容公差(及び、所定の層の厚さから相違して基材12の全体的な熱膨張応答を悪化させる可能性)が、CE/E−ePTFE層66(全ての層の中で最高の熱膨張率を有し、基材12の他の層材料よりも高い)についてはより大きいことを特徴とする。

上記に説明した原理にしたがって層を配置する必要があるが、その他の適切な層材料が、図3に示したものと置き換えられてもよい。例えば、一般的な誘電性材料であるFR4(又は任意の適切な誘電性材料)の層が、図3に示したBT−エポキシ/ガラス層に置き換えられてよい。また、ラミネートされたパッケージ12を形成するのに、より多くの又はより少ない数の層が採用されてもよい。

本発明のこの局面の実施による、基材11の機械的特性の改良をより明確に説明するため、次の表を参照されたい。

基材12を形成する層の組成を、上記のように、別な公知の基材層材料で置き換えることによって変更させることができるが、基材の内側層として、最も大きい製造厚さ許容公差(通常、誘導体)を有する層を配置しても、本発明によって提供される改良性能が得られることは明らかである。

以上から明らかなように、ラミネート式基材又はパッケージ12の個々の層の配置は、寸法コントロール、高い曲げ剛性、基材内での熱膨張率の適合性を得るように選択的になされる。即ち、基材内の熱膨張率の差異を回避するために、対称面の相対する側の層が同じ材料からなり、同じ厚さを有することが重要である。ラミネートされた基材の外側層に金属層を配置することが望ましいだけでなく、曲げ剛性を高めるには、外側金属層を内側金属層よりも薄くすることが望ましい。

3.単位面積の組成コントロール

本発明のもう1つの局面は、2つの層の熱膨張率がマッチすることを保証するために、相対する層の相殺操作が行われるべきかどうかを判断するため、各層の材料組成を分析することである。

例えば、図3と4に関して、伝導性層60は、回路を形成するために金属が除去された領域を有する、パターン状の層である。金属が除去された層60の領域においては、対称に配置された伝導性層74の対応領域は、異なる金属分を有し、2つの層60と74の間に熱膨張率の局所的な相違をもたらす。熱膨張率の差異は曲がりをもたらすことがある。相違するが対称的に相対する層に多少の金属が堆積されたような、堆積によって形成された層についても同じことがあてはまる。

本発明の1つの局面は、1つの層の材料含有率を分析し、次いで材料含有率をマッチさせるように相対する層を変化させることである。図3と4に関して、基材12が、単位面積の正方形80の列に分割される。これらの正方形は、例えば1mm2である。この正方形80は、パッケージの全層にわたるスペースに広がり、1つの層の各正方形は、対称の相対する層に同等領域を有する。

正方形の列のそれぞれの正方形の各々の境界の中にある基材12の各層の組成が分析され、問題とする単位領域の各層の中で、これらの材料の各々の材料と濃度を特定する。

各層の中の材料のこの濃度又は分布は、層の設計ファイルのオリジナルデータより、又は層のマスクワークの分析によって求められる。例えば、図3と4に示すように、銅層60と74は、上記のように、真の層ではなく、電気コネクター用の適切な導体を形成するためのパッケージ12の中の導体の分布である。この状態をより的確に説明するため、図5を参照すると、図3の断面V−Vの平面図を示す。

図5に示すように、「層」60を含む銅導体は、基材12の全領域には延在せず、銅の小さい不均一な又は不均等に分布した部分を占めるに過ぎなく、その領域では、層60を構成する銅導体によって覆われずに、基材12の平面領域のこれらの部分でBT−エポキシ/ガラス層62が露出する。

次に、図6は、銅の電気導体74の不均等で不均一な分布と、層60の銅の量に比較し、層74を形成する導体の銅の若干多めの量を示す。

この仕方において、層の中の単位面積あたりの例示の銅濃度が明らかにされることができる。図6に示すように、層60と74の各々の共通単位領域80の中の銅の調節された濃度は同じでなく、これは、これらの層に与えられる電気回路の要件のためである。それにもかかわらず、層60の電気不活性銅ストリップ60Aと、層74から除去された電気的に不要の銅部分74Aは、2つの銅の電気回路層60と74の間で適切なバランスを形成するのである。同じ基材層材料の濃度をバランスさせることにより、基材12の曲がりはかなり抑えることができる。この目的のためのバランスは、対称面から同じ距離にある相対する層のペアに同じ濃度又は同じ空隙を形成することと定義される。

例えば、層60(図5)の中の銅の量をバランスさせて比較層74の中の銅の量に近づけるため、電気不活性の銅のストリップ60Aが、BT−エポキシ/ガラス層62の表面に付加される。あるいは、層74を形成する電気導体から、電気的に不要な銅74Aの等価量が除去されることにより、相対的な銅濃度がバランスされることができる。

当然ながら、現実の実施においては完全なバランスはあり得ない。本発明の目的のためのバランスは、回路の電気的要件が満たされる一方で、物理的構造としての層の各々の銅濃度の間の均一性を出来るだけ近く形成することを可能にする程度で達成される。1つの相対する層のペア、例えば層60と74の間でアンバランスが存在すると、このアンバランスは、同等で反対の曲げモーメントを形成するように、第2のペアの例えば64と70の層を故意にアンバランスさせることによって相殺されることもできる。

意図する目的を達成するために上記の仕方のいずれかの1つ以上を利用してバランスを強制することも、当然ながら本発明の範囲内である。

電気導体層60と74に関して本発明の特定の例を説明したが、本発明の目的において定義されるバランスは、銅について上記に説明したプロセスを用い、Cu/Ni/Au層56、CE/E−ePTFE層58、BT−エポキシ/ガラス層62に含まれる成分の範囲内で追求されることも必要である。

この仕方において、単位面積の四角形80によって画定される単位面積の四角形の各々の中の層の間で、成分濃度の全体的バランス、又は同等性を確立することにより、曲がりその他の不都合な熱膨張による曲げモーメントは、大幅に削減される。

層の成分材料の濃度を操作することによる技術は、基材12に限定されるものではなく、リッドや束縛リングなどのチップ/パッケージシステムのその他の構成部分の全部又は一部に首尾よく適用されることができる。

上記の本質的意義は、相対する層の熱膨張率が局所的にマッチされることである。即ち、ラミネート構造の相対する層に同じ材料を使用したとき、互いに重なる領域(共通領域を意味)は、2つの層の一方もしくは他方、又は両方を交替することによって、ほぼ同じ量の材料を有する。この交替は、材料の付加(例えば、堆積)又は材料の除去(例えば、エッチング)の形態であることができる。この効果は同じであり、即ち、個々の対称的にマッチした層の長さと幅で熱膨張率の勾配を調整(account)することにより、パッケージの信頼性が高められる。

4.ダイ区域の熱膨張率コントロール

再び図1と2に関して、チップ18のような集積回路チップは、一般に、パッケージ12のような非セラミック材料からなる下地パッケージに比較して実質的に異なる熱膨張率(CTE)を有するシリコンのような材料からなる。これらの熱膨張率の相違は、チップ18をパッケージ12に取り付けるハンダボール接続に応力を与える。

この問題の解決は、2つの異なる熱膨張率であって、1つはプリント回路ボード(PWB)40のそれにほぼマッチして他方はチップ18のそれにほぼマッチする熱膨張率を有するパッケージを作成することを含む。言い換えると、チップ18の熱膨張率は、チップ18の直ぐ下にある基材12の部分12Aの熱膨張率にほぼマッチされる。

一般に、チップ18は有機物パッケージよりも低い熱膨張率を有するため、パッケージの部分12Aは、基材の周囲領域よりも低い熱膨張率を有する。しかしながら、このことは、条件が逆転できないと言うことではなく、別な又は異なる構成部分を装着するために、中央領域は周囲領域よりも高い熱膨張率を有することができる。

中央に異なる熱膨張率を形成するため、パッケージ12のチップ装着領域12Aは,種々の仕方で達成されることができる。1つは、材料そのものが異なる熱膨張率を提供するように選択され、中央領域に多層構造で種々の材料を使用することである。チップ18の下のパッケージ12の部分12Aに層状の材料(例えば、銅、モリブデン、インバール)の組み合わせが選択され、チップ18とパッケージ12の双方の通常の作動温度範囲にわたって、チップ18の熱膨張率に類似であるが全体的に高い合計熱膨張率を領域12Aに提供する。この仕方において、チップ18と基材12の間の不都合な相対的運動が大きく解消される。

チップ18の熱膨張率にパッケージ12の部分12Aの熱膨張率を近づけるることで、また、本発明にしたがうことにより、全パッケージ12の平均熱膨張率が、パッケージ12とその取付チップ18が結合されるプリント回路ボード40の熱膨張率にマッチされるはずである。プリント回路ボード40の熱膨張率を、パッケージ12とチップ18の総計熱膨張率に本質的に近似させ得ないことは、プリント回路ボード40とパッケージ12の間に、熱が起因する曲げ・剪断モーメントの発生をもたらすことがある。このようにして生じたプリント回路ボード40とパッケージ12の間のアンバランスな力はチップ18に伝達され、これが、上記の不都合な状態でこの曲がりと相対的なモーメントに結びつき、例えば、ハンダ付け電気接続やパッケージとプリント回路ボード40の間の電気接続に剪断を及ぼす。同様な状態で、パッケージ12とプリント回路ボード40の間に電気接続を形成するために使用されたハンダボール40が、不都合な剪断事象に曝される。本発明のこの局面の典型的な態様において、調整されるべき次の構成部分と例示の熱膨張率特性は以下の通りである。

従って、チップ18の下のパッケージ12の領域12Aは、例えば6〜10PPM/℃のような、2〜3PPM/℃の範囲まで出来るだけ近い熱膨張率を享有することができる。また、パッケージ12の総計又は平均熱膨張率は、プリント回路ボードの熱膨張率に近づくために、16〜17PPM/℃の範囲にあることができる。

ここで、

α=x面とy面で空間的に変化するパッケージ12の熱膨張率

α=全パッケージ12の平均熱膨張率

パッケージのチップの下の部分にいろいろな熱膨張率を使用することは、フリップチップパッケージ、又はパッケージとプリント回路ボードの間の周囲のボールグリット列コネクターを採用する上で特に適する。図2に見られるように、ハンダボールは、チップキャビティ30の下部領域のプリント回路ボード40とパッケージ12の間には使用されない。この理由は、チップ18の熱膨張率にマッチさせるために下げられた、パッケージ12の領域12Aの間で熱膨張率の不一致が存在するであろうためである。ここで、プリント回路ボード40とチップ/パッケージの組み合わせの間の相対的運動が、特殊な応用において調整されるならば、チップ18の一部又は全部がハンダボール42と同居することができる。

上記に例示し説明した態様は、主として、2つの明確に異なる領域と2つの明確に異なる熱膨張率を有する基材に関するものであったが、特にマルチチップモジュール(MCM)のようなパッケージ上にマルチチップを装着する場合、いくつかの追加の領域が適用されることもできる。また、チップ装着領域は、中央に位置する必要はなく、パッケージの実質的に全ての領域に配置されることができる。

5.選択的な熱膨張率の調節

パッケージ12のいろいろな領域がいろいろな熱膨張率を有することが望まれる場合、例えばパッケージの熱膨張率を2つの異なる構成部分にマッチさせることを試みるとき、パッケージ12を形成する層状構造を物理的に変更することによって熱膨張率を変化させることができる。

図7に関して、コア層82の一方の表面86から他方の表面88までコア層を貫く複数の横に配向した孔84を含めるため、コア層82が、ドリル、エッチングその他によって加工される。コア層82は、図3のコア層52に相当する1つであり、層52と同様に、コア層は一般に銅からなる。

図8において、コア層82は、2つの誘電性層90と92の間に重ねられて示されている。一般に、層のラミネーションアセンブリは、さらに、誘電性層90と92のそれぞれ相対する側に配置された伝導性層94と96を備えることができる。

誘電性層が、プレスする直前にB段階である有機材料からなる場合、誘電性材料は、図9に示したように、孔に流入してそれを満たす。コア層82は、このため、その中に全体に分配された誘電性材料を有する銅マトリックスを備えた複合材料となる。この誘電性材料は、銅よりも高い熱膨張率を有し、このため、コア層の熱膨張率は、孔84が存在すると高められる。

あるいは、孔84は、パッケージの熱膨張率に所望の作用を与えるため、ラミネーションの前に何らかの材料で満たされることもできる。例えば、割合に低い熱膨張率を有するフィラーが、液体として孔84を満たすことができ、ラミネーション工程にコア82を供する前に固化させることができる。

別な態様として、図10を参照して、コア層98が、機械加工、エッチングその他で加工され、所望の熱膨張率変化を与えるように選択されたフィラー材料102で充填される1つ以上の溝100を形成することもできる。より低い熱膨張率のフィラーは、コア98の熱膨張率を下げることができ、より高い熱膨張率のフィラーは、コア98の熱膨張率を高めることができる。

孔、溝、その他の仕方が使用されるにおいて、コアは、任意の公知技術の例えばレーザー穿孔、機械加工、打ち抜き、エッチングなどで加工することができる。また、この加工は、必ずしも、ラミネートされたパッケージのコア層に形成されず、誘電性又は伝導性の任意の層に形成されることができる。

コア層を越えて層に加工を施す場合、対称の等価層が同様に変更される必要がある。例えば、図3において、孔が形成されて伝導性層64の中に満たされた場合、対称的に相対する伝導性層70の同じ位置に、同じパターンの孔と同じフィラーが使用されなければならない。

図11に示すように、熱膨張率の局所的な変化が必要な場所に、割合に密に詰まった配置で、コア層82に格子状パターンで孔84が配置されることができる。例えば、チップ18の下の領域でパッケージ12の熱膨張率をマッチさせるため(図2)、コア層82に、コア層を覆うチップ装着領域で孔をパターン形成することができる。次いでその孔に、その領域のパッケージの熱膨張率を増加又は低下させる材料を充填することができる。

6.チップパッケージのリッドの熱膨張率調節

上記のように、チップ18は、1cm2〜4cm2のオーダーであることができるが、場合により100ワットものかなりの熱量を発生する。チップ18の電気特性の劣化やさらには破壊を回避するために、チップ18が許容温度内で作動を続けることができるように、この熱を発散させる何らかの手段を提供する必要がある。

チップ18によって発生した熱をリッド32に常に放散するように、重要な放散機能を与えるため、本発明の1つの局面において、アミーンらの米国特許’473に記載のタイプのペーストとその特許に記載のペースト誘導体を用いると、チップ18をリッド32に接続する体積に、適切な熱伝導性と熱膨張率がマッチする接着剤を提供することが見出された。

本発明のさらなる原理にしたがい、マッチしない熱膨張率特性によって生じる曲がりの程度を抑える目的で、リッド32の熱膨張率を今度はチップ18の熱膨張率に近似させ、さらに、かなり相違する束縛リング22とパッケージ12の熱膨張率に近似させることが、リッド32の材料組成の操作による。

上記のように、従来技術のリッドは、一般に、アルミニウム又は銅から作成されるか、あるいは、アルミニウム又は銅を炭化ケイ素又はその他の低熱膨張率強化マトリックスに付加して作成される。例えば、アルミニウムは23PPM/℃の熱膨張率を有し、純粋な炭化ケイ素は3.7PPM/℃の熱膨張率を有する。このため、リッド32は、純粋な炭化ケイ素の3.7PPM/℃と純粋なアルミニウムの23PPM/℃の範囲の任意に設定された熱膨張率を享有できる可能性がある。

本発明によると、リッド32が熱的・物理的に接触するチップ/パッケージ10の異なる構成部分とマッチするためには、熱膨張率の異なる領域を設けられるべきであることが確認された。このことは、いろいろな仕方で達成されることができる。例えば、リッド32は、炭化ケイ素とアルミニウムを含む金属マトリックス材料からなることができる。材料の濃度は、リッドの所望の2つの領域の熱膨張率を達成するように変化させることができ、特に、チップ18に位置的に対応するリッドの中央領域は、リッド32の周囲領域よりも低い熱膨張率を有する構成にされ、好ましくは、束縛リング22より高い熱膨張率にマッチする熱膨張率にされる。

2つの領域の熱膨張率のリッドは、次の仕方で作成されることができる。図12に関して、プレフォーム104は、炭化ケイ素粉末又はウィスカーからなる。プレフォームはプレスされて所望の形状にされるか、又は機械加工又は切断されてその所望の形状を形成することができる。所望の形状は、中央領域106が外側領域108と110よりも厚い寸法を有するものである。プレフォーム104は、標準的な粉末金属冶金技術を用いて作成可能である。

次いでプレフォーム106は、型の中に入れられ、溶融アルミニウムを加圧含浸される。図13に示すように、型ダイ112と114は、プレフォームの中央領域にほぼ隣接し、外側領域の周りに空隙を形成する。加圧含浸の後、図14に示すように、仕上げられたリッド116は、パッケージ12にフィットする所望の全体的形状を有するが、中央領域は、比較的高い濃度の炭化ケイ素を有し、中央領域は比較的低い熱膨張率を有することができる。具体的には、低めの熱膨張率は、チップのそれにほぼマッチし、これは約2.6であり、一方でより高い熱膨張率のアルミニウムを高めの濃度で有する外側領域は、束縛リングのそれにほぼマッチするように設計される。

束縛リングに結合されるリッドの周囲部分は、リングの熱膨張率に近づくように、高めのアルミニウムと低めの炭化ケイ素の濃度を有するべきであるため、リッドを形成する炭化ケイ素の周囲部分にアルミニウムを吸収させるにおいて、リッドの中央部分よりもこの周囲領域に割合に多めのアルミニウムが添加される。リッドの各部分に相対的濃度を選択することによって、リッドの平均熱膨張率は、パッケージ12の平均熱膨張率と、チップ18の異なる平均熱膨張率にマッチする。リッドにおけるこの相対的なアルミニウムと炭化ケイ素の濃度の操作は、ミクロチップパッケージと構成部分が実質的に平坦性を維持する一方で、ダイ又は接着剤境界に及ぼされる応力を減らすことを可能にする。

炭化ケイ素プレフォームの大きい中央部分は、本質的に多孔質であり、仕上げられたリッドの異なる領域において、アルミニウムと炭化ケイ素の比を確定する。前述のように、炭化ケイ素に対するアルミニウムの多めの濃度は、リングの付近に必要である。これらの濃度は、プレフォームの中にアルミニウムを溶解させ、プレフォームの外側領域の上又は下の空隙を充填することによって達成される。この仕方において、1つの領域のリングと別な領域のチップの熱膨張率に近づく熱膨張率を与えるアルミニウムと炭化ケイ素の濃度が提供される。

その結果、本発明の実施を介して、リッドのある部分の熱膨張率が、リッドの対応部分に結合されたチップ/パッケージシステム10(図1)の別な構成部分の熱膨張率特性に本質的にマッチするように形成されることを可能にする。

上記に炭化ケイ素/アルミニウムの系を説明したが、異なる領域に異なる熱膨張率を呈するリッドを形成するように、その他の材料が使用されることもできる。また、単一の粉末状材料のセラミックや金属を使用し、異なる圧縮力を適用することによって、異なる領域で熱膨張率を変化させることもできる。例えば、中央領域が、外側領域よりも高い又は低い理論密度を有することができ、ある場合に、熱膨張率の十分な差異を提供することもできる。この場合、粉末状材料は、熱膨張率の所望の差異を与えるように、選択され及び/又は混合されることができる。

別な態様が図15〜17に示されており、ここでは、リッド118が中央開口部120を有するように作成される。インサート122が、開口部120にフィットするサイズにされる。インサート122は、リッド118を形成するのに使用される材料と異なる熱膨張率を有する材料からなる。特に、リッドの中央領域に比較的低い熱膨張率が望まれる場合、中央領域がチップを覆う場合のように、インサートは、リッドの残部よりも低い熱膨張率を有する材料から作成されることができる。

図15〜17の態様を実施するため、リッド118は、単一片から作成されて中央開口部120が機械加工されることができ、あるいは、リッドが粉末の金属又はセラミックから作成されるように、開口部が一体に形成されることもできる。インサートは、同じ技術で形成されることができ、例えば、アルミニウムを含浸された炭化ケイ素プレフォームを含んでなることもできる。任意の割合で、インサートの熱膨張率はチップのそれにマッチするように特別に作成され、また、リッド118の熱膨張率は束縛リングのそれにマッチするように特別に作成されることができる。

また、リッドの中央領域における炭化ケイ素のより高い濃度は、所望のリッドの同じ寸法を有する低密度の多孔質炭化ケイ素プレフォームを除去することによって達成可能である。この中央キャビティの中に、高密度の多孔質炭化ケイ素のスラグが入れられ、キャビティを充填する。このプレフォームをアルミニウムで含浸した後、高めの炭化ケイ素濃度の中央領域と、低めの炭化ケイ素濃度の周囲領域を有するリッドが得られる。

7.熱膨張の相殺

次に図18に関し、チップ124が、ハンダボール128によってパッケージ126に装着されて示されている。束縛リング130は、パッケージ126の上側表面に装着されている。

チップ124とパッケージ126の間の熱膨張率の相違により、チップ124に作用してチップの平坦性を潜在的に損なう曲げモーメントが発生する。チップ124がシリコンであって、パッケージが、本願で説明する材料からなる薄い有機物誘電性層を使用したものであれば、材料の相違による熱膨張率の相違は大きい。

本発明によると、パッケージにチップを結合させる前に、パッケージ126の下側表面に偽ダイ132が結合される。偽ダイ132は、チップ124に熱膨張率がマッチし、とりわけアンダーフィル接着剤が硬化するときにチップ/パッケージ取付によって発生する曲げモーメントに対抗する。即ち、偽ダイ132は、チップ取付の際に、モーメントを反対の曲げモーメントで相殺する。

偽ダイ132は、シリコンからなることができるが、チップ124に類似の熱膨張率を呈するその他の材料も使用可能である。ここで、それはチップ124の正反対に配置されるべきである。また、曲げモーメントに抵抗するように厚めに作成されるならば、シリコンチップを覆う異なる熱膨張率を有する材料が使用されてもよい。例えば、アルミニウムは約9の熱膨張率を有するが、同じ作用を得るのに十分に厚くされるならば、使用可能である。

本発明のもう1つの局面は、偽ダイをパッケージに接着によって結合させ、同時に、チップ124とパッケージ126の間の領域にアンダーフィル接着剤を施すことである。両方の接着剤の同時硬化は、偽ダイの曲げモーメントが、アンダーフィルの接着剤の収縮によって生じる曲げモーメントを相殺することを保証する。

偽ダイ132は、受動的強化材であることができるが、パッケージ上に形成されたコンデンサーのような電気部品の形態を取ることもできる。また、偽ダイは、品質管理に不合格の実際のチップであることもでき、あるいは、コンデンサー、抵抗、インダクタンスのような「受動的」部品と称されることが多い1つ以上の回路部品であることもできる。ここで、重要な点は、受動的部品が、マイクロチップパッケージの予想される作動温度の範囲にわたって、チップによって生じる熱膨張率と本質的に同じであって但し方向が逆の、熱膨張が引き起こす曲げモーメントを提供すべきである。

この仕方において、さもなければチップや基材をひずませる又は反らせて、同等であるが基材の反対側に及ぼす力が、実質的に互いに相殺することができる。これらの等しくて反対の力の間のバランスの物理的結果は、互いに打ち消し合い、それによって、チップを本質的に平坦に維持することを可能にする。

下記の表は、電気的受動部品として使用される種々の材料に実験的に現れた結果を例示する。

ダイ区域とミクロチップのパッケージを平坦に維持するのに、いろいろな強化材によって与えられる改良の例示するため、下記の表に注目されたい。

−工業的有用性−

上記の本発明の態様の各々は、マイクロチップパッケージを形成する個々の構成部分の間の相対的な動きを本質的に除去、コントロール、又は低下させることにより、この相対的な動きの源を制約することなく、改良されたマイクロチップパッケージに大きく寄与する。即ち、熱膨張に起因するひずみ、異なる基材層の製造公差による反りなどによって、マイロチップパッケージの構成部分間の相対的動きの各々と、このような動きの不都合な結果は、かなりの程度で回避される。

上記のように、接着剤28と38はいろいろな接着剤材料であることができる。1つの態様において、接着剤はフルオロポリマー材料を含み、例えば、多孔質ポリテトラフルオロエチレン(PTFE)であり、特には、Gore社の米国特許第3953566号に教示の押出及び/又は延伸膨張PTFEである。この材料は、一般に、米国特許第3953566号にしたがってその元の長さの少なくとも2〜4倍に伸長された多孔質延伸膨張PTFEである。この伸長によって生じた気孔は、充填材料が2つの構成部分の間に押し込められるとき、生来的な空気の逃げ場として作用する。また、延伸膨張PTFEの性質により、構成部分のパーツの間の熱膨張率の相違により生じた応力は、伝導性層がそれらの間に配置されるならば、伝導性層に開放されることができる。

適切な境界組成物には、約50〜60体積%の固形分のZnO、BN、その他の非伝導性で良好な熱伝導性のフィラーを含むPTFEが挙げられる。最終的な生産品は、所望の適合性の程度を得るように、4:1、3:1、又は2:1の比で延伸膨張されることができる。前述のように、延伸膨張プロセスによって生じた気孔の存在は、仕上生産品の適合性に寄与し、この材料が2つの平行なプレートの間に配置されて一緒に圧力を受けたとき、捕獲空気を逃がすのに役立つ。これらの材料は、任意の適切な形状に作成されることができ、例えば、5〜15ミル(0.127〜0.381mm)の範囲の厚さを有する薄いテープである。

本発明に使用するのに適切なもう1つの組成物は、1〜40μmの粒子サイズを有する銅やニッケルのような金属粉末を充填したPTFEである。2モードや3モードの分布が、このような材料の詰まりを与え、例えば、40〜45μmの粒子を混合した1〜5μmの粒子である。これにより、高い充填密度を可能にし、適合性を損なうことなく、熱伝導性の増加もまた得られる。仕上られた充填材入りPTFEに対する金属の全体積割合(空気を含む)は20〜90%の範囲である。仕上げられた材料17と56は、接着剤とフィラーの混合物を吸収した又は含浸された多孔質マトリックス系としての材料であることができる。

本発明のもう1つの態様において、接着剤17と56は、基材の元の気孔体積に多量のフィラーと熱可塑性又は熱硬化性接着剤を吸収し、加熱させて接着剤を部分硬化させ、B段階組成物を形成した不織基材としての多孔質マトリックスである。基材は、フルオロポリマー、例えば、米国特許第3953566号、同4482516号(いずれも本願で参考にして取り入れられている)の多孔質延伸膨張ポリテトラフルオロエチレン材料である。望ましくは、平均流量気孔サイズ(MFPS)は、最大粒子の約2〜5倍又はそれ以上であるべきであり、フィラーのそれの約2.4倍を上回るMFPSが特に好ましい。ここで、平均流量気孔サイズと平均粒子サイズの比を1.4より高いように選択して得られる適当な組成物も、本発明の範囲内である。また、最小気孔サイズと平均粒子サイズの比が少なくとも0.8より大きい、又は最小気孔サイズと最大粒子サイズの比が少なくとも0.4より大きいとき、許容できる組成物が調製可能である。MFPSと粒子サイズの比は、Microtrak▲R▼FRA型粒子分析装置を用いて測定することができる。

あるいは、相対的な気孔と粒子のサイズを測定するための別なメカニズムが、最小気孔サイズが最大粒子サイズの約1.4倍以上であるとして計算されることもできる。

延伸膨張フルオロポリマー基材の他に、多孔質延伸膨張ポリオレフィンの例えば超高分子量(UHMW)ポリエチレン、延伸膨張ポリプロピレン、ペースト押出と、犠牲フィラー、多孔質の無機又は有機フォーム、微細多孔質セルロースアセテートを混和することによって調製されたポリテトラフルオロエチレンが使用されることもできる。

多孔質基材は、少なくとも30%、好ましくは少なくとも50%、最も好ましくは少なくとも70%の初期空隙体積を有し、空隙の中に熱硬化性又は熱可塑性接着剤樹脂と微粒子フィラーのペーストの含浸を容易にし、同時に全体的な複合材料の脆性と粒子の沈降を防ぐために融通性のある強化を提供する。

フィラーは、Microtrak(登録商標)型式FRAの粒子分析装置で分析した場合、粒子の集合を形成し、ヒストグラムによって最大粒子サイズ、最小粒子サイズ、及び平均粒子サイズを表示する。

接着剤に混和されるべき適切なフィラーには、限定されるものではないが、BaTiO3、SiO2、Al2O3、ZnO、ZrO2、TiO2、沈降したゾルゲルセラミックの例えばシリカ、チタニア、及びアルミナ、非伝導性炭素(カーボンブラック)、及びこれらの混合物が挙げられる。特に好ましいフィラーはSiO2、ZrO2、TiO2そのもの、又はこれらと非伝導性炭素との組み合わせである。最も好ましいフィラーは、米国特許第4705762号に教示の蒸気金属燃焼プロセスによって製造されたフィラーであり、限定されるものではないが、例えば、本質的に充実、即ち中空球でなく、均一な表面曲率と高度な球形性を有する、ケイ素、チタン、アルミニウムから得られるシリカ、チタニア、アルミナの粒子である。

フィラーは、シリル化剤によって及び/又はカップリング剤使用によるような接着剤マトリックスに反応する薬剤を使用することによってフィラーを疎水性にする周知の技術により処理されることができる。適切なカップリング剤には、シラン、チタネート、ジルコネート、及びアルミネートが挙げられる。適切なシリル化剤には、限定されるものではないが、官能性シリル化剤、シラザン、シラノール、シロキサンを挙げることができる。適切なシラザンには、限定されるものではないが、ヘキサメチルジシラザン(Huls H730)とヘキサメチルシクロトリシラザン、シリルアミドの例えばビス(トリメチルシリル)アセトアミド(Huls B2500)、シリルユリアの例えばトリメチルシリルユリア、及びシリルイミダゾールの例えばトリメチルシリルイミダゾールが挙げられる。

チタネートカップリング剤は、テトラアルキル型、モノアルコキシ型、配位型、キレート型、第4塩型、ネオアルコキシ型、シクロヘテロ原子型によって例示される。好ましいチタネートには、テトラアルキルチタネート、Tyzor(登録商標)TOT〔テトラキス(2-エチル-ヘキシル)チタネート〕、Tyzor(登録商標)TPT〔テトライソプロピルチタネート〕、キレート化チタネート、Tyzor(登録商標)GBA〔チタンアセチルアセチルアセトネート〕、Tyzor(登録商標)DC〔チタンエチルアセトアセトネート〕、Tyzor(登録商標)CLA(デュポン社の所有)、モノアルコキシ(Ken−React(登録商標)KRVTTS)、Ken−React(登録商標)、KR55テトラ(2,2-ジアリロキシメチル)ブチル、ジ(ジトリデシル)ホスフィットチタネート、LICA(登録商標)38ネオペンチル(ジアリル)オキシ、トリ(ジオクチル)ピロ-ホスフェートチタネートが挙げられる。

適切なジルコネートは、Kenrichカタログの22頁に詳しく記載されている任意のジルコネートであり、とりわけKZ55-テトラ(2,2-ジアリロキシメチル)ブチル、ジ(ジトリデシル)ホスフィットジルコネート、NZ−01−ネオペンチル(ジアリル)オキシ、トリネオデカノイルジルコネート、NZ−09−ネオペンチル(ジアリル)オキシ、トリ(ドデシル)ベンゼン-スルホニルジルコネートが挙げられる。

本発明に使用可能なアルミネートには、限定されるものではないが、Kenrich(登録商標)、ジイソブチル(オレイル)アセトアセチルアルミネート(KA301)、ジイソプロピル(オレイル)アセトアセチルアルミネート(KA322)、及びKA489が挙げられる。

上記の他に、例えば、ジビニルベンゼンやジビニルピリジンような架橋したビニルポリマー、又は最初に非常に高い希釈率(MEK中の0.1〜1.0%の溶液)で施される開示された任意の熱硬化性マトリックス接着剤のサイジングのようなある種のポリマーが使用可能である。また、ジクミルペルオキシドのようなある種の有機過酸化物がフィラーと反応されることもできる。

接着剤そのものは熱硬化性又は熱可塑性でよく、ポリグリシジルエーテル、ポリシアヌレート、ポリイソシアネート、ビス-ドリアジン樹脂、ポリ(ビス-マレイミド)、ノルボルネンを末端とするポリイミド、ポリノルボルネン、アセチレンを末端とするポリイミド、ポリブタジエン及びその官能化コポリマー、環状オレフィンポリシクロブテン、ポリシロキサン、官能化ポリフェニレンエーテル、ポリアクリレート、ノボラックポリマーとそのコポリマー、フルオロポリマーとそのコポリマー、メラミンポリマーとそのコポリマー、ポリ(ビスフェニルシクロブタン)、及びこれらの配合物又はプレポリマーを挙げることができる。上記の接着剤は、難燃性や高められた靱性を付与するように、それらを相互に配合されることもでき、又は別なポリマーや添加剤を配合されることもできると理解すべきである。

本願において、平均流量気孔サイズと最小気孔サイズは、それらの値を直接提示するCoulter▲R▼ポロメロターII(英国のLutonにあるコールターエレクトロニクス社)を用いて測定した。平均粒子サイズと最大粒子サイズは、マイクロトラック光散乱粒子サイズ分析器の型番FRA(米国ペンシルバニア州のノースウェールズにあるLeeds & Northupのマイクロトラック部門)を用いて測定した。平均粒子サイズ(APS)は、粒子の50%がそれよりも大きい値と定義される。最大粒子サイズ(LPS)は、マイクロトラックのヒストグラムで最大の検出可能な粒子と定義される。あるいは、最大粒子サイズは、マイクロトラックFRAが100%の粒子がそれを通過したと決定したときの最小点と定義される。

一般に、接着剤とフィラーの誘電体の調製方法は、(a)潤滑されて押出されたプレフォームを、小さな粒子と接着剤が空隙又は気孔体積の中に自由に流れ込むことを可能にするのに十分な微細構造まで伸長することによって、ポリテトラフルオロエチレンシートを延伸膨張する、(b)例えば熱硬化性又は熱可塑性材料のポリマーとフィラーからペーストを作成する、(c)浸漬、コーティング、圧力供給によって、延伸膨張ポリテトラフルオロエチレンのような高度に多孔質の足場の中に接着剤とフィラーのペーストを吸収させることを含む。

表1は、基材の平均流量気孔サイズ(MFPS)と粒子サイズの関係の効果を示す。平均流量気孔サイズ(MFPS)と最大粒子サイズの比が1.4以下であると、劣った結果が見られる。この場合、均一な複合材料が観察されず、フィラー粒子の殆どは、微細多孔質の基材に均一には侵入しない。平均流量気孔サイズ(MFPS)対最大粒子サイズの比が約2.0を上回ると、均一な複合材料が得られる。また、平均流量気孔サイズ対最大粒子サイズの比が大きい程、均一な分散系が微細多孔質基材の中に入り込む相対的な割合が高い。

例1

281.6gのTiO2(TI Pure R-900、デュポン社)を、MEK中の難燃化されたジシアンアミド/2-メチルイミダゾール触媒のビスフェノールAを基剤とするポリグリシジルエーテル(Nelco N-4002-5,ネルコ社)の20重量%溶液中に混ぜ入れることによって微細な分散系を調製した。均一性を保証するため、この分散系を絶えず攪拌した。延伸膨張ポリテトラフルオロエチレン(PTFE)の小片をこの樹脂混合物の中に浸した。可撓性のある複合材料を得るため、このウェブを張力下で165℃にて1分間乾燥した。このようにして得られた部分硬化した接着剤複合材料は、57重量%のTiO2、13重量%のPTFE、及び30重量%のエポキシ接着剤を含んだ。この接着剤シートの数層を銅箔の間に配置し、真空を利用した液圧プレスにより225℃の温度で90分間600psiでプレスし、次いで圧力下で冷却した。これにより19.0の誘電率を有する銅ラミネートが得られ、100μm(0.0039インチ(3.9ミル))の誘電体ラミネート厚さの平均層厚さにおいて、280℃のハンダ衝撃に30秒間耐えた。

例2

フェニルトリメトキシシラン(04330,Huls/Petrarch)で前処理した386gのSiO2(HW-11-89,Harbison Walker社)を、200gのビスマレイミドトリアジン樹脂(BT206OBJ,三菱ガス化学社)と388gのMEKのマンガン触媒溶液に混ぜ入れることによって微細な分散系を調製した。均一性を保証するため、この分散系を絶えず攪拌した。次いで厚さ0.0002インチの延伸膨張PTFEの小片をこの樹脂混合物の中に浸し、取り出し、次いで可撓性のある複合材料を得るため、張力下で165℃にて1分間乾燥した。このプリプレグの数層を銅箔の間に配置し、真空を利用した液圧プレスにより225℃の温度で250psiで90分間プレスし、次いで圧力下で冷却した。このようにして得られたこの生成した誘電体は、53重量%のSiO2、5重量%のPTFE、及び42重量%の接着剤を含み、銅に対する良好な接着性、3.3の誘電率(10GHz)、及び0.005の誘電正接(10GHz)を示した。

例3

274.7gのビスマレイミドトリアジン樹脂(BT206OBJ,三菱ガス化学社)と485gのMEKのマンガン触媒溶液の中に483gのSiO2(HW-11-89)を混ぜ入れることによって微細な分散系を調製した。均一性を保証するため、この分散系を絶えず攪拌した。次いで厚さ0.0002インチの延伸膨張PTFEの小片をこの樹脂混合物の中に浸し、取り出し、次いで可撓性のある複合材料を得るため、張力下で165℃にて1分間乾燥した。このプリプレグの数層を銅箔の間に配置し、真空を利用した液圧プレスにより225℃の温度で90分間にわたって250psiでプレスし、次いで圧力下で冷却した。このようにして得られた生成した誘電体は、57重量%のSiO2、4重量%のPTFE、及び39重量%の接着剤を含み、銅に対する良好な接着性、3.2の誘電率(10GHz)、及び0.005の誘電正接(10GHz)を示した。

例4

15.44kgのTiO2粉末(TI Pure R-900、デュポン社)を、3.30kgのビスマレイミドトリアジン樹脂(BT206OBJ,三菱ガス化学社)と15.38kgのMEKのマンガン触媒溶液の中に混ぜ入れることによって微細な分散系を調製した。この分散系を、均一性を保証するように絶えず攪拌した。TiO2を充填した厚さ0.0004インチの延伸膨張PTFE(TiO2の充填率が40%であって膜を最後に圧縮しなかった以外は、モルチマーの米国特許第4985296号の教示にしたがって充填した)の小片を、次いでこの樹脂混合物の中に浸し、取り出し、次いで可撓性のある複合材料を得るため、張力下で165℃にて1分間乾燥した。このようにして得られた部分硬化した接着剤複合材料は、70重量%のTiO2、9重量%のPTFE、及び21重量%の接着剤を含んだ。このプリプレグの数層を銅箔の間に配置し、真空を利用した液圧プレスにより220℃の温度で500psiにて90分間プレスし、次いで圧力下で冷却した。この得られた誘電体は、銅に対する良好な接着性、10.0の誘電率、及び0.008の誘電正接を示した。

例5

7.35kgのSiO2(ADMATECHS SO-E2,Tatsumori LTD)に7.35kgのMEKと73.5gのカップリング剤、即ち、3-グリシジルオキシプロピルトリメトキシシラン(Dynasylan GLYMO(Petrach Systems))を混合することによって微細分散系を調製した。SO−E2は、メーカーによると0.4〜0.6μmの粒子直径、4〜8m2/gの比表面積、0.2〜0.4g/cc(ルース)の嵩密度を有する高い球形性のシリカと説明されている。

この分散系に、メチルエチルケトン(MEK)中のシアン化フェノール樹脂のプリマセットPT−30(ロンザ社)の50重量%溶液の932g、MEK中のRSL1462(シェルレジンズ社(CAS#25068-38-6))の50重量%溶液の896g、MEK中のBC−58(グレートレークス社)の50重量%溶液の380g、MEK中のビスフェノールA(アルドリッチ社)の50%溶液の54g、12.6gのイルガノックス1010(チバガイギー社)、マンガン-2-エチルヘキサノエート(Mn HEX-CEM(OMG社))の0.6%溶液の3.1g、及び2.40kgのMEKを添加した。この分散系を、約1〜3ガロン/分の速度で約20分間にわたってMisonics連続フローセルによる超音波攪拌に供した。このようにして得られた微細分散系を、固形分11.9重量%の全浴濃度(overall bath concentration)までさらに希釈した。

この微細分散系を含浸浴に注ぎ入れた。延伸膨張ポリテトラフルオロエチレンのウェブは、図10の結節とフィブリルの構造と次の特性を有した。

フレージャー数は、評価される材料の空気透過率に関係する。空気透過率は、空気の流れの測定のために約6平方インチの円形領域に設けられたガスケット付固定具にウェブを締めつけることによって測定される。上流側は、乾燥圧縮空気の供給源に直列の流量計に接続された。サンプル固定具の下流側は大気に開放された。テストは、サンプルの上流側に水柱0.5インチの圧力を加え、直列の流量計(流量計に接続されたボール浮遊式ローターメーター)を通過する空気の流量を記録することによって行われる。

ボール破裂強度は、破壊の最大値を測定することによってサンプルの相対的な強度を評価するテストである。ウェブは、2枚のプレートの間に締めつけられながら、直径1インチのボールで攻撃される。Chatillonフォースゲージボール破裂試験を使用した。媒体が測定装置にぴんと張って配置され、破裂プローブのボールに接触するようにウェブを持ち上げることによって圧力が加えられる。破断時の圧力が記録される。

上記のウェブは、均一性を保証するため、ある速度又は約3フィート/分で常時攪拌した含浸浴の中を通した。含浸したウェブは、溶媒の全て又は殆どを除去するため直ちに加熱オーブンを通過させ、ロール上に回収する。

このプリプレグの数層を銅箔の間に配置し、真空を利用した液圧プレスで220℃の温度で90分間にわたって200psiでプレスし、次いで圧力下で冷却した。得られた誘電体は、銅に対する良好な接着性、3.0の誘電率(10GHz)、及び0.0085の誘電正接(10GHz)を示した。

例4と例7で使用した粒子状フィラーの物理的特性を下記に比較する。

例6

溶融ケイ素の蒸気燃焼によって調製したSiO2を主成分とするフィラーと接着剤の含浸された混合物を含む延伸膨張ポリテトラフルオロエチレン(ePTFE)マトリックスを次のようにして調製した。最初に2つの前駆体混合物を調製した。1つは、例5に類似のシラン処理シリカを含むスラリーの形態であり、もう1つは、樹脂と別な成分の触媒添加されていない配合物とした。

−混合物I−

シリカスラリーは、MEK中の例5のSO−E2シリカの50/50配合物であり、本シリカは、シリカの1重量%に等しいシランのコーティングを含んだ。5ガロンの容器に17.5ポンドのMEKと79gのシランを添加し、MEK中のシランの均一な分散を保証するため、2つの成分を混合した。次いで例5のシリカの17.5ポンドを添加した。MEK・シリカ・シラン混合物の2つの5ガロン容器を反応器に加え、その内容物、即ちスラリーを、約1時間にわたって超音波分散器によって再循環させ、存在し得る全てのシリカ凝集物を破壊した。超音波攪拌を終え、内容物を連続的に混合しながら、反応器の内容物を約1時間約80℃に加熱した。次いで反応した混合物を10ガロンの容器に移した。

−混合物II−

所望の樹脂配合物の生成物は、約60%の固形分を含有する触媒添加されていない樹脂配合物を含むMEKを基剤とした混合物(接着剤)であり、その固形分は、正確には、41.2%のPE−30シアン化フェノール樹脂、39.5%のRSL1462エポキシ樹脂、16.7%のBC58難燃剤、1.5%のイルガノックス1010安定剤、及び1%のビスフェノールA共触媒の混合物であり、%はいずれも重量基準である。

10ガロンの容器の中に14.8ポンドのPT−30と15〜20ポンドのMEKを添加し、PT−30を完全に溶かすように激しく攪拌した。次いで6ポンドのBC58を秤量し、MEK/PT−30の溶液に添加し、BC58を溶媒和するために激しく攪拌した。安定剤の244.5gのイルガノックス1010、及びビスフェノールAの163gを添加した。10ガロンの容器を再度秤量し、14.22ポンドのRSL1462を添加した。追加のMEKを添加し、混合物の重量を60ポンドにした。次いで約1〜2時間にわたって、又は固体成分を完全に溶かすのに必要なだけ長くその内容物を激しく攪拌した。

所望の生成物は、シランで処理したシリカ、触媒添加されていない樹脂配合物、及びMEKの混合物であり、その固形分の68重量%がシリカであり、全固形分は混合物の5〜50重量%である。正確な固形分濃度は実験ごとに変わり、一部は含浸される膜によって決まる。触媒レベルは、PT−30とRSL1462の合計に対して10ppmである。

混合物IとIIの固形分を、前駆体の正確性を実証するため、及び生じた全ての溶媒の飛散を補償するために測定した。混合物Iを10ガロンの容器に添加し、12ポンドの固体分、例えば、23.48ポンドの混合物I中の51.5%の固形分を得た。次いで混合物IIをその容器に添加し、5.64ポンドの固体分、例えば、9.46ポンドの混合物II中の59.6%の固形分を得た。マンガン触媒溶液(ミネラルスピリット中の0.6%)の3.45gを混合物Iと混合物IIの混合物に添加し、十分に混合し、高い固形分の混合物を作成した。

その高固形分の混合物に十分なMEKを添加して63ポンドの全重量にすることによって、ePTFEマトリックスを含浸するための固形分28%の混合物の浴混合物を調製した。

次に、ePTFEマトリックスをこの浴混合物で含浸し、誘電体材料を作成した。

例7

26.8gのファーネフブラック(ニュージャージ州のリッジフィールドパークにあるデグッサ社より入手のSpecial Schwarz 100)、及び79gのカップリング剤(Dynaslan GLYMO CAS #2530-83-8、3-グリシジルオキシプロピル-トリメトキシシラン(Petrach Systems))を混合することによって微細分散系を調製した。この分散系を1分間にわたって超音波攪拌に供し、次いで予め超音波攪拌しておいた17.5ポンドのMEK中の17.5ポンドのSiO2(SO−E2)の攪拌中の分散系に添加した。一定の頂部からの混合をしながら最終的な分散系を加熱して1分間の還流を行い、次いでこれを室温まで放冷した。

これとは別に、MEK中のプリマセットPT−30の57.5重量%混合物の3413g、MEK中のRSL1462の76.8重量%混合物の2456g、MEK中のBC58(グレートレークス社)の53.2重量%溶液の1495g、MEK中のビスフェノールA(アルドリッチ社)の23.9重量%溶液の200g、71.5gのイルガノックス1010、ミネラルスピリット中のMn HEX−CEM(OMG社)の0.6重量%溶液の3.21g、及び2.40kgのMEKを加えることによって接着剤ワニスを調製した。

別な容器の中に、上記の分散系の3739g、及び0.0233gのファーネスブラック(ニュージャージ州のリッジフィールドパークにあるデグッサ社より入手のSpecial Schwarz 100)、1328gの上記の接着剤ワニス、及び38.3ポンドのMEKを添加した。この混合物を含浸浴に注ぎ入れ、ある速度又は約3フィート/分でePTFEウェブを含浸浴の中に通した。均一性を保証するため、この分散系を絶えず攪拌した。含浸したウェブは、溶媒の全て又は殆どを除去するために直ちに加熱オーブンを通過させ、ロール上に回収した。

このプリプレグの数層を銅箔の間に配置し、真空を利用した液圧プレスで200℃の温度で90分間にわたって200psiでプレスし加圧下に冷却した。得られた誘電体は、銅に対する良好な接着性を示した。

例8

MEK中のプリマセットPT−30(PMN P-88-1591)の57.5重量%溶液の3413g、MEK中のRSL1462の76.8重量%溶液の2456g、MEK中のBC−58(グレートレークス社)の53.2重量%溶液の1495g、MEK中のビスフェノールA(アルドリッチ社)の23.9重量%溶液の200g、71.5gのイルガノックス1010、ミネラルスピリット中のMn HEX−CEM(OMG社)の0.6重量%溶液の3.21g、及び2.40kgのMEKを加えることによって接着剤ワニスを調製した。

別な容器の中に、上記の接着剤ワニスの1328gを、42.3ポンドのMEK、6.40gのファーネスブラック(ニュージャージ州のリッジフィールドパークにあるデグッサ社より入手のSpecial Schwarz 100)、及び1860.9gのSiO2(SO−E2)と共に加えた。この混合物を含浸浴に注ぎ入れ、ある速度又は約3フィート/分でePTFEウェブを含浸浴の中を通した。均一性を保証するため、この分散系を絶えず攪拌した。含浸したウェブは、溶媒の全て又は殆どを除去するため直ちに加熱オーブンを通過させ、ロール上に回収した。

このプリプレグの数層を銅箔の間に配置し、真空を利用した液圧プレスで220℃の温度で90分間にわたって200psiでプレスし加圧下に冷却した。得られた誘電体は、銅に対する良好な接着性を示した。

本発明を、特定の態様について説明したが、当業者には、以上の説明と添付図面に照らして多くの変化や変更があり得ることは明白である。したがって、本発明は、特許請求の範囲の思想と範囲の中に収まる全ての変更や変化を包含するものである。

Claims (1)

- 同様の材料の第1層と第2層を作成し、

第1層と第2層の一方にパターン形成して電気回路パターンを作成し、それによって、材料部分の分布を有するパターン形成された層を作成し、

第1層と第2層の他方において材料部分の分布を変化させ、パターン形成された層の前記材料部分の分布にマッチさせる、

工程を含む、面内に熱膨張率勾配を設計する方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/745,597 US5888630A (en) | 1996-11-08 | 1996-11-08 | Apparatus and method for unit area composition control to minimize warp in an integrated circuit chip package assembly |

| US08/745,597 | 1996-11-08 | ||

| PCT/US1997/018639 WO1998020556A1 (en) | 1996-11-08 | 1997-10-17 | Method of increasing package reliability by designing in plane cte gradients |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010178017A Division JP5491316B2 (ja) | 1996-11-08 | 2010-08-06 | パッケージの信頼性を高める方法、層状構造及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000505246A JP2000505246A (ja) | 2000-04-25 |

| JP2000505246A5 JP2000505246A5 (ja) | 2005-06-16 |

| JP4615631B2 true JP4615631B2 (ja) | 2011-01-19 |

Family

ID=24997393

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP52141598A Expired - Lifetime JP4615631B2 (ja) | 1996-11-08 | 1997-10-17 | 面内に熱膨張率勾配を設計する方法 |

| JP2010178017A Expired - Lifetime JP5491316B2 (ja) | 1996-11-08 | 2010-08-06 | パッケージの信頼性を高める方法、層状構造及びその製造方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010178017A Expired - Lifetime JP5491316B2 (ja) | 1996-11-08 | 2010-08-06 | パッケージの信頼性を高める方法、層状構造及びその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US5888630A (ja) |

| JP (2) | JP4615631B2 (ja) |

| AU (1) | AU4758497A (ja) |

| WO (1) | WO1998020556A1 (ja) |

Families Citing this family (56)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5778523A (en) * | 1996-11-08 | 1998-07-14 | W. L. Gore & Associates, Inc. | Method for controlling warp of electronic assemblies by use of package stiffener |

| SG82591A1 (en) * | 1998-12-17 | 2001-08-21 | Eriston Technologies Pte Ltd | Bumpless flip chip assembly with solder via |

| US7531417B2 (en) * | 1998-12-21 | 2009-05-12 | Megica Corporation | High performance system-on-chip passive device using post passivation process |