JP4613395B2 - 半導体レーザ素子及びその製造方法 - Google Patents

半導体レーザ素子及びその製造方法 Download PDFInfo

- Publication number

- JP4613395B2 JP4613395B2 JP2000174539A JP2000174539A JP4613395B2 JP 4613395 B2 JP4613395 B2 JP 4613395B2 JP 2000174539 A JP2000174539 A JP 2000174539A JP 2000174539 A JP2000174539 A JP 2000174539A JP 4613395 B2 JP4613395 B2 JP 4613395B2

- Authority

- JP

- Japan

- Prior art keywords

- convex portion

- stripe

- etching

- substrate

- resonator

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【産業上の利用分野】

本発明は、半導体レーザ素子及びその製造方法に係り、特に窒化物半導体層が積層された半導体層に凸部を形成することで、ストライプ形状の導波路領域を有する半導体レーザ素子に関する。

【0002】

【従来の技術】

窒化物半導体を主に用いた半導体素子は、青色発光ダイオード、青色レーザ素子が知られている。特に、レーザ素子に関しては、様々な用途に用いるべく、その特性向上についての研究が多くなされている。

【0003】

窒化物半導体を用いたレーザ素子は、比較的長時間での連続発振が実現されているが、レーザ素子の応用に向けては、まだ多くの問題がある。その中でも、製造プロセスにおいては、発光ダイオードに比べて、複雑な素子構造が必要とされるため、微細加工工程における精度を向上させることが重要となる。また、現在一般的に用いられている窒化物半導体を用いたレーザ素子の構造は、共振器方向に垂直な方向で、屈折率差を設けた屈折率導波型であり、共振器端面には、劈開によるもの、基板に異種物質を用いた場合には、劈開が困難なためエッチングにより形成したもので形成されている。

【0004】

【発明が解決しようとする課題】

窒化物半導体層を主に積層した後、共振器を形成するために通常エッチングによる微細加工を施すが、この時、共振器として積層した半導体層にストライプ形状の凸部を形成して、屈折率導波型のストライプ形状の導波路領域を形成する際に、共振器端面となる凸部端部、及び光の導波に大きく影響を及ぼす凸部側面(ストライプ側面)に、微細加工時の問題が発生する。それは、エッチング、特に一般的に用いられているドライエッチングでは、微細加工することで加工部が凹凸を呈すること、また、比較的狭い領域で複雑な形状に微細加工を施すと、角が丸くなるなどの問題が発生する。

【0005】

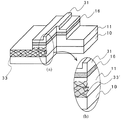

具体的には、図11(b)に示すように、比較的幅の狭いストライプ構造を形成する際に、ストライプ側面は、拡大図(d)に模式的に示すように、エッチングによる加工で、表面に微細な凹凸が形成され、波状の側面が形成されていることがわかる。また、凸部の端部では、角が丸みを帯びており、その端部を拡大した図(c)に模式的に示すように、狭い領域に角が集中するような場所では、図中の矢印に示すような方向に、エッチングがなされ、良好な端面の形成が困難なものとなる。

【0006】

加えて、窒化物半導体を積層した半導体層を、ドライエッチングする際には、一般的にRIE(反応性イオンエッチング)でCl2ガスを用いた方法が用いられている。しかし、このようなドライエッチングでは、表面の凹凸が形成されやすい傾向にあり、特に窒化物半導体においては、その傾向が強く現れる。

【0007】

また、レーザ素子の導波路領域として幅の狭いストライプ構造を有する場合には、特に上述した微細加工時の導波路領域への影響が増大する。すなわち、ストライプ側面の凹凸は、ストライプ幅が狭くなるにつれ、導波路領域に与える悪影響が増すことになり、結果として素子特性の悪化を招く。

【0008】

さらに、上述した共振器端面についても、同様であり、ストライプ幅が狭くなるにつれて、その端面の平坦性が損なわれ、鏡面の共振器反射面を得ることが困難になるばかりでなく、素子端面不良による不良品の発生が多くなる。

【0009】

【課題を解決するための手段】

本発明は、上記課題を解決するためにされたものであり、半導体レーザ素子についてはさらにその信頼性を高める構造とし、半導体レーザ素子の製造方法については、共振器を構成するストライプ形状の凸部側面、及び共振器反射面となる素子端面の形成について、優れた微細加工を実現するものである。

【0010】

すなわち、本発明の半導体レーザ素子は、以下の(1)〜(4)に示す構成とするものである。

【0011】

(1)基板上に窒化物半導体からなる層が複数積層されて、活性層をp型クラッド層とn型クラッド層とで挟み込む構造を含む共振器を有すると共に、共振器端面に挟まれてストライプ形状の導波路領域を有する半導体レーザ素子であって、前記ストライプ形状の導波路領域が、前記半導体層の一部が除去されて形成されたストライプ形状の第1の凸部と、該第1の凸部端部の一方に延在した第2の凸部と、を有すると共に、共振器反射面が、前記第1の凸部端部と、第2の凸部側面のうち第1の凸部に離間した外部側面と、に設けられていることを特徴とする。このように、共振器として第1の凸部と第2の凸部とを有することで、横モードの安定した半導体レーザ素子が得られる。詳しいことは不明であるが、従来のようなストライプ形状の導波路領域と、それに加えて、それよりも幅の広い前記第2の凸部が共振器に含まれることにより、光の導波に変化がもたらされ、これが横モードの安定性に良好に作用しているものと考えられる。

【0012】

(2)前記第1の凸部のストライプ幅が、5μm以下であることを特徴とする。この構成により、第1の凸部により形成されるストライプ形状の導波路領域において、良好な光の閉込めを可能にし、横モードの安定したレーザ素子が、得られる。さらに好ましくは、1μm以上3μm以下の範囲とすることで、さらに横モードの安定したレーザ素子となる。

【0013】

(3)前記第2の凸部に設けられた共振器反射面と、第1の凸部との距離が、5μm以下であることを特徴とする。この構成により、第1の凸部により形成されるストライプ状の導波路領域と、第2の凸部の共振器反射面との間が、発振閾値の急激な上昇を招かない程度の距離におさめられることとなる。すなわち、第1の凸部だけでレーザ素子の導波路領域が構成される場合に比べて、上記第2の凸部を含む場合の方が発振閾値が上昇する傾向にあるが、その上昇は上記距離5μmを超えると、素子特性に深刻な影響を及ぼすものとなる傾向にあるためである。更に好ましくは、第2の凸部の長さを、1μm以上3μm以下とすることで、共振器に第2の凸部を有することによる素子特性変化が、好適に作用する傾向にある。

【0014】

(4)前記第1の凸部上面に接して電極が設けられていると共に、該電極が第1の凸部の端部に達しない長さであることを特徴とする。この構成により、第2の凸部に電極がかからず、第2の凸部による導波路領域における利得に変化がもたらされ、そのことがモード制御に好適に作用し、発振特性に優れるレーザ素子となる。

【0015】

また、本発明の半導体レーザ素子の製造方法は、以下の(5)〜(11)に示す方法である。

【0016】

(5)基板上に、p型クラッド層とn型クラッド層とで活性層を挟む構造の半導体層が積層され、エッチングにより該半導体層の一部を除去することで形成された第1の凸部にストライプ形状の導波路領域を有するレーザ素子の製造方法であって、前記基板上に窒化物半導体からなる層を積層した後、エッチングにより前記ストライプ形状の第1の凸部と、第1の凸部の少なくとも一方の端部に第1の凸部のストライプ幅より広い第2の凸部と、を形成するエッチング工程と、エッチング工程の後、第1の凸部上で第1の凸部のストライプ方向にほぼ垂直な面で基板を分割して、共振器反射面を形成する基板分割工程と、を具備してなることを特徴とする。この製造方法により、従来問題となっていたストライプ状の凸部の形成において、第1の凸部端部に延在して第2の凸部が形成されることにより、微細な構造の第1の凸部端部の損傷を防ぎ、導波路領域が精度良く得られ、さらに基板分割工程により良好な素子端面が得られる。また、第2の凸部が端部の一方にのみ形成された場合であって、エッチングにより他方の第1の凸部端部が損傷を受けても、基板分割工程により、その損傷部を排除して、共振器反射面を形成することができる。すなわち、この製造方法によるレーザ素子は、第2の凸部にエッチングによる素子端面、基板分割工程により形成された第1の凸部端部にそれぞれ良好な反射面を有する共振器を形成されたものとなる。

【0017】

(6)前記エッチング工程において、前記積層した半導体層の一部を除去することで露出した第1の表面上に前記第1の凸部と第2の凸部とを形成した後、該第1の表面より深くエッチングし、前記半導体層中に前記第1の凸部に離間して、電極形成面を設けることを特徴とする。この製造方法により、第1の表面上に形成した第1の凸部が、後に続く電極形成面のためのエッチングにおいても、損傷することなく、良好なストライプ形状、端部、側面を維持でき、優れた導波路領域を有するレーザ素子が得られ、また精度良く第1の凸部が微細加工されていることから、素子信頼性にも優れ、素子ばらつきの少ないレーザ素子が得られる。

【0018】

(7)前記エッチング工程において、第1の凸部のストライプ方向にほぼ垂直で第1の凸部とは離間した外部側面を、前記第2の凸部に形成して共振器反射面とすることを特徴とする。この製造方法により、従来問題となっていた微細な構造を有する第1の凸部端部をエッチングで形成する必要がなく、第1の凸部より幅広な第2の凸部の側面(外部側面)にエッチング端面を形成することで、良好な共振器反射面が形成される。これは、従来微細なストライプ形状の凸部にエッチング端面をけいせいすると、その端面に激しい損傷が観られ、良好な共振器反射面を形成できなかったが、第2の凸部にエッチング端面を形成することで、これを回避できることにある。このことで、基板分割面に比べて生産性に優れるエッチング端面を、微細なストライプ形状の凸部を有するレーザ素子にも利用することが可能となる。

【0019】

(8)前記エッチング工程において、ほぼ矩形状の開口部を設けることで該開口部に挟まれる第1の凸部を形成することを特徴とする。この製造方法により、エッチング工程において、複雑なマスクパターンとならずに、第1の凸部、第2の凸部が形成でき、また、両端部の第2の凸部に挟まれて第1の凸部が形成されるため、精度良く微細加工されたストライプ形状となる。

【0020】

(9)前記エッチング工程において、第1の凸部に離間すると共に、第2の凸部に延在する第3の凸部を形成することを特徴とする。

【0021】

(10)前記エッチング工程において、エッチングにより前記第1の表面上に、少なくとも第1の凸部と、第1の凸部よりストライプ幅の広い第2の凸部とを、それぞれ複数有するストライプ形状の凸部を形成した後、該ストライプ形状の凸部を分断するようにエッチングして、該前記外部側面を第2の凸部に形成することを特徴とする。この製造方法により、第1の凸部形成と同時に、第2の凸部が形成されるため、それより幅の狭い第1の凸部は、特にその端部における微細構造が損傷を受けることなく形成可能で、この後、第2の凸部に共振器反射面を設けることで、生産性に優れたレーザ素子の製造方法となる。

【0022】

【発明の実施の形態】

(半導体レーザ素子)

本発明の半導体レーザ素子として、具体的には、図5〜7に示すように、基板10上に、窒化物半導体からなる層が複数積層され、その積層体に活性層16をp型クラッド層とn型クラッド層と(14,15)で挟み込む構造を有し、共振器として図に示すようにストライプ形状の導波路領域を有している。図に観るように、基板上の共振器として、ストライプ形状の導波路領域を形成する第1の凸部1と、その第1の凸部1に延在する第2の凸部2とを有し、第1の凸部端部、第2の凸部側面(外部側面5)に共振器反射面が設けられた構造である。すなわち、基板上の共振器として、従来の半導体レーザ素子のようにストライプ形状の導波路領域を形成する第1の凸部1に加えて、共振器反射面が設けられた第2の凸部2を有するものである。この時、もう一方の共振器反射面としては、第1の凸部の端部(端面)に設けられる。

【0023】

また、本発明において、窒化物半導体とは、AlxGayIn1-x-y(0≦x≦1,0≦y≦1,0≦x+y≦1)で表され、本発明の半導体レーザ素子は、この窒化物半導体からなる層を基板上に積層したものである。好ましくは、基板上に形成される積層構造として、後述の実施例のように、p型窒化物半導体からなるp型クラッド層、n型窒化物半導体からなるn型クラッド層とで、活性層を挟み込む構造を有すること、より好ましくは、活性層がInを含む窒化物半導体からなる層を有することである。なぜなら、このような積層構造でもって、上述の第1の凸部及び第2の凸部を含む共振器構造のものは、後述の比較例で示すように共振器としてストライプ形状の凸部を有するだけのものに比べて、良好な発振特性が得られ、特にその第2の凸部での光反射率が向上することによる発振閾値が低下し、さらには単一モード発振での安定性が向上する傾向にある。

【0024】

ここで、本明細書において、第1の凸部の長さとは、図2などに観るように、ストライプ形状の第1の凸部のストライプ方向(長手方向)における長さであり、第1の凸部の幅とは、そのストライプ方向に垂直な方向における長さである。また、第2の凸部についても同様に、第2の凸部の長さは、上記第1の凸部のストライプ方向の長さであり、第2の凸部の幅は、そのストライプ方向に垂直な方向の長さである。

(共振器)

本発明の半導体レーザ素子は、基板上に共振器として、上述したように積層した半導体にエッチングなどで微細加工を施して、上記第1の凸部と第2の凸部とを有するものである。この共振器構造としては、例えば図5〜7に示すように、エッチングにより半導体層の一部を除去して、残った第1の凸部、第2の凸部によるリッジ構造であってもよく、第1の凸部、第2の凸部などを形成後再成長させて埋め込むような構造であっても良い。この時、共振器として、主に第1の凸部によるストライプ形状の導波路領域でもって、光の閉込め、モード制御がなされる。

【0025】

具体的には、以下の実施例で説明するように、本発明の半導体レーザ素子は、第1の凸部により屈折率導波型の導波路を形成し、第2の凸部に共振器反射面を、もう一方の共振器反射面が第1の凸部端部に設けられた構造となる。

(第1の凸部)

本発明の半導体レーザ素子において、第1の凸部とは、共振器として第1の凸部と第2の凸部とを有すことから、レーザ素子の共振器長より短いストライプ長さで設けられるものであり、上述したように、主に第1の凸部によりストライプ形状の導波路領域が形成される。

【0026】

また、本発明のレーザ素子において、第1の凸部のストライプ幅としては、5μm未満が好ましく、1μm以上3μm以下の範囲にあることがさらに好ましい。なぜなら、上記範囲内であると、上述したような単一横モードでの安定した発振を実現する屈折率導波型のレーザ素子となるからである。また、この場合には、第1の凸部上面に、図5〜7に示すように、電極を形成するが、この時電極は、第1の凸部だけに設けられるようにすることが好ましい。なぜなら、ストライプ形状の導波路領域を形成する第1の凸部の上部にのみ、すなわち第2の凸部の上部を除いて、電極が形成されることにより、第2の凸部における利得領域に変化が生まれ、このことが第1の凸部による導波路領域での効率的な光の発振を可能にする傾向にあり、発振特性に優れるレーザ素子となる。このため、電極は、第1の凸部の端部に達しない長さ、すなわち第1の凸部の長さより短く設けられることが好ましい。また、第1の凸部において、第2の凸部が設けられていない端部であっても、この電極がそこに達しない長さであることにより、その製造において、基板分割時の衝撃による電極の剥がれ等を防止できるため、好ましい。

【0027】

さらに、本発明のレーザ素子において、第1の凸部端部、第2の凸部の外部側面に設けられた共振器反射面の内、第1の凸部端部をレーザ光の出射側とすることが好ましい。これは、後でも述べられているように、第2の凸部において光は、第1の凸部の幅よりも広い幅で光が導波するため、レーザ光のアスペクト比などの光学特性が悪化し、またそれを制御することも構造的に困難であるため、その特性に関して素子間のばらつきも大きくなる。このため、第1の凸部端部に設けられた共振器反射面をレーザ光の出射側とすることで、第1の凸部によるストライプ状の光導波路での良好な光閉込め、モード制御を維持したまま、高効率で光を出射させることが可能となる。

(第2の凸部)

本発明の半導体レーザ素子において、第2の凸部の長さとしては、5μm以下が好ましい。なぜなら、第2の凸部2の長さが、5μmを超えるとレーザ素子の発振特性が急激に低下する傾向にあるためである。これは第2の凸部2に共振器反射面が設けられることにより、導波路に変化がもたらされ、モード安定性が増す傾向にあるが、第2の凸部があることによる悪影響も生まれ、特に電流―光出力特性におけるスロープ効率の低下が観られ、特に5μmを超えると顕著になることによるものである。更に好ましくは、1μm以上3μm以下の範囲の長さで、第2の凸部が設けられていることにより、上述した素子特性の低下を抑えつつ、共振器として第2の凸部を有することによるモードの安定性の向上が得られる傾向にある。

【0028】

また、本発明のレーザ素子において、第2の凸部は図2〜9に示すように、第1の凸部の端部に延在するように設けられ、第1の凸部端部と第2の凸部側面(共振器反射面を有する外部側面に離間した面)とで接合されている。また、第2の凸部は、第1の凸部の両端部に設けられると、上述した導波路領域の変化が大きくなり、損失が大きくなるためかえって発振特性の低下を招き、またレーザ光出射において、第2の凸部に設けられた共振器反射面が出射面となるため、レーザ光の形状が悪化し、加えて素子のばらつきも大きくなる傾向にあり、好ましくない。

(第3の凸部)

また、本発明の半導体レーザ素子は、以上の共振器を構成する第1の凸部と第2の凸部の他に、共振器の外周を囲むように、第3の凸部が設けられていても良い。この第3の凸部は、後述する半導体レーザ素子の製造方法で説明するように、第1の凸部もしくは第2の凸部を形成する際などに、第1の凸部に離間し、第2の凸部に延在して形成され、レーザ素子の駆動において、共振器を構成する第1の凸部、第2の凸部とは異なり、共振器として機能しない。すなわち、ストライプ形状の導波路領域である第1の凸部とは離間しているため光はほとんど導波しない。加えて、本発明の半導体レーザ素子が、第1の凸部上面と第1の凸部に離間し、第1の凸部からみて第3の凸部より離れた位置の半導体層表面(電極形成面)に電極を有する構造の場合には、リーク電流を防ぎ、素子の信頼性が向上する傾向が観られ、好ましい。

(半導体レーザ素子の製造方法)

次に、本発明の半導体レーザ素子の製造方法について、以下に詳しく説明する。

【0029】

基板上に、窒化物半導体からなる層を積層し、共振器としてこの積層した半導体層をエッチングすることで第1の凸部、第2の凸部を形成し、基板分割時に共振器反射面を形成するものである。以下、各工程ごとに順を追って説明する。

【0030】

本発明の製造方法において、第1の凸部を形成する際に、その端部に第2の凸部が形成される。

【0031】

まず、基板上に積層する半導体としては、実施例で示すように、上述した組成式で表される窒化物半導体を主に用いる。具体的には、その基板上に形成される積層体は、p型クラッド層とn型クラッド層とで活性層を挟む構造を少なくとも有し、好ましくは上述したように各々、p型窒化物半導体からなるp型クラッド層、n型窒化物半導体からなるn型クラッド層とで、Inを含む窒化物半導体を有する活性層を挟み込む構造を有することである。

(エッチング工程)

本発明の製造方法においてエッチング工程とは、各層を積層した後、基板上の半導体層をエッチングによる微細加工を施して、共振器を構成する第1の凸部、第2の凸部を形成する工程のことである。このエッチング工程は、上述した従来のエッチング時の問題を解決するため、ストライプ形状の導波路領域を主に形成する第1の凸部と、それに延在する第2の凸部を形成するわけであるが、その実施形態として様々な方法をとることができる。以下、その具体例を挙げて説明する。

【0032】

具体的にはエッチング工程としては、図1の模式断面図に示すように、基板10上に半導体層11を積層した後、半導体層11表面にエッチングの際にマスクとなる膜12を形成し、さらに所望のパターンのフォトレジスト膜20を形成して(図1(a)))、所望のパターンのマスク12を形成し(図1(b))、このマスク12により開口部6に挟まれた第1の凸部1を半導体層11に設ける(図1(c))。次に、第1の凸部1上に電極を設けるための保護膜13を表面に設け、開口部6の内部に保護膜13が設けられるようにマスク12を用いて不要な保護膜13をリフトオフ法により除去し(図1(d))、開口部6底面(第1の表面)に離間した位置に、電極形成面4を露出させ、第1の凸部上面、電極形成面4にそれぞれ電極40,41を設ける(図1(e))。最後に、基板10上に、複数の素子領域を設けるように、基板表面7が露出するまでエッチングして半導体層11の一部を除去し(図1(f))、この後続いて、各素子領域に分割し、共振器反射面を形成する基板分割工程を経るものである。

【0033】

このエッチング工程における様々な実施形態として、図2の模式的な斜視図に示すように、まず半導体層11に第1の凸部1を挟む開口部6をエッチングにより設けて、次に図2(b)〜(d)に示すように、共振器構造を形成し、切断面AAで基板を切断して第1の凸部1に共振器反射面を形成する。図2(b)では、第1の凸部1、開口部6から離間した位置の半導体層11を一部除去して電極形成面4を露出させ、図に観るように、第1の凸部1に延在した第2の凸部2と、その第2の凸部2間を架橋するように形成された第3の凸部3とで、第1の凸部1の周囲を囲むように、形成されている。図2(c)では、第1の凸部1のストライプ幅方向において開口部6の一部を除去する他は、(b)と同様にして、形成されている。図2(d)では、(c)に比べて一方の第2の凸部2を除去する他は、同様にして形成されている。

【0034】

このように、図2(a)に観るように、まず第1の凸部1を形成した後、図2(b)〜(d)に観るように、第2の凸部2及び共振器反射面を含む外部側面5を形成することで、ストライプ形状の凸部の形成において従来問題となっていた端部付近の形状不良・一部欠損と、ストライプ側面の表面凹凸を効果的に抑制することができ、良好な共振器が形成できる。

【0035】

さらに、その他の実施形態として、図3に模式的な斜視図として示すように、半導体層11の一部をエッチングにより除去して、第1の凸部1と、その第1の凸部1よりストライプ幅の広い第2の凸部2とを有するストライプ形状の凸部を形成する(図3(a))。これに続いて、図3(b)に示すようにそのストライプ形状の凸部に離間した位置の半導体層11の一部を除去して電極形成面4を露出させた後、図中の斜線部22をマスクして基板表面が露出するまでエッチングして第2の凸部2に共振器反射面を含む外部側面を形成してもよく、さらにまた、上記ストライプ形状の凸部を形成した後、図(a)中の斜線部21をマスクしてエッチングにより半導体層11の一部を除去して図(c)に示すように、第2の凸部2の外部側面5と電極形成面4を形成する。これらの方法によっても、上述の方法と同様に、良好な共振器構造の形成が可能である。

【0036】

さらに別の実施形態として、図4に示すように、エッチングにより第1の凸部1を挟む開口部6を設け、第1の凸部1のストライプ方向に、開口部6と第2の凸部2とが交互に設けられ、ストライプに垂直な方向では、第1の凸部1を挟むように開口部6と、更にその外側に第3の凸部とを設ける形態がある。この実施形態では、第2の凸部2に外部側面が形成されず、次の段階でのエッチングにより、マスク領域を図中の22、22´として第2の凸部に共振器反射面となる端面を設ける。

【0037】

ここで、本明細書中で、電極形成面として記載があるものは、これを電極形成に利用することで、基板の同一面側に正・負一対の電極を設ける際に効率よく、すなわちリーク電流などなくウエハに対し密に素子チップが形成でき好ましい。

第1の凸部が形成される表面(第1の表面)よりも深くエッチングし、第1の表面より基板に近い位置に露出された表面である。この露出された表面は、第1の凸部からは離間した位置に形成され、第3の凸部を形成する場合には、第1の凸部を挟むように第1の表面(開口部)を形成し、その外側に第3の凸部を形成し、更にそれよりも外側に電極形成面を形成する。このような電極形成面は、第1の凸部上面と基板上に電極を設け、基板を挟んで電極を対向配置したものである場合において、電極を設けない表面であってもよく、すなわち電極を設けない他は電極形成面と同様な表面となる。

(第1の凸部)

本発明の製造方法において、第1の凸部はストライプ形状に形成され、少なくとも一方の端部には、第2の凸部が形成され、基板分割工程において第1の凸部端面に共振器反射面が形成される。第1の凸部は、図2(a)に示すように、第1の凸部1を形成するために、ほぼ矩形状の開口部6で挟み込むように形成してもよく、図3(a)に示すように開口部底面6´上に第1の凸部1とそれよりストライプ幅の広い第2の凸部をそれぞれ複数有するストライプ形状の凸部を形成してもよい。ここで、第1の凸部のストライプ幅が比較的狭いものであると、エッチングによるストライプ端部の破壊が発生するため、本発明の製造方法における第1の凸部の形成は、その両端部を第1の凸部のストライプ幅より広い第2の凸部で保護するように、形成することで従来の問題を回避でき好ましい。この第1の凸部の幅として、5μm以下となる幅であると第2の凸部を設けることにより良好なストライプ形状の第1の凸部が得られ、さらに上述した1μm以上3μm以下の範囲内にある場合に、従来では上述のストライプ形状の凸部端部に製造上深刻な影響を与えるものであり、この範囲にあるストライプ幅の第1の凸部では、エッチングでの形成時に第2の凸部が端部に形成されることにより、ストライプ形状の凸部端部が破壊されることを防ぐことができる。

【0038】

具体的には、従来は、ストライプ形状の凸部を形成すると、図11(b),(c),(e)に示すようにその端部が、エッチングによりその端部が、優先的にエッチングされ、凸部30の端部は丸みを帯び、更にその端面では半導体層11が余分に除去されたことによる凹部32が形成され、平坦な端面を形成することができなかった。しかし、本発明の製造方法では、第1の凸部よりストライプ幅の広い第2の凸部を形成することで、第1の凸部端部はエッチングによる損傷から守られる。また第2の凸部の側面(外部側面)は、第1の凸部を形成するよりも後に、形成することで共振器反射面となる平坦性に良好な端面を形成できる。これは、エッチング工程において、本発明の製造方法が第1の凸部形成を最初に形成することで、図11に観るような半導体層が凹凸を呈している状態でマスクを設ける場合に比べて、エッチングマスクの精度を最大限のものとし、優れたエッチング精度を実現できることにある。

【0039】

ここで、窒化物半導体をエッチングする方法には、ウエットエッチング、ドライエッチング等の方法があり、平滑な面を形成するには、好ましくはドライエッチングを用いる。ドライエッチングには、例えば反応性イオンエッチング(RIE)、反応性イオンビームエッチング(RIBE)、電子サイクロトロンエッチング(ECR)、イオンビームエッチング等の装置があり、いずれもエッチングガスを適宜選択することにより、窒化物半導体をエッチングしてできる。

(第2の凸部)

本発明の製造方法において、エッチング工程により形成される第2の凸部は、第1の凸部に延在して形成され、具体的には第1の凸部端部に第1の凸部形成時、もしくはそれ以後に形成される。この第2の凸部は、第1の凸部より幅が広く形成され、すなわち第1の凸部端部で外側に広がって第2の凸部が接合されている。この時、第1の凸部と第2の凸部との接合部は、好ましくはほぼ直角を成して接合されることがエッチングマスクの形状の関係から好ましいが、特にこれに限定される直角から少し丸みを帯びていても、

さらにまた、第2の凸部には、第1の凸部とは離間した位置に外部側面がエッチング工程により形成され、この外部側面に共振器反射面となる素子端面とする。この共振器反射面となる外部側面は、好ましくは第1の凸部を形成した後、エッチングにより形成することが好ましい。なぜなら、第1の凸部とは異なる段階で形成することにより、同時に形成する場合に比べて、複雑な形状の微細加工とならないため、上述した微細構造を形成する際の精度低下を防ぎ、幅広な第2の凸部にエッチングによる外部側面を形成することで、平坦なエッチング端面が得られ、これを共振器反射面とすることができる。

【0040】

ここで、外部側面を形成した後の第2の凸部の大きさとしては、上記第1の凸部が幅5μm以下であるとエッチングによる微細加工時の損傷が大きくなることから、第2の凸部の幅として好ましくは5μm以上とすることで、共振器反射面となる外部側面がエッチングによる損傷の発生を低く抑え、より好ましくは10μm以上とすることで、平坦性の良好な外部側面が得られる。この場合むしろ第2の凸部だけを考慮することよりも、エッチング時のマスクパターンの精度を考えると、第1の凸部と第2の凸部とのストライプ幅の差を考慮することが重要であり、この差が大きくなると製造において、マスクパターンの形成が容易であり、歩留まりが向上する。例えば、図2に示すような開口部6を形成するような場合には、上記ストライプ幅の差は、開口部6の幅に当たるため、この差が大きいことは開口部の幅を広くとることができ、そのことはマスクパターンを精度良く形成することを可能とし、歩留まりよくエッチング工程を経ることができる。第1の凸部と第2の凸部とのストライプ幅の差としては、具体的には、少なくとも2μm以上とする事で、エッチング工程において第1の凸部と第2の凸部との接合部、外部側面の形成を歩留まりよく製造でき、素子ばらつきを抑え、より好ましくは10μm以上とすることで、上記接合部、外部側面を精度良く形成し、丸み、表面凹凸などの発生をを低く抑えた第1の凸部、第2の凸部が形成できる。更に好ましくは、50μm以上とすることで、第2の凸部の外部側面、特に共振器反射面として機能する領域でる第1の凸部との接合部に対向する位置において、平坦性に優れるエッチング端面が形成される。

(第3の凸部)

本発明の製造方法において、エッチング工程により形成される第3の凸部は、第2の凸部に延在して形成され、具体的には、第1の凸部を挟む開口部を設けることで、その開口部を囲む第2の凸部及び第3の凸部を形成する。具体的には、図2に示すように、第1の凸部1と開口部6とを設けた後(図2(a))、それを覆う大きさでマスクし、エッチングにより非マスク領域を除去することで、図2(d)に示すように第1の凸部に離間する第3の凸部を形成する。この時、マスク幅(第1の凸部におけるストライプ方向に垂直な方向の幅)をそれよりも狭くすることで、図2(c),(d)に示すように、第3の凸部を形成しない形態をとることもできる。

(第1の表面)

本発明において、第1の表面には、共振器を構成する第1の凸部が設けられ、また開口部を形成する場合には、その開口部底面となる。ここで、ほぼ矩形状の開口部とは、ほぼ正方形であっても良い。

(基板分割)

本発明の製造方法において、第1の凸部、第2の凸部を形成するエッチング工程の後に、基板を分割する基板分割工程を具備する。この基板分割工程は、具体的には、図2(b)〜(d)の分割位置AAで分割するものであり、このとき、図からわかるように、第1の凸部1の端部に設けられた第2の凸部2の外部側面5から共振器長だけ離れた位置でもって、分割するものである。このことにより、分割位置AAで第1の凸部に分割面が形成され、それを共振器反射面とし、もう一方の共振器反射面は外部側面5とし、共振器として第1の凸部1と第2の凸部2とを有するレーザ素子が得られる。

【0041】

上記基板分割工程には、他の形態があり、例えば図9に示すように、エッチング工程で形成した第1の凸部1のほぼ中央部を基板分割位置AAとすることで、形成される分割面の図9のように分割工程により、基板上に配置されたブロック状の素子領域において、それぞれ2つのレーザ素子、及びその分割面が形成される。この形態では、1つの素子領域を通る分割で、レーザ素子のそれぞれの第1の凸部端部に分割面を形成でき、効率よく共振面が形成される反面、分割時の衝撃に弱く、分割面の表面凹凸が多く観られる傾向にある。

【0042】

本発明の基板分割工程において、特に限定されるものでなく従来知られている方法により分割でき、具体的にはスクライバー、ダイサーなどの手段を用いて分割してもよく、またこれらの手段だけで分割が困難な場合には、ブレーキングなど機械的に外力を加えて分割するなどの手段を用いてもよく、またこれらを組み合わせて、基板の性質などにより適宜選択すると良い。この時、分割を助けるために、予め基板を研磨などの手段により薄くしてもよく、その他に溝を形成して、実質上基板を薄くするのと同様な効果が得られるようにしても良い。これらの方法は、基板材料、厚み、等により適宜選択、若しくは組み合わせて、基板を分割する。

【0043】

従来、サファイア基板などの劈開困難な基板を、窒化物半導体の基板として用いた場合には、比較例1における基板分割を説明する図12に示すように、基板11上の半導体層11にその劈開性の影響を受けることとなり、表面に激しい凹凸を呈した分割面33が形成される。これは、窒化物半導体を有する半導体層の劈開面(ほぼGaNの劈開面に一致する)を基準にして基板分割を実施すると、その劈開面でサファイア基板を劈開することが困難であるため、基板10に近い側から半導体層11のある程度の膜厚に至るまで、半導体層の劈開面を取り出すことができない。このように、基板10の裏面(半導体層11が設けられた主面に対向する面)から上記手段で基板を分割すると、基板10に近い側から、最初は半導体層11の劈開面によらず割れ続けることで凹凸のある表面33、ある程度の膜厚のところまで割れることで初めて劈開面でもって分割されるという、過程でもって基板分割がなされる。このため、窒化物半導体と異なる材料よりなり、窒化物半導体を有する半導体層の劈開性に良好に一致しない異種基板、すなわち劈開困難な異種基板を用いた場合には、このような精度の低い基板分割工程となる。

【0044】

【実施例】

[実施例1]

図10は本発明の一実施例に係るレーザ素子の構造を示す模式的な断面図でありストライプ形状の凸部に垂直な面で切断した際の積層構造を示すものである。

以下、この図を基に実施例1について説明する。

【0045】

基板101として、(0001)C面を主面とするサファイア基板を用いた。

この時、オリフラ面はA面であった。窒化物半導体を成長させる基板としては、サファイア(主面がC面、R面、A面)の他、SiC、ZnO、スピネル(MgAl2O4)、GaAs、SiC(6H,4H,3Cを含む)等、窒化物半導体を成長させるために従来知られている、窒化物半導体と異なる材料よりなる異種基板を用いることができる。また、GaNなどの窒化物半導体からなる基板上に直接積層しても良い。

【0046】

初めに、サファイアよりなる基板1をMOVPE反応容器内にセットし、温度を500℃にして、トリメチルガリウム(TMG)、アンモニア(NH3)を用い、GaNよりなるバッファ層(図示せず)を200Å(オングストローム)の膜厚で成長させる。

【0047】

下地層102:バッファ層成長後、温度を1050℃にして、TMG、アンモニアを用い、アンドープGaNよりなる下地層102を4μmの膜厚で成長させる。この層は、素子構造を形成する各層の成長において基板として作用する。このように、異種基板上に、窒化物半導体の素子構造を形成する場合には、低温成長バッファ層、窒化物半導体の基板となる下地層を形成すると良い。

【0048】

次に素子構造として、以下の層を順に積層する。

【0049】

n側コンタクト層103:膜厚4μm、Siを3×1018/cm3ドープしたGaN

クラック防止層104:膜厚0.15μmのIn0.06Ga0.94N(省略してもよい)

n側クラッド層105:総膜厚1.2μmの超格子構造 厚25ÅのアンドープAl0.16Ga0.84Nと、膜厚25Å、Siを1×1019/cm3ドープしたGaNと、を交互に積層する。

【0050】

n側光ガイド層106:膜厚0.2μmのアンドープGaN

活性層107:総膜厚380Åの多重量子井戸構造 膜厚100ÅのSiドープIn0.05Ga0.95Nよりなる障壁層(B)と、膜厚40ÅのアンドープIn0.2Ga0.8Nよりなる井戸層(W)とを、(B)-(W)-(B)-(W)-(B)の順に積層する。

【0051】

p側キャップ層108:膜厚300Å、Mgを1×1020/cm3ドープしたp型Al0.3Ga0.7N

p側光ガイド層109:膜厚0.1μm、Mgを1×1018/cm3ドープしたp型GaN

p側クラッド層110:総膜厚0.6μmの超格子構造 膜厚25ÅのアンドープAl0.16Ga0.84Nと、膜厚25ÅでMgを1×1020/cm3ドープしたp型GaNと、を交互に積層する。

【0052】

p側コンタクト層111:膜厚150Å、Mgを2×1020/cm3ドープしたp型GaN

以上、素子構造を形成した後、ウエハをMOVPE装置から取り出し、エッチング工程として積層した半導体層に第1の凸部、第2の凸部を形成する。このエッチング工程では、図1に示すように、ウエハをPVD装置にセットしてSiO2よりなるマスク12を半導体層11表面に形成し、さらにフォトリソグラフィーによりマスク12を所定のパターン状に形成して(図1(a),(b))、エッチングにより、ストライプ形状の第1の凸部1を挟む開口部6を設ける(図1(c))。この時、第1の凸部1のストライプ幅は、1.8μmとする。

【0053】

続いて、ウエハをPVD装置に移し、図1(d)に示すように、Zr酸化物(主にZrO2)よりなる絶縁膜13をほぼウエハ全面に形成し、ウエハをフッ酸に浸漬し、マスク12を除去するリフトオフ法により、開口部6内面に絶縁膜13を形成する。この絶縁膜13は、第1の凸部1上面に電極を形成する際に、p−n間を絶縁するためであり、加えて第1の凸部1により形成されるストライプ状の導波路領域で良好な横モードの安定を実現することができる。図1(f)に示すように、開口部6内面に絶縁膜13を形成した後、第1の凸部1に離間した位置で、開口部6底面より深くエッチングして半導体層中のn側コンタクト層を露出させる。この時、図2(b),8(a)に示すように、第1の凸部1の両端部に第2の凸部2、およびこの第2の凸部2間に第3の凸部3を形成するように、エッチングし、第2の凸部2の長さ、第3の凸部3の幅をそれぞれ5μmとし、開口部の幅(第1の凸部のストライプ幅方向)をそれぞれ50μmとした。また、このn側コンタクト層の表面4を露出させることにより、図2(b),8(a)に示すように、第2の凸部2に外部側面5も、第1の凸部1に離間し、そのストライプ方向にほぼ垂直となるように、形成する。この表面4(電極形成面)にn電極41を形成し、絶縁膜13を介して第1の凸部1上面にp電極40を形成する(図1(e))。この時、p電極の大きさは、幅100μmで、長さが第1の凸部よりも数μm〜十数μm短く、且つ第1の凸部端部にかからないように形成する。これは、後に続く基板分割工程において、分割位置にかからない長さで第1の凸部上の電極を形成することで、分割時の衝撃から電極を守り、電極を欠けや剥がれ等防止でき、歩留まりよく製造することができるためであり、上述した電極の長さに限定されずに、これを考慮して電極を第1の凸部より短く形成することが好ましい。

【0054】

以上、エッチング工程の後次に、ウエハのほぼ全面に、SiO2とTiO2よりなる誘電体多層膜113を形成し、更にその多層膜113にp電極、n電極表面の一部を露出するための開口部を設け、それら電極に電気的に接続する取り出し電極111,112を、図10に示すように形成する。このことにより、共振器反射面とするエッチング端面側(第2の凸部の外部側面)にミラーが形成され、加えて各取り出し電極は共振器長より短い長さで形成し、後に続く基板分割工程における分割位置に達しない長さとする事で、分割時の衝撃により各取り出し電極の欠け・剥がれ等を回避でき好ましい。第1の凸部上部の電極に電気的に接続する取り出し電極112は、図10に示すように、第1の凸部に隣接する開口部の上部にまで連続して形成することで、確実なワイヤボンディングができ好ましい。

【0055】

最後に、基板10が露出する深さでエッチングする事により、半導体層11をブロック状に分離して、各ブロックから1個のレーザ素子を得るように配置する(図1(f),図8(b))。以上、エッチング工程を経た後に、ウエハを分割する基板分割工程に移るが、それよりも前に基板分割を確実なものとするため、基板を研磨などの方法により薄くしても良い。ここでは、サファイア基板を厚さ約70μmとなるまで、研磨した。このように、基板分割工程より前に、基板を薄くすることで劈開困難な基板を用いた場合であっても、基板分割の精度を高め、良好な基板分割を可能とする。

【0056】

次に基板分割工程として、以下に示す方法でウエハを分割し、レーザ素子を得る。図2(b),8(b)に示すように、ブロック状の半導体層を図中のAA分割面でもって分割する。詳しくは、分割面AAとなるように基板10裏面(半導体層が形成されていない主面)に、スクライバーで溝を設け、ブレーキングして、面AAで分割する。このことにより、第1の凸部1の端部に、切断面が設けられこれを共振器反射面とする。このとき、共振器長、つまり第1の凸部の端部から第2の凸部の外部側面までの長さ、は、300〜500μmとすることが好ましく、また第1の凸部上の電極40は分割位置AAよりも短く形成する。また、面AAはサファイア基板のオリフラ面(サファイアA面)にほぼ一致し、半導体層中の窒化ガリウムの劈開面であるM面にもほぼ一致し、分割面の中にこの窒化ガリウムM面が半導体層の素子構造に取り出されることで、良好な共振器反射面となる。図8(c)に示すようにバー状に分割された基板に、更に、分割面BB、CCで基板を分割し、レーザ素子を得る。

【0057】

得られるレーザ素子にヒートシンクを取り付け、室温でレーザ発振を試みたところ、閾値電流密度2.5kA/cm2、閾値電圧5Vで、波長405nmで連続発振が確認され、室温で1万時間以上の寿命を示すものである。

【0058】

[実施例2]

エッチング工程において、第1の凸部1を挟む開口部6を形成した後(図2(a))、第1の凸部1のストライプ幅方向において、第3の凸部を形成しない幅でマスクを設け、エッチングすることで、図2(c)に示すように、第1の表面6上に第1の凸部と、その両端部に第2の凸部を形成する。これを除いてその他は、実施例1と同様にしてレーザ素子を得る(図7)。第3の凸部を有していないため、実施例1に比べて、開口部に形成する絶縁膜、それを介して形成される電極などの形成において、リーク電流の発生などの危険性が高まり、製造歩留まりはわずかに下がる傾向にあるが、得られるレーザ素子の特性はほぼ同等のものであり、良好な特性のレーザ素子である。

【0059】

[実施例3]

エッチング工程において、開口部6を形成した後、図2(d)に示すように第1の表面6上に、第1の凸部1とその端部の一方にのみ第2の端部を形成する他は、実施例1と同様にしてレーザ素子を得る。この時、基板分割工程において、素子端面の形成には、図中の分割位置AAは、実施例1、2に比べて、第1の凸部1端部から離れた位置となる。これは、第2の凸部2が形成されていない端部では、エッチングによる損傷を回避するために、第1の凸部1の長さを、実施例1、2に比べて長くして、第2の凸部2が設けられていない側の第1の凸部1端部から離れた位置で分割する。得られるレーザ素子の特性は、実施例1、2に比べて、悪化する傾向にあるものの、従来のレーザ素子に比べて、良好な特性のレーザ素子である。

【0060】

[実施例4]

エッチング工程において、得られるレーザ素子の第1の凸部のストライプ長さに対して2倍の長さで第1の凸部1を形成し、図9に示すように、n側コンタクト層を露出させた表面4上に、第1の凸部1、第2の凸部2、第3の凸部3が設けられたブロック状の領域を複数設けられ、更に基板分割工程において、図9(b)に示すように、第1の凸部1のほぼストライプ長さが半分となる位置を、基板分割位置AAとして、基板を分割する。これ以外の作製条件については実施例1と同様であり、図5に模式的に示すようなレーザ素子が得られる。

【0061】

得られるレーザ素子は、実施例1に比べて、分割位置AAにおいて形成され、互いに対向する分割面は、異なるレーザ素子の共振器反射面となることから、ウエハ当たりのチップ数が多くなる。しかし、実施例1と異なり、基板分割時の衝撃が、互いに分割面で合わさったブロック状の素子領域のそれぞれにかかることから、衝撃に対して弱い形状となり、また良好な分割面が得られなかった際に、ブロック状の素子領域から得られるレーザ素子チップが不良品となり、結果として、実施例1に比べてウエハ当たりの良品率が低下する傾向にある。また、分割面の良好なレーザ素子の特性については、実施例1とほぼ同等な発振特性を示す。

【0062】

[実施例5]

エッチング工程において、図3(a)に示すように、第1の表面6´上にストライプ状の凸部をエッチングにより形成し、この凸部が、第1の凸部1と、それよりストライプ幅の広い第2の凸部2とが少なくとも含まれ、第2の凸部2に挟まれる第1の凸部1を複数形成有するものとする。続いて、図中のハッチング領域21に示すように、第1の凸部1とそれを挟む第2の凸部2の一部とで構成される領域21を、マスクして非マスク領域をエッチングして、図3(c)に示すように、n側コンタクト層表面4を露出させ、第2の凸部2に外部側面5を形成する。その他は、実施例1と同様にして、レーザ素子を得る。この時、第1の凸部1のストライプ幅方向における第2の凸部2の長さは、第1の凸部1の幅(1.8μm)より長く、表面4露出時の第1の表面6´の幅200μmよりも短く形成されるものであり、ここでは、150μmとする。

【0063】

得られるレーザ素子は、第2の凸部が、第1の凸部の両端部に十分な幅、長さでもって形成されることから、良好なストライプ状の凸部(第1の凸部)の形成が可能であり、実施例1、2と同程度の特性を有する。

【0064】

[実施例6]

エッチング工程において、図3(a)に示すように、エッチングにより第1の凸部1と第2の凸部2とを複数有する凸部を第1の表面6´上に形成した後、その凸部よりも広い幅で、第1の凸部1のストライプ方向にほぼ平行なストライプ形状のマスクを形成し、この非マスク領域にある半導体層11の一部をエッチングにより除去することで、n側コンタクト層の表面4を露出させ、実施例1と同様に、第1の表面6´と上記凸部側面絶縁膜を形成する(図示せず)。この時、第1の凸部1のストライプ幅は2μmとし、第2の凸部のストライプ幅は、150μmとし、n側コンタクト層表面4上に形成される第1の表面のストライプ幅(第1の凸部1のストライプ方向に垂直な方向における長さ)は200μmとして、実施例5と同様に、実施例1〜4と異なり第2の凸部2より広い第1の表面4を形成する。

【0065】

続いて、その絶縁膜を介してp電極を第1の凸部1上面に接して形成し、ハッチング領域22内の表面4上にn電極を形成する。この時、p電極は実施例1と同様に、第1の凸部1の両端部に設けられた第2の凸部2に達しない長さで形成し、n電極も実施例1と同様に、第1の凸部1のストライプ方向に平行に形成する。次に、図中のハッチング領域22をマスクして、基板10表面が露出する深さでエッチングして、非マスク領域の半導体層を除去する。

【0066】

以上のエッチング工程の後、実施例1と同様にして、レーザ素子チップを得る。得られるレーザ素子は、実施例5と同様に、良好なレーザ素子の製造が可能で、実施例1と同様に、優れた特性のレーザ素子となる。

【0067】

[実施例7]

エッチング工程において、実施例1と同様に、開口部をエッチングにより形成した後、図4に示すように、第1の凸部1をほぼ中央として、設けられた開口部を覆う幅でストライプ形状のマスクを形成し、非マスク領域をn側コンタクト層が露出する深さでエッチングして、半導体層の一部を除去し、図4に示すような形状の半導体層を得る。この時、ストライプ形状のマスクは、開口部の幅が80μm、第3の凸部の幅が5μm、となるストライプ幅で設ける。続くエッチング工程として、図中のハッチング領域22´にマスクを設け、非マスク領域を基板10が露出する深さでエッチングして、図8(b)に示すような基板10表面にブロック状の半導体層領域を配置し、第1の凸部1の両端部に設けられた第2の凸部2に共振器反射面となる外部側面を形成する。最後に、露出させたn側コンタクト層とp側コンタクト層表面にそれぞれn,p電極を設け、基板分割工程として、図中の切断位置AAでウエハを切断して、第1の凸部1の一方の端部に共振器反射面を形成して、レーザ素子を得る。

【0068】

得られるレーザ素子は、実施例1と同様に、優れた特性を有するレーザ素子であり、またその製造においても、同様に、精度良く良好な共振面、ストライプ側面を有するレーザ素子が、得られる。

【0069】

[実施例8]

基板10表面を露出する際のマスクを、図4中のハッチング領域22とする他は、実施例7と同様にしてレーザ素子を得る。この時、第1の凸部1の両端部に設けられた第2の凸部2の内、一方を図に観るように、次に隣接する第1の凸部1に達する長さで、エッチングマスクを形成している。得られるレーザ素子は、実施例7に比べて、第1の凸部間が、離れていることから、基板分割時の衝撃により強く、分割による共振面の凹凸が少なくなる傾向にあり、比較的良好な共振面が形成される。

【0070】

[実施例9]

第1の凸部の幅を2.5μmとする他は、実施例1と同様にしてレーザ素子を得る。

【0071】

得られるレーザ素子は、実施例1とほぼ同等に良好なレーザ素子が得られ、横モードの制御も実施例1に比べ僅かに劣る傾向にあるものの良好なものである。更に、第1の凸部の幅を3μm、5μmと広くしたところ、横モードの制御性が明らかに悪化する傾向にあり、レーザ光のスポット形状の良好なレーザ素子が得られにくい傾向にある。

【0072】

[実施例10]

第2の凸部の幅を2μmとする他は、実施例1と同様にしてレーザ素子を作製する。得られるレーザ素子は、実施例1とほぼ同程度の素子特性を示し、更に凸部の幅を2.5μm、3μmと大きくすると、横モードの制御に劣る傾向にあり、得られるレーザ光のファー・フィールド・パターンが悪化する。さらに3μmより大きくすると、良好なレーザ光を得ることが困難となる。

【0073】

[実施例11]

エッチング工程において、開口部を、その底面がn側クラッド層の膜厚が0.1μmとなる深さまでエッチングする他は、実施例1と同様にして、レーザ素子を得る。得られるレーザ素子は、図6に示すように、第1の凸部に、活性層16が含まれ、実施例1に比べて良好な横モードの閉込めを実現するものである。

【0074】

[比較例1]

実施例1と同様にして、基板上に各層を積層した後、エッチング工程として、以下のようにして、導波路領域を形成するストライプ形状の凸部を形成する。

【0075】

ウエハをPVD装置に移した後、SiO2からなるマスクをフォトリソグラフィー技術によりn側コンタクト層が露出する深さでエッチングした。この時、図11(a)に示すように、露出されたn側コンタクト層表面に、幅約50μmのストライプ形状の凸部が形成され、該凸部に導波路領域となるストライプを形成する。まず、図11(a)に示すように、ウエハのほぼ全面にSiO2よりなるマスク12を設け、さらにマスク12上、にフォトリソグラフィー技術によりフォトレジスト膜20をストライプ形状のパターンで、前記凸部上に設ける。続いて、SiCl4ガスを用いてRIEにより、フォトレジスト膜20の設けられていない領域のマスク12を除去し、前記凸部上に幅約2μmのストライプ形状のマスク12を形成し、非マスク領域をエッチングして、p側クラッド層表面を露出させ、図11(b)に示すように、その表面上にストライプ形状の凸部(リッジストライプ)を形成する。この時、エッチング深さは、p側クラッド層の膜厚が0.1μmとなる位置である。

【0076】

得られたリッジストライプ30を観察したところ、その両端部においてエッチングによる損傷がみられ、図11(b)に模式的に示すように、角が取れ、丸みを帯びた形状を有していた。また、図11(c),(e)に示すように、その端面においては、活性層からストライプ形状の凸部30に至る領域(図中のハッチング領域32)において、大きく損傷を受ける傾向にあり、図中の白抜き矢印方向への浸食が発生しているものと思われる。このような端面を共振器反射面に用いた場合には、レーザ発振が困難なものとなる。更にまた、図11(d)に示すように、凸部30の側面に、凹凸を呈するものもみられた。

【0077】

リッジストライプ30を形成後、さらにPVD装置にウエハを搬送してSiO2のマスク12の上から形成したリッジストライプの露出した表面にかけて、Zr(主としてZrO2)よりなる保護膜を0.5μm厚さで形成し、ウエハをフッ酸に浸漬し、SiO2のマスクをリフトオフ法により除去する。続いて、実施例1と同様に露出したp側コンタクト層、n側コンタクト層表面にそれぞれp,n電極を形成し、図11(b)に示す切断位置CCでウエハを分割して、リッジストライプ30に共振器反射面となる端面を形成した。

【0078】

得られたレーザ素子の中には、上述したリッジストライプの共振器反射面であるエッチング端面が、図11に示すような損傷を有するものがあり、その素子特性は、実施例1に比べると横モードの制御性に劣り、閾値電流も上昇する傾向にあった。

【0079】

【発明の効果】

本発明によれば、ストライプ状の導波路領域として、ストライプ状の凸部を設けるようなレーザ素子構造であっても、従来のレーザ素子に比べて、モードの制御性に優れ、またレーザ光の光学特性にも優れたレーザ素子が得られる。さらに、その製造においては、従来問題となっていた凸部側面及び端部の損傷を改善でき、導波路として良好に機能する導波路領域を、精度良く製造することができる。

【0080】

【図面の簡単な説明】

【図1】本発明の製造方法を説明する模式断面図。

【図2】本発明のレーザ素子を説明する模式図。

【図3】本発明の一実施形態を説明する模式図。

【図4】本発明の一実施形態を説明する模式図。

【図5】本発明の一実施形態を説明する模式図。

【図6】本発明の一実施形態を説明する模式図。

【図7】本発明の一実施形態を説明する模式図。

【図8】本発明の製造方法を説明する模式図。

【図9】本発明の製造方法を説明する模式図。

【図10】本発明の一実施形態の素子構造を説明する断面図。

【図11】従来のレーザ素子を説明する模式図。

【図12】従来のレーザ素子を説明する模式図。

【符号の説明】

1 ・・・・第1の凸部

2 ・・・・第2の凸部

3 ・・・・第3の凸部

4 ・・・・電極形成面

5 ・・・・共振器端面

6 ・・・・開口部底面・第1の表面

7 ・・・・基板表面

8 ・・・・分割面(共振器端面)

10・・・・基板

11・・・・半導体層

12・・・・マスク

13・・・・絶縁膜

14,15・・・・クラッド層

16・・・・活性層

20・・・・フォトレジスト膜

21・・・・マスク領域

22・・・・マスク領域

40・・・・p電極

41・・・・n電極

Claims (13)

- 基板上に窒化物半導体からなる層が複数積層されて、活性層をp型クラッド層とn型クラッド層とで挟み込む構造を有すると共に、ストライプ形状の導波路領域を有する半導体レーザ素子であって、

前記ストライプ形状の導波路領域が、ストライプ形状の第1の凸部と、該第1の凸部の一方の端部に設けられた第1の凸部よりも幅広な第2の凸部と、を有すると共に、共振器反射面が、前記第1の凸部の他方の端部と、第2の凸部側面のうち第1の凸部に離間した外部側面と、に設けられ、前記第1の凸部の他方の端部をレーザの出射側とすることを特徴とする半導体レーザ素子。 - 前記第2の凸部の幅方向の端部から延在し、共振器の外周を囲むように形成される第3の凸部を有する請求項1記載の半導体レーザ素子。

- 前記第1の凸部のストライプ幅が、5μm以下であることを特徴とする請求項1又は2記載の半導体レーザ素子。

- 前記第2の凸部に設けられた共振器反射面と、第1の凸部との距離が、5μm以下であることを特徴とする請求項1乃至3記載の半導体レーザ素子。

- 前記第1の凸部上面に接して電極が設けられていると共に、該電極が第1の凸部の端部に達しない長さであることを特徴とする請求項1乃至4記載の半導体レーザ素子。

- 前記第3の凸部は、前記第1の凸部を挟む開口部を挟むように形成されることを特徴とする請求項2乃至4のいずれか1項に記載の半導体レーザ素子。

- 基板上に、p型クラッド層とn型クラッド層とで活性層を挟む構造の半導体層が積層され、エッチングにより該半導体層の一部を除去することで形成された第1の凸部にストライプ形状の導波路領域を有するレーザ素子の製造方法であって、

前記基板上に窒化物半導体からなる層を積層した後、エッチングにより前記ストライプ形状の第1の凸部と、第1の凸部の少なくとも一方の端部に第1の凸部よりも幅広な第2の凸部を形成するエッチング工程と、エッチング工程の後、第1の凸部上で第1の凸部のストライプ方向にほぼ垂直な面で基板を分割して、出射側の共振器反射面を形成する基板分割工程と、を具備してなることを特徴とする半導体レーザ素子の製造方法。 - 前記エッチング工程において、前記積層した半導体層の一部を除去することで露出した第1の表面上に前記第1の凸部と第2の凸部とを形成した後、該第1の表面より深くエッチングし、前記半導体層中に前記第1の凸部に離間して、電極形成面を設けることを特徴とする請求項7に記載の半導体レーザ素子の製造方法。

- 前記エッチング工程において、第1の凸部のストライプ方向にほぼ垂直で第1の凸部とは離間した外部側面を、前記第2の凸部に形成して共振器反射面とすることを特徴とする請求項7又は8に記載の半導体レーザ素子の製造方法。

- 前記エッチング工程において、ほぼ矩形状の開口部を設けることで該開口部に挟まれる第1の凸部を形成することを特徴とする請求項7乃至9のいずれか1項に記載の半導体レーザ素子の製造方法。

- 前記第2の凸部の幅方向の端部に延在し、前記開口部を挟むように第3の凸部を形成することを特徴とする請求項10に記載の半導体レーザ素子の製造方法。

- 前記エッチング工程において、エッチングにより前記第1の表面上に、少なくとも第1の凸部と、第1の凸部よりストライプ幅の広い第2の凸部とを、それぞれ複数有するストライプ形状の凸部を形成した後、前記第2の凸部を分断するようにエッチングして、前記外部側面を第2の凸部に形成することを特徴とする請求項8乃至11記載のいずれか1項に半導体レーザ素子の製造方法。

- 前記第3の凸部は、共振器の外周を囲むように形成することを特徴とする請求項11又は12に記載の半導体レーザ素子の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000174539A JP4613395B2 (ja) | 2000-06-09 | 2000-06-09 | 半導体レーザ素子及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000174539A JP4613395B2 (ja) | 2000-06-09 | 2000-06-09 | 半導体レーザ素子及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001358404A JP2001358404A (ja) | 2001-12-26 |

| JP2001358404A5 JP2001358404A5 (ja) | 2007-07-26 |

| JP4613395B2 true JP4613395B2 (ja) | 2011-01-19 |

Family

ID=18676560

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000174539A Expired - Fee Related JP4613395B2 (ja) | 2000-06-09 | 2000-06-09 | 半導体レーザ素子及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4613395B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4889930B2 (ja) * | 2004-08-27 | 2012-03-07 | シャープ株式会社 | 窒化物半導体レーザ素子の製造方法 |

| JP2009164234A (ja) * | 2007-12-28 | 2009-07-23 | Rohm Co Ltd | 窒化物半導体レーザ素子 |

| JP2009188273A (ja) | 2008-02-07 | 2009-08-20 | Rohm Co Ltd | ジャンクションダウン型の光半導体素子及び光半導体装置 |

| JP2012083473A (ja) * | 2010-10-08 | 2012-04-26 | Anritsu Corp | 光ゲート素子 |

| JP6409614B2 (ja) | 2015-02-23 | 2018-10-24 | 日亜化学工業株式会社 | 半導体素子の製造方法及び半導体素子 |

| JP6700019B2 (ja) * | 2015-10-20 | 2020-05-27 | スタンレー電気株式会社 | 半導体発光素子 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05327113A (ja) * | 1992-05-20 | 1993-12-10 | Oki Electric Ind Co Ltd | 半導体レーザ素子 |

| JPH09266351A (ja) * | 1996-03-28 | 1997-10-07 | Fuji Photo Film Co Ltd | AlInGaN系半導体発光素子 |

| JPH11340573A (ja) * | 1998-05-28 | 1999-12-10 | Sharp Corp | 窒化ガリウム系半導体レーザ素子 |

-

2000

- 2000-06-09 JP JP2000174539A patent/JP4613395B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001358404A (ja) | 2001-12-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3822976B2 (ja) | 半導体装置およびその製造方法 | |

| KR100763829B1 (ko) | 반도체 레이저 소자 및 그 제조방법 | |

| KR101375433B1 (ko) | 질화물 반도체 레이저 소자의 제조 방법 및 질화물 반도체레이저 소자 | |

| JP4446315B2 (ja) | 窒化物系半導体レーザ素子の製造方法 | |

| JP2005286213A (ja) | 集積型半導体レーザ素子及びその製造方法 | |

| CN111525391B (zh) | 半导体激光元件 | |

| US20090122822A1 (en) | Semiconductor device having trench extending perpendicularly to cleaved plane and manufacturing method of the same | |

| JP2009267377A (ja) | 窒化物系半導体レーザ素子およびその製造方法 | |

| KR101262226B1 (ko) | 반도체 발광 소자의 제조방법 | |

| US7183585B2 (en) | Semiconductor device and a method for the manufacture thereof | |

| US20100054292A1 (en) | Semiconductor laser device and manufacturing method thereof | |

| US8406264B2 (en) | Nitride semiconductor laser element | |

| JP4613395B2 (ja) | 半導体レーザ素子及びその製造方法 | |

| JP2006165407A (ja) | 窒化物半導体レーザ素子 | |

| US20110013659A1 (en) | Semiconductor laser device and method of manufacturing the same | |

| JP2006093682A (ja) | 半導体レーザおよびその製造方法 | |

| JP3199594B2 (ja) | 窒化物半導体レーザ素子の光共振面の形成方法 | |

| JP7336377B2 (ja) | 半導体レーザ素子 | |

| JP2001244560A (ja) | 半導体発光装置の製造方法及び半導体発光装置 | |

| KR101423340B1 (ko) | 질화물 반도체 레이저 소자의 제조 방법 및 질화물 반도체레이저 소자 | |

| JPH10190149A (ja) | 窒化物半導体レーザ素子の製造方法 | |

| JPWO2005088790A1 (ja) | 半導体レーザ素子、およびその製造方法 | |

| JP3849876B2 (ja) | 半導体レーザ素子及びその製造方法 | |

| JP4321295B2 (ja) | 窒化物半導体レーザ素子の製造方法 | |

| JPH07312462A (ja) | 面発光レーザダイオードの製造方法,及び面発光レーザダイオード |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070611 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070611 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100427 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100511 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100709 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100921 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101004 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4613395 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131029 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131029 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |