JP4488872B2 - 位相同期回路及び半導体集積回路装置 - Google Patents

位相同期回路及び半導体集積回路装置 Download PDFInfo

- Publication number

- JP4488872B2 JP4488872B2 JP2004343661A JP2004343661A JP4488872B2 JP 4488872 B2 JP4488872 B2 JP 4488872B2 JP 2004343661 A JP2004343661 A JP 2004343661A JP 2004343661 A JP2004343661 A JP 2004343661A JP 4488872 B2 JP4488872 B2 JP 4488872B2

- Authority

- JP

- Japan

- Prior art keywords

- delay

- clock signal

- phase

- circuit

- time

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/135—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals by the use of time reference signals, e.g. clock signals

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

- Manipulation Of Pulses (AREA)

- Dram (AREA)

Description

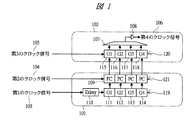

図1は本発明の実施の形態1による位相同期回路の基本的構成を示すブロック図である。

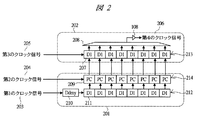

図4は、本発明の実施の形態2による位相同期回路の基本的構成を示すブロック図である。

一方、第3のクロック信号は、まず、この段数を単位遅延時間に乗じた時間だけ遅延される。このように位相一致段までの遅延時間をT1とすると、

T1=Sd・3・D1=3・(Dtgt−(Dc+ Do)/3)=3・Dtgt−(Dc+ Do) 式(2)

さらに、この信号は収束回路408と出力バッファ108を通過するため、総和の遅延時間Dgenは、以下のようになる。

以上の式(3)を見れば分かるように、第3のクロック信号と第4の力クロック信号の間の時間差は、第1のクロック信号と第2のクロック信号の間の時間差の3倍の時間になることが確認できる。

一方、第3のクロック信号は、まず、単位遅延時間D1にこの段数Sdを乗じた時間だけ遅延される。このように位相一致段までの遅延量をT1とすると、

T1=Sd・D1=(Dtgt−2・(Dc+Do))/2=Dtgt/2−(Dc +Do) 式(5)

さらに、この信号は収束回路408と出力バッファ108を通過するため、第3のクロック信号から第4のクロック信号までの総和の遅延時間Dgenは、以下のようになる。

以上の式(6)を見れば分かるように、生成される遅延時間は、第1及び第2のクロック信号間の時間差の1/2倍(すなわち半分)になっていることが確認できる。

図9は、本発明の実施の形態3による位相同期回路の詳細構成を示す回路図である。本実施の形態3による位相同期回路は、前記実施の形態1と前記実施の形態2とを組み合わせたものである。本実施の形態3は、外部からの第1及び第2のクロック信号の時間差と異なる時間差を生成しながら、しかも遅延段数を削減することにより、柔軟性と回路規模の縮小、ひいてはチップ面積、電力を削減することが可能な位相同期回路を提供する。

図11は、本発明の実施の形態4による位相同期回路の詳細構成を示す回路図である。本実施の形態4による位相同期回路は、前記実施の形態2における生成回路を複数個設けたものである。図11に示す位相同期回路はその一例であり、2組の第3のクロック信号105a,105bが存在し、それぞれの入力が遅延されて2組の第4のクロック信号106a,106bが出力されるものである。

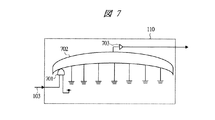

図14は、前記実施の形態1〜4による位相同期回路の応用例の1つとして、DDR−SDRAM(Double Data Rate−SDRAM)1401とLSI(Large Scale Integrated circuit)1402との接続関係を示すブロック図である。

図16は、前記実施の形態1による位相同期回路において、複数の遅延段における遅延素子の遅延時間を相違させる方法についての一例を示す図である。前記図5に示した位相同期回路の例では、インバータ遅延の従属接続数を変化させることで、単位遅延時間が異なる遅延素子を構成していた。しかし、同一論理の同じゲートの従属接続数を変化させる以外にも、ゲートの種類を複数の遅延素子のそれぞれで変化させるという方法(ある遅延素子ではインバータゲートを用い、他の遅延列では複数入力のNANDゲートを用いるといったような方法)もあり得る。

図18は、本発明の実施の形態7による位相同期回路の構成を示す回路図である。本実施の形態7による位相同期回路は、前記実施の形態1(図5)と前記実施の形態2を組み合わせた上で、第1及び第2のクロック信号と第3のクロック信号とが遅延列の配置方向に対して、逆方向に進行する一例を示したものである。ここでは、計測遅延列と生成遅延列のそれぞれの複数の遅延素子の遅延時間を変えるために、各遅延列内部の遅延素子の従属接続数を変えている。例えば、図18では、計測遅延列において、遅延段501内の遅延素子は1段のインバータ遅延503で構成し、遅延段502内の遅延素子は2段のインバータ遅延504,505で構成している。また、生成遅延列において、遅延段1801内の遅延素子は1段のANDゲート1803で構成し、遅延段1802内の遅延素子は2段のANDゲート1803で構成している。また、計測遅延列と生成遅延列との遅延素子の遅延時間における一定の比率を実現するために、論理ゲートの種類(インバータ遅延とORゲート)を変えた構成となっている。

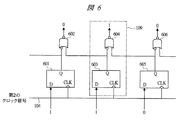

図19(a)は本発明の実施の形態8において、周波数2倍化回路の構成を示す回路図、図19(b)は、その動作を示すタイミングチャート、図19(c)は2のn乗倍化回路の構成を示すブロック図である。なお、nは自然数である。

102,202,402,514,910,1110 遅延生成回路

103,203 第1のクロック信号

104,204 第2のクロック信号

105,105a,105b,205 第3のクロック信号

106,106a,106b,206 第4のクロック信号

107,208,408 収束回路

108,703 出力バッファ

109,209 位相比較器

110,210,410,1111 固定遅延素子

111〜118,501,502,506,507,901,902,905,906,1601,1603,1605,1607,1801,1802 遅延段

119,212,419,911 計測遅延列(第1の遅延列)

120,213,420,912 生成遅延列(第2の遅延列)

121,214,421 位相比較器列

207,211,311,312,313,314,407,411,903,904,907,908,1107 遅延素子

503〜505,508〜510,1602,1604,1606,1608 インバータ遅延

511,701,1803 ANDゲート

512,702 多入力OR回路

601,603,605,1405 フリップフロップ

602,604,606 ゲート

1301 スイッチ

1302 セレクタ

1303 選択条件メモリ

1401,1504 DDR−SDRAM

1402 LSI

1403 メモリインタフェース

1404,1507 位相同期回路

1500,2000 システム

1501 第1のプロセッサ

1502 第2のプロセッサ

1503 SDR−SDRAM

1505,2001 クロックモジュール

1506,2002 クロック発生回路(CPG)

1701,1702 補間回路

1901,2003,2101 入力クロック信号

1902 出力クロック信号

1903,2103 位相変換回路

1904,1912,2102,2104,2112 クロック信号

1905,2006,2008 生成出力クロック信号

1906,2107 排他的ORゲート

1913 周波数2倍化回路

2004 周波数2のn乗倍化回路

2005 第1のプロセッサ

2007 第2のプロセッサ

2105 第1の生成出力クロック信号

2106 第2の生成出力クロック信号

2113 周波数3倍化回路

Claims (13)

- 第1のクロック信号と第2のクロック信号との遷移時間差に基づいて、第3のクロック信号の遷移時間を遅延させて第4のクロック信号を生成する位相同期回路であって、

遅延時間の異なる複数の遅延素子を含み、前記第1のクロック信号が入力される第1の遅延列と、

前記第1の遅延列に対応して複数の位相比較器を含み、前記第1の遅延列からの信号及び前記第2のクロック信号が入力され、前記第1のクロック信号と前記第2のクロック信号との遷移時間差を計測する位相比較器列と、

前記第1の遅延列に対応して遅延時間の異なる複数の遅延素子を含み、前記位相比較器列からの信号及び前記第3のクロック信号が入力される第2の遅延列と、を有し、

前記第1の遅延列及び前記第2の遅延列の前記複数の遅延素子のそれぞれの遅延時間は固定であることを特徴とする位相同期回路。 - 請求項1記載の位相同期回路において、

前記第1の遅延列は、前記第1のクロック信号が早く到達する初段側の遅延素子の遅延時間が小さく、前記第1のクロック信号が遅く到達する後段側の遅延素子の遅延時間が大きいことを特徴とする位相同期回路。 - 第1のクロック信号と第2のクロック信号との遷移時間差に基づいて、第3のクロック信号の遷移時間を遅延させて第4のクロック信号を生成する位相同期回路であって、

複数の遅延素子を含み、前記第1のクロック信号が入力される第1の遅延列と、

前記第1の遅延列に対応して複数の位相比較器を含み、前記第1の遅延列からの信号及び前記第2のクロック信号が入力され、前記第1のクロック信号と前記第2のクロック信号との遷移時間差を計測する位相比較器列と、

前記第1の遅延列に対応して複数の遅延素子を含み、前記位相比較器列からの信号及び前記第3のクロック信号が入力される第2の遅延列と、を有し、

前記第1の遅延列に含まれる遅延素子の遅延時間と前記第2の遅延列に含まれる遅延素子の遅延時間との比率はそれぞれ一定であることを特徴とする位相同期回路。 - 請求項3記載の位相同期回路において、

前記遅延素子の遅延時間の前記比率の値は、1以外であることを特徴とする位相同期回路。 - 第1のクロック信号と第2のクロック信号との遷移時間差に基づいて、第3のクロック信号の遷移時間を遅延させて第4のクロック信号を生成する位相同期回路であって、

遅延時間の異なる複数の遅延素子を含み、前記第1のクロック信号が入力される第1の遅延列と、

前記第1の遅延列に対応して複数の位相比較器を含み、前記第1の遅延列からの信号及び前記第2のクロック信号が入力され、前記第1のクロック信号と前記第2のクロック信号との遷移時間差を計測する位相比較器列と、

前記第1の遅延列に対応して遅延時間の異なる複数の遅延素子を含み、前記位相比較器列からの信号及び前記第3のクロック信号が入力される第2の遅延列と、を有し、

前記第1の遅延列及び前記第2の遅延列の前記複数の遅延素子のそれぞれの遅延時間は固定であり、前記第1の遅延列に含まれる遅延素子の遅延時間と前記第2の遅延列に含まれる遅延素子の遅延時間との比率はそれぞれ一定であることを特徴とする位相同期回路。 - 請求項5記載の位相同期回路において、

前記第1の遅延列は、前記第1のクロック信号が早く到達する初段側の遅延素子の遅延時間が小さく、前記第1のクロック信号が遅く到達する後段側の遅延素子の遅延時間が大きく、

前記遅延素子の遅延時間の前記比率の値は、1以外であることを特徴とする位相同期回路。 - 請求項3記載の位相同期回路において、

位相調整用の固定遅延素子をさらに有し、

前記第1の遅延列に含まれる遅延素子の遅延時間と前記第2の遅延列に含まれる遅延素子の遅延時間との比率と、前記固定遅延素子の遅延時間と、前記第3のクロック信号が入力されてから前記第4のクロック信号が出力されるまでの遅延時間から前記第2の遅延列における遅延時間を除いた時間との比率は、同じであることを特徴とする位相同期回路。 - 請求項1記載の位相同期回路において、

前記第1のクロック信号が早く到達する初段側の遅延素子と、前記第1のクロック信号が遅く到達する後段側の遅延素子とは、速度性能が異なるデバイスを用いた論理的に同一なゲートにより構成されていることを特徴とする位相同期回路。 - 請求項3記載の位相同期回路において、

前記第1の遅延列の1つに対し、前記第2の遅延列を複数系統有することを特徴とする位相同期回路。 - 同期する位相関係が異なる複数の同期型メモリに接続することが可能である半導体集積回路装置であって、

請求項9記載の位相同期回路と、

接続される前記同期型メモリの種類により複数ある前記第4のクロック信号系統のいずれかを利用する機能と、を有することを特徴とする半導体集積回路装置。 - 同期する位相関係が異なる複数の同期型メモリのうち1つを接続することが可能である半導体集積回路装置であって、

請求項9記載の位相同期回路と、

接続される前記同期型メモリの情報が記憶される選択条件メモリと、

前記選択条件メモリ内の情報に基づいて、複数ある前記第4のクロック信号系統のいずれか1つを選択して出力する選択回路と、を有することを特徴とする半導体集積回路装置。 - 同期する位相関係が異なる複数のマイクロプロセッサに接続することが可能である半導体集積回路装置であって、

請求項9記載の位相同期回路と、

接続される前記マイクロプロセッサの種類により複数ある前記第4のクロック信号系統のいずれかを利用する機能と、を有することを特徴とする半導体集積回路装置。 - 請求項3記載の位相同期回路と、

位相変換回路と、

排他的OR回路とを有し、

前記第1のクロック信号と前記第3のクロック信号は共通であり、前記位相変換回路は前記第1のクロック信号を入力とし前記第2のクロック信号を出力とし、前記排他的OR回路は前記第1のクロック信号及び前記第4のクロック信号を入力としていることを特徴とする半導体集積回路装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004343661A JP4488872B2 (ja) | 2004-11-29 | 2004-11-29 | 位相同期回路及び半導体集積回路装置 |

| US11/288,176 US7253670B2 (en) | 2004-11-29 | 2005-11-29 | Phase synchronization circuit and semiconductor integrated circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004343661A JP4488872B2 (ja) | 2004-11-29 | 2004-11-29 | 位相同期回路及び半導体集積回路装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006157357A JP2006157357A (ja) | 2006-06-15 |

| JP4488872B2 true JP4488872B2 (ja) | 2010-06-23 |

Family

ID=36566795

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004343661A Expired - Fee Related JP4488872B2 (ja) | 2004-11-29 | 2004-11-29 | 位相同期回路及び半導体集積回路装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7253670B2 (ja) |

| JP (1) | JP4488872B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7287235B1 (en) * | 2004-08-06 | 2007-10-23 | Calypto Design Systems, Inc. | Method of simplifying a circuit for equivalence checking |

| JP4397933B2 (ja) * | 2004-08-19 | 2010-01-13 | 株式会社ルネサステクノロジ | 位相同期回路 |

| DE102005011894B4 (de) * | 2005-03-15 | 2010-11-25 | Qimonda Ag | Schaltungsanordnung zum Erzeugen eines Synchronisiersignals |

| US7564284B2 (en) * | 2007-03-26 | 2009-07-21 | Infineon Technologies Ag | Time delay circuit and time to digital converter |

| JP2008251070A (ja) * | 2007-03-29 | 2008-10-16 | Hitachi Ltd | 半導体記憶装置 |

| US8243555B2 (en) * | 2008-08-07 | 2012-08-14 | Infineon Technologies Ag | Apparatus and system with a time delay path and method for propagating a timing event |

| DE102009030039A1 (de) * | 2009-06-23 | 2010-12-30 | Rohde & Schwarz Gmbh & Co. Kg | Vorrichtung zum Erzeugen einer vorgegebenen Phasenverschiebung |

| US8130016B2 (en) * | 2009-08-27 | 2012-03-06 | Altera Corporation | Techniques for providing reduced duty cycle distortion |

| US7893739B1 (en) * | 2009-08-27 | 2011-02-22 | Altera Corporation | Techniques for providing multiple delay paths in a delay circuit |

| US20140218009A1 (en) * | 2011-08-29 | 2014-08-07 | Asahi Kasei Microdevices Corporation | Device for measuring a duration of a level of an electrical signal |

| JP2013070281A (ja) * | 2011-09-22 | 2013-04-18 | Toshiba Corp | Dll回路、逓倍回路、及び半導体記憶装置 |

| TWI490515B (zh) * | 2013-12-20 | 2015-07-01 | Chroma Ate Inc | 自動測試設備以及時脈同步方法 |

| CN118743110A (zh) * | 2022-02-28 | 2024-10-01 | 华为技术有限公司 | 一种相控阵装置、通信设备及控制方法 |

| CN115940896B (zh) * | 2022-06-10 | 2024-04-30 | 上海星思半导体有限责任公司 | 一种数字时钟电路 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4814879A (en) * | 1987-08-07 | 1989-03-21 | Rca Licensing Corporation | Signal phase alignment circuitry |

| JPH0836437A (ja) * | 1994-07-26 | 1996-02-06 | Hitachi Ltd | 位相同期回路 |

| JP3672056B2 (ja) * | 1995-08-18 | 2005-07-13 | 松下電器産業株式会社 | タイミング信号発生回路 |

| US5755955A (en) * | 1995-12-21 | 1998-05-26 | Petro-Canada | Hydrocracking of heavy hydrocarbon oils with conversion facilitated by control of polar aromatics |

| KR100197563B1 (ko) * | 1995-12-27 | 1999-06-15 | 윤종용 | 동기 지연라인을 이용한 디지탈 지연 동기루프 회로 |

| JPH1013395A (ja) * | 1996-06-25 | 1998-01-16 | Toshiba Corp | 位相同期回路 |

| KR100224690B1 (ko) * | 1997-02-05 | 1999-10-15 | 윤종용 | 위상동기 지연회로 |

| KR100260556B1 (ko) * | 1997-08-22 | 2000-07-01 | 윤종용 | 내부 클럭 발생회로 |

| KR100527402B1 (ko) * | 2000-05-31 | 2005-11-15 | 주식회사 하이닉스반도체 | 디디알 동기식메모리의 지연고정루프 장치 |

| JP3813435B2 (ja) | 2000-11-07 | 2006-08-23 | 株式会社東芝 | 同期遅延制御回路 |

| US6617894B2 (en) * | 2001-05-14 | 2003-09-09 | Samsung Electronics Co., Ltd. | Circuits and methods for generating internal clock signal of intermediate phase relative to external clock |

| KR100414215B1 (ko) * | 2002-01-03 | 2004-01-07 | 삼성전자주식회사 | 조절 가능한 동기 범위를 갖는 동기 미러 지연 회로 |

| KR100558554B1 (ko) * | 2004-01-07 | 2006-03-10 | 삼성전자주식회사 | 내부 클럭 발생 장치 |

-

2004

- 2004-11-29 JP JP2004343661A patent/JP4488872B2/ja not_active Expired - Fee Related

-

2005

- 2005-11-29 US US11/288,176 patent/US7253670B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20060114040A1 (en) | 2006-06-01 |

| JP2006157357A (ja) | 2006-06-15 |

| US7253670B2 (en) | 2007-08-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100256004B1 (ko) | 반도체 기억 장치 시스템 및 반도체 기억 장치 | |

| US6774690B2 (en) | Digital dual-loop DLL design using coarse and fine loops | |

| TWI299943B (en) | Delay locked loop in semiconductor memory device and its clock locking method | |

| JP5160856B2 (ja) | Ddrメモリコントローラ及び半導体装置 | |

| CN1716783B (zh) | 寄存器控制的延迟锁定回路及其控制方法 | |

| US8115529B2 (en) | Device and control method of device | |

| JP4488872B2 (ja) | 位相同期回路及び半導体集積回路装置 | |

| US7659759B2 (en) | Phase synchronous circuit | |

| CN100583640C (zh) | 半导体集成电路 | |

| US7710171B2 (en) | Delayed locked loop circuit | |

| JP2002124873A (ja) | 半導体装置 | |

| JP2010213308A (ja) | 遅延固定ループ回路の遅延ライン部及び遅延固定ループ回路におけるクロック信号の遅延固定方法 | |

| KR20040103207A (ko) | 전력 소모를 줄인 레지스터 제어 지연고정루프 | |

| JP2002025259A (ja) | リング遅延とカウンタを利用したレジスタ制御遅延固定ループ | |

| US7292500B2 (en) | Reducing read data strobe latency in a memory system | |

| JPH10336008A (ja) | クロック発生回路及び半導体装置 | |

| US6373307B1 (en) | Semiconductor integrated circuit | |

| US20040000934A1 (en) | Clock divider and method for dividing clock signal in DLL circuit | |

| JP2022505662A (ja) | 非同期asic | |

| US7671649B2 (en) | Apparatus and method for generating multi-phase clocks | |

| US20080001638A1 (en) | Clock generator circuit, method of clock generating, and data output circuit using the clock generating circuit and method | |

| US8283962B2 (en) | Semiconductor device and operation method thereof for generating phase clock signals | |

| US7227396B2 (en) | Clock signal input/output device for correcting clock signals | |

| KR100410632B1 (ko) | 소비전류와 레이아웃 면적의 감소를 위한 지연고정루프 | |

| KR100415544B1 (ko) | 양방향 지연을 이용한 디엘엘 회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070507 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100223 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100316 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100330 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130409 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4488872 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A072 | Dismissal of procedure [no reply to invitation to correct request for examination] |

Free format text: JAPANESE INTERMEDIATE CODE: A072 Effective date: 20100921 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130409 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130409 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140409 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |