JP4397248B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP4397248B2 JP4397248B2 JP2004044788A JP2004044788A JP4397248B2 JP 4397248 B2 JP4397248 B2 JP 4397248B2 JP 2004044788 A JP2004044788 A JP 2004044788A JP 2004044788 A JP2004044788 A JP 2004044788A JP 4397248 B2 JP4397248 B2 JP 4397248B2

- Authority

- JP

- Japan

- Prior art keywords

- formation region

- nitride film

- film

- mark

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W46/00—Marks applied to devices, e.g. for alignment or identification

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W46/00—Marks applied to devices, e.g. for alignment or identification

- H10W46/501—Marks applied to devices, e.g. for alignment or identification for use before dicing

Landscapes

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Element Separation (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

上述の半導体装置の製造方法において、さらに、凹部を基準位置として、素子形成領域に回路素子を形成することが好ましい。

また、上述の半導体装置の製造方法において、第3工程が、素子形成領域及びマーク形成領域の両領域の全面に第1サブシリコン窒化膜を形成する第1サブ工程と、マーク形成領域以外に存在する第1サブシリコン窒化膜を除去する第2サブ工程と、素子形成領域及びマーク形成領域の両領域の全面に第2サブシリコン窒化膜を形成することにより、マーク形成領域に、第1及び第2サブシリコン窒化膜の積層体としての第2の窒化膜を形成し、及び素子形成領域に、第2サブシリコン窒化膜からなる第1の窒化膜を形成する第3サブ工程とを含むことが好ましい。

また、上述の半導体装置の製造方法において、第6工程が、素子形成領域の第1の窒化膜及びマーク形成領域に形成された凹部の底面を構成する第2の窒化膜を除去する第1サブ工程と、素子形成領域の酸化膜及び凹部の底面を構成する第2の窒化膜の下に位置する酸化膜を除去する第2サブ工程とを含むことが好ましい。

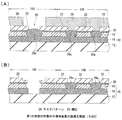

図1から図4を参照して、この発明の第1の実施の形態につき説明する。

膜としてシリコン窒化膜22を同時に形成する。シリコン窒化膜22を、例えば、ジクロ

ロシラン(SiH 2 Cl 2 )ガスを主成分とするLP−CVD(Low Pressur

e−Chemical Vapor Deposition)法を用いて、60〜150

nmの膜厚で形成する。ここでのシリコン窒化膜22の膜厚は、後工程で素子形成領域1

00及びマーク形成領域150の第2のシリコン層16に酸化部を選択酸化によって形成

する際の酸化阻止用マスクとしてはもとより、凹部を形成する際の耐エッチングマスクと

して機能する程度の膜厚とする(詳細後述)。

図5(A)から図9(C)を参照して、この発明の第2の実施の形態につき説明する。

12:第1のシリコン層(半導体支持基板)

14:シリコン酸化膜(絶縁膜)

16:第2のシリコン層(半導体層)

18、54:凹部(マーク)

18a、54a:凹部のエッジ部

20、50:シリコン酸化膜(パッド酸化膜(酸化膜))

22、52、69:シリコン窒化膜(窒化膜)

24、28、39、56、62、76:マスクパターン

23a、23b、25a、25b、27a、27b、29、65a、65b、66、71:開口

26a、68:酸化部(素子分離部)

26b:酸化部

30、72:シリコン酸化膜(ゲート酸化膜)

32:ポリシリコン膜

34:タングステンシリサイド膜

36、69:シリコン窒化膜

38、73:レジスト層

40、74:積層体

42、75:ゲート電極

58:第1のシリコン窒化膜(窒化膜)

60:第2のシリコン窒化膜(窒化膜)

67:凹部

100:素子形成領域

150:マーク形成領域

161:第2のシリコン層のうち開口25aと対向する部分

162:第2のシリコン層のうち開口25bと対向する部分

163:第2のシリコン層のうち開口66と対向する部分

Claims (4)

- 半導体支持基板、該半導体支持基板上に形成された絶縁膜、及び該絶縁膜上に形成された半導体層を具え、素子形成領域と該素子形成領域に隣接するマーク形成領域とを有する基板を用意する第1工程と、

前記素子形成領域及び前記マーク形成領域の前記半導体層上に酸化膜を形成する第2工程と、

前記素子形成領域の前記酸化膜上に第1の膜厚を有する第1の窒化膜を形成するとともに、前記マーク形成領域の前記酸化膜上に該第1の膜厚よりも厚い第2の膜厚を有する第2の窒化膜を形成する第3工程と、

前記素子形成領域の前記第1の窒化膜に前記酸化膜を露出させる開口を形成するとともに、前記マーク形成領域の前記第2の窒化膜に前記酸化膜を露出させないように凹部を形成する第4工程と、

前記素子形成領域の前記開口の下に位置する前記半導体層を酸化する第5工程と、

前記素子形成領域の前記第1の窒化膜及び前記酸化膜を除去するとともに、前記マーク形成領域に形成された前記凹部の底面を構成する前記第2の窒化膜及び該底面を構成する前記第2の窒化膜の下に位置する前記酸化膜を除去する第6工程と

を含むことを特徴とする半導体装置の製造方法。 - 請求項1に記載の半導体装置の製造方法において、

さらに、前記凹部を基準位置として、前記素子形成領域に回路素子を形成することを特徴とする半導体装置の製造方法。 - 前記第3工程が、

前記素子形成領域及び前記マーク形成領域の両領域の全面に第1サブシリコン窒化膜を形成する第1サブ工程と、

前記マーク形成領域以外に存在する前記第1サブシリコン窒化膜を除去する第2サブ工程と、

前記素子形成領域及び前記マーク形成領域の両領域の全面に第2サブシリコン窒化膜を形成することにより、前記マーク形成領域に、前記第1及び第2サブシリコン窒化膜の積層体としての前記第2の窒化膜を形成し、及び前記素子形成領域に、前記第2サブシリコン窒化膜からなる前記第1の窒化膜を形成する第3サブ工程と

を含むことを特徴とする請求項1又は2に記載の半導体装置の製造方法。 - 前記第6工程が、

前記素子形成領域の前記第1の窒化膜及び前記マーク形成領域に形成された前記凹部の底面を構成する前記第2の窒化膜を除去する第1サブ工程と、

前記素子形成領域の前記酸化膜及び前記凹部の底面を構成する前記第2の窒化膜の下に位置する前記酸化膜を除去する第2サブ工程と

を含むことを特徴とする請求項1〜3の何れか一項に記載の半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004044788A JP4397248B2 (ja) | 2004-02-20 | 2004-02-20 | 半導体装置及びその製造方法 |

| US11/048,891 US7332405B2 (en) | 2004-02-20 | 2005-02-03 | Method of forming alignment marks for semiconductor device fabrication |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004044788A JP4397248B2 (ja) | 2004-02-20 | 2004-02-20 | 半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005236118A JP2005236118A (ja) | 2005-09-02 |

| JP2005236118A5 JP2005236118A5 (ja) | 2006-09-28 |

| JP4397248B2 true JP4397248B2 (ja) | 2010-01-13 |

Family

ID=34858080

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004044788A Expired - Fee Related JP4397248B2 (ja) | 2004-02-20 | 2004-02-20 | 半導体装置及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7332405B2 (ja) |

| JP (1) | JP4397248B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7435659B2 (en) * | 2005-02-28 | 2008-10-14 | Texas Instruments Incorporated | Method for manufacturing a semiconductor device having an alignment feature formed using an N-type dopant and a wet oxidation process |

| JP4794377B2 (ja) * | 2006-07-06 | 2011-10-19 | Okiセミコンダクタ株式会社 | 半導体装置の製造方法 |

| US7723178B2 (en) * | 2008-07-18 | 2010-05-25 | International Business Machines Corporation | Shallow and deep trench isolation structures in semiconductor integrated circuits |

| US9000525B2 (en) * | 2010-05-19 | 2015-04-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | Structure and method for alignment marks |

| JP2014216377A (ja) * | 2013-04-23 | 2014-11-17 | イビデン株式会社 | 電子部品とその製造方法及び多層プリント配線板の製造方法 |

| US9178066B2 (en) * | 2013-08-30 | 2015-11-03 | Taiwan Semiconductor Manufacturing Company Limited | Methods for forming a semiconductor arrangement with structures having different heights |

| US12347787B2 (en) * | 2022-06-13 | 2025-07-01 | Yangtze Memory Technologies Co., Ltd. | Three dimensional (3D) memory device and fabrication method |

| CN119381339B (zh) * | 2023-07-20 | 2025-09-26 | 长鑫科技集团股份有限公司 | 半导体结构及其形成方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3174786B2 (ja) | 1991-05-31 | 2001-06-11 | 富士通株式会社 | 半導体装置の製造方法 |

| JP3447231B2 (ja) | 1998-11-20 | 2003-09-16 | セイコーインスツルメンツ株式会社 | 半導体集積回路の製造方法 |

| WO2001067509A1 (fr) * | 2000-03-09 | 2001-09-13 | Fujitsu Limited | Dispositif semi-conducteur et procede de fabrication |

| JP5194328B2 (ja) * | 2001-02-01 | 2013-05-08 | ソニー株式会社 | 半導体装置及びその製造方法 |

| US6656815B2 (en) * | 2001-04-04 | 2003-12-02 | International Business Machines Corporation | Process for implanting a deep subcollector with self-aligned photo registration marks |

| JP3665275B2 (ja) * | 2001-05-28 | 2005-06-29 | 沖電気工業株式会社 | 位置合わせマークの形成方法 |

| US6635576B1 (en) * | 2001-12-03 | 2003-10-21 | Taiwan Semiconductor Manufacturing Company | Method of fabricating borderless contact using graded-stair etch stop layers |

| JP4227341B2 (ja) * | 2002-02-21 | 2009-02-18 | セイコーインスツル株式会社 | 半導体集積回路の構造及びその製造方法 |

| US7105442B2 (en) * | 2002-05-22 | 2006-09-12 | Applied Materials, Inc. | Ashable layers for reducing critical dimensions of integrated circuit features |

| US6673635B1 (en) | 2002-06-28 | 2004-01-06 | Advanced Micro Devices, Inc. | Method for alignment mark formation for a shallow trench isolation process |

| US7045837B2 (en) * | 2003-01-31 | 2006-05-16 | Infineon Technologies Ag | Hardmask with high selectivity for Ir barriers for ferroelectric capacitor manufacturing |

-

2004

- 2004-02-20 JP JP2004044788A patent/JP4397248B2/ja not_active Expired - Fee Related

-

2005

- 2005-02-03 US US11/048,891 patent/US7332405B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US20050186756A1 (en) | 2005-08-25 |

| JP2005236118A (ja) | 2005-09-02 |

| US7332405B2 (en) | 2008-02-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8080886B2 (en) | Integrated circuit semiconductor device with overlay key and alignment key and method of fabricating the same | |

| JP4397248B2 (ja) | 半導体装置及びその製造方法 | |

| JPH1079426A (ja) | 層間コンタクトの形成方法及びその構造 | |

| JP2003243293A (ja) | 半導体装置の製造方法 | |

| KR100442852B1 (ko) | 트렌치 소자분리 영역 형성방법 | |

| JP4439935B2 (ja) | 半導体装置の製造方法 | |

| JP3172998B2 (ja) | 半導体装置及びその製造方法 | |

| US7754568B2 (en) | Semiconductor device and method of fabricating the same | |

| KR100995142B1 (ko) | 반도체소자의 컨택홀 형성방법 | |

| JP2009218379A (ja) | 半導体装置の製造方法 | |

| KR20010107707A (ko) | Sti 구조를 갖는 반도체 장치를 제조하기 위한 방법 | |

| JP2003282700A (ja) | ホール形成方法 | |

| JP2007149768A (ja) | 半導体装置の製造方法 | |

| JP2006245198A (ja) | 半導体装置の製造方法 | |

| KR20010093668A (ko) | 얕은 트렌치 분리 소자 형성 방법 | |

| KR20060076498A (ko) | 반도체 소자의 소자 분리막 형성 방법 | |

| JP2002118253A (ja) | 半導体装置およびその製造方法 | |

| JP3607022B2 (ja) | 半導体装置の製造方法 | |

| JP2004319637A (ja) | アライメントマークの形成方法およびそれを用いた半導体装置の製造方法 | |

| JPH0547921A (ja) | 半導体装置の製造方法 | |

| JPH0481323B2 (ja) | ||

| JPH11177090A (ja) | 半導体装置及びその製造方法 | |

| KR20030056607A (ko) | 반도체 소자의 제조 방법 | |

| JPH0478177B2 (ja) | ||

| JP2002093897A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060814 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060814 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20081126 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20090204 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090526 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090602 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090730 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090929 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091020 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121030 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4397248 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121030 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131030 Year of fee payment: 4 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |