JP3607022B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP3607022B2 JP3607022B2 JP31573996A JP31573996A JP3607022B2 JP 3607022 B2 JP3607022 B2 JP 3607022B2 JP 31573996 A JP31573996 A JP 31573996A JP 31573996 A JP31573996 A JP 31573996A JP 3607022 B2 JP3607022 B2 JP 3607022B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- resist pattern

- insulating film

- patterning

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/70—Microphotolithographic exposure; Apparatus therefor

- G03F7/70425—Imaging strategies, e.g. for increasing throughput or resolution, printing product fields larger than the image field or compensating lithography- or non-lithography errors, e.g. proximity correction, mix-and-match, stitching or double patterning

- G03F7/7045—Hybrid exposures, i.e. multiple exposures of the same area using different types of exposure apparatus, e.g. combining projection, proximity, direct write, interferometric, UV, x-ray or particle beam

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- ing And Chemical Polishing (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electron Beam Exposure (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

Description

【発明の属する技術分野】

本発明は半導体装置の製造方法、特に光リソグラフィと電子線リソグラフィの両方を用いてレジストマスクを形成し、これを下地層のパターニングマスクとして用いる半導体装置の製造方法に関する。

【0002】

【従来の技術】

従来より半導体装置の製造方法においては、半導体基板全面に導電膜を形成し、これをパターニングし、導電膜を所定の形状に加工して配線層等を形成する工程が行われている。

【0003】

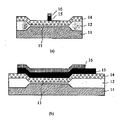

以下に従来の技術として、配線層の形成工程のうち、MOSトランジスタのゲート電極配線と配線接続部の形成工程について図12乃至図14を用いて説明する。尚、以下の説明において配線接続部はゲート電極配線に接続されているものとする。またこの配線接続部は、上層に形成される図示せぬ配線層とゲート電極配線とのコンタクトをとるために、合わせ余裕を持って、その寸法はゲート電極配線に比較し大きめに形成されるものとする。

【0004】

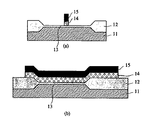

さらに各図の(a)は、発明の実施の形態において参照する図1(c)のA−A面に対応する部分の断面図であり、各図の(b)は、B−B面に対応する部分の断面図である。

【0005】

まず図12に示すように、半導体基板111の素子分離領域にはフィールド絶縁膜112を、また半導体基板111の素子領域上にはゲート絶縁膜113を形成する。図においてフィールド絶縁膜112は、LOCOS(Local Oxidation of Silicon)法により形成した例を示しているが、STI(Shallow Trench Isolation)法により形成してもよい。次にこれらの絶縁膜112、113上に、ゲート電極配線を形成するために多結晶シリコン膜等により導電膜114を形成する。次に導電膜114上に、キャップ絶縁膜115を形成する。尚、導電膜114やキャップ絶縁膜115は、CVD(Chemical Vapour Deposition)法やスパッタ法によって堆積する。この後キャップ絶縁膜上に、光リソグラフィ用のレジストか或いは電子線リソグラフィ用のレジストかを塗布し、このレジストを光リソグラフィ、或いは電子線リソグラフィによりゲート電極配線の形状に感光させ、感光させた後のレジストを現像することにより、レジストパターン116を形成する。

【0006】

続いて図13に示すように、レジストパターン116をマスクとして、異方性エッチングによりキャップ絶縁膜115をパターニングする。次にアッシング等により、エッチングの際のマスクとして用いたレジストパターン116を除去する。

【0007】

続いて図14に示すように、パターニングされたキャップ絶縁膜115をマスクとして、異方性エッチングにより導電膜114をパターニングし、ゲート電極配線とそれに接続される配線接続部を形成する。

【0008】

上記の例は、MOSトランジスタのゲート電極配線とこれに接続される配線接続部の領域の形成方法について示しているが、この他、通常の素子間の配線層と配線接続部を形成する場合等についても、上記と同様の製造工程を用いて行うことができる。

【0009】

【発明が解決しようとする課題】

従来の技術においては、ゲート電極配線を形成するためのマスクとして用いるレジストパターンの形成では、g線やi線或いはKrFエキシマレーザーを光源として用いる光リソグラフィが一般的であり、この他、電子線ビームによってパターンを描画する電子線リソグラフィを用いることが考えられる。

【0010】

光リソグラフィは、レジストパターンの形成に通常用いられている方法であり、スループットも比較的高いため半導体装置の量産に向いている。しかし今後さらに微細化していく超LSIの製造を考慮すると、解像度の点で問題がある。現状の光リソグラフィ技術では、KrFエキシマレーザを光源として用いた場合でも、幅0.25μm程度のパターニングが限界とされている。今後の超LSIの微細化の流れに伴って、配線のデザインルールは0.1 μm近辺、もしくはそれ以下になっていくと予測されており、その配線のデザインルールを現状の光リソグラフィ技術を用いてパターニングすることは困難である。

【0011】

一方電子線リソグラフィは、光リソグラフィと比較して解像度は高く、0.1 μm近辺のデザインルールのパターニングに関しては、充分対応することができるとされている。しかし、光リソグラフィと比較すると、スループットが極端に悪いという問題点がある。これは光リソグラフィではレジストの平面を一度に広範囲に感光させることが可能なのに対し、電子線リソグラフィではレジストの平面を一度に広範囲を感光させることができず、描画により感光させる領域を塗りつぶす必要があるからである。

【0012】

通常、半導体集積回路の素子中の配線のパターンは、デザインルールの比較的大きいパターン、すなわち現状の光リソグラフィでも充分パターニングが可能なパターンと、デザインルールの比較的小さいパターン、すなわち現状の光リソグラフィではパターニングが困難になりつつあるパターンとが混在している。そこでスループットの向上と、解像度の向上の両立のため、デザインルールが小さく、光リソグラフィではパターニングが困難なパターンの形成の際のみ、電子線リソグラフィを用い、その他の部分のパターンの形成には、光リソグラフィを用いることが考えられる。

【0013】

しかしながら本来、光リソグラフィと電子線リソグラフィとでは、エッチングのマスクとして形成するためのレジストの種類が異なる。従って光リソグラフィと電子線リソグラフィを単純に併用することは不可能である。光リソグラフィと電子線リソグラフィとをそれぞれに対応したレジストを用いて併用しようとすれば、例えば光リソグラフィにより形成したレジストパターンが、電子線に影響されないように、形成したレジストパターンを覆ったマスクを形成した後に、電子線リソグラフィを行う必要が生じたり、エッチングのマスクとして使用した後のレジストパターンを除去する必要等が生じ、工程数の増加を招くこととなる。一方、解像度を落とさずに光、電子線の両方により感光することが可能なレジストの開発も進められているが、まだ実用化には至っていない。

【0014】

またデザインルールの大きいパターン及び小さいパターンの全てを電子線リソグラフィによりパターニングすることも考えられるが、この場合、スループットが大幅に低下する。即ち、前述のように光リソグラフィではレジストの平面を一度に広範囲に感光させることが可能なのに対して、電子線リソグラフィでは描画によって感光すべき領域を塗りつぶす必要があるからである。現状ではウエハ一枚当たり、レジストの感光に要する時間は、光リソグラフィによる露光ではウエハの移動時間等も含め数分程度であるのに対し、電子線リソグラフィではウエハ一枚当たり数時間は必要である。よって、特に大規模な量産が行われる半導体装置の製造においては、電子線リソグラフィのみでレジストパターンを感光させることは現実的ではない。

【0015】

【課題を解決するための手段】

本発明は半導体装置の製造方法、特に配線層の形成工程において、スループットの低下を防ぎ、かつ超LSIの微細化に対応できるよう、小さいデザインルールの部分のレジストのパターニングには電子線リソグラフィを用い、その他の部分のレジストのパターニングには光リソグラフィを用いるための製造方法を提供する。それは以下の手段により行う。

【0016】

すなわち本発明の第一の手段によれば第一、第二領域を有する半導体基板表面上に第一絶縁膜と、導電膜と、第二絶縁膜と、前記導電膜とエッチング特性が実質的に同様な選択膜とを順次形成する工程と、光リソグラフィ法により前記選択膜表面の前記第一領域上に第一レジストパターンを形成する工程と、前記第一レジストパターンをマスクとし前記選択膜をパターニングする工程と、前記第一レジストパターンを除去する工程と、電子線リソグラフィ法により前記第二絶縁膜表面の前記第二領域上に第二レジストパターンを形成する工程と、前記第二レジストパターンと前記選択膜とをマスクとし前記第二絶縁膜をパターニングする工程と、前記第二レジストパターンを除去する工程と、パターニングされた前記第二絶縁膜をマスクとして前記導電膜をパターニングする工程とを具備することを特徴とする。

【0017】

また本発明の第二の手段によれば第一、第二領域を有する半導体基板上に第一絶縁膜と、導電膜と、第二絶縁膜と、前記導電膜とエッチング特性が実質的に同様な選択膜とを順次形成する工程と、電子線リソグラフィ法により前記選択膜表面の第二領域上に第二レジストパターンを形成する工程と、前記第二レジストパターンをマスクとし前記選択膜をパターニングする工程と、前記第二レジストパターンを除去する工程と、光リソグラフィ法により前記第二絶縁膜上に第一レジストパターンを形成する工程と、前記第一レジストパターンと前記選択膜をマスクとし前記第二絶縁膜をパターニングする工程と、前記第一レジストパターンを除去する工程と、パターニングされた前記第二絶縁膜をマスクとして前記導電膜をパターニングする工程とを具備することを特徴とする。

【0018】

【発明の実施の形態】

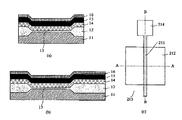

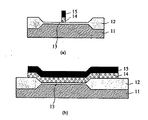

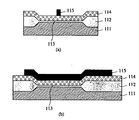

本発明の第一の実施の形態として、MOSトランジスタのゲート電極配線とそれに接続される配線接続部の製造工程について、図1乃至図5を参照して説明する。尚、図1(c)は各要素の形成後のMOSトランジスタの上面図の概略を示している。この図では、ゲート電極配線の形成領域211、素子形成領域212、素子分離領域213及び配線接続部の形成領域214とを示している。また各図の(a)は図1(c)におけるA−A面に対応する部分の断面図、つまりゲート電極配線に垂直な方向の断面を示しており、また各図の(b)は図1(c)におけるB−B面に対応する部分の断面図、つまりゲート電極配線に平行な方向の断面を示している。またこの配線接続部は、上層に形成される図示せぬ配線層とゲート電極配線とのコンタクトをとるために、合わせ余裕を持って、その寸法はゲート電極配線に比較し大きめに形成されるものとする。

【0019】

まず図1(a)、(b)に示すように、半導体基板11上の素子分離領域に、LOCOS法を用いてフィールド絶縁膜12を形成する。LOCOS法に換えてSTI法によりフィールド絶縁膜を形成することもできる。次にゲート酸化を行い、素子領域上に膜厚5 〜20nmのゲート絶縁膜13を形成する。次にゲート電極配線を形成するために、ゲート絶縁膜13上にCVD法やスパッタ法等により膜厚100 〜400 nmの導電膜14を形成する。次に導電膜14上にCVD法等により膜厚200 nm程度のキャップ絶縁膜15を形成する。さらにキャップ絶縁膜15上に導電膜14とエッチング特性が実質的に同様な選択膜16を形成する。

【0020】

ここで導電膜14は、リンやボロンを高濃度に含んだ多結晶シリコン、またはタングステン等の高融点金属、または上層にタングステンシリサイドやモリブデンシリサイド等の高融点金属シリサイドを、下層に多結晶シリコンを用いた積層構造、または上層にタングステンやモリブデン等の高融点金属を、下層に多結晶シリコンを用いた積層構造により形成する。

【0021】

キャップ絶縁膜15は、導電膜14とエッチングでの選択比の充分とれる材料、すなわちシリコン酸化膜やシリコン窒化膜等で形成する。

選択膜16は、導電膜14とエッチング特性が実質的に同等な材料、すなわち導電膜14を形成した全部または一部と同一の材料か、あるいは導電膜14の材料を含有する材料、例えば多結晶シリコンや高融点金属、高融点金属シリサイド、あるいはこれらを含有した材料により形成する。一般に高融点金属や高融点金属シリサイドは多結晶シリコンに対し、そのエッチングの選択比は数倍程度であるため、選択膜16は多結晶シリコンで形成するのが最も望ましい。具体的には、導電膜14を多結晶シリコン或いは高融点金属の単層で形成した場合や、導電膜14を高融点金属或いは高融点金属シリサイドと多結晶シリコンとの積層で形成した場合には、選択膜16は多結晶シリコンにより形成するのが最も望ましい。

【0022】

尚、選択膜16を多結晶シリコンにより形成する場合、この多結晶シリコンの膜厚は、導電膜14の一部として形成する多結晶シリコンの膜厚以下で形成するのが望ましい。

【0023】

但し、選択膜16の膜厚、材料に関しては、後述するゲート電極の形成のためのエッチング時に導電膜14の除去される部分と共に、除去されるような条件を選択すればよい。

【0024】

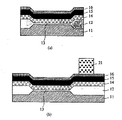

続いて図2に示すように、選択膜16の全面に光リソグラフィ用のレジストを塗布する。次に光リソグラフィを用い、レジストを所定のパターンに露光し、これを現像することによりレジストパターン21を形成する。このレジストパターン21は、光リソグラフィで充分対応することが可能な、デザインルールの比較的大きな箇所に形成する。すなわちゲート電極配線等の光リソグラフィでは対応が困難な箇所ではなく、上層配線との接続をとるための配線接続部やパッドに対応する箇所に形成する。現状の光リソグラフィでは線幅0.25μm程度でパターニングすることが可能であるが、ここではレジストパターンの縦横の寸法は0.8 〜1.4 μm程度で形成する。

【0025】

続いて図3に示すように、レジストパターン21をマスクとして、選択膜16を異方性エッチングによりエッチングする。この際、キャップ絶縁膜15と選択膜16とはエッチングの選択比が大きいため、選択膜16のみをエッチングし、キャップ絶縁膜15を残留させることができる。尚、選択膜16のエッチングに際しては、Cl2 やHBr、SF6 等をエッチングガスとして用いることにより、絶縁膜とのエッチングの選択比を10乃至30程度とすることができる。次にレジストパターン21をアッシング、或いはアッシングと硫酸及び過酸化水素との薬液処理との組み合わせにより除去する。

【0026】

続いて図4に示すように、キャップ絶縁膜15上及びパターニングされた選択膜16上に電子線リソグラフィ用のレジストを塗布する。次に光リソグラフィではパターニングが困難となりつつあるゲート電極配線に対応する箇所のみを、電子線リソグラフィを用いて感光し、現像することにより、レジストパターン41を形成する。電子線リソグラフィでは線幅0.1 μm程度以下でもパターニングすることが可能であるが、ここではレジストパターンの線幅は0.15μm程度で形成する。

【0027】

尚、光リソグラフィで充分対応が可能なデザインルールの比較的大きいパターンと、光リソグラフィではパターニングが困難となりつつあるデザインルールが比較的小さいパターンとが結合して、一つのパターンを形成している場合には、レジストパターン41は、選択膜16にオーバーラップさせて形成することにより、両者の間に多少の合わせずれが生じても対応することが可能である。

【0028】

続いて図5に示すように、この前の工程までにパターニングが完了しているレジストパターン41と選択膜16の双方をマスクとして、キャップ絶縁膜15を異方性エッチングによりエッチングする。この際、キャップ絶縁膜15と導電膜14及び選択膜16とはエッチングの選択比が比較的大きいので、キャップ絶縁膜15のみをエッチングし、導電膜14及び選択膜16を残留させることができる。尚、キャップ絶縁膜15のエッチングに際しては、CF4 やCO、CHF3 等を組み合わせてエッチングガスとして用いることにより、導電膜とのエッチングの選択比を10乃至30程度とすることができる。次にレジストパターン41をアッシング等により除去する。

【0029】

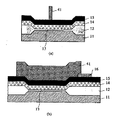

続いて図6に示すように、キャップ絶縁膜15をマスクとして導電膜14を異方性エッチングによりエッチングする。この際、選択膜16は導電膜14とエッチング特性が実質的に同様なため、導電膜14と同時にエッチングされ、除去される。従って選択膜16を除去する工程を省略することができる。尚、導電膜14のエッチングに際しては、Cl2 やHBr、SF6 等をエッチングガスとして用いることにより、キャップ絶縁膜15とのエッチングの選択比を10乃至30程度とすることができる。以上の工程により、ゲート電極配線とそれに接続される配線接続部の形成工程が終了する。

【0030】

本発明の第一の実施の形態によれば、キャップ絶縁膜15上にさらに導電膜14とエッチング特性が実質的に同様な選択膜16を形成する。そして光リソグラフィ技術で対応することが可能なデザインルールの大きい部分のレジストパターン21を形成した後、これをマスクとして選択膜16のパターニングを行う。次に光リソグラフィ技術では対応することが困難になりつつある部分のレジストパターン41を電子線リソグラフィを用いて形成し、レジストパターン41及びパターニングされた選択膜16をマスクとしてキャップ絶縁膜15のパターニングを行う。そして最終的にパターニングされたキャップ絶縁膜15をマスクとして導電膜14をパターニングする。

【0031】

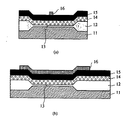

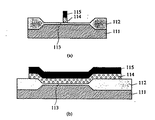

次に本発明の第二の実施の形態について、図7乃至図11を参照して説明する。尚、第一の実施の形態と同一の構成要素については、図中で同一の符号を記し、これらの説明を省略する。また各構成の膜厚や材料についても特に示さない限り、第一の実施の形態と同一とする。尚、各図の(a)は図1(c)におけるA−A面に対応する断面図、各図の(b)は図1(c)におけるB−B面に対応する断面図である。

【0032】

まず図7に示すように、半導体基板11上にゲート絶縁膜13、導電膜14、キャップ絶縁膜15、選択膜16を順次形成する。この工程は第一の実施の形態における図1に示した工程と同様である。また導電膜14、キャップ絶縁膜15、選択膜16の膜厚、材料についても第一の実施の形態と同様である。次に選択膜16上に電子線リソグラフィ用のレジストを塗布し、光リソグラフィ技術では対応することが困難となりつつある部分のみを、電子線リソグラフィを用いてパターニングし、レジストパターン71を形成する。光リソグラフィで充分対応が可能なデザインルールの大きいパターンと、光リソグラフィでは対応が困難となりつつあるデザインルールの小さいパターンが結合している部分がある場合には、レジストパターン71は本来のパターンよりもデザインルールの大きいパターン側にオーバーラップさせて形成することにより、両者の間に多少の合わせずれが生じても対応することが可能である。

【0033】

続いて図8に示すように、レジストパターン71をマスクとして選択膜16を異方性エッチングによりエッチングする。この際、選択膜16とキャップ絶縁膜15とはエッチングの選択比が大きいので、選択膜16のみをパターニングし、キャップ絶縁膜15を残留させることができる。次に、レジストパターン71をアッシング等により除去する。

【0034】

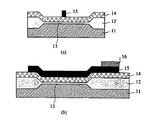

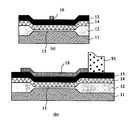

続いて図9に示すように、光リソグラフィ用のレジストをキャップ絶縁膜15上及び選択膜16上に塗布する。次に光リソグラフィを用いて、所定のパターンを露光、現像することによりレジストパターン91を形成する。このレジストパターン91は、光リソグラフィで充分対応することが可能な、デザインルールの比較的大きな箇所に形成する。すなわちゲート電極配線等の光リソグラフィでは対応が困難な箇所ではなく、上層配線との接続をとるための配線接続部やパッドを形成する部分に対応する箇所に形成する。

【0035】

続いて図10に示すように、レジストパターン91と選択膜16の双方をマスクとし、異方性エッチングによりキャップ絶縁膜15をエッチングする。この際、キャップ絶縁膜15と導電膜14及び選択膜16とはエッチングの選択比が大きいので、キャップ絶縁膜15のみをエッチングし、導電膜14及び選択膜16を残留させることができる。次にレジストパターン91をアッシング等により除去する。

【0036】

続いて図11に示すように、キャップ絶縁膜15をマスクとして導電膜14を異方性エッチングによりエッチングする。この際、選択膜16は導電膜14とエッチング特性が実質的に同様なため、導電膜14と共に同時にエッチングされ、除去される。従って選択膜16を除去する工程を省略することができる。以上の工程により、ゲート電極配線とそれに接続される配線接続部の形成工程が終了する。

【0037】

第二の実施の形態においては、第一の実施の形態と同様にキャップ絶縁膜15上にさらに導電膜14とエッチング特性が実質的に同様な選択膜16を形成する。そしてまず光リソグラフィ技術で対応することが困難となりつつある部分に、電子線リソグラフィを用いてレジストパターン71を形成し、これを用いて選択膜16をパターニングする。次に光リソグラフィで対応が可能なデザインルールの大きい部分のレジストパターン21を形成した後、これらをマスクとしてキャップ絶縁膜15のパターニングを行う。そして最終的にパターニングされたキャップ絶縁膜15をマスクとして導電膜14をパターニングする。すなわち第一の実施の形態と第二の実施の形態とは、光リソグラフィを用いたレジストパターンの形成と、電子線リソグラフィを用いたレジストパターンの形成の順序が異なる。

【0038】

以上の各実施の形態では、ゲート電極配線となる導電膜とその上面に形成されるキャップ絶縁膜の積層構造を用い、この積層構造の上に、導電膜とエッチング特性が実質的に同様な選択膜を設けることにより、光リソグラフィと電子線リソグラフィを併用することが可能となる。また選択膜は導電膜のエッチングの工程と同時に除去されるため、これを除去するための工程を省略することが可能となる。これにより、配線層等のパターニングの際、現状の光リソグラフィではパターニングを行うことが困難となりつつあるデザインルールの小さい部分のみを選択し、この部分のみ電子線リソグラフィでパターニングすることが可能となり、超LSIの微細化に対応し、かつスループットの低下を防ぐことができる。

【0039】

尚、上記の実施の形態では選択膜16の膜厚は、導電膜14の膜厚と同等、さらには導電膜14の膜厚以上であっても、導電膜のエッチング工程において同時に除去される性質を有すればよい。

また上記の実施の形態では、ゲート電極配線と配線接続部の形成工程について示したが、これに限定されることはなく、導電膜と絶縁層の積層となっている配線層全般の形成工程に適用することが可能である。

さらに半導体基板上に高抵抗を有する導電膜によって形成される抵抗素子と、この抵抗素子に接続される抵抗素子の接続極部の形成工程にも適用することが可能である。すなわち電子線リソグラフィによって、線幅がより狭い領域をパターニングすることができるため、より高抵抗な抵抗素子を微細な領域中に形成することができる。

また上記に示した数値、材料等は上記に限定されるものではなく、種々態様により実施することが可能である。

【0040】

【発明の効果】

本発明によれば、現状の光リソグラフィ技術では対応することが困難となりつつあるパターンを含む場合、その配線層として形成する膜の上面に、さらにこの配線層とエッチング特性の類似した選択膜を設けることにより、光リソグラフィと電子線リソグラフィとを混用して、パターニングを行うことが可能となる。さらにこの選択膜は、導電膜をエッチングする際に同時にエッチングされて除去されるため、これを除去するための工程を追加する必要が無い。

よって配線層のパターニングの際、現状の光リソグラフィではパターニングを行うことが困難となりつつあるデザインルールの小さい部分のみを選択し、この部分のみ電子線リソグラフィでパターニングすることが可能であり、スループットの低下を防ぐことができる。

【図面の簡単な説明】

【図1】本発明の第一の実施の形態を説明する工程断面図。

【図2】本発明の図1に続く第一の実施の形態を説明する工程断面図。

【図3】本発明の図2に続く第一の実施の形態を説明する工程断面図。

【図4】本発明の図3に続く第一の実施の形態を説明する工程断面図。

【図5】本発明の図4に続く第一の実施の形態を説明する工程断面図。

【図6】本発明の図5に続く第一の実施の形態を説明する工程断面図。

【図7】本発明の第二の実施の形態を説明する工程断面図。

【図8】本発明の図7に続く第二の実施の形態を説明する工程断面図。

【図9】本発明の図8に続く第二の実施の形態を説明する工程断面図。

【図10】本発明の図9に続く第二の実施の形態を説明する工程断面図。

【図11】本発明の図10に続く第二の実施の形態を説明する工程断面図。

【図12】従来の製造方法を説明する工程断面図。

【図13】従来の図12に続く製造方法を説明する工程断面図。

【図14】従来の図13に続く製造方法を説明する工程断面図。

【符号の説明】

11、 111 半導体基板

12、 112 フィールド絶縁膜

13、 113 ゲート絶縁膜

14、 114 導電膜

15、 115 キャップ絶縁膜

16 選択膜

21、 41、71、91、116 レジストパターン

211 素子形成領域

212 ゲート電極配線形成領域

213 素子分離形成領域

214 配線接続部形成領域

Claims (15)

- 第一、第二領域を有する半導体基板表面上に第一絶縁膜と、導電膜と、第二絶縁膜と、前記導電膜とエッチング特性が実質的に同様な選択膜とを順次形成する工程と、

光リソグラフィ法により前記選択膜表面の前記第一領域上に第一レジストパターンを形成する工程と、

前記第一レジストパターンをマスクとし前記選択膜をパターニングする工程と、

前記第一レジストパターンを除去する工程と、

電子線リソグラフィ法により少なくとも前記第二絶縁膜表面の前記第二領域上に第二レジストパターンを形成する工程と、

前記第二レジストパターンと前記選択膜とをマスクとし前記第二絶縁膜をパターニングする工程と、

前記第二レジストパターンを除去する工程と、

パターニングされた前記第二絶縁膜をマスクとして前記導電膜をパターニングする工程と

を具備することを特徴とする半導体装置の製造方法。 - 第一、第二領域を有する半導体基板上に第一絶縁膜と、導電膜と、第二絶縁膜と、前記導電膜とエッチング特性が実質的に同様な選択膜とを順次形成する工程と、

電子線リソグラフィ法により前記選択膜表面の第二領域上に第二レジストパターンを形成する工程と、

前記第二レジストパターンをマスクとし前記選択膜をパターニングする工程と、

前記第二レジストパターンを除去する工程と、

光リソグラフィ法により少なくとも前記第二絶縁膜上に第一レジストパターンを形成する工程と、

前記第一レジストパターンと前記選択膜とをマスクとし前記第二絶縁膜をパターニングする工程と、

前記第二絶縁膜をパターニングする工程の後、前記第一レジストパターンを除去する工程と、

パターニングされた前記第二絶縁膜をマスクとして前記導電膜をパターニングする工程と

を具備することを特徴とする半導体装置の製造方法。 - 前記導電膜をパターニングする工程において、パターニングされた前記選択膜を同時に除去することを特徴とする請求項1または2記載の半導体装置の製造方法。

- 前記選択膜の膜厚を前記導電膜の膜厚以下に形成することを特徴とする請求項1または2記載の半導体装置の製造方法。

- 前記第一領域は配線接続部形成領域であり、前記第二領域はゲート電極配線形成領域であることを特徴とする請求項1または2記載の半導体装置の製造方法。

- 前記第一領域は抵抗素子接続部形成領域であり、前記第二領域は抵抗素子形成領域であることを特徴とする請求項1または2記載の半導体装置の製造方法。

- 前記導電膜と前記選択膜とを同一の材料かまたは同一の材料を含有させて形成することを特徴とする請求項1または2記載の半導体装置の製造方法。

- 前記導電膜を高融点金属シリサイドと多結晶シリコンとの積層で形成し、前記選択膜を多結晶シリコンにより形成することを特徴とする請求項1または2記載の半導体装置の製造方法。

- 前記導電膜を高融点金属と多結晶シリコンとの積層で形成し、前記選択膜を多結晶シリコンにより形成すること特徴とする請求項1または2記載の半導体装置の製造方法。

- 前記導電膜と前記選択膜とを多結晶シリコンで形成すること特徴とする請求項1または2記載の半導体装置の製造方法。

- 前記選択膜として形成する多結晶シリコンの膜厚を、前記導電膜として形成する多結晶シリコンの膜厚以下に形成することを特徴とする請求項8乃至10記載の半導体装置の製造方法。

- 前記第二絶縁膜をシリコン酸化膜またはシリコン窒化膜により形成することを特徴とする請求項1または2記載の半導体装置の製造方法。

- 前記第一領域と前記第二領域とが隣接する場合、前記第二レジストパターンを前記第一領域上の一部にも前記第二領域上から延長して形成することを特徴とする請求項1または2記載の半導体装置の製造方法。

- 第一、第二領域を有する半導体基板表面上に第一絶縁膜と、導電膜と、第二絶縁膜と、選択膜とを順次形成する工程と、

光リソグラフィ法により前記選択膜表面の前記第一領域上に第一レジストパターンを形成する工程と、

前記第一レジストパターンをマスクとし前記選択膜をパターニングする工程と、

前記第一レジストパターンを除去する工程と、

電子線リソグラフィ法により少なくとも前記第二絶縁膜表面の前記第二領域上に第二レジストパターンを形成する工程と、

前記第二レジストパターンと前記選択膜とをマスクとし前記第二絶縁膜をパターニングする工程と、

前記第二レジストパターンを除去する工程と、

パターニングされた前記第二絶縁膜をマスクとして前記導電膜をパターニングする工程とを具備し、

前記選択膜は、前記導電膜をパターニングする工程において、同時に除去される特性をもって形成することを特徴とする半導体装置の製造方法。 - 第一、第二領域を有する半導体基板上に第一絶縁膜と、導電膜と、第二絶縁膜と、選択膜とを順次形成する工程と、

電子線リソグラフィ法により前記選択膜表面の第二領域上に第二レジストパターンを形成する工程と、

前記第二レジストパターンをマスクとし前記選択膜をパターニングする工程

と、

前記第二レジストパターンを除去する工程と、

光リソグラフィ法により少なくとも前記第二絶縁膜上に第一レジストパターンを形成する工程と、

前記第一レジストパターンと前記選択膜とをマスクとし前記第二絶縁膜をパターニングする工程と、

前記第二絶縁膜をパターニングする工程の後、前記第一レジストパターンを除去する工程と、

パターニングされた前記第二絶縁膜をマスクとして前記導電膜をパターニングする工程とを具備し、

前記選択膜は、前記導電膜をパターニングする工程において、同時に除去される特性をもって形成することを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP31573996A JP3607022B2 (ja) | 1995-12-11 | 1996-11-27 | 半導体装置の製造方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP32153595 | 1995-12-11 | ||

| JP7-321535 | 1995-12-11 | ||

| JP31573996A JP3607022B2 (ja) | 1995-12-11 | 1996-11-27 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH09223665A JPH09223665A (ja) | 1997-08-26 |

| JP3607022B2 true JP3607022B2 (ja) | 2005-01-05 |

Family

ID=26568410

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP31573996A Expired - Fee Related JP3607022B2 (ja) | 1995-12-11 | 1996-11-27 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3607022B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2810447B1 (fr) * | 2000-06-16 | 2003-09-05 | Commissariat Energie Atomique | Procede de creation d'un etage de circuit integre ou conexistent des motifs fins et larges |

-

1996

- 1996-11-27 JP JP31573996A patent/JP3607022B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH09223665A (ja) | 1997-08-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6579757B2 (en) | Method for fabricating semiconductor device which prevents gates of a peripheral region from being oxidized | |

| US8080886B2 (en) | Integrated circuit semiconductor device with overlay key and alignment key and method of fabricating the same | |

| KR100225831B1 (ko) | 반도체장치의 제조방법 | |

| US6432816B2 (en) | Method for fabricating semiconductor device | |

| US6448179B2 (en) | Method for fabricating semiconductor device | |

| US6362113B1 (en) | Method of forming pattern | |

| KR20000005759A (ko) | 반도체장치및제조방법 | |

| JPH1079426A (ja) | 層間コンタクトの形成方法及びその構造 | |

| US5902133A (en) | Method of forming a narrow polysilicon gate with i-line lithography | |

| JP3607022B2 (ja) | 半導体装置の製造方法 | |

| JP3585039B2 (ja) | ホール形成方法 | |

| CN101436529B (zh) | 半导体器件的制造方法 | |

| US5512500A (en) | Method of fabricating semiconductor device | |

| US6989323B2 (en) | Method for forming narrow gate structures on sidewalls of a lithographically defined sacrificial material | |

| JPH11204506A (ja) | 回路パターンが形成されたウェハおよびその製造方法 | |

| KR100632422B1 (ko) | 반도체 기판내에 구조를 형성하는 방법 | |

| US7387869B2 (en) | Method of forming pattern for semiconductor device | |

| US7125775B1 (en) | Method for forming hybrid device gates | |

| JP2003007678A (ja) | 半導体装置の製造方法及びこの方法により製造される半導体装置 | |

| US6191041B1 (en) | Method of fabricating semiconductor device | |

| JPH07321015A (ja) | 半導体装置の製造方法 | |

| KR100583120B1 (ko) | 반도체소자의 제조방법 | |

| KR100257770B1 (ko) | 반도체 소자의 미세한 전도막 패턴 형성 방법 | |

| JPH04291345A (ja) | パターン形成方法 | |

| JPH0327521A (ja) | Mos型トランジスタの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040922 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20041005 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20041006 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081015 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081015 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091015 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101015 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111015 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111015 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121015 Year of fee payment: 8 |

|

| LAPS | Cancellation because of no payment of annual fees |