JP4337549B2 - 固体撮像装置 - Google Patents

固体撮像装置 Download PDFInfo

- Publication number

- JP4337549B2 JP4337549B2 JP2003583019A JP2003583019A JP4337549B2 JP 4337549 B2 JP4337549 B2 JP 4337549B2 JP 2003583019 A JP2003583019 A JP 2003583019A JP 2003583019 A JP2003583019 A JP 2003583019A JP 4337549 B2 JP4337549 B2 JP 4337549B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- supply voltage

- unit

- pixel

- imaging device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/62—Detection or reduction of noise due to excess charges produced by the exposure, e.g. smear, blooming, ghost image, crosstalk or leakage between pixels

- H04N25/626—Reduction of noise due to residual charges remaining after image readout, e.g. to remove ghost images or afterimages

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/709—Circuitry for control of the power supply

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/766—Addressed sensors, e.g. MOS or CMOS sensors comprising control or output lines used for a plurality of functions, e.g. for pixel output, driving, reset or power

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

【発明の属する技術分野】

本発明は、複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有する増幅型(CMOSセンサ型)の固体撮像装置に関し、特にその電源回路の改良に関するものである。

【0002】

【従来の技術】

従来より、たとえば図1〜図7に示すような増幅型(CMOSセンサ型)の固体撮像装置が知られている。以下、これらの図を用いて従来例の構成及び動作を説明する。

【0003】

図1は、従来の固体撮像装置の構成例を示す概略平面図である。

【0004】

この固体撮像装置は、半導体チップ1上に、2次元配列で多数の単位画素を配置した画素部2と、各種のタイミング信号を生成するタイミングジェネレータ部3と、単位画素の各画素列(カラム)毎にCDS(相関二重サンプリング)を行うカラムCDSやA/D変換を行うカラムAD等の出力カラム部4と、この出力カラム部4を水平方向に選択して駆動する水平駆動部5と、各画素行を選択して駆動する垂直駆動部6と、画素部2から読み出された画素信号に対して信号処理を行う信号処理部(DSP)7等が形成されている。

【0005】

この固体撮像装置は、電源系統としては第1の電源系統(以下、便宜上デジタル電源という)と第2の電源系統(以下、便宜上アナログ電源という)の2つの電源系統を持って駆動される。半導体チップ1は、第1の電源系統であるデジタル電源電圧DVDDが供給される電源端子8と、デジタルグランド電圧DVSSが供給される電源端子9と、第2の電源系統であるアナログ電源電圧AVDDが供給される電源端子10と、アナロググランド電圧AVSSが供給される電源端子11とを有する。

【0006】

このように従来の固体撮像装置では、デジタル電源電圧(DVDD)とアナログ電源電圧(AVDD)は同じ電圧値(例えば1.8V、2.5V、3.3Vなど)であったため、半導体チップ1上に複数の電極パッドPADが配置されていても、チップ1の外部からは1種類の電源電圧が供給され、単一電源電圧で動作している。

【0007】

図2は、図1に示す従来例の画素部2の積層構造を示す断面図である。

【0008】

図示のように、シリコン基板12上にはPウェル13が形成されており、このPウェル13上に、素子分離領域(本例ではLOCOS素子分離であるがSTI等の場合もある)14と、電源領域(AVDD)15と、リセットトランジスタのリセットゲート(Reset)16と、フローティングデフュージョン(FD)部と呼ばれる電荷検出部17と、フォトダイオード23の信号電荷をFD部17に転送する転送トランジスタ(転送ゲートTG)18と、フォトダイオード23を構成するP+型受光層19及びN型光電変換層20等が形成されている。

【0009】

このような固体撮像装置において、半導体プロセス世代が進んでいくと、使用する電源電圧が小さくなっていく。たとえば0.35μmプロセスでは3.3V、0.25μmプロセスでは2.5V、0.18μmプロセスでは1.8V、などである。

【0010】

一方、固体撮像装置は第2の電源系統で駆動される回路部(以下、アナログ回路部という)と第1の電源系統で駆動される回路図(以下、デジタル回路部という)が必須のアナログデジタル混載デバイスである。よって、上述したデジタル回路部は電源電圧が低下しても動作する。

【0011】

【発明が解決しようとする課題】

しかし、アナログ回路部の低電圧化は難しい。

特にアナログ回路部の中でも画素部2については、フォトダイオード23から信号電荷(Qsig)を電荷検出部17に完全転送しなければならないため、低電圧化が難しい。

【0012】

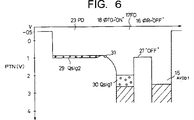

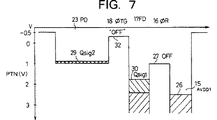

図3〜図7は、図2に示した断面図に対応するポテンシャル電位を示す説明図であり、縦軸がポテンシャル電位PTN(V)、横軸が図2の基板表面における各素子の形成位置に対応している。

【0013】

以下、これらの図により、従来の信号電荷の読出し動作を説明する。

まず、図3において、フォトダイオード(PD)23に信号電荷24を蓄積している間、リセットトランジスタ16のドレイン端子15は電源電圧AVDD1になっている。図示の例では、AVDD1=2.5Vである(図中、26で示す)。この時、転送ゲート18のゲート電圧(ΦTG)は0Vである。

また、リセットトランジスタ16の“OFF”時のポテンシャル電位(ΦR)は、例えば1V程度である(図中、27で示す)。このリセットトランジスタ16は、ディープディプリーション(Deep Depletion)型トランジスタとなっている。

【0014】

次に、図4に示すように、リセットトランジスタ16のゲートを“ON”状態にする。つまり、ΦR=2.5Vである。そうすると、リセットトランジスタ16のゲート下の電位は深くリセット(図示の例では3Vにリセット)され(図中、28で示す)、FD電位は電源電圧15(AVDD1=2.5V)と同じ電位となる(図中、26で示す)。つまり、リセットトランジスタ16にディープディプリーション型トランジスタを用いることによってFD電位を電源電圧までリセットしている。

【0015】

次に、図5は、リセットトランジスタ16を“OFF”状態にしたときのポテンシャルを示しており、FD電位は、そのままAVDD1の電位と同じである。実際にはリセットトランジスタ16のゲートとの寄生容量により、AVDD1=2.5Vよりも若干少なくなる(図中、25で示す)。

【0016】

また、図6は読出し時のポテンシャルを示している。転送ゲート18に“ON”電圧を印加することによって、信号電荷(Qsig)24をFD部17に読み出す。

ここで、信号電荷(Qsig)24のうち、大部分の信号電荷(Qsig1)30がFD部17へ読み出されるが、一部の信号電荷(Qsig2)29はフォトダイオード23に残る。

この残った信号電荷は残像なり、画像特性を劣化させる。

ここで、残像が発生する原因は、転送ゲート18に印加する電圧が相対的に小さいため、転送ゲート18のゲート下にポテンシャルバリア31が発生し、フォトダイオード23の信号電荷を完全に読み出すことができないからである。

【0017】

このように、従来の増幅型固体撮像装置において、画素部を駆動する電圧が小さくなればなるほど、この残像の発生の可能性が大きくなり、画質を劣化させてしまう。

【0018】

図7は、転送ゲート18を“OFF”した後のポテンシャルを示している。図示のように、転送ゲート18のゲート電圧(ΦTG)は0Vになり(図中、32で示す)、フォトダイオード23には信号電荷(Qsig2)29が残されてしまう。

【0019】

以上のように、従来の増幅型固体撮像装置では、画素部を駆動する電圧が小さいために、フォトダイオードの信号電荷を完全に読み出すことができず、残像が発生する原因となる。

また、このような背景から画素部の動作マージンも大きくとれないという問題が生じ、さらに、画素部の構造等が制約を受け、製造工程が煩雑になったり、大きい電源電圧が必要となるといった問題も生じる。

【0020】

本発明の第1の目的は、複数の電源電圧を使うことによって、画素部の動作マージンを大きくしたり、信号電荷の完全転送を図ることが可能な固体撮像装置を提供することにある。

本発明の第2の目的は、製造工程におけるマスク枚数の削減やプロセス工程の短縮を実現できる固体撮像装置を提供することにある。

【0021】

【課題を解決するための手段】

前記目的を達成するため、本発明の第1の観点は、複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源系統の第1の電源電圧の供給を受けて動作し、前記画素部が第2の電源系統の前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、外部から前記第1の電源系統の第1の電源電圧を入力し、前記周辺回路部に供給する第1の電源入力手段と、外部から前記第2の電源系統の第2の電源電圧を入力し、前記画素部に供給する第2の電源入力手段と、前記第1の電源電圧のレベルを変換するレベルシフト手段と、を有し、前記単位画素が、少なくとも受光量に応じた信号電荷を生成する光電変換部と、前記光電変換部によって生成された信号電荷を取り出すための電荷検出部と、前記光電変換部によって生成された信号電荷を前記電荷検出部に転送する転送手段と、前記光電変換部をリセットするリセット手段と、前記電荷検出部の信号電荷を電気信号に変換して出力信号線に出力する増幅手段と、を含み、前記レベルシフト手段は、レベルシフトさせた電源電圧を、前記転送手段および前記リセット手段に供給し、当該転送手段に供給する電源電圧値は、前記リセット手段に供給する電源電圧値より高く設定して供給する。

【0022】

また、本発明の第2の観点は、複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源電圧の供給を受けて動作し、前記画素部が前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、外部から単一レベルの電源電圧を入力する電源入力手段と、前記電源入力手段によって入力された電源電圧のレベルを前記第1の電源電圧および/または第2の電源電圧に変換するレベルシフト手段と、を有し、前記レベルシフト手段によって生成された第1の電源電圧を前記周辺回路部に選択的に供給し、生成された第2の電源電圧を前記画素部に選択的に供給し、前記単位画素が、少なくとも受光量に応じた信号電荷を生成する光電変換部と、前記光電変換部によって生成された信号電荷を取り出すための電荷検出部と、前記光電変換部によって生成された信号電荷を前記電荷検出部に転送する転送手段と、前記光電変換部をリセットするリセット手段と、前記電荷検出部の信号電荷を電気信号に変換して出力信号線に出力する増幅手段と、を含み、前記レベルシフト手段は、レベルシフトさせた電源電圧を、前記転送手段および前記リセット手段に供給し、当該転送手段に供給する電源電圧値は、前記リセット手段に供給する電源電圧値より高く設定して供給する。

【0023】

本発明の固体撮像装置では、外部から複数の異なる電源電圧を入力し、この複数の電源電圧を画素部及び周辺回路部に選択的に供給するようにしたことから、複数の電源電圧を使うことにより、各部分に最適な消費電力の設定が可能となり、特に画素部に必要な第2の電源電圧を有効に設定できる。

したがって、各部の動作マージンが拡大し、画素部を含む回路部分の消費電力を削減することができ、さらに画素部における信号電荷の完全転送を図ることが可能となる。

また、通常はイオン注入マスクで打ち分けているトランジスタの閾値Vthの変更が不要となるので、イオン注入作業時におけるマスク枚数を大幅に削減でき、プロセス工程の短縮を実現できる。

【0024】

また、本発明の固体撮像装置では、外部から電源電圧からレベルシフト手段を用いて複数の異なる電源電圧を生成し、この複数の異なる電源電圧を画素部及び周辺回路部に選択的に供給するようにしたことから、複数の電源電圧を使うことにより、各部分に最適な消費電力の設定が可能となり、特に画素部に必要な第2の電源電圧を有効に設定できる。

したがって、各部の動作マージンが拡大し、画素部を含む回路部分の消費電力を削減することができ、さらに画素部における信号電荷の完全転送を図ることが可能となる。

【0025】

また、通常はイオン注入マスクで打ち分けているトランジスタの閾値Vthの変更が不要となるので、イオン注入作業時におけるマスク枚数を大幅に削減でき、プロセス工程の短縮を実現できる。

【0026】

【発明の実施の形態】

以下、本発明による固体撮像装置の実施の形態について説明する。

【0027】

本発明の実施の形態による固体撮像装置は、複数レベルの電源電圧を半導体チップの外部から供給したり、あるいは半導体チップ内に昇圧手段を設けることにより、画素部には高電圧を印加し、周辺回路部には低電圧を印加し、FD部を高圧でリセットすることで、FD部の動作ダイナミックレンジを拡大するようにし、残像等の問題を解決するものである。

【0028】

図8は、本発明の第1実施形態による増幅型固体撮像装置の構成例を示す概略平面図である。なお、図1に示す回路と共通の機能を有する構成部については便宜上、同一符号を付して説明する。

【0029】

この固体撮像装置は、撮像信号をアナログ信号で出力する構成例であり、半導体チップ1上に、2次元配列で多数の単位画素を配置した画素部2と、各種のタイミング信号を生成するタイミングジェネレータ部3と、画素部2からの各画素行のアナログ画素信号を格納するラインメモリ部(カラム領域)4Aと、ラインメモリ部4Aを水平方向に選択して駆動する水平駆動部5と、各画素行を選択して駆動する垂直駆動部6と、画素部2から読み出された画素信号に対して所定の信号処理を行って出力する出力アンプ部51等が形成されている。

【0030】

また、このような半導体チップ1は、第1の電源系統であるデジタル電源系統として、電源端子45から第1のデジタル電源電圧(DVDD1)、電源端子46から第1のデジタルグラウンド電圧(DVSS1)、電源端子47から第2のデジタル電源電圧(DVDD2)、電源端子48から第2のデジタルグラウンド電圧(DVSS2)、電源端子49から第3のデジタル電源(DVDD3)49、及び電源端子50から第3のデジタルグラウンド電圧(DVSS3)が供給されている。

【0031】

また、半導体チップ1は、第2の電源系統であるアナログ電源系統として、電源端子40から第1のアナログ電源電圧(AVDD1)、電源端子41から第1のアナロググラウンド電圧(AVSS1)、電源端子42から第2のアナログ電源電圧(AVDD2)、及び電源端子43から第2のアナロググラウンド電圧(AVSS2)が供給されている。

なお、半導体チップ1には、基板コンタクト(VSUB)44が設けられている。

【0032】

このような回路構成において、画素部2、ラインメモリ部4A、出力アンプ部51は第2の電源系統、すなわちアナログ電源で駆動されるアナログ回路部であり、TG部3、垂直駆動部6、水平駆動部5は第1の電源系統、すなわちデジタル電源で駆動されるデジタル回路部である。

【0033】

このような固体撮像装置において、半導体プロセス世代が進んでいくと、使用する電源電圧が小さくなっていく。たとえば0.35μmプロセスでは3.3V、0.25μmプロセスでは2.5V、0.18μmプロセスでは1.8V、などである。

【0034】

本実施形態では、半導体チップ1の外部から電源電圧値の異なる複数の電源を供給するようにしたものである。

すなわち、図8において、DVDD1=DVDD2ではない。例えばDVDD1=3.3Vとすると、DVDD2=2.5Vである。このような電源電圧値を固体撮像装置の外部から半導体チップ1に供給することによって、特にフォトダイオード23からの信号電荷の完全転送が可能となる。

【0035】

また、アナログ用の電源電圧値AVDD1とAVDD2を異なる電圧で使うこともできる。画素部2の電源をAVDD1とし、ラインメモリ部4A、出力アンプ部51の電源をAVDD2とすることによって、回路の各部分に最適な消費電力の設定が可能となってくる。

これにより、各部の動作マージンが拡大し、アナログ部分の消費電力を削減することができる。

【0036】

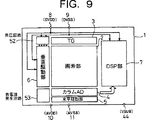

図9は、本発明の第2実施形態による増幅型固体撮像装置の構成例を示す概略平面図である。なお、図1に示す回路と共通の機能を有する構成部については便宜上、同一符号を付して説明する。

【0037】

この固体撮像装置は、撮像信号をデジタル信号に変換し、さらにデジタル信号処理を施して出力する構成例であり、半導体チップ1上に、2次元配列で多数の単位画素を配置した画素部2と、各種のタイミング信号を生成するタイミングジェネレータ部3と、カラムCDSやカラムAD等の出力カラム部(カラム領域)4と、この出力カラム部4を水平方向に選択して駆動する水平駆動部5と、各画素行を選択して駆動する垂直駆動部6と、画素部2から読み出された画素信号に対して信号処理を行う信号処理部(DSP)7と、外部からの第2の電源電圧としてのアナログ電源電圧及び第1の電源電圧としてのデジタル電源電圧を昇圧する昇圧回路52と、外部からのアナログ電源電圧及びデジタル電源電圧によって負電源を生成する負電源発生回路53等が形成されている。

【0038】

そして、このような半導体チップ1は、第1の電源系統であるデジタル電源系統として、電源端子8からデジタル電源電圧(DVDD)、電源端子9からデジタルグラウンド電圧(DVSS)が供給され、第2の電源系統であるアナログ電源系統として、電源端子10からアナログ電源電圧(AVDD)、電源端子11からアナロググラウンド電圧(AVSS)が供給されている。

なお、半導体チップ1には、基板コンタクト(VSUB)44が設けられている。

【0039】

本実施形態では、デジタル電源電圧(DVDD)とアナログ電源電圧(AVDD)10は、ともに同じ電源電圧値であり、これを昇圧回路52において電源電圧AVDD=DVDDを昇圧し、さらに負電源発生回路53によって負電源を生成することにより、半導体チップ1の内部で別の電源電圧値を生成している。

【0040】

このように半導体チップ1の外部から供給される電源電圧値は単一でも、チップ内部で複数の電源電圧を作り出すことによって、特に画素部2の動作マージンを大幅に拡大することができる。

また、この結果、通常はイオン注入マスクで打ち分けているトランジスタの閾値Vthの変更が不要となるので、イオン注入作業時におけるマスク枚数を大幅に削減することが可能となる。

【0041】

図10は、本発明の第3実施形態による増幅型固体撮像装置の構成例を示す概略平面図である。なお、なお、図1に示す回路と共通の機能を有する構成部については便宜上、同一符号を付して説明する。

【0042】

この固体撮像装置は、図8に示す第1実施形態の構成例をデジタル出力とし、さらにデジタル信号処理を行う構成に変形した構成例であり、半導体チップ1上に、2次元配列で多数の単位画素を配置した画素部2と、各種のタイミング信号を生成するタイミングジェネレータ部3と、カラムCDSやカラムAD等の出力カラム部(カラム領域)4と、この出力カラム部4を水平方向に選択して駆動する水平駆動部5と、各画素行を選択して駆動する垂直駆動部6と、画素部2から読み出された画素信号に対して信号処理を行う信号処理部(DSP)7等が形成されている。

【0043】

また、このような半導体チップ1は、第1の電源系統であるデジタル電源系統として、電源端子45から第1のデジタル電源電圧(DVDD1)、電源端子46から第1のデジタルグラウンド電圧(DVSS1)、電源端子47から第2のデジタル電源(DVDD2)、電源端子48から第2のデジタルグラウンド電圧(DVSS2)、電源端子49から第3のデジタル電源(DVDD3)49、及び電源端子50から第3のデジタルグラウンド電圧(DVSS3)が供給されている。

【0044】

また、半導体チップ1は、第2の電源系統であるアナログ電源系統として、電源端子40から第1のアナログ電源電圧(AVDD1)、電源端子41から第1のアナロググラウンド電圧(AVSS1)、電源端子42から第2のアナログ電源電圧(AVDD2)、及び電源端子43から第2のアナロググラウンド電圧(AVSS2)が供給されている。

なお、半導体チップ1には、基板コンタクト(VSUB)44が設けられている。

【0045】

この第3実施形態においても、電源電圧値の異なる複数電源を半導体チップ1の外部から供給することによって、回路の動作マージンを拡大し、さらに各回路ブロックの消費電力の最適化を実行することが可能となる。

【0046】

次に、本発明の第4実施形態として、上述した画素部2の単位画素と、その駆動を行う垂直駆動部6の構成例について説明する。

【0047】

図11は、本発明の第4実施形態における単位画素と垂直駆動部の構成例を示すブロック図である。

【0048】

上述のように画素部2には、2次元配列で多数の単位画素55が設けられており、本例の各単位画素55は、フォトダイオード23、転送トランジスタ(転送ゲートTG)18、電荷検出部(FD部)17、増幅トランジスタ56、アナログ電源端子(AVDD1)40、選択(アドレス)トランジスタ57、垂直信号線59等からなる。

【0049】

また、画素部2を駆動する垂直駆動部6は、画素行を垂直方向に順次選択する垂直レジスタ部64と、この垂直レジスタ部64による選択信号のレベルを電源電圧によってシフトするレベルシフタ回路61、62、63等からなる。

【0050】

各レベルシフタ回路61、62、63は、選択トランジスタ57、リセットトランジスタ16、転送ゲート18のゲート電圧を制御し、制御パルスΦR(リセット用)、ΦTG(転送ゲート用)、ΦA(選択用)を単位画素55の各トランジスタに印加する。

【0051】

図11の例では、転送ゲート18と選択トランジスタ57に電源電圧DVDD1よりも大きな電圧を印加したいので、レベルシフタ回路61と63によって、DVDD1よりも大きな電源電圧DVDD2を供給している。

このように、垂直駆動部6の構成は複雑になるが、電源電圧とGND電圧間の電圧差が大きいので、画素の動作マージンを大きくできる。

この結果、通常はイオン注入マスクで打ち分けているトランジスタの閾値Vthの変更が不要となるので、イオン注入作業時におけるマスク枚数を大幅に削減することが可能となる。

【0052】

図12A〜Cは、図11に示す各制御パルスの動作タイミングを示すタイミングチャートである。 選択トランジスタ57に印加されるパルスΦAをDVDD2の電圧にする(DVDD2>DVDD1)。こうすることによって、選択トランジスタ57のチャネル電圧は電源電圧DVDD1よりも大きくできる。その後、リセットトランジスタ16にパルスΦR=DVDD1を印加する。これにより、電荷検出部17がリセットできる。

【0053】

電荷検出部17は完全に画素部2の電源電圧AVDD1と同一の電位までリセットしたいので、この図ではΦR=DVDD1でも完全リセットできる閾値電圧になっている(ΦRもDVDD2を使ってよいが、図12A〜12Cでは使わない場合を示した)。その後、転送ゲート18にΦTG=DVDD2を印加することによって、フォトダイオード23の信号電荷を電荷検出部17に読み出すことができる。

【0054】

図13は、図11に示す実施形態の画素部2の積層構造を示す断面図である。

【0055】

図示のように、シリコン基板12上にはPウェル13が形成されており、このPウェル13上に、素子分離領域(本例ではLOCOS素子分離であるがSTI等の場合もある)14と、電源領域(AVDD)15と、リセットトランジスタのリセットゲート(Reset)16と、電荷検出部17と、フォトダイオード23の信号電荷を電荷検出部17に転送する転送ゲート(TG)18と、フォトダイオード23を構成するP+型受光層19及びN型光電変換層20等が形成されている。

【0056】

電荷検出部17は、コンタクト17A等を介して増幅トランジスタ56のゲートに接続され、電源領域15は、コンタクト15A等を介して第1のアナログ電源端子(AVDD1)40に接続されている。

【0057】

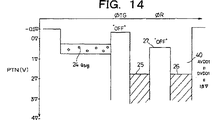

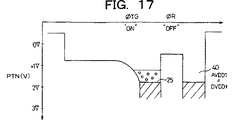

図14〜図18は、図13に示した断面図に対応するポテンシャル電位を示す説明図であり、縦軸がポテンシャル電位(V)、横軸が図4の基板表面における各素子の形成位置に対応している。なお、既に説明した図3〜図7と共通の要素については、同一符号を付してある。

【0058】

まず、本例において画素部2の電源電圧(AVDD1)は、この図では1.8Vである(図中、26で示す)。

そして、図14においては、転送ゲート18とリセットトランジスタ16は、ΦTG=ΦR=“OFF”状態となっている。フォトダイオード23の領域には、信号電荷(Qsig)24が蓄積されている。

【0059】

次に、図15は、ΦTG=“OFF”、ΦR=“ON”の状態でのポテンシャル電位を示したものである。ここで、電荷検出部(FD部)17は、画素部の電源電圧AVDD1によって1.8Vにセットされる。

【0060】

次に、図16は、ΦTG=“OFF”、ΦR=“OFF”の状態でのポテンシャル電位を示したものである。ここで、リセットトランジスタ16をOFFしたことによって、電荷検出部17の電位が変動する。これは、リセットトランジスタ16のゲートと電荷検出部17との間の寄生容量による影響である。

【0061】

次に、図17は、ΦTG=“ON”、ΦR=“OFF”の状態でのポテンシャル電位を示したものである。ΦTG=“ON”=DVDD2の電圧はDVDD1よりも大きく、この場合、DVDD2=2.5V(>DVDD1)となる。

したがって、転送ゲート18に印加される電圧が大きいので、フォトダイオード23の信号電荷(Qsig)24を完全に電荷検出部17に読み出すことが可能となる。

【0062】

次に、図18は、ΦTG=“OFF”、ΦR=“OFF”の状態でのポテンシャル電位を示している。

【0063】

以上のように、本実施形態では、たとえば、ΦTG=“ON”=DVDD2というように、画素部2の電源電圧AVDD1=DVDD1よりも大きい電圧を使用することにより、フォトダイオード23の信号電荷を完全に転送することが可能となる。

【0064】

図19は、本発明の第5実施形態における単位画素と垂直駆動部の構成例を示すブロック図である。

【0065】

この第5実施形態は、外部から複数レベルの電源電圧を供給する構成であって、上述した図11の第4実施形態と異なる画素構成を有するものである。

【0066】

各単位画素55の構成要素は、上述した第4実施形態と同様に、フォトダイオード23、転送トランジスタ18、増幅トランジスタ56、選択トランジスタ57、リセットトランジスタ16等であるが、その接続状態が異なっている。

また、垂直駆動部6は、垂直レジスタ部64、2つのレベルシフタ回路65、66等からなる。

【0067】

図20A〜Cは、図19に示す各制御パルスの動作タイミングを示すタイミングチャートである。

【0068】

選択トランジスタ57を活性化するために、ΦR=“ON”=DVDD1(=AVDD1)が印加される。

これにより、選択トランジスタが活性化し、この画素が選択される(実際は行方向に複数配置されているので行方向の全ての画素が活性化する)。

その後、リセットトランジスタ16を活性化する。つまり、ΦR=DVDD1が印加され、電荷検出部17が画素部2の電源電圧(AVDD1)にリセットされる。

【0069】

次に、転送ゲート18にパルスを印加する。すなわち、ΦTG=“ON”=DVDD2>DVDD1とすることによって、フォトダイオード23の信号を完全に電荷検出部17へ転送することが可能となる。

また、複数の電源電圧を用いることで、画素部2に用いるトランジスタの閾値Vthを1種類にでき、マスク枚数の削減が可能となる。

【0070】

図21は、本発明の第6実施形態における単位画素と垂直駆動部の構成例を示すブロック図である。

【0071】

この第6実施形態は、上述した図9の第2実施形態と同様に、外部から単一の電源電圧を供給する構成であって、チップ内部に昇圧回路52を形成し、複数電源電圧を生成する構成の場合である。

【0072】

そして、単位画素55は、フォトダイオード23、転送ゲート18、電荷検出部17、増幅トランジスタ56、リセットトランジスタ16、選択トランジスタ57等からなる。また、垂直駆動部6は、垂直レジスタ部64と、レベルシフタ回路71、72、73と、各レベルシフタ回路71、72、73への電源を供給する昇圧回路52からなる。

【0073】

また、レベルシフタ回路71、72、73からは単位画素を駆動するために、Φpパルス67、ΦRパルス22、ΦTGパルス21、ΦAパルス60の4本の制御信号が供給されている。

【0074】

図22A〜Eは、図21に示す各制御パルスの動作タイミングを示すタイミングチャートである。

図23〜図28は、本実施形態におけるポテンシャル電位を示す説明図であり、縦軸がポテンシャル電位(V)、横軸が基板表面における各素子の形成位置に対応している。なお、既に説明した図3〜図7と共通の要素については、同一符号を付してある。

【0075】

図21の回路において、最初の状態は図22Aと図23に対応する。

次に、昇圧回路52を活性化する。これによって、昇圧回路52が動作し、昇圧電圧(DVDD1)68、(DVDD2)69、(DVDD3)70が発生する。つまり、図22Bと図24に対応する。

この時、リセットトランジスタ16のドレイン端74の電圧はVDである。次に、選択トランジスタ57を選択するパルス(ΦA)60に電源電圧(DVDD2)を印加する。これによって画素が活性化される。

【0076】

次に、リセットトランジスタ16を選択するパルス(ΦR)22に電源電圧(DVDD1)を印加する。図22Cと図25が対応する。これによって、電荷検出部17の電圧は昇圧電圧DVDD3=VDにセットされる。つまり、電荷検出部17は昇圧された電圧DVDD3にリセットされたことになる。

【0077】

次に、リセットトランジスタ16の選択するパルス(ΦR)22を“OFF”する。これは図22Dと図26に対応する。

この後、転送ゲート(TG)18に電源電圧DVDD1を印加する。これは図22Eと図27が対応する。これにより、フォトダイオード23の信号電荷(Qsig)24が、電荷検出部18に読み出される。この時、電荷検出部18の電圧が大きいので、読み出される信号電荷量を大きくできる。つまり、信号のダイナミックレンジを大きくすることが可能である。

【0078】

また、図27に破線領域75で示すように、大きなドレイン電界によるパンチスルー効果を得ることが可能であるので、完全転送をやりやすくなる。つまり、画素の電源電圧(AVDD1)が小さくなっても、このような本実施の形態を用いることで、フォトダイオードの信号電荷を完全に読み出すことができるようになる。

転送ゲート(TG)18を“OFF”する。これは図22Fと図28に対応する。

【0079】

図29は、本発明の第7実施形態における単位画素の構成例を示すブロック図であり、図30A〜Fは、図29に示す各制御パルスの動作タイミングを示すタイミングチャートである。

【0080】

図29において、単位画素55は、フォトダイオード23、転送ゲート18、電荷検出部17、増幅トランジスタ56、リセットトランジスタ16、選択トランジスタ57等からなる。

増幅トランジスタ56のドレイン端は、単位画素55の電源電圧(AVDD1)40に接続されており、リセットトランジスタ16のドレイン端は制御線(Φp)76に接続されている。

【0081】

次に、このような単位画素55の動作を図30A〜Fを用いて説明する。

最初、ΦR1=“H”、Φp=“H”状態(第2の状態)から、Φp=“H”→“L”(第1の状態)に切り替る。その後、ΦR2=“L”→“H”とパルスが印加される。これによってリセットトランジスタ16のゲート電圧(VG)は接地電位GNDから上昇する。

【0082】

次に、ΦR1=“H”→“L”にし、続けてΦp=“L”→“H”にする。そうすると、リセットトランジスタ16のゲート(VG)とドレイン端(Φp)の寄生容量によるカップリングにより、リセットトランジスタのゲート電圧が上昇し、DVDD1以上にすることができる。これによって、電荷検出部17の電位VFDをDVDD1にセットできる。

これは、昇圧回路52や、ディプリーション型のトランジスタを使用しなくても、電荷検出部17を完全に電源電圧でリセットできるやり方であり、マスク枚数の削減などの手法に有利である。

【0083】

図31は、本発明の第8実施形態における単位画素の構成例を示すブロック図であり、図32A〜Eは、図31に示す各制御パルスの動作タイミングを示すタイミングチャートである。

【0084】

図31において、単位画素55は、フォトダイオード23、転送ゲート18、電荷検出部17、増幅トランジスタ56、リセットトランジスタ16、選択トランジスタ57等からなる。

【0085】

本実施形態において、アナログ電源電圧端子(AVDD1)40→選択トランジスタ57→増幅トランジスタ56→垂直信号線59の順番が重要である。以下、この動作タイミングを図32A〜Eを用いて説明する。

【0086】

まず、画素を活性化させない状態で、リセットトランジスタ16を“ON”にする。そうすると、電荷検出部17の電位VFDは電源DVDD1にセットされる。この例では、DVDD1=AVDD1であるので、電荷検出部17の電圧VFDは画素の電源電圧になる。

【0087】

次に、選択トランジスタ57を活性化するため、ΦAが印加される。これによってノード84の電圧Vnが0V→中間電圧に昇圧される。ノード84と電荷検出部17は寄生容量でカップリングしていて、電荷検出部17はフローティング状態であるので、図32Eに86で示すように電荷検出部17のVFDは、DVDD1よりも大きな電圧に昇圧される。

このように、リセットするタイミング87を、画素を選択するタイミング88よりも先行させることによって、電荷検出部17の電位VFDを昇圧させることができる。

これは、駆動タイミングの工夫だけで実現できるので、閾値の異なるトランジスタを使わなくて良いし、昇圧回路も少なくて済む。

【0088】

図33は、本発明の第9実施形態における単位画素の構成例を示すブロック図である。

上述した第8実施形態では、図32Cの83に示すように、転送ゲートにパルスを印加しない場合の電圧を負電圧(DVSS3)とした。これによって、蓄積期間中のフォトダイオードに流れ込むリーク電流を抑圧することができる。

そこで、第9実施形態では、上述のような負電圧を実現するための具体的手段について説明する。

【0089】

たとえば図31に示すようなレベルシフト回路80、81等は、図33に示すような構造を有するものである。

すなわち、このレベルシフト回路は、垂直レジスタ部64からの信号を受けるインバータ部(トランジスタ89、92)と、その後のGND側の電圧をDVSS1(=0V)からDVSS2(<0V)へシフトする回路(トランジスタ90、91、93、94)とを有するものである。

このような回路構成により、DVDD2に負電圧を印加すれば、このレベルシフト回路が“OFF”しているときに、画素部2への転送ゲートパルスΦTGには“負電圧”が印加されることになる。

【0090】

図34は、このようなレベルシフト回路の積層構造の具体例を示す概略断面図である。図示のように、シリコン基板12上の画素部2には、全体的にセンサPウェル領域98が形成されており、センサPウェル電圧(AVSS1)が印加されている。

また、このセンサPウェル領域98の周囲を取り囲むようにNウェル領域99が形成され、その外側に第2のPウェル領域100が形成されている。そして、この第2のPウェル領域100には、コンタクト104によってDVSS2が印加され、Pウェル電圧ごと負電源となっている。

このPウェル領域100に、図33に示した破線枠106の部分(トランジスタ93、94)が形成されることになる。

また、第2のPウェル領域100の外側には、さらにNウェル領域101が形成され、基板コンタクト44が形成される。

なお、さらに外側の周辺回路部は、Nウェル領域103、Pウェル領域102等で形成され、Pウェル領域102にはコンタクト105によってDVSS1が印加されている。このような構造によって、画素部2に負電圧を印加するためのウェル構造を形成することが可能となる。

【0091】

以上、本発明の具体的構成例について説明したが、本発明はさらに他の構造の増幅型固体撮像装置(CMOSイメージセンサ)にも広く採用できるものであり、特に低電圧化した場合に非常に有効な技術を提供し得るものである。

【0092】

本発明の固体撮像装置は、複数の電源電圧を使うことにより、各部分に最適な消費電力の設定が可能となり、特に画素部に必要な第2の電源電圧を有効に設定できるため、各部の動作マージンが拡大し、画素部を含むアナログ部分の消費電力を削減することができ、さらに画素部における信号電荷の完全転送を図ることが可能となることから、良好な画質を維持することができ、デジタルカメラ等の撮像装置に適用可能である。

【0093】

【発明の効果】

以上説明したように本発明の固体撮像装置によれば、外部から複数の電源電圧を入力し、この複数の電源電圧を画素部及び周辺回路部に選択的に供給するようにしたことから、複数の電源電圧を使うことにより、各部分に最適な消費電力の設定が可能となり、特に画素部に必要なアナログ電源電圧を有効に設定できるため、各部の動作マージンが拡大し、画素部を含むアナログ部分の消費電力を削減することができ、さらに画素部における信号電荷の完全転送を図ることが可能となる効果がある。

また、通常はイオン注入マスクで打ち分けているトランジスタの閾値Vthの変更が不要となるので、イオン注入作業時におけるマスク枚数を大幅に削減でき、プロセス工程の短縮を実現できる効果がある。

また、本発明の固体撮像装置によれば、外部から電源電圧からレベルシフト手段を用いて複数の電源電圧を生成し、この複数の電源電圧を画素部及び周辺回路部に選択的に供給するようにしたことから、複数の電源電圧を使うことにより、各部分に最適な消費電力の設定が可能となり、特に画素部に必要なアナログ電源電圧を有効に設定できるため、各部の動作マージンが拡大し、画素部を含むアナログ部分の消費電力を削減することができ、さらに画素部における信号電荷の完全転送を図ることが可能となる効果がある。

また、通常はイオン注入マスクで打ち分けているトランジスタの閾値Vthの変更が不要となるので、イオン注入作業時におけるマスク枚数を大幅に削減でき、プロセス工程の短縮を実現できる効果がある。

【図面の簡単な説明】

【図1】 図1は、従来の増幅型固体撮像装置の構成例を示す概略平面図である。

【図2】 図2は、図1に示す従来例における画素部の積層構造を断面図である。

【図3】 図3は、図1に示す従来例のポテンシャル電位の遷移を示す説明図である。

【図4】 図4は、図1に示す従来例のポテンシャル電位の遷移を示す説明図である。

【図5】 図5は、図1に示す従来例のポテンシャル電位の遷移を示す説明図である。

【図6】 図6は、図1に示す従来例のポテンシャル電位の遷移を示す説明図である。

【図7】 図7は、図1に示す従来例のポテンシャル電位の遷移を示す説明図である。

【図8】 図8は、本発明の第1実施形態による増幅型固体撮像装置の構成例を示す概略平面図である。

【図9】 図9は、本発明の第2実施形態による増幅型固体撮像装置の構成例を示す概略平面図である。

【図10】 図10は、本発明の第3実施形態による増幅型固体撮像装置の構成例を示す概略平面図である。

【図11】 図11は、本発明の第4実施形態における単位画素と垂直駆動部の構成例を示すブロック図である。

【図12】 図12A〜Cは、図11に示す実施形態の動作タイミングを示すタイミングチャートである。

【図13】 図13は、図11に示す実施形態の画素部の積層構造を示す断面図である。

【図14】 図14は、図11に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図15】 図15は、図11に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図16】 図16は、図11に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図17】 図17は、図11に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図18】 図18は、図11に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図19】 図19は、本発明の第5実施形態における単位画素と垂直駆動部の構成例を示すブロック図である。

【図20】 図20A〜Cは、図19に示す実施形態の動作タイミングを示すタイミングチャートである。

【図21】 図21は、本発明の第6実施形態における単位画素と垂直駆動部の構成例を示すブロック図である。

【図22】 図22A〜Eは、図21に示す実施形態の動作タイミングを示すタイミングチャートである。

【図23】 図23は、図21に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図24】 図24は、図21に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図25】 図25は、図21に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図26】 図26は、図21に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図27】 図27は、図21に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図28】 図28は、図21に示す実施形態のポテンシャル電位の遷移を示す説明図である。

【図29】 図29は、本発明の第7実施形態における単位画素の構成例を示すブロック図である。

【図30】 図30A〜Fは、図29に示す実施形態の動作タイミングを示すタイミングチャートである。

【図31】 図31は、本発明の第8実施形態における単位画素の構成例を示すブロック図である。

【図32】 図32A〜Eは、図31に示す実施形態の動作タイミングを示すタイミングチャートである。

【図33】 図33は、本発明の第9実施形態における単位画素の構成例を示すブロック図である。

【図34】 図34は、図33に示すレベルシフト回路の積層構造の一例を示す概略断面図である。

【符号の説明】

1……半導体チップ、2……画素部、3……タイミングジェネレータ部、4……出力カラム部、4A……ラインメモリ部、5……水平駆動部、6……垂直駆動部、7……信号処理部(DSP)、8、45、47、49……デジタル電源、10、40、42……アナログ電源、51……出力アンプ部、52……昇圧回路、53……負電源発生回路、61〜63、65、66、71〜73、80、81……レベルシフタ回路。

Claims (20)

- 複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源系統の第1の電源電圧の供給を受けて動作し、前記画素部が第2の電源系統の前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、

外部から前記第1の電源系統の第1の電源電圧を入力し、前記周辺回路部に供給する第1の電源入力手段と、

外部から前記第2の電源系統の第2の電源電圧を入力し、前記画素部に供給する第2の電源入力手段と、

前記第1の電源電圧のレベルを変換するレベルシフト手段と、を有し、

前記単位画素が、

少なくとも受光量に応じた信号電荷を生成する光電変換部と、

前記光電変換部によって生成された信号電荷を取り出すための電荷検出部と、

前記光電変換部によって生成された信号電荷を前記電荷検出部に転送する転送手段と、

前記光電変換部をリセットするリセット手段と、

前記電荷検出部の信号電荷を電気信号に変換して出力信号線に出力する増幅手段と、を含み、

前記レベルシフト手段は、

レベルシフトさせた電源電圧を、前記転送手段および前記リセット手段に供給し、当該転送手段に供給する電源電圧値は、前記リセット手段に供給する電源電圧値より高く設定して供給する

固体撮像装置。 - 前記画素部に隣接して各画素行の信号を蓄積するカラム領域を有する

ことを特徴とする請求項1記載の固体撮像装置。 - 前記第1および第2の電源電圧の少なくとも1つは負電源電圧である

請求項1または2記載の固体撮像装置。 - 少なくとも第1の電源電圧値で動作する回路領域と、第2の電源電圧値で動作する回路領域とを有し、電源電圧値の異なる各回路領域を接続する領域に前記レベルシフタ手段を挿入して電源電圧値の変換を行う

請求項1から3のいずれか一に記載の固体撮像装置。 - 前記画素部を駆動するための垂直駆動部を有し、前記リセット手段となるリセットトランジスタのソースが前記電荷検出部に接続され、前記リセットトランジスタのドレインが前記垂直駆動部により制御されるドレイン制御線に接続された

請求項1から4のいずれか一に記載の固体撮像装置。 - 前記ドレイン制御線には、信号電荷の読み出し期間以外の期間中は第3の電源電圧が印加されるとともに、信号電荷の読み出し期間中は前記第3の電源電圧より高い第4の電源電圧が印加され、この第4の電源電圧によって前記電荷検出部のリセット及び信号電荷の読み出しを含む一連の読出し動作が行われ、前記信号電荷の読出し動作終了後に前記ドレイン制御線の印加電圧が前記第3の電源電圧に戻る

請求項5記載の固体撮像装置。 - 複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源系統の第1の電源電圧の供給を受けて動作し、前記画素部が第2の電源系統の前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、

外部から前記第1の電源系統の第1の電源電圧を入力し、前記周辺回路部に供給する第1の電源入力手段と、

外部から前記第2の電源系統の第2の電源電圧を入力し、前記画素部に供給する第2の電源入力手段と、

前記画素部を駆動するための垂直駆動部と、を有し、

前記単位画素が、

少なくとも受光量に応じた信号電荷を生成する光電変換部と、

前記光電変換部によって生成された信号電荷を取り出すための電荷検出部と、

前記光電変換部によって生成された信号電荷を前記電荷検出部に転送する転送手段と、

前記光電変換部をリセットするリセット手段と、

前記電荷検出部の信号電荷を電気信号に変換して出力信号線に出力する増幅手段と、を含み、

前記リセット手段となるリセットトランジスタのソースが前記電荷検出部に接続され、前記リセットトランジスタのドレインが前記垂直駆動部により制御されるドレイン制御線に接続され、

前記リセットトランジスタのゲートをフローティング状態に制御する制御トランジスタを有し、

前記ドレイン制御線が第1の状態時に前記リセットトランジスタのゲートを第2の状態でホールドすることによって第1の電圧にセットし、前記ドレイン制御線を第2の状態にすることにより、容量カップリングによってリセットトランジスタのゲートを第1の電圧よりも大きい第2の電圧にセットする

固体撮像装置。 - 複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源系統の第1の電源電圧の供給を受けて動作し、前記画素部が第2の電源系統の前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、

外部から前記第1の電源系統の第1の電源電圧を入力し、前記周辺回路部に供給する第1の電源入力手段と、

外部から前記第2の電源系統の第2の電源電圧を入力し、前記画素部に供給する第2の電源入力手段と、

前記画素部を駆動するための垂直駆動部と、を有し、

前記単位画素が、

少なくとも受光量に応じた信号電荷を生成する光電変換部と、

前記光電変換部によって生成された信号電荷を取り出すための電荷検出部と、

前記光電変換部によって生成された信号電荷を前記電荷検出部に転送する転送手段と、

前記光電変換部をリセットするリセットトランジスタと、

前記電荷検出部の信号電荷を電気信号に変換して出力信号線に出力する増幅手段と、

画素行を選択するための選択トランジスタと、

を含み、

前記垂直駆動部の駆動より、前記リセットトランジスタをON状態にすることで前記電荷検出部を第1の電圧にセットし、前記リセットトランジスタをOFF状態にすることで前記電荷検出部をフローティング状態とし、前記選択トランジスタをON状態にすることによって前記選択トランジスタのソースと前記電荷検出部の寄生容量により、前記電荷検出部を第2の電圧に昇圧する

固体撮像装置。 - 複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源系統の第1の電源電圧の供給を受けて動作し、前記画素部が第2の電源系統の前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、

外部から前記第1の電源系統の第1の電源電圧を入力し、前記周辺回路部に供給する第1の電源入力手段と、

外部から前記第2の電源系統の第2の電源電圧を入力し、前記画素部に供給する第2の電源入力手段と、

前記画素部を駆動するための垂直駆動部と、を有し、

前記単位画素が、

少なくとも受光量に応じた信号電荷を生成する光電変換部と、

前記光電変換部によって生成された信号電荷を取り出すための電荷検出部と、

前記光電変換部によって生成された信号電荷を前記電荷検出部に転送する転送手段と、

前記光電変換部をリセットするリセットトランジスタと、

前記電荷検出部の信号電荷を電気信号に変換して出力信号線に出力する増幅トランジスタと、

画素行を選択するための選択トランジスタと、

少なくとも1個の電源電圧源と、

を含み、

単位画素内の接続順序が電源電圧源、選択トランジスタ、増幅トランジスタ、出力信号線の順であり、前記垂直駆動部による前記画素部の駆動の順序が先に前記リセットトランジスタを一度ONし、その後、前記選択トランジスタをONすることにより、前記光電変換部の信号電荷を読み出す

固体撮像装置。 - 複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源系統の第1の電源電圧の供給を受けて動作し、前記画素部が第2の電源系統の前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、

外部から前記第1の電源系統の第1の電源電圧を入力し、前記周辺回路部に供給する第1の電源入力手段と、

外部から前記第2の電源系統の第2の電源電圧を入力し、前記画素部に供給する第2の電源入力手段と、を有し、

前記第1および第2の電源電圧の少なくとも1つは負電源電圧であり、

半導体基板上の画素部形成領域に第1導電型の第1のウェル領域を形成し、その外周部に第2導電型の第2のウェル領域を形成し、さらにその外周部に第1導電型の第3のウェル領域を形成し、

前記第3のウェル領域に負電源電圧を印加するとともに、この第3のウェル領域内部にnチャネルの絶縁ゲート型電界効トランジスタを形成し、前記nチャネルの絶縁ゲート型電界効トランジスタのソースと前記第3のウェル領域とを同じ負電源電圧とした

固体撮像装置。 - 複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源電圧の供給を受けて動作し、前記画素部が前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、

外部から単一レベルの電源電圧を入力する電源入力手段と、

前記電源入力手段によって入力された電源電圧のレベルを前記第1の電源電圧および/または第2の電源電圧に変換するレベルシフト手段と、を有し、

前記レベルシフト手段によって生成された第1の電源電圧を前記周辺回路部に選択的に供給し、生成された第2の電源電圧を前記画素部に選択的に供給し、

前記単位画素が、

少なくとも受光量に応じた信号電荷を生成する光電変換部と、

前記光電変換部によって生成された信号電荷を取り出すための電荷検出部と、

前記光電変換部によって生成された信号電荷を前記電荷検出部に転送する転送手段と、

前記光電変換部をリセットするリセット手段と、

前記電荷検出部の信号電荷を電気信号に変換して出力信号線に出力する増幅手段と、を含み、

前記レベルシフト手段は、

レベルシフトさせた電源電圧を、前記転送手段および前記リセット手段に供給し、当該転送手段に供給する電源電圧値は、前記リセット手段に供給する電源電圧値より高く設定して供給する

固体撮像装置。 - 前記画素部に隣接して各画素行の信号を蓄積するカラム領域を有する

請求項11記載の固体撮像装置。 - 前記複数の電源電圧の少なくとも1つは負電源電圧である

請求項11または12記載の固体撮像装置。 - 少なくとも第1の電源電圧値で動作する回路領域と、第2の電源電圧値で動作する回路領域とを有し、電源電圧値の異なる各回路領域を接続する領域に前記レベルシフタ手段を挿入して電源電圧値の変換を行う

請求項11から13のいずれか一に記載の固体撮像装置。 - 前記画素部を駆動するための垂直駆動部を有し、前記リセット手段となるリセットトランジスタのソースが前記電荷検出部に接続され、前記リセットトランジスタのドレインが前記垂直駆動部により制御されるドレイン制御線に接続された

請求項11から14のいずれか一に記載の固体撮像装置。 - 前記ドレイン制御線には、信号電荷の読み出し期間以外の期間中は第3の電源電圧が印加されるとともに、信号電荷の読み出し期間中は前記第3の電源電圧より高い第4の電源電圧が印加され、この第4の電源電圧によって前記電荷検出部のリセット及び信号電荷の読み出しを含む一連の読出し動作が行われ、前記信号電荷の読出し動作終了後に前記ドレイン制御線の印加電圧が前記第3の電源電圧に戻る

請求項15記載の固体撮像装置。 - 複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源電圧の供給を受けて動作し、前記画素部が前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、

外部から単一レベルの電源電圧を入力する電源入力手段と、

前記画素部を駆動する垂直駆動部と、

前記電源入力手段によって入力された電源電圧のレベルを前記第1の電源電圧および/または第2の電源電圧に変換するレベルシフト手段と、を有し、

前記レベルシフト手段によって生成された第1の電源電圧を前記周辺回路部に選択的に供給し、生成された第2の電源電圧を前記画素部に選択的に供給し、

前記単位画素が、

少なくとも受光量に応じた信号電荷を生成する光電変換部と、

前記光電変換部によって生成された信号電荷を取り出すための電荷検出部と、

前記光電変換部によって生成された信号電荷を前記電荷検出部に転送する転送手段と、

前記光電変換部をリセットするリセット手段と、

前記電荷検出部の信号電荷を電気信号に変換して出力信号線に出力する増幅手段と、を含み、

前記リセット手段となるリセットトランジスタのソースが前記電荷検出部に接続され、前記リセットトランジスタのドレインが前記垂直駆動部により制御されるドレイン制御線に接続され、

前記リセットトランジスタのゲートをフローティング状態に制御する制御トランジスタを有し、

前記ドレイン制御線が第1の状態時に前記リセットトランジスタのゲートを第2の状態でホールドすることによって第1の電圧にセットし、前記ドレイン制御線を第2の状態にすることにより、容量カップリングによってリセットトランジスタのゲートを第1の電圧よりも大きい第2の電圧にセットする

固体撮像装置。 - 複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源電圧の供給を受けて動作し、前記画素部が前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、

外部から単一レベルの電源電圧を入力する電源入力手段と、

前記画素部を駆動する垂直駆動部と、

前記電源入力手段によって入力された電源電圧のレベルを前記第1の電源電圧および/または第2の電源電圧に変換するレベルシフト手段と、を有し、

前記レベルシフト手段によって生成された第1の電源電圧を前記周辺回路部に選択的に供給し、生成された第2の電源電圧を前記画素部に選択的に供給し、

前記単位画素が、

少なくとも受光量に応じた信号電荷を生成する光電変換部と、

前記光電変換部によって生成された信号電荷を取り出すための電荷検出部と、

前記光電変換部によって生成された信号電荷を前記電荷検出部に転送する転送手段と、

前記光電変換部をリセットするリセットトランジスタと、

前記電荷検出部の信号電荷を電気信号に変換して出力信号線に出力する増幅手段と、

画素行を選択するための選択トランジスタと、

を含み、

前記垂直駆動部の駆動より、前記リセットトランジスタをON状態にすることで前記電荷検出部を第1の電圧にセットし、前記リセットトランジスタをOFF状態にすることで前記電荷検出部をフローティング状態とし、前記選択トランジスタをON状態にすることによって前記選択トランジスタのソースと前記電荷検出部の寄生容量により、前記電荷検出部を第2の電圧に昇圧する

固体撮像装置。 - 複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源電圧の供給を受けて動作し、前記画素部が前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、

外部から単一レベルの電源電圧を入力する電源入力手段と、

前記画素部を駆動する垂直駆動部と、

前記電源入力手段によって入力された電源電圧のレベルを前記第1の電源電圧および/または第2の電源電圧に変換するレベルシフト手段と、を有し、

前記レベルシフト手段によって生成された第1の電源電圧を前記周辺回路部に選択的に供給し、生成された第2の電源電圧を前記画素部に選択的に供給し、

前記単位画素が、

少なくとも受光量に応じた信号電荷を生成する光電変換部と、

前記光電変換部によって生成された信号電荷を取り出すための電荷検出部と、

前記光電変換部によって生成された信号電荷を前記電荷検出部に転送する転送手段と、

前記光電変換部をリセットするリセットトランジスタと、

前記電荷検出部の信号電荷を電気信号に変換して出力信号線に出力する増幅トランジスタと、

画素行を選択するための選択トランジスタと、

少なくとも1個の電源電圧源と、

を含み、

単位画素内の接続順序が電源電圧源、選択トランジスタ、増幅トランジスタ、出力信号線の順であり、前記垂直駆動部による前記画素部の駆動の順序が先に前記リセットトランジスタを一度ONし、その後、前記選択トランジスタをONすることにより、前記光電変換部の信号電荷を読み出す

固体撮像装置。 - 複数の単位画素から構成される画素部と、前記画素部を制御する周辺回路部とを有し、当該周辺回路が第1の電源電圧の供給を受けて動作し、前記画素部が前記第1の電源電圧とは値が異なる第2の電源電圧の供給を受けて動作する固体撮像装置であって、

外部から単一レベルの電源電圧を入力する電源入力手段と、

前記画素部を駆動する垂直駆動部と、

前記電源入力手段によって入力された電源電圧のレベルを前記第1の電源電圧および/または第2の電源電圧に変換するレベルシフト手段と、を有し、

前記レベルシフト手段によって生成された第1の電源電圧を前記周辺回路部に選択的に供給し、生成された第2の電源電圧を前記画素部に選択的に供給し、

前記第1および第2の電源電圧の少なくとも1つは負電源電圧であり、

半導体基板上の画素部形成領域に第1導電型の第1のウェル領域を形成し、その外周部に第2導電型の第2のウェル領域を形成し、さらにその外周部に第1導電型の第3のウェル領域を形成し、

前記第3のウェル領域に負電源電圧を印加するとともに、この第3のウェル領域内部にnチャネルの絶縁ゲート型電界効トランジスタを形成し、前記nチャネルの絶縁ゲート型電界効トランジスタのソースと前記第3のウェル領域とを同じ負電源電圧とした

固体撮像装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002102046 | 2002-04-04 | ||

| JP2002102046 | 2002-04-04 | ||

| PCT/JP2003/004338 WO2003085964A1 (fr) | 2002-04-04 | 2003-04-04 | Dispositif analyseur d'image a semi-conducteurs |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009120030A Division JP4905501B2 (ja) | 2002-04-04 | 2009-05-18 | 固体撮像装置の駆動方法 |

| JP2009120018A Division JP4905500B2 (ja) | 2002-04-04 | 2009-05-18 | 固体撮像装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2003085964A1 JPWO2003085964A1 (ja) | 2005-08-18 |

| JP4337549B2 true JP4337549B2 (ja) | 2009-09-30 |

Family

ID=28786247

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003583019A Expired - Fee Related JP4337549B2 (ja) | 2002-04-04 | 2003-04-04 | 固体撮像装置 |

| JP2009120030A Expired - Fee Related JP4905501B2 (ja) | 2002-04-04 | 2009-05-18 | 固体撮像装置の駆動方法 |

| JP2009120018A Expired - Fee Related JP4905500B2 (ja) | 2002-04-04 | 2009-05-18 | 固体撮像装置 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009120030A Expired - Fee Related JP4905501B2 (ja) | 2002-04-04 | 2009-05-18 | 固体撮像装置の駆動方法 |

| JP2009120018A Expired - Fee Related JP4905500B2 (ja) | 2002-04-04 | 2009-05-18 | 固体撮像装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7515185B2 (ja) |

| EP (2) | EP2244456B1 (ja) |

| JP (3) | JP4337549B2 (ja) |

| CN (1) | CN100362659C (ja) |

| TW (1) | TWI255548B (ja) |

| WO (1) | WO2003085964A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10764516B2 (en) | 2015-06-30 | 2020-09-01 | Sony Corporation | Image sensor and electronic device |

Families Citing this family (39)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100535926B1 (ko) * | 2003-09-22 | 2005-12-09 | 동부아남반도체 주식회사 | 씨모스 이미지 센서 제조 방법 |

| JP4533004B2 (ja) * | 2004-06-07 | 2010-08-25 | キヤノン株式会社 | 固体撮像素子 |

| JP2006019971A (ja) * | 2004-06-30 | 2006-01-19 | Fujitsu Ltd | チャージポンプ動作に起因する雑音を低減したcmosイメージセンサ |

| JP2006060294A (ja) * | 2004-08-17 | 2006-03-02 | Pentax Corp | 固体撮像素子 |

| US7675015B2 (en) * | 2004-11-08 | 2010-03-09 | Samsung Electronics Co., Ltd. | CMOS image sensor with boosted voltage signal and related method of operation |

| KR101145059B1 (ko) | 2004-12-30 | 2012-05-11 | 인텔렉츄얼 벤처스 투 엘엘씨 | Cmos 이미지센서 및 그 구동방법 |

| JP4452199B2 (ja) | 2005-02-25 | 2010-04-21 | パナソニック株式会社 | 固体撮像装置およびその駆動方法 |

| KR100755662B1 (ko) * | 2005-06-23 | 2007-09-05 | 삼성전자주식회사 | 반도체 집적 회로 소자 및 그 제조 방법 |

| JP4865267B2 (ja) * | 2005-07-14 | 2012-02-01 | 富士フイルム株式会社 | 固体撮像装置及び内視鏡 |

| JP4696788B2 (ja) * | 2005-08-30 | 2011-06-08 | 日本ビクター株式会社 | 固体撮像装置 |

| JP4828914B2 (ja) | 2005-10-28 | 2011-11-30 | 株式会社東芝 | 固体撮像装置およびその駆動方法 |

| JP4898522B2 (ja) * | 2006-04-21 | 2012-03-14 | キヤノン株式会社 | 撮像装置、放射線撮像システム、及び、撮像装置の制御方法 |

| JP2008053286A (ja) * | 2006-08-22 | 2008-03-06 | Matsushita Electric Ind Co Ltd | 撮像装置チップセット及び画像ピックアップシステム |

| KR100889483B1 (ko) * | 2006-10-20 | 2009-03-19 | 한국전자통신연구원 | 저전압 동작 특성 향상을 위한 이미지 센서 |

| EP1983742A1 (en) * | 2007-04-16 | 2008-10-22 | STMicroelectronics (Research & Development) Limited | Image sensor power distribution |

| US20090115878A1 (en) * | 2007-11-07 | 2009-05-07 | Micron Technology, Inc. | Method, system and apparatus to boost pixel floating diffusion node voltage |

| KR101603354B1 (ko) * | 2008-04-11 | 2016-03-14 | 보드 오브 리전츠 오브 더 유니버시티 오브 텍사스 시스템 | 나노입자 전기발생 화학발광 증폭 방법 및 시스템 |

| JP5332314B2 (ja) * | 2008-05-29 | 2013-11-06 | ソニー株式会社 | 固体撮像素子およびカメラシステム |

| JP5266884B2 (ja) | 2008-05-30 | 2013-08-21 | ソニー株式会社 | 固体撮像装置、撮像装置、画素駆動方法 |

| JP2010050710A (ja) * | 2008-08-21 | 2010-03-04 | Nikon Corp | 固体撮像素子 |

| TWI390487B (zh) * | 2008-08-29 | 2013-03-21 | Au Optronics Corp | 驅動積體電路晶片及平面顯示器之驅動電路 |

| JP5257183B2 (ja) * | 2009-03-25 | 2013-08-07 | セイコーエプソン株式会社 | センシング装置および電子機器 |

| JP5218309B2 (ja) | 2009-07-14 | 2013-06-26 | ソニー株式会社 | 固体撮像素子およびその制御方法、並びにカメラシステム |

| JP5796218B2 (ja) | 2009-11-26 | 2015-10-21 | パナソニックIpマネジメント株式会社 | 固体撮像装置および撮像装置 |

| JP5489681B2 (ja) * | 2009-12-02 | 2014-05-14 | キヤノン株式会社 | 固体撮像装置 |

| KR101898297B1 (ko) * | 2010-03-08 | 2018-09-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 구동 방법 |

| JP5542091B2 (ja) | 2010-05-18 | 2014-07-09 | 富士フイルム株式会社 | 固体撮像素子及び撮像装置 |

| JP5511541B2 (ja) * | 2010-06-24 | 2014-06-04 | キヤノン株式会社 | 固体撮像装置及び固体撮像装置の駆動方法 |

| JP5470181B2 (ja) * | 2010-07-09 | 2014-04-16 | パナソニック株式会社 | 固体撮像装置 |

| JP5646420B2 (ja) * | 2011-09-14 | 2014-12-24 | 株式会社東芝 | 固体撮像装置 |

| JP6052511B2 (ja) | 2011-12-16 | 2016-12-27 | パナソニックIpマネジメント株式会社 | 固体撮像装置及び撮像装置 |

| JP6242211B2 (ja) * | 2013-12-26 | 2017-12-06 | キヤノン株式会社 | 撮像装置および撮像システム |

| JP6171997B2 (ja) | 2014-03-14 | 2017-08-02 | ソニー株式会社 | 固体撮像素子およびその駆動方法、並びに電子機器 |

| JP6443667B2 (ja) * | 2014-05-23 | 2018-12-26 | パナソニックIpマネジメント株式会社 | 撮像装置 |

| US9362320B2 (en) * | 2014-06-03 | 2016-06-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated circuit having a level shifter and method of making the same |

| FR3024788B1 (fr) | 2014-08-01 | 2017-05-19 | Sagem Defense Securite | Procede de verification de tracabilite de premieres instructions en un langage de programmation procedurale generees a partir de secondes instructions en un langage de modelisation |

| WO2017051451A1 (ja) * | 2015-09-24 | 2017-03-30 | オリンパス株式会社 | 固体撮像素子および内視鏡システム |

| US10455173B2 (en) * | 2015-09-30 | 2019-10-22 | Nikon Corporation | Image sensor and electronic camera |

| KR20220124484A (ko) * | 2021-03-03 | 2022-09-14 | 에스케이하이닉스 주식회사 | 이미지 센싱 장치 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63124685A (ja) * | 1986-11-14 | 1988-05-28 | Hitachi Ltd | 固体撮像装置 |

| JP3313125B2 (ja) * | 1991-10-07 | 2002-08-12 | 株式会社日立製作所 | Ccd型固体撮像素子 |

| JP3271086B2 (ja) * | 1992-09-29 | 2002-04-02 | ソニー株式会社 | 固体撮像素子の駆動回路 |

| JP2975973B2 (ja) * | 1993-08-10 | 1999-11-10 | 株式会社半導体エネルギー研究所 | 半導体装置およびその作製方法 |

| JP3517278B2 (ja) * | 1994-06-10 | 2004-04-12 | ペンタックス株式会社 | 撮像素子の電圧制御装置 |

| US5625210A (en) * | 1995-04-13 | 1997-04-29 | Eastman Kodak Company | Active pixel sensor integrated with a pinned photodiode |

| JPH09121306A (ja) * | 1995-10-24 | 1997-05-06 | Matsushita Electric Ind Co Ltd | Ccd駆動装置 |

| JP3998753B2 (ja) * | 1997-04-28 | 2007-10-31 | 富士フイルム株式会社 | 画像読取装置 |

| JP3573929B2 (ja) * | 1997-09-29 | 2004-10-06 | 三洋電機株式会社 | 電源回路 |

| US6127697A (en) * | 1997-11-14 | 2000-10-03 | Eastman Kodak Company | CMOS image sensor |

| JPH11313256A (ja) * | 1998-04-28 | 1999-11-09 | Sharp Corp | 増幅型固体撮像装置 |

| JP3657780B2 (ja) * | 1998-06-30 | 2005-06-08 | 株式会社東芝 | 撮像装置 |

| JP3571226B2 (ja) * | 1998-09-10 | 2004-09-29 | 株式会社東芝 | 固体撮像装置 |

| JP2000092395A (ja) * | 1998-09-11 | 2000-03-31 | Nec Corp | 固体撮像装置およびその駆動方法 |

| JP2000224495A (ja) | 1998-11-24 | 2000-08-11 | Canon Inc | 撮像装置及びそれを用いた撮像システム |

| JP4307602B2 (ja) * | 1998-11-24 | 2009-08-05 | オリンパス株式会社 | 撮像装置及び撮像装置の動作モード設定方法 |

| JP3031367B1 (ja) | 1998-12-02 | 2000-04-10 | 日本電気株式会社 | イメージセンサ |

| US6218656B1 (en) * | 1998-12-30 | 2001-04-17 | Eastman Kodak Company | Photodiode active pixel sensor with shared reset signal row select |

| JP2000209508A (ja) | 1999-01-19 | 2000-07-28 | Toshiba Corp | 固体撮像装置 |

| JP2001085658A (ja) * | 1999-09-09 | 2001-03-30 | Sony Corp | 固体撮像装置 |

| JP3796412B2 (ja) * | 2000-02-28 | 2006-07-12 | キヤノン株式会社 | 撮像装置 |

| JP3724374B2 (ja) * | 2001-01-15 | 2005-12-07 | ソニー株式会社 | 固体撮像装置及びその駆動方法 |

-

2003

- 2003-04-04 JP JP2003583019A patent/JP4337549B2/ja not_active Expired - Fee Related

- 2003-04-04 EP EP10008326.0A patent/EP2244456B1/en not_active Expired - Fee Related

- 2003-04-04 WO PCT/JP2003/004338 patent/WO2003085964A1/ja active Application Filing

- 2003-04-04 TW TW092107731A patent/TWI255548B/zh not_active IP Right Cessation

- 2003-04-04 CN CNB038111136A patent/CN100362659C/zh not_active Expired - Fee Related

- 2003-04-04 EP EP03715768A patent/EP1492334B1/en not_active Expired - Fee Related

- 2003-04-04 US US10/509,977 patent/US7515185B2/en not_active Expired - Fee Related

-

2009

- 2009-05-18 JP JP2009120030A patent/JP4905501B2/ja not_active Expired - Fee Related

- 2009-05-18 JP JP2009120018A patent/JP4905500B2/ja not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10764516B2 (en) | 2015-06-30 | 2020-09-01 | Sony Corporation | Image sensor and electronic device |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI255548B (en) | 2006-05-21 |

| US20050224841A1 (en) | 2005-10-13 |

| EP1492334A4 (en) | 2007-02-21 |

| TW200402877A (en) | 2004-02-16 |

| EP2244456A2 (en) | 2010-10-27 |

| EP1492334B1 (en) | 2011-08-17 |

| JP4905501B2 (ja) | 2012-03-28 |

| CN100362659C (zh) | 2008-01-16 |

| EP2244456B1 (en) | 2014-07-23 |

| CN1653804A (zh) | 2005-08-10 |

| JP2009182992A (ja) | 2009-08-13 |

| JP2009182349A (ja) | 2009-08-13 |

| EP2244456A3 (en) | 2011-11-30 |

| WO2003085964A1 (fr) | 2003-10-16 |

| JP4905500B2 (ja) | 2012-03-28 |

| US7515185B2 (en) | 2009-04-07 |

| EP1492334A1 (en) | 2004-12-29 |

| JPWO2003085964A1 (ja) | 2005-08-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4337549B2 (ja) | 固体撮像装置 | |

| JP4161855B2 (ja) | 固体撮像装置、駆動制御方法及び駆動制御装置 | |

| US8085330B2 (en) | Image pickup apparatus | |

| JP5203562B2 (ja) | Cmosイメージセンサー及びその駆動方法 | |

| JP3951879B2 (ja) | 固体撮像素子及びその駆動方法 | |

| JP4051034B2 (ja) | 増幅型固体撮像装置およびその駆動方法 | |

| JPH0951485A (ja) | 固体撮像素子 | |

| JP4434530B2 (ja) | 固体撮像装置 | |

| JP4229884B2 (ja) | 増幅型固体撮像装置 | |

| JP3697164B2 (ja) | 走査回路とそれを用いた撮像装置 | |

| KR20060041013A (ko) | Cmos 이미지 센서 및 그 구동 방법 | |

| JP4269957B2 (ja) | 直流レベル変換回路および直流レベル変換回路を制御する方法 | |

| JP4655785B2 (ja) | 固体撮像素子の駆動方法 | |

| KR100690883B1 (ko) | 이미지 센서 | |

| JP2007129763A (ja) | 固体撮像素子及びその駆動方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060404 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090317 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090518 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090609 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090622 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120710 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130710 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |