JP4199397B2 - 半導体素子の実装構造体 - Google Patents

半導体素子の実装構造体 Download PDFInfo

- Publication number

- JP4199397B2 JP4199397B2 JP35941299A JP35941299A JP4199397B2 JP 4199397 B2 JP4199397 B2 JP 4199397B2 JP 35941299 A JP35941299 A JP 35941299A JP 35941299 A JP35941299 A JP 35941299A JP 4199397 B2 JP4199397 B2 JP 4199397B2

- Authority

- JP

- Japan

- Prior art keywords

- plating layer

- zinc

- circuit wiring

- semiconductor element

- copper

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

Landscapes

- Chemically Coating (AREA)

- Wire Bonding (AREA)

Description

【発明の属する技術分野】

本発明は、各種電子デバイスに使用される半導体素子の実装構造体に関するものである。

【0002】

【従来の技術】

従来より、半導体素子の実装方法としてフェースダウンボンディングが知られている。

【0003】

このフェースダウンボンディングに使用される半導体素子の下面には、高密度にパターン形成された電子回路以外に複数個の端子が設けられており、これら複数個の端子を絶縁基板上面の対応する回路配線に半田接合させることにより半導体素子が絶縁基板上に実装される。

【0004】

尚、前記回路配線の形成には、加工の容易性等からアルミニウムが一般的に使用されており、この場合、半田接合される回路配線の上面には半田濡れ性の向上のために、ニッケルめっき層及び金めっき層が順次、被着されていた。

【0005】

【発明が解決しようとする課題】

ところで、この従来の実装構造体においては、アルミニウムから成る回路配線上にニッケルめっき層を析出させる際の触媒として、通常、パラジウムが使用されている。

【0006】

しかしながら、パラジウムを触媒として使用した場合、パラジウムめっき層の形成に使用されるめっき液中の硝酸によってアルミニウムから成る回路配線の表面が酸化・腐食され、回路配線とパラジウムめっき層との密着性が著しく低いものとなる。このため、半導体素子の実装等に伴ってパラジウムめっき層やその下の回路配線に熱が印加されると、パラジウムめっき層が熱応力によって回路配線より剥離することがあり、半導体素子を回路基板上に良好な状態で実装させておくことが不可となる欠点を有していた。

【0007】

また一方、前述のパラジウムに代えて亜鉛を触媒として使用することが検討されており、この亜鉛は硝酸を含まないめっき液を用いて回路配線上に被着させることができることから、亜鉛めっき層の形成に伴いアルミニウムから成る回路配線が酸化・腐食されることは殆どなく、亜鉛めっき層をアルミニウムから成る回路配線の上面に強固に被着させておくことができる。

【0008】

しかしながら、前記亜鉛めっき層はその上に被着されるニッケルめっき層との馴染みがあまり良好でないことから、結局、先に述べた従来の実装構造体と同様に、半導体素子の実装等に伴ってニッケルめっき層やその下の亜鉛めっき層に熱が印加されると、ニッケルめっき層が熱応力によって亜鉛めっき層より剥離するという欠点を有していた。

【0009】

【課題を解決するための手段】

本発明は上記欠点に鑑みて案出されたもので、本発明の半導体素子の実装構造体は、回路配線が被着されている絶縁基板と、下面に複数個の端子を有する半導体素子とから成り、該半導体素子の端子を絶縁基板上の回路配線に半田接合させることによって電気的に接続した半導体素子の実装構造体において、前記回路配線はアルミニウムから成り、かつ該回路配線の半田接合部に亜鉛−銅めっき層、ニッケルめっき層及び金めっき層が順次、被着させてあることを特徴とするものである。

【0010】

また本発明の半導体素子の実装構造体は、前記亜鉛−銅めっき層中の銅含有率が1wt%〜20wt%であることを特徴とするものである。

【0011】

【発明の実施の形態】

以下、本発明を添付図面に基づいて詳細に説明する。

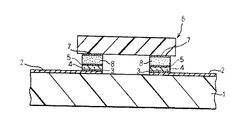

図1は本発明の一形態に係る半導体素子の実装構造体を示す断面図、図2は図1の要部拡大図であり、1 は絶縁基板、2は回路配線、3 は亜鉛−銅めっき層、4はニッケルめっき層、5は金めっき層、6は半導体素子、7は端子、8は半田である。

【0012】

前記絶縁基板1は、アルミナセラミックス等のセラミック材料により形成されており、その上面で回路配線2やめっき層3,4,5を支持するための支持母材として機能するものである。

【0013】

前記絶縁基板1は、例えばアルミナセラミックスから成る場合、アルミナ、シリカ、マグネシア等のセラミックス原料粉末に適当な有機溶剤、溶媒を添加・混合して泥漿状に成すとともに、これを従来周知のドクターブレード法やカレンダーロール法等を採用することによってセラミックグリーンシートを得、しかる後、該セラミックグリーンシートを所定の長方形状に打ち抜いた上、高温で焼成することによって製作される。

【0014】

また前記絶縁基板1の上面には、アルミニウムから成る複数個の回路配線2が所定パターンに被着されている。

【0015】

前記回路配線2は、外部電気回路からの入力信号や外部電源からの電力を半導体素子6に供給したり、或いは、半導体素子6からの出力信号を他の電気回路等に供給したりするためのものであり、その一端で半導体素子6の対応する端子7に半田8を介して電気的に接続される。

【0016】

尚、前記回路導体2は、従来周知の薄膜手法、具体的には、スパッタリングやフォトリソグラフィー技術,エッチング技術等を採用し、アルミニウムを所定厚み、所定パターンに被着させることによって絶縁基板1の上面に形成される。

【0017】

また前記回路導体2の一部上面、具体的には後述する半導体素子6の端子7が半田接合される部位には、亜鉛−銅めっき層3、ニッケルめっき層4及び金めっき層5が順次、被着されている。

【0018】

前記亜鉛−銅めっき層3は、ニッケルめっき層4を形成する際の触媒として機能するものであり、例えば0.3μm〜0.6μmの厚みを有し、銅含有率が1wt%〜20wt%に設定される。

【0019】

かかる亜鉛−銅めっき層3は、亜鉛の中に粒径100Å〜200Å程度の小さな銅の塊を分散させた状態、もしくは亜鉛と銅とで合金をつくった状態で形成されており、従来周知の無電解めっき法を採用することによって所定厚みに被着・形成される。このとき、亜鉛−銅合金の無電解めっきに使用されるめっき液には硝酸を含有させておく必要がないことから、亜鉛−銅めっき層3の形成に伴いアルミニウムから成る回路配線2が酸化・腐食されることは殆どない。

【0020】

またこの場合、前記めっき液中にキレート剤を添加しておけば、亜鉛−銅めっき層3の厚みや組成が均一になり、良好な亜鉛−銅めっき層3を得ることができる。従って亜鉛−銅めっき層3を形成するためのめっき液にはキレート剤を添加しておくことが好ましい。

【0021】

また前記亜鉛−銅めっき層3上のニッケルめっき層4は、半導体素子6の端子7を回路配線2に半田接合する際、回路配線2の半田濡れ性を良好になして半導体素子6の端子7を回路配線2に対して確実に半田接合させるためのものであり、亜鉛−銅めっき層3の上面に例えば2μm〜5μmの厚みに被着・形成される。

【0022】

前記ニッケルめっき層4は、従来周知の無電解めっき法を採用することによって亜鉛−銅めっき層3の上面に被着・形成され、このとき、ニッケルの形成に使用されるめっき液は次亜リン酸ナトリウムを還元剤として含んでおり、かかるめっき液には亜鉛−銅めっき層3中の亜鉛が溶解することから、この溶解に伴って亜鉛−銅めっき層3の表面には径100Å〜200Åの微細孔が1000〜5000個/μm2 の密度で多数形成され、ニッケルめっき層4を多数の微細孔を有した亜鉛−銅めっき層3の上面にアンカー効果によって極めて強固に被着させることができる。従って半導体素子6の実装等に伴って熱が印加されても、ニッケルめっき層4が下地(亜鉛−銅めっき層3)より剥離するのが有効に防止され、半導体素子6を回路基板上に良好な状態で実装させておくことができる。

【0023】

ここで、亜鉛−銅めっき層3中の銅含有率が1wt%よりも小さいと微細孔の形成密度が小さくなってニッケルめっき層4を亜鉛−銅めっき層3の上面に極めて強固に被着させておくことが難しくなり、また銅含有率が20wt%よりも大きいとニッケルめっき層4の形成時にニッケルの析出速度が遅くなって所定厚みのニッケルめっき層4を得るのに長時間を要することなる。従ってニッケルめっき層4を亜鉛−銅めっき層3の上面に極めて強固に、且つ短時間で効率良く被着・析出させるには、亜鉛−銅めっき層3中の銅含有率を1wt%〜20wt%の範囲内に設定しておくことが好ましい。

【0024】

またこのとき、ニッケルめっき層4の形成に使用するめっき液中にスルフォン酸塩やスルフォンアミド等を所定量、添加・混合させておけば、ニッケルめっき層4の内部応力が圧縮応力となり、ニッケルめっき層4を亜鉛−銅めっき層3に対してより強固に被着させることが可能となる。従ってニッケルめっき層4の形成に使用するめっき液中にはスルフォン酸塩やスルフォンアミドを添加・混合させておくことが好ましい。

【0025】

更に前記ニッケルめっき層4上に被着される金めっき層5は、ニッケルめっき層4の表面が大気中の水分等によって深い領域まで酸化・腐食されてしまうのを有効に防止するためのものであり、ニッケルめっき層4の上面に例えば0.04μm〜0.05μmの厚みに被着・形成される。

【0026】

前記金めっき層5は、従来周知の無電解めっき法を採用することによってニッケルめっき層4の上面に所定厚みに被着・形成される。

【0027】

そして上述した回路基板上には、半導体素子6がフェースダウンボンディングにて実装される。

【0028】

前記半導体素子6は、単結晶シリコン等から成る基材の下面に高密度にパターン形成された電子回路と複数個の端子7とを有しており、一部の端子7を介して内部に信号が入力されると、これらの入力信号に基づいて他の端子7より所定の出力を発するようになっている。

【0029】

前記半導体素子6は、その下面に設けられている複数個の端子7が絶縁基板上面の対応する回路配線2の一端、具体的には亜鉛−銅めっき層3、ニッケルめっき層4及び金めっき層5を被着させた箇所に半田8を介して対面配置されるようにして絶縁基板1上に載置され、しかる後、半田8を加熱・溶融させて回路配線2と端子7とを半田接合することによって半導体素子6が絶縁基板1上に取着・実装されることとなる。

【0030】

尚、本発明の実装構造体は上述の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更、改良等が可能である。

【0031】

例えば上述の形態において各めっき層3,4,5を無電解めっきによって被着させる際にその前処理として洗浄等を行っても良いことは勿論である。

【0032】

【発明の効果】

本発明によれば、アルミニウムから成る回路配線と亜鉛−銅めっき層、亜鉛−銅めっき層とニッケルめっき層がそれぞれ強固に被着されるため、半導体素子の実装等に伴って熱が印加されても、亜鉛−銅めっき層やニッケルめっき層が下地より剥離することはなく、半導体素子を回路基板上に良好な状態で実装させておくことができる。

【0033】

また本発明によれば、亜鉛−銅めっき層中の銅含有率を1wt%〜20wt%に設定しておくことにより、ニッケルめっき層を亜鉛−銅めっき層の上面に極めて強固に、且つ短時間で効率良く被着・析出させることができる。

【図面の簡単な説明】

【図1】本発明の一形態に係る半導体素子の実装構造体を示す断面図である。

【図2】図1の要部拡大図である。

【符号の説明】

1 ・・・絶縁基板、2・・・回路配線、3 ・・・亜鉛−銅めっき層、4・・・ニッケルめっき層、5・・・金めっき層、6・・・半導体素子、7・・・端子、8・・・半田

Claims (2)

- 回路配線が被着されている絶縁基板と、下面に複数個の端子を有する半導体素子とから成り、該半導体素子の端子を絶縁基板上の回路配線に半田接合させることによって電気的に接続した半導体素子の実装構造体において、

前記回路配線はアルミニウムから成り、かつ該回路配線の半田接合部に亜鉛−銅めっき層、ニッケルめっき層及び金めっき層が順次、被着させてあることを特徴とする半導体素子の実装構造体。 - 前記亜鉛−銅めっき層中の銅含有率が1wt%〜20wt%であることを特徴とする請求項1に記載の半導体素子の実装構造体。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP35941299A JP4199397B2 (ja) | 1999-12-17 | 1999-12-17 | 半導体素子の実装構造体 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP35941299A JP4199397B2 (ja) | 1999-12-17 | 1999-12-17 | 半導体素子の実装構造体 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001176920A JP2001176920A (ja) | 2001-06-29 |

| JP4199397B2 true JP4199397B2 (ja) | 2008-12-17 |

Family

ID=18464379

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP35941299A Expired - Fee Related JP4199397B2 (ja) | 1999-12-17 | 1999-12-17 | 半導体素子の実装構造体 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4199397B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010056191A (ja) * | 2008-08-27 | 2010-03-11 | Mitsubishi Electric Corp | 半導体装置の製造方法および半導体装置 |

-

1999

- 1999-12-17 JP JP35941299A patent/JP4199397B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001176920A (ja) | 2001-06-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JPS58164249A (ja) | 金属の選択的被覆方法 | |

| JP4199397B2 (ja) | 半導体素子の実装構造体 | |

| JP2002076189A (ja) | 配線基板 | |

| JP4090151B2 (ja) | パッケージ基板 | |

| JP4683768B2 (ja) | 配線基板 | |

| JP2001024296A (ja) | セラミック回路基板 | |

| JP3596335B2 (ja) | ワイヤボンディング端子を用いた半導体搭載用基板 | |

| JPS6035543A (ja) | 半導体装置の製造方法 | |

| JP3801334B2 (ja) | 半導体素子搭載用基板とその製造方法 | |

| JPH05283853A (ja) | プリント回路基板 | |

| JP3898482B2 (ja) | 配線基板 | |

| JP3554195B2 (ja) | 配線基板 | |

| JP2866512B2 (ja) | 配線基板 | |

| JP2690643B2 (ja) | 配線基板 | |

| JPH0465024A (ja) | ジャンパーチップ | |

| JPH10107394A (ja) | セラミック配線基板 | |

| JP3740407B2 (ja) | 配線基板 | |

| JP4511011B2 (ja) | 配線基板の製造方法 | |

| JP3645744B2 (ja) | セラミック配線基板 | |

| JP2001044323A (ja) | 電子部品実装用回路基板 | |

| JPS61256688A (ja) | 回路基板の製造方法 | |

| JP4646373B2 (ja) | 配線基板およびその製造方法 | |

| JPS61245555A (ja) | 半導体用端子接続構体 | |

| JP3771854B2 (ja) | 配線基板 | |

| JP4306941B2 (ja) | 配線基板およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061117 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080829 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080909 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081003 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111010 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4199397 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121010 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131010 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |