JP3740407B2 - 配線基板 - Google Patents

配線基板 Download PDFInfo

- Publication number

- JP3740407B2 JP3740407B2 JP2001338345A JP2001338345A JP3740407B2 JP 3740407 B2 JP3740407 B2 JP 3740407B2 JP 2001338345 A JP2001338345 A JP 2001338345A JP 2001338345 A JP2001338345 A JP 2001338345A JP 3740407 B2 JP3740407 B2 JP 3740407B2

- Authority

- JP

- Japan

- Prior art keywords

- copper

- layer

- boron

- plating layer

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H10W70/655—

-

- H10W90/724—

Landscapes

- Parts Printed On Printed Circuit Boards (AREA)

- Manufacturing Of Printed Wiring (AREA)

Description

【発明の属する技術分野】

本発明は、半導体素子を収容するための半導体素子収納用パッケージや混成集積回路基板等に用いられる配線基板に関するものである。

【0002】

【従来の技術】

従来、半導体素子収納用パッケージや混成集積回路基板等に用いられる配線基板は、一般に、酸化アルミニウム質焼結体や窒化アルミニウム質焼結体等の電気絶縁材料から成る絶縁基体と、該絶縁基体の表面および内部に被着されたタングステン、モリブデン、マンガン等の金属材料から成る配線層とにより形成されており、絶縁基体の表面に半導体素子や容量素子、抵抗器等の電子部品を搭載するとともに該電子部品の各電極を配線層に錫−鉛半田、錫−銀系半田等の低融点ロウ材を介して電気的に接続するようになっている。

【0003】

かかる配線基板は、配線層の所定部位を外部電気回路基板の配線導体に錫−鉛半田、錫−銀系半田等の低融点ロウ材を介し接続することによって外部電気回路基板上に実装され、同時に配線基板に搭載されている電子部品の各電極も所定の外部電気回路に電気的に接続されることとなる。

【0004】

また前記配線基板は、通常、配線層の露出表面に銅めっき層および金めっき層が順次被着されており、該銅めっき層によって配線層の電気抵抗を低く、かつ配線層に対する低融点ロウ材の接合を良好としており、また金めっき層によって配線層及び銅めっき層の酸化腐食を有効に防止している。

【0005】

【発明が解決しようとする課題】

しかしながら、上記従来の配線基板においては、銅めっき層を形成している銅の結晶粒の平均粒径が一般に約1μmであり、タングステン、モリブデン、マンガン等の金属材料から成る配線層表面の凹凸径(凹部:約1μm)に比べて大きい。そのため配線層表面に銅めっき層を被着させても銅めっき層は配線層表面の凹部内に十分入り込まずに配線層表面と銅めっき層との間に多数の空隙部が形成されてしまい、その結果、銅めっき層と配線層との密着強度が弱くなり、外力印加によって銅めっき層が配線層より容易に剥離したり、配線層表面と銅めっき層との間の空隙部に入り込んでいる気体が配線層に電子部品の電極を低融点ロウ材を介して接続する際の熱等によって大きく膨張し、銅めっき層にフクレ等が発生してしまうという欠点があった。

【0006】

また、前記配線層に、電子部品の電極を低融点ロウ材を介して接合する際の熱等が作用すると、銅めっき層の銅が金めっき層の表面に移動拡散して銅の酸化物層を形成してしまい、配線層に対する低融点ロウ材の濡れ性が劣化したり、接触電気抵抗が著しく増大してしまったりするという問題もあった。

【0007】

本発明は上記従来の欠点に鑑み案出されたもので、その目的は配線層と銅めっき層との間に剥離が発生したり銅めっき層にフクレ等が生じるのを有効に防止し、配線層に銅めっき層及び金めっき層を強固に被着させることによって配線層に電子部品の電極を低融点ロウ材を介して強固に取着接続することができる配線基板を提供することにある。

【0008】

【課題を解決するための手段】

本発明の配線基板は、絶縁基体に電子部品の電極が低融点ロウ材を介して接続される配線層を被着形成して成る配線基板であって、前記配線層のうち少なくとも電子部品の電極が低融点ロウ材を介して接合される領域の表面に、ホウ素の含有量が0.3重量%以上の銅−ホウ素めっき層と、銅めっき層と、パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層と、金めっき層とを順次被着させたことを特徴とするものである。

【0009】

また本発明の配線基板は、前記銅−ホウ素めっき層の厚みが0.03μm以上であることを特徴とするものである。

【0010】

更に本発明は、前記銅−ホウ素めっき層を形成する銅の結晶粒の平均粒径が0.02μm以下であることを特徴とするものである。

【0011】

また更に本発明は、前記パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層のホウ素含有量が0.2重量%〜2重量%の範囲であることを特徴とするものである。

【0012】

本発明の配線基板によれば、少なくとも電子部品の電極が低融点ロウ材を介して接続される配線層の表面に、ホウ素の含有量が0.3重量%以上で銅−ホウ素の結晶粒径が0.3μm未満と小さい銅−ホウ素めっき層を被着させたことから配線層の表面に多数の凹凸があったとしても、この凹部内に銅−ホウ素の結晶が良好に入り込んで配線層と銅−ホウ素めっき層とが間に空隙部を形成することなく強固に被着し、また銅−ホウ素めっき層上に、各々の密着性が良好な銅めっき層と、パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層と、金めっき層とを順次被着させたことから配線層に銅めっき層、合金層および金めっき層を強固に被着させることができるとともに前記銅めっき層によって配線層の電気抵抗を小さなものとなすことができ、更に金めっき層によって配線層の酸化腐食を有効に防止しつつ配線層に電子部品の電極を低融点ロウ材を介して確実、強固に電気的接続することができる。

【0013】

また同時に、前記銅めっき層と金めっき層との間に銅の拡散を有効に阻止するパラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層を形成したことから銅めっき層の銅の金めっき層表面への拡散が極めて効果的に防止され、配線層に電子部品の電極を低融点ロウ材を介して接合する際の熱等が作用したとしても金めっき層の表面に銅の酸化物層が形成されることはほとんどなく、これによって配線層に対する低融点ロウ材の接合性を良好なものに維持することができる。

【0014】

【発明の実施の形態】

次に本発明を添付図面に基づいて詳細に説明する。

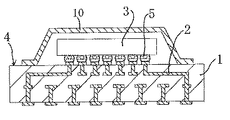

図1は、本発明の配線基板を半導体素子収納用パッケージに適用した場合の一実施例を示す断面図であり、1は絶縁基体、2は配線層である。この絶縁基体1と配線層2とで半導体素子3を搭載するための配線基板4が構成される。

【0015】

前記絶縁基体1は、酸化アルミニウム質焼結体、ムライト質焼結体、窒化アルミニウム質焼結体、炭化珪素質焼結体、ガラスセラミック焼結体等の電気絶縁材料から成り、その上面に半導体素子3を搭載する搭載部を有し、該搭載部表面に露出した配線層2に半導体素子3の電極が半田等の低融点ロウ材からなる接続部材5を介して接続される。

【0016】

前記絶縁基体1は、例えば、酸化アルミニウム質焼結体から成る場合には、酸化アルミニウム、酸化珪素、酸化カルシウム、酸化マグネシウム等の原料粉末に適当な有機バインダー、溶剤を添加混合して泥漿状のセラミックスラリーとなすとともに該セラミックスラリーを従来周知のドクターブレード法やカレンダーロール法等のシート成形技術を採用してシート状のセラミックグリーンシート(セラミック生シート)を得、しかる後、前記セラミックグリーンシートに切断加工や打ち抜き加工等を施して適当な形状とするとともにこれを複数枚積層し、最後に前記積層されたセラミックグリーンシートを還元雰囲気中、約1600℃の温度で焼成することによって製作される。

【0017】

また前記絶縁基体1は、その上面の搭載部から下面にかけて多数の配線層2が被着形成されており、該配線層2の搭載部に露出した部位には半導体素子3の各電極が錫−鉛半田等の低融点ロウ材から成る接続部材5を介して電気的に接続され、また絶縁基体1の下面に導出された部位には外部電気回路基板の配線導体が半田等の低融点ロウ材を介して電気的に接続される。

【0018】

前記配線層2は、接続される半導体素子3の電極を外部電気回路に接続する作用をなし、例えば、タングステンやモリブデン、モリブデン/マンガン、タングステン/銅、モリブデン/銅、タングステン/モリブデン/銅、等のタングステン、モリブデン、マンガンの少なくとも1種を主成分とする金属材料により形成されている。

【0019】

前記配線層2は、タングステン等の金属粉末に適当な有機バインダーや溶剤を添加混合して得た金属ペーストを絶縁基体1となるセラミックグリーンシートに予め従来周知のスクリーン印刷法により所定パターンに印刷塗布しておくことによって、絶縁基体1の所定位置に被着形成される。

【0020】

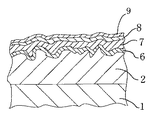

前記配線層2は、図2に示す如く、少なくとも半導体素子3の電極が低融点ロウ材から成る接続部材5を介して接続される領域に銅−ホウ素めっき層6、銅めっき層7、パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8、金めっき層9が順次被着されている。

【0021】

前記銅−ホウ素めっき層6は、配線層2に銅めっき層7、パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8、金めっき層9を密着性良く被着させる下地金属層として作用する。

【0022】

前記銅−ホウ素めっき層6は、例えば、配線層2の表面にパラジウム活性を施した後、この配線層2を、ジメチルアミンボラン等のホウ素系化合物を還元剤として用いたホウ素系無電解銅めっき液中に所定時間浸漬することによって配線層2の表面に所定厚みに被着される。この場合、前記銅−ホウ素めっき層6は被着時に共析して含有されるホウ素成分の作用により結晶粒の粒成長が効果的に抑制されて銅―ホウ素の結晶粒の平均粒径は、例えば、0.3μm以下の小さなものとなり、その結果、配線層2表面に多数の凹凸があったとしても、この凹部内に銅−ホウ素の結晶が良好に入り込んで配線層2と銅−ホウ素めっき層6とは間に空隙部を形成することなく強固に密着させることができる。

【0023】

なお、前記銅−ホウ素めっき層6は、銅−ホウ素の結晶粒の平均粒径を0.3μm以下の小さなものとするにはホウ素の含有量を0.3重量%以上としておく必要があり、ホウ素の含有量を0.3重量%以上としておくことによって銅−ホウ素の結晶粒の粒径は0.3μm以下となり、配線層2の表面に凹凸を有するとしても凹部内に良好に入り込んで配線層2に強固に被着する。

【0024】

また前記銅−ホウ素めっき層6は、銅−ホウ素の結晶粒の平均粒径を0.02μm以下としておくと銅−ホウ素めっき層6を表面に凹凸を有する配線層2により一層強固に被着させることができる。従って、前記銅−ホウ素めっき層6は、銅−ホウ素の結晶粒の平均粒径を0.02μm以下としておくことが好ましく、より好適には0.01μm以下としておくのがよい。

【0025】

前記銅−ホウ素めっき層6の平均粒径を0.02μm以下とするには、銅−ホウ素めっき層6中のホウ素含有率を0.5重量%程度以上とすることによって行なわれ、電気伝導性等の特性を考慮すれば0.5重量%〜4重量%の範囲とすることが好ましい。

【0026】

更に前記銅−ホウ素めっき層6は、その厚みが0.03μm未満の薄いものとなると配線層2の表面全体を完全に覆うことが難しく、後述する銅めっき層7、パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8、および金めっき層9を配線層2に強固に被着させるのが困難となる傾向にある。従って、前記銅−ホウ素めっき層6は、その厚みを0.03μm以上としておくことが好ましい。

【0027】

また更に、前記銅−ホウ素めっき層6の表面には該銅−ホウ素めっき層6と後述するパラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8のいずれに対しても密着性が優れた銅めっき層7が被着形成されている。

【0028】

前記銅めっき層7は、配線層2にパラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8を強固に被着させ、かつ配線層2に対し半田等の低融点ロウ材を強固に被着させるとともに配線層2の電気抵抗を下げる作用をなす。

【0029】

前記銅めっき層7は、例えば、銅−ホウ素めっき層6を被着させた配線層2を、ホルマリンを還元剤として用いた無電解銅めっき液中に所定時間浸漬することによって銅−ホウ素めっき層6の表面に所定厚みに被着形成される。この場合、ホルマリンを還元剤として用いた無電解銅めっき液を用いると、このめっき液が自己触媒作用を有するため銅−ホウ素めっき層6の表面に活性処理を施すことなく、銅めっき層7を所定厚みに、かつ銅−ホウ素めっき層6に対し接合強度を大として被着させることが可能となる。

【0030】

なお、前記銅めっき層7は、共析成分を含有しないホルマリン等を用いて形成され高純度であることから配線層2の半田等の低融点ロウ材に対する接合性が大きく改善されるとともに電気抵抗が極めて小さい値となり、配線層2を伝搬する電気信号等に減衰が発生するのを有効に防止することが可能となる。

【0031】

また、前記銅めっき層7はその表面に、該銅めっき層7と、後述する金めっき層9のいずれに対しても密着性が優れた、パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8が被着形成されている。

【0032】

前記パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8は、錫−鉛半田等の低融点ロウ材を介して半導体素子3の電極を配線層2に接続する際に作用する熱により銅めっき層7の銅が後述する金めっき層9の表面に移動拡散することを阻止する作用をなす。

【0033】

前記パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8は、塩化パラジウム等の、パラジウム、白金、ロジウム、ルテニウムの少なくとも1種の供給源となる化合物と、ジメチルアミンボラン、トリメチルアミンボラン等のホウ素系還元剤とを主成分とする無電解めっき液中に配線層2の露出表面(銅めっき層7が被着)を所定時間浸漬することにより、所定厚みに被着形成することができる。

【0034】

なお、前記銅めっき層7上にパラジウム−ホウ素合金層8を被着形成した場合、含有するホウ素成分の作用により銅の移動拡散を極めて効果的に阻止することができ、例えば、後述する金めっき層9の厚みを0.05μm未満と極めて薄いものとした場合や、錫−銀系半田等のいわゆる鉛フリー半田を用いて比較的高温でロウ付けした場合でも、銅めっき層7の銅が金めっき層9の表面に移動して酸化物層を作ることはなく、配線層2に対する低融点ロウ材の接合性や接触抵抗を良好に維持することができる

また、前記パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8のホウ素含有量が0.2重量%未満となると、錫−銀系半田等の比較的高温でロウ付けする低融点ロウ材を使用する場合、銅めっき層7の銅が金めっき層9に移動拡散するのを有効に阻止することが困難となる傾向にあり、また2重量%を超えると触媒不活性なホウ素成分が増大してめっき法による形成速度が遅くなり、量産性が低いものとなって実用性が損なわれてしまったり、内部応力が増大してクラック等を生じ易くなったりする傾向がある。従って、前記パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8は、ホウ素の含有量を0.2重量%〜2重量%の範囲としておくことが好ましい。

【0035】

更に、前記パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8は、その厚みが0.05μm未満となると銅めっき層7の銅が金めっき層9の表面に移動拡散するのを阻止することが困難となり、3μmを超えると形成時に発生して残留する内部応力が大きくなって銅めっき層7に対して強固に被着することが困難となるおそれがある。従って、前記パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8は、その厚みを0.05μm〜3μmの範囲とすることが好ましく、また後述する金めっき層9の厚みを0.05μm未満と非常に薄いものとする場合には、銅めっき層7の酸化腐食を防ぐために0.3μm以上の厚みとすることが好ましい。

【0036】

また更に、前記パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8の表面には金めっき層9が被着形成されている。

【0037】

前記金めっき層9は、配線層2、銅−ホウ素めっき層6および銅めっき層7の酸化腐食を防止するとともに、配線層2に対する低融点ロウ材の接合性を良好なものとする作用をなす。

【0038】

前記金めっき層9は、例えば、金化合物であるシアン化金カリウムおよび錯化剤であるエチレンジアミン四酢酸を主成分とする無電解金めっき液中に、前記パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層8が被着されている配線層2を所定時間浸漬させることによって前記合金層8の表面に所定厚みに被着される。

【0039】

更に前記金めっき層9は、その厚みが0.8μmを超えて厚くすると、半導体素子3の電極を配線層2に半田等の低融点ロウ材からなる接続部材5を介して接続したとき、低融点ロウ材5の錫と金との間で脆い金属間化合物が生成され、半導体素子3の配線層2に対する接続の信頼性が大きく低下してしまう危険性がある。従って、前記金めっき層9は、その厚さを0.8μm以下としておくことが好ましい。

【0040】

また一方、前記半導体素子3が搭載された絶縁基体1は、その上面に蓋体10が樹脂、ガラス、ロウ材等からなる封止材を介して接合され、この蓋体10と絶縁基体1とによって半導体素子3を内部に気密に封止するようになっている。

【0041】

前記蓋体10は酸化アルミニウム質焼結体やムライト質焼結体、窒化アルミニウム質焼結体等のセラミックス材料、あるいは鉄−ニッケル−コバルト合金や鉄−ニッケル合金等の金属材料から成り、例えば、酸化アルミニウム質焼結体から成る場合には、酸化アルミニウム、酸化珪素、酸化マグネシウム、酸化カルシウム等の原料粉末を従来周知のプレス成形法を採用することによって椀状に成形するとともにこれを約1500℃の温度で焼成することによって形成される。

【0042】

かくして上述の本発明の配線基板を適用した半導体素子収納用パッケージによれば、絶縁基体1上面の搭載部表面に露出した配線層2に半導体素子3の電極を半田等の低融点ロウ材から成る接続部材5を介して電気的、機械的に接続し、しかる後、絶縁基体1の上面に蓋体10を樹脂やガラス、ロウ材等から成る封止材を介して接合させ、絶縁基体1と蓋体10とから成る容器内部に半導体素子3を気密に収容することによって最終製品としての半導体装置が完成する。

【0043】

なお、本発明は上述の実施例に限定されるものではなく、本発明の要旨を逸脱しない範囲であれば種々の変更は可能であり、例えば、本発明の配線基板を、半導体素子、容量素子、抵抗器等の電子部品を搭載する混成集積回路用の配線基板に適用してもよい。

【0044】

【発明の効果】

本発明の配線基板によれば、少なくとも電子部品の電極が低融点ロウ材を介して接続される配線層の表面に、ホウ素の含有量が0.3重量%以上で銅−ホウ素の結晶粒径が0.3μm以下と小さい銅−ホウ素めっき層を被着させたことから配線層の表面に多数の凹凸があったとしても、この凹部内に銅−ホウ素の結晶が良好に入り込んで配線層と銅−ホウ素めっき層とが間に空隙部を形成することなく強固に被着し、また銅−ホウ素めっき層上に、各々の密着性が良好な銅めっき層と、パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層と、金めっき層とを順次被着させたことから配線層に銅めっき層および金めっき層を強固に被着させることができるとともに前記銅めっき層によって配線層の電気抵抗を小さなものとなすことができ、更に金めっき層によって配線層の酸化腐食を有効に防止しつつ配線層に電子部品の電極を低融点ロウ材を介して確実、強固に電気的接続することができる。

【0045】

また同時に、前記銅めっき層と金めっき層との間に銅の拡散を有効に阻止するパラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層を形成したことから銅めっき層の銅の金めっき層表面への拡散が極めて効果的に防止され、配線層に電子部品の電極を低融点ロウ材を介して接合する際の熱等が作用したとしても金めっき層の表面に銅の酸化物層が形成されることはほとんどなく、これによって配線層に対する低融点ロウ材の接合性を良好なものに維持することができる。

【図面の簡単な説明】

【図1】本発明の配線基板を半導体素子収納用パッケージに適用した場合の一実施例を示す断面図である。

【図2】図1に示す配線基板の要部断面図である。

【符号の説明】

1・・・・絶縁基体

2・・・・配線層

3・・・・半導体素子

4・・・・配線基板

5・・・・接続部材

6・・・・銅−ホウ素めっき層

7・・・・銅めっき層

8・・・・パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層

9・・・・金めっき層

10・・・蓋体

Claims (4)

- 絶縁基体に電子部品の電極が低融点ロウ材を介して接続される配線層を被着形成して成る配線基板であって、前記配線層のうち少なくとも電子部品の電極が低融点ロウ材を介して接合される領域の表面に、ホウ素の含有量が0.3重量%以上の銅−ホウ素めっき層と、銅めっき層と、パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層と、金めっき層とを順次被着させたことを特徴とする配線基板。

- 前記銅−ホウ素めっき層の厚みが0.03μm以上であることを特徴とする請求項1に記載の配線基板。

- 前記銅−ホウ素めっき層を形成する銅の結晶粒の平均粒径が0.02μm以下であることを特徴とする請求項1に記載の配線基板。

- 前記パラジウム、白金、ロジウム、ルテニウムの少なくとも1種とホウ素との合金層のホウ素含有量が0.2重量%〜2重量%の範囲であることを特徴とする請求項1に記載の配線基板。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001338345A JP3740407B2 (ja) | 2001-11-02 | 2001-11-02 | 配線基板 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001338345A JP3740407B2 (ja) | 2001-11-02 | 2001-11-02 | 配線基板 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2003142789A JP2003142789A (ja) | 2003-05-16 |

| JP3740407B2 true JP3740407B2 (ja) | 2006-02-01 |

Family

ID=19152854

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001338345A Expired - Fee Related JP3740407B2 (ja) | 2001-11-02 | 2001-11-02 | 配線基板 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3740407B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102010042543B4 (de) | 2010-06-30 | 2017-06-29 | Vectron International Gmbh | Metallisierung für Hohlraumgehäuse und nicht-magnetisches hermetisch dichtes Hohlraumgehäuse |

-

2001

- 2001-11-02 JP JP2001338345A patent/JP3740407B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003142789A (ja) | 2003-05-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2002076189A (ja) | 配線基板 | |

| JP4683768B2 (ja) | 配線基板 | |

| JP3898482B2 (ja) | 配線基板 | |

| JP3740407B2 (ja) | 配線基板 | |

| JP3420469B2 (ja) | 配線基板 | |

| JP2003100952A (ja) | 配線基板 | |

| JP2001148561A (ja) | 配線基板の製造方法 | |

| JP2627509B2 (ja) | 導電層を有する電子部品 | |

| JP3771854B2 (ja) | 配線基板 | |

| JP2001339141A (ja) | 配線基板 | |

| JP2001339014A (ja) | 配線基板 | |

| JP2003069201A (ja) | 配線基板 | |

| JP2001102733A (ja) | 電子部品の実装方法 | |

| JP2001339015A (ja) | 配線基板 | |

| JPH05267496A (ja) | セラミックス配線基板の製造方法 | |

| JP3645744B2 (ja) | セラミック配線基板 | |

| JP3512554B2 (ja) | 配線基板 | |

| JP2001085807A (ja) | 配線基板 | |

| JP3854177B2 (ja) | 半導体素子搭載用配線基板およびその製造方法 | |

| JP2000244087A (ja) | 配線基板 | |

| JP4109391B2 (ja) | 配線基板 | |

| JP2003008190A (ja) | 配線基板 | |

| JP2002076595A (ja) | 配線基板 | |

| JP2003105549A (ja) | 配線基板およびその製造方法 | |

| JP2003037355A (ja) | 配線基板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040517 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20051101 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20051107 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091111 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101111 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101111 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111111 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |