JP4141581B2 - フラッシュメモリを搭載する記憶装置 - Google Patents

フラッシュメモリを搭載する記憶装置 Download PDFInfo

- Publication number

- JP4141581B2 JP4141581B2 JP09801999A JP9801999A JP4141581B2 JP 4141581 B2 JP4141581 B2 JP 4141581B2 JP 09801999 A JP09801999 A JP 09801999A JP 9801999 A JP9801999 A JP 9801999A JP 4141581 B2 JP4141581 B2 JP 4141581B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- flash memory

- external

- read

- write

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/0626—Reducing size or complexity of storage systems

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/023—Free address space management

- G06F12/0238—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory

- G06F12/0246—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory in block erasable memory, e.g. flash memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0655—Vertical data movement, i.e. input-output transfer; data movement between one or more hosts and one or more storage devices

- G06F3/0656—Data buffering arrangements

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0673—Single storage device

- G06F3/0679—Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/72—Details relating to flash memory management

- G06F2212/7203—Temporary buffering, e.g. using volatile buffer or dedicated buffer blocks

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Memory System (AREA)

- Read Only Memory (AREA)

Description

【発明の属する技術分野】

本発明は、記憶装置に関し、より特定的には、フラッシュメモリを搭載する記憶装置に関する。

【0002】

【従来の技術】

近年、半導体製造技術の進歩に伴い、フラッシュメモリの記憶容量も大きくなってきている。この大容量化に伴い、小型でかつ低消費電力である特性を生かして特に携帯機器の分野においては記録メディアとしてフラッシュメモリを搭載した記憶装置が使用されるようになってきた。

【0003】

【発明が解決しようとする課題】

フラッシュメモリは、不揮発性で、一括消去後再書込ができる半導体記憶装置である。フラッシュメモリは、高密度に記憶素子を集積し、かつ、高速にデータ授受をするため、セクタアドレスを指定して一定量のデータをセクタ単位で読出、消去、書込(プログラム)を一括して行う。フラッシュメモリの大容量化に伴い、フラッシュメモリが一括してデータを読出す単位であるセクタ容量も増加する傾向にあり、たとえば、256MビットのAND型フラッシュメモリではこのセクタ容量は2048バイトになっている。

【0004】

一方、パーソナルコンピュータを初めとする情報機器がハードディスクやメモリカード等の記憶装置とデータ授受を行なう際の単位のデータ容量(本明細書中では以降メディアセクタ容量と称する)は、たとえば、標準的には512バイトであり、このメディアセクタ容量は特に増加する傾向は見られない。

【0005】

このような、セクタ構造を持ったフラッシュメモリを搭載する記憶装置では、フラッシュメモリのセクタデータを一時的に格納し、ホストシステムとのデータ転送を行なうためのタイミングおよび容量の調整を行なうためのバッファメモリを記憶装置の内部に搭載する必要がある。このバッファメモリは通常SRAM(Static Random Access Memory)等が用いられる。

【0006】

ホストシステムとのデータ転送の容量、すなわちメディアセクタ容量が、フラッシュメモリのセクタ容量よりも小容量である場合でも、バッファメモリの容量は、フラッシュメモリのセクタ容量と同容量もしくはそれ以上の容量にする必要があった。

【0007】

しかしながら、フラッシュメモリのセクタ容量が年々大容量化しつつあり、このような場合には、バッファメモリとして大容量のSRAMを搭載する必要があり、コスト的にデメリットが生じていた。

【0008】

本発明は、このような問題点を解決するようになされたもので、その目的は、メディアセクタ容量に相当する小容量のバッファメモリを搭載することを可能にし、コストダウンを図ったフラッシュメモリを搭載する記憶装置を提供することである。

【0009】

【課題を解決するための手段】

この発明は、ある局面においては、ホストシステムから外部書込アドレス信号と外部書込データとを受けてデータ記憶を行う書込モードを備える記憶装置であって、外部書込データ容量より容量の大きい内部書込データ容量を単位として複数のデータの書込がなされるフラッシュメモリを備え、フラッシュメモリは、書込モードにおいて、内部書込アドレス信号を受けて、内部書込データに含まれる複数のデータを取込み保持し、書込モードにおいて、外部書込アドレス信号を受けて内部書込アドレス信号を発生し、外部書込データを受けて保持して外部書込データと外部書込アドレス信号とに基づいて内部書込データを出力するデータ入出力部をさらに備え、データ入出力部は、書込モードにおいて、ホストシステムから外部書込データおよび外部書込アドレス信号を受ける第1のインタフェイス部と、外部書込データ容量以上で、かつ、内部書込データ容量より小さい記憶容量を有し、書込モードにおいて第1のインタフェイス部から外部書込データを受け取る、バッファメモリと、書込モードにおいて、第1のインタフェイス部から外部書込アドレス信号を受けて内部書込アドレス信号を発生し、バッファメモリから読出した外部書込データに、フラッシュメモリを構成するメモリセルの消去状態に対応するデータを加えて内部書込データを発生する、第2のインタフェイス部とを含む。

【0010】

好ましくは、フラッシュメモリは、内部書込アドレス信号に対応し、内部書込データ容量と同じ容量を持つメモリ領域単位を有し、メモリ領域単位はオフセット信号に対応する複数の領域を含み、第2のインタフェイス部は、外部書込アドレス信号に含まれるオフセット信号を出力し、外部書込データに対応する内部書込データをメモリ領域単位のオフセット信号に対応する領域に書き込む。

【0011】

より好ましくは、第2のインタフェイス部は、メモリ領域単位の外部書込データに対応する内部書込データを書き込んだ残りの領域に、フラッシュメモリを構成するメモリセルの消去状態に対応するデータを書き込む。

【0012】

さらに好ましくは、内部書込データ容量は、外部書込データ容量の整数倍である。

【0013】

より好ましくは、フラッシュメモリは、クロックに同期して内部書込データを順次取込み、第2のインタフェイス部は、バッファメモリに対する読出制御信号を発生してバッファメモリから外部書込データを受けて内部書込データを発生し、外部書込アドレス信号から内部書込アドレス信号を発生する、データ転送制御部を有し、データ転送制御部は、フラッシュメモリに内部書込データの書込が開始されるときに、クロックのカウントを開始するカウンタと、外部書込アドレス信号に含まれるオフセット信号とカウンタのカウント値の上位から所定数ビットとが一致した時に一致信号を出力する比較器と、バッファメモリがクロックに同期して外部書込データを出力するように一致信号に応じて読出制御信号をバッファメモリに与えるゲート回路と、一致信号が非活性化されている時は、フラッシュメモリを構成するメモリセルの消去状態に対応するデータをフラッシュメモリに与え、一致信号が活性化した時はバッファメモリから読出された外部書込データをフラッシュメモリに与える選択回路とを有する。

【0014】

好ましくは、記憶装置は、ホストシステムから外部読出アドレス信号を受けてホストシステムに外部読出データを出力する読出モードをさらに備え、データ入出力部は、読出モード時に、外部読出アドレス信号を受けて内部読出アドレス信号を発生してフラッシュメモリに与え、フラッシュメモリから読出される内部読出データの一部を選択して外部読出データとして保持した後、ホストシステムに対して外部読出データを出力し、第1のインタフェイス部は、読出モード時に、ホストシステムから受けた外部読出アドレス信号に応じた外部読出データをホストシステムに出力し、バッファメモリは、外部読出データ容量以上で、かつ、内部読出データ容量より小さい記憶容量を有し、読出モード時に、第1のインタフェイス部に対して保持していた外部読出データを出力し、第2のインタフェイス部は、読出モード時に、第1のインタフェイス部から外部読出アドレス信号を受けて内部読出アドレス信号を発生してフラッシュメモリに与えてフラッシュメモリから内部読出データが含む複数のデータを読出し、内部読出しデータの一部を外部読出データとしてバッファメモリに送出する。

【0018】

好ましくは、フラッシュメモリは、クロックに同期して内部読出データを順次出力し、第2のインタフェイス部は、外部読出アドレス信号から内部読出アドレス信号を発生し、内部読出データの一部を選択して外部読出データとしてバッファメモリが格納するようにバッファメモリへ書込制御信号を発生する、データ転送制御部を有し、データ転送制御部は、フラッシュメモリから内部読出データの読出が開始されるときに、クロックのカウントを開始するカウンタと、外部書込アドレス信号に含まれるオフセット信号とカウンタのカウント値の上位から所定数ビットとが一致した時に一致信号を出力する比較器と、バッファメモリがクロックに同期して内部読出データの一部を外部読出データとして格納するように一致信号に応じて書込制御信号をバッファメモリに与えるゲート回路とを有する。

【0019】

この発明は他の局面では、フラッシュメモリを搭載する記憶装置であって、フラッシュメモリと、ホストシステムから入力される外部アドレスに対応する内部主アドレスおよび内部副アドレスを発生し、ホストシステムから入力される外部データをフラッシュメモリに出力、またはフラッシュメモリから入力されるデータを外部データとしてホストシステムへ出力する、データ入出力部とを備え、データ入出力部は、内部主アドレスによってフラッシュメモリの外部データの容量より大きい容量を持つメモリ領域単位を選択し、内部副アドレスによってメモリ領域単位内のデータ入出力開始位置を指定し、データ入出力開始位置からフラッシュメモリのデータ読出、またはデータ入出力開始位置からフラッシュメモリへのデータの書込を行う。

【0020】

好ましくは、データ入出力部は、ホストシステムとフラッシュメモリとの間のタイミング調整をするために外部データを一時的に保持するバッファメモリを含み、バッファメモリの記憶容量は、外部データの容量以上で、メモリ領域単位の容量より小さい。

【0021】

【発明の実施の形態】

以下図面を参照しつつ、本発明の実施の形態について詳しく説明する。なお、図中同一符号は、同一または相当部分を示す。

【0022】

[実施の形態1]

図1は、フラッシュメモリを搭載した記憶装置1の概略構成を示すブロック図である。

【0023】

図1を参照して、記憶装置1は、ホストシステム12と記憶する外部データの授受を行なうためのものであり、ホストシステムからメディアアドレスを受けてアドレス変換を行い、ホストシステムとの間で外部データを授受するためにデータ変換を行うデータ入出力部9と、データ入出力部9が変換したアドレス信号に応じてデータ授受を行うフラッシュメモリ10とを含む。データ入出力部9はフラッシュメモリ10が入出力するデータと外部データとの間のデータの変換を行う。

【0024】

データ入出力部9は、ホストシステムとデータ転送を行なうホストインタフェイス部2と、ホストインタフェイス部2がホストシステム12とデータ転送を行なうためにフラッシュメモリのセクタデータの一部を一時的に格納する512バイトの容量を持つバッファメモリ4と、ホストインタフェイス部2からの指令に応じてバッファメモリ4とフラッシュメモリとのデータ授受のコントロールを行なうフラッシュインタフェイス部7と、記憶装置1が記憶すべきデータを保持する半導体装置であるフラッシュメモリ10とを含む。

【0025】

フラッシュインタフェイス部7は、フラッシュメモリの仕様にあわせたシーケンスで、読出や書込等の動作を設定するコマンドや、読出や書込時にメモリ領域を指定するためのアドレスをフラッシュメモリに送出するシーケンサ部6と、ホストシステム12から与えられたメディアセクタアドレスからフラッシュメモリのセクタアドレスおよびカラムアドレスオフセットを生成するデータ転送制御部8とを含む。

【0026】

フラッシュメモリ10は、各々が2048バイトの容量を持つ複数のセクタを有する。フラッシュメモリ10は、セクタアドレスが指定されると、指定されたセクタに記憶されている2048バイトのデータをシリアルに出力することができる。

【0027】

図2は、実施の形態1におけるフラッシュメモリとバッファメモリとのアドレスの対応関係を示すメモリマップである。

【0028】

図2を参照して、メディアセクタ容量、すなわち記憶装置1が一括してデータ授受を行なうセクタ容量が512バイト、フラッシュメモリ10の1セクタが2048バイトである場合のメモリアップであり、フラッシュメモリ10の1/4セクタをメディアセクタとして割当てている。

【0029】

たとえば、メディアセクタアドレス0hは、フラッシュセクタアドレス0hのフラッシュカラムアドレス0h〜1FFhに相当する。メディアセクタアドレス1hは、フラッシュセクタアドレス0hのフラッシュカラムアドレス200h〜3FFhに相当する。同様に、メディアセクタアドレス2hは、フラッシュセクタアドレス0hのフラッシュカラムアドレス400h〜5FFhに相当する。メディアセクタアドレス3hは、フラッシュセクタアドレス0hのフラッシュカラムアドレス600h〜7FFhに相当する。つまり、各フラッシュセクタアドレスはそれぞれ4分割され、メディアセクタアドレスに割当てられている。

【0030】

図3は、メディアセクタアドレスをフラッシュセクタアドレスとカラムアドレスオフセット生成ビットとに変換する説明をするための図である。

【0031】

図3を参照して、メディアセクタアドレスMA15〜MA0の上位14ビットは、フラッシュセクタアドレスSA13〜SA0として使用される。また、メディアセクタアドレスのうち下位2ビットであるMA1、MA0は、カラムアドレスオフセット生成ビットC1、C0として使用され、このカラムアドレスオフセット生成ビットから後に説明するスタートフラッシュカラムアドレスオフセットを発生する。

【0032】

図4は、スタートフラッシュカラムアドレスオフセットとメディアセクタアドレスの下位2ビットとの関係を示す図である。

【0033】

図4を参照して、MA1、MA0がともに0であるときは、スタートフラッシュカラムアドレスオフセットは0hに設定され、メディアセクタ容量である512バイトのデータの授受がバッファメモリとフラッシュメモリとの間で行なわれる。

【0034】

MA1、MA0がそれぞれ、0、1であるときは、スタートフラッシュカラムアドレスオフセットは200hに設定され、バッファメモリとフラッシュメモリとの間のデータ授受が行なわれる。

【0035】

MA1、MA0がそれぞれ1、0の場合には、スタートフラッシュカラムアドレスオフセットは400hに設定され、バッファメモリとフラッシュメモリとの間でデータ授受が行なわれる。

【0036】

MA1、MA0がともに1であるときは、スタートフラッシュカラムアドレスオフセットは600hに設定され、バッファメモリとフラッシュメモリとの間のデータ授受が行なわれる。

【0037】

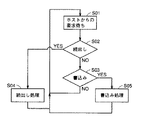

図5は、実施の形態1の記憶装置の処理のメインフローを示す図である。

図5を参照して、ステップS01は、ホストシステムからの要求待ちのステップである。続いて、ステップS02において、読出の要求があったか否かが判断される。読出要求があった場合には、ステップS04に移り、読出処理が行なわれる。読出処理が完了すると、再び、ステップS01に戻りホストシステムからの要求待ち状態となる。

【0038】

ステップS02において、読出要求が行なわれていない場合には、ステップS03に進む。ステップS03では、ホストシステムから書込要求が行なわれていないかどうかが判断される。書込要求があった場合には、ステップS05に進み、書込処理が行なわれる。書込処理が完了すると、再び、ステップS01に進みホストシステムからの要求待ち状態となる。

【0039】

ステップ03において、書込要求が行なわれなかった場合には、再び、ステップS01に戻り、ホストシステムからの要求待ち状態となる。

【0040】

図6は、図5に示したステップS04の読出処理の詳細を示すフローチャートである。

【0041】

図6を参照して、ステップS11において、読出が開始される。

次いで、ステップS12において、メディアセクタアドレスがホストシステムから受信される。続いて、受信したメディアセクタアドレスをもとにアドレス変換が行なわれ、図4で示したスタートフラッシュカラムアドレスオフセットの値が生成される。

【0042】

続いてステップS14において、フラッシュメモリからセクタ読出が行なわれる。そして読出されたデータは、ステップS15において、オフセット値に基づきバッファメモリに書込まれる。続いてステップS16において、ホストシステムに割込み信号を送出し、ステップS17において、バッファメモリに書込まれたデータをホストシステムに対して読出データとして送出する。そしてステップS18において、読出が終了する。

【0043】

図7は、図6に示した読出処理の各ステップが記憶装置内のどのブロックで実施されているかを示す図である。

【0044】

図7を参照して、まずホストシステムからコントローラやバッファメモリに対してメディアセクタアドレスの読出要求が発信される。コントローラというのは、図1におけるホストインタフェイス部2およびフラッシュインタフェイスシーケンサ部6に該当する。

【0045】

これを受けて、コントローラではメディアセクタアドレスからフラッシュメモリのセクタアドレスSAとオフセット値の生成がされる。そして、フラッシュメモリに対してリードコマンドとセクタアドレスSAが発信される。応じて、フラッシュメモリではセクタリードが行なわれ2048バイトのデータが順次フラッシュインタフェイスデータ出力としてコントローラに送出される。これを受けてコントローラではメディアセクタアドレスに基づくオフセットに対応する512バイトのデータを抜き出してバッファメモリへと転送する。

【0046】

そしてバッファメモリへのデータの格納が終了すると、コントローラはホストシステムに対してメディアセクタアドレスのデータ読出要求を行ないホストシステムは割込みを受付ける。続いて、コントローラはバッファメモリからデータを出力しこれによりメディアセクタアドレスのデータ読出が行なわれる。そして読出が終了する。

【0047】

図8は、図5に示したステップS05における書込処理の詳細を示すフローチャートである。

【0048】

図8を参照して、まず、ステップS21において書込が開始される。

続いて、ステップS22においてホストシステムから発信されたメディアセクタアドレスが受信される。

【0049】

続いて、ステップS23において、記憶装置がホストシステムに対してデータを要求する。そして、ステップS24において、記憶装置がホストシステムからデータを受信する。このデータはステップS25において、バッファメモリに書込まれる。

【0050】

そして、ステップS26において、ステップS22で受信したメディアセクタアドレスからオフセット値の生成がされる。その後、ステップS27においてフラッシュメモリに対するプログラムコマンドの設定がされる。続いて、ステップS28において、バッファメモリからのデータを初期値データと合成し所定のタイミングでフラッシュメモリに書込が行なわれる。

【0051】

そして、ステップS29において書込が終了する。

図9は、図8に示した書込処理の各ステップがホストシステムとコントローラおよびバッファメモリとフラッシュメモリとの間でどのように行なわれるかを示す図である。

【0052】

図9を参照して、まずホストシステムからメディアセクタアドレスの書込要求がコントローラに向けて発信される。続いて、コントローラはこれを受けてメディアセクタアドレスへのデータ書込要求をホストシステムに対して行なう。応じてホストシステムはメディアセクタアドレスに対するデータの書込を行なう。このデータはコントローラを経由してバッファメモリに入力される。

【0053】

続いて、コントローラでは受信していたメディアセクタアドレスからフラッシュメモリのセクタアドレスおよびオフセット値の生成がされる。そして、フラッシュメモリに対するプログラムコマンドおよびセクタアドレスの発信がされる。

【0054】

これを受けて、フラッシュメモリはデータ書込可能状態となる。そして、コントローラからの所定の信号に基づきバッファメモリからはオフセット値に基づいて格納されていた512バイトのデータが転送される。フラッシュメモリへの書込データが転送されている期間のうち、バッファメモリに格納されていたデータが転送される期間以外の書込データとしては“FFh”が転送される。フラッシュメモリへバッファメモリのデータを含む書込データが入力されると、その後、所定のウエイト時間経過後書込が終了する。

【0055】

ここで、書込みデータ“FFh”について説明する。

フラッシュメモリの各メモリセルは、フローティングゲートを有するMOSトランジスタで構成されている。各メモリセルはMOSトランジスタのしきい値電圧の状態でデータ“1”、“0”を保持している。一般に、メモリセルの消去直後の状態は、保持データ“1”に対応する。データ“0”の書込動作がされるとしきい値電圧が変化し、変化後のしきい値電圧を有するメモリセルの状態が保持データ“0”に対応する。一方、データ“1”の書込動作ではしきい値電圧は変化しない。このため、初期状態としてデータ“0”を保持しているメモリセルに対してデータ“1”の書込動作が行われても、保持データは変化しない。

【0056】

つまり、通常は、メモリセルデータの消去が行なわれてからデータの書込が行なわれるが、実施の形態1では、消去動作を行わずデータとして“FFh”を書込む。“FFh”はビットがすべて“1”の1バイトのデータであるため、フラッシュメモリは書込む直前のデータを保持するのである。

【0057】

図10は、図1に示したデータ転送制御部8の詳細を示すブロック図である。図10を参照して、データ転送制御部8は、記憶装置内部で生成されるリードセクタイネーブル信号RSE♯をクロック信号SCの立上がりに同期してラッチするフリップフロップ22と、フリップフロップ22の出力と記憶装置内部で生成されるライトセクタイネーブル信号WSE♯との論理和をリセット信号RSTとして出力するAND回路24と、リセット信号RSTによってリセットされその後クロック信号SCの立上がりに応答してカウントアップを開始するSCカウンタ26と、ホストシステムより16ビットのメディアセクタアドレスをラッチして上位14ビットをシーケンサ部6へセクタアドレスSA0〜SA15として出力するメディアセクタアドレスラッチ部30と、SCカウンタ26の出力である11ビットの計数値のうち上位2ビットとメディアセクタアドレスラッチ部30がラッチしたメディアセクタアドレスの下位2ビットとを比較する比較器32とを含む。

【0058】

比較器32は、SCカウンタ26からの2ビットのデータとメディアセクタアドレスラッチ部30からの2ビットのデータとが一致したときにLレベルとなる比較結果信号をCMPを出力する。

【0059】

データ転送制御部8は、さらに、フリップフロップ22の出力とクロック信号SCと結果信号CMPとを受けてライトイネーブル信号/WE♯を出力するゲート回路28と、バッファメモリ4からの出力と固定データ“FFh”とを受けて比較結果信号CMPに応じてフラッシュメモリに対して出力するセレクタ34とを含む。セレクタ34は、比較信号CMPがLのときはバッファメモリからの出力をフラッシュメモリに対して出力し、比較信号CMPがHのときは固定データ“FFh”をフラッシュメモリに対して出力する。

【0060】

尚、説明の便宜のため、図10にはバッファメモリ4が記載されている。バッファメモリ4は、SCカウンタ26の11ビットの計数値のうちの下位9ビットをアドレス信号ADRとして受け、ライトセクタイネーブル信号WSE♯をアウトプットイネーブル信号/OE♯として受け、ゲート回路28の出力をライトイネーブル信号/WE♯として受けこれらに応答してフラッシュメモリからのデータ入力DIを受けて保持し、またはセレクタ34を介してフラッシュメモリへデータ出力DOを送出する。

【0061】

図11は、フラッシュメモリからバッファメモリへのデータ転送の様子を示すタイミング図である。

【0062】

図11を参照して、時刻t1からクロック信号SCに応じてデータ信号DATAがフラッシュメモリから読出される。この読出は、セクタ単位で行なわれるため、通常は2048データが連続して以後読出される。

【0063】

ここで、ホストシステムから指定されたメディアセクタアドレスのうち最下位の2ビットである(MA1,MA0)が(0,1)のときには時刻t1〜t2においては、フラッシュメモリから読出されたデータはバッファメモリへは転送されない。

【0064】

そして、時刻t2〜t3において、カラムアドレス200h〜3FFhに相当するデータがフラッシュメモリから読出されている間は、これらのデータはバッファメモリへと転送されて保持される。この保持されるデータは、フラッシュメモリから読出されるセクタ容量2048バイトのうちの512バイトであり、セクタ容量の4分の1である。

【0065】

時刻t3以降は、カラムアドレス400h以降のデータが順次読出されるが、これらはバッファメモリへは保持されることはない。

【0066】

図12は、図11に示したバッファメモリへのデータ書込の動作をより詳細に示した動作波形図である。

【0067】

図10、図12を参照して、時刻t0において、ホストシステムから読出要求が行なわれたことに応じて、リードセクタイネーブル信号RSE♯がHレベルからLレベルへと立下がる。続いて、時刻t1においてリセット信号RSTがHレベルからLレベルへと立下がり、SCカウンタ26のリセットが解除される。以降、時刻t1〜t2において、クロック信号SCの入力に応じてSCカウンタ26は11ビットのカウント値を0hから1FFhまでカウントアップする。カウント値の下位9ビットであるバッファメモリに入力されるアドレス信号ADRは、同様に0hから1FFhまで変化する。このとき、比較器32に入力されるカウント値の上位2ビットは(0,0)であり、メディアセクタアドレスラッチ部30からの2ビットの入力は(0,1)であるため、比較結果信号CMPは不一致を示すHレベルである。そのため、データ入力信号DIの内容は、時刻t1〜t2においては、バッファメモリ4に書込まれることはない。

【0068】

時刻t2において、SCカウンタ26のカウント値が200hになり、カウント値の上位2ビットがメディアセクタアドレスラッチ部30から入力される2ビットの信号と一致する。応じて、比較結果信号CMPがHからLレベルへと立下がる。すなわち、そして、比較結果信号CMPは、カウント値が200h〜3FFhである間Lレベルとなる。この比較結果信号CMPの変化に応じて、ゲート回路28がクロック信号SCをライトイネーブル信号/WE♯としてバッファメモリに対して出力する。バッファメモリ4は、ライトイネーブル信号/WE♯が入力されるため、ライトイネーブル信号/WE♯の立上がりエッジにおけるアドレス信号ADRが示すアドレスにデータ入力であるデータ0h〜データ1FFhが書込まれる。

【0069】

時刻t3以降においては、SCカウンタ26のカウント値が400h以上となるため、比較結果信号CMPは再びHレベルになり、以降入力されるデータはバッファメモリへは書込まれない。

【0070】

図13は、バッファメモリからフラッシュメモリへのデータ転送の様子を示すタイミング図である。

【0071】

図13を参照して、メディアセクタアドレス(MA1,MA0)が(0,1)のときには、時刻t1〜t2において、フラッシュメモリのカラムアドレス0h〜1FFhには、ダミーデータである“FFh”が書込まれる。このダミーデータは、フラッシュメモリの消去直後の初期値に対応するデータであり、一般に、フラッシュメモリはこの初期値データを書込む動作を行なっても既に内部に保持されているデータが破壊されることはない。

【0072】

したがって、実施の形態1の記憶装置は、一括消去され、その後逐次データを追加していくような用途、例えば、デジタルカメラの画像の一時保存や、携帯型デジタルオーディオ機器の音響信号の保存等に好適に用いられる。

【0073】

時刻t2〜t3において、フラッシュメモリのカラムアドレス200h〜3FFhには、バッファメモリからデータが順次書込まれる。このデータはフラッシュメモリのセクタ容量の1/4に相当する512バイトのデータである。

【0074】

時刻t3以降は、時刻t1〜t2と同様に、ダミーデータである“FFh”が書込まれる。

【0075】

図14は、図13に示したバッファメモリからフラッシュメモリへのデータ転送の様子をさらに詳しく説明するための動作波形図である。

【0076】

図10、図14を参照して、時刻t0において、ホストシステムからの書込要求に応じてライトセクタイネーブル信号WSE♯がHレベルからLレベルへと立下がる。応じて、リセット信号RSTがHレベルからLレベルへと立下がり、SCカウンタ26のリセットが解除される。また、バッファメモリのアウトプットイネーブル入力信号/OE♯はHレベルからLレベルへと立下がり、バッファメモリ4は、アクセス可能な状態となる。

【0077】

時刻t1〜t2において、クロック信号SCの立上がりに同期して、セレクタ34が出力するデータ出力信号がフラッシュメモリへ書込まれる。そのときの書込カラムアドレスに対応するカウント値がSCカウンタ26によってカウントアップされる。時刻t1〜t2においてはメディアセクタアドレス(MA1,MA0)がSCカウンタ26の上位2ビットと一致しないので、データ出力信号DOはセレクタ34の“1”側の入力ノードに入力されている固定データ“FFh”である。

【0078】

時刻t2において、カウント値の変化に従って、比較結果信号CMPはHレベルからLレベルへと立下がり、アドレス信号ADRに指定されるアドレスのデータはバッファメモリ4から読出され、セレクタ34を介してデータ出力信号D0としてフラッシュメモリへと転送される。以降時刻t3に至るまでの間バッファメモリからフラッシュメモリへとデータ転送が行なわれる。

【0079】

データ0h〜データ1FFhの512バイトのデータの転送が終了すると、時刻t3において、カウント値の変化に従い比較結果信号CMPがLレベルからHレベルへと立上がるため、再びデータ出力信号はセレクタ34の“1”側の入力ノードに入力されている固定値“FFh”となる。

【0080】

以上説明したように、実施の形態1の記憶装置は、一括消去され、その後逐次データを追加していくような用途、例えば、デジタルカメラの画像の一時保存や、携帯型デジタルオーディオ機器の音響信号の保存等に好適に用いられる。

【0081】

そして、使用するフラッシュメモリの1セクタの容量よりもホストシステムとのデータ転送の単位容量であるメディアセクタ容量が小さい場合に、一時的なデータ格納を行なうバッファメモリの容量をメディアセクタ容量に合わせて小さくすることができるため、ハードウェアを構成する上でコスト的に有利な記憶装置を提供することができる。

【0082】

[実施の形態2]

図15は、実施の形態2の記憶装置51の概略構成を示すブロック図である。

【0083】

図15を参照して、記憶装置51は、ホストシステム12と記憶する外部データの授受を行なうためのものであり、ホストシステムからメディアアドレスを受けてアドレス変換を行い、ホストシステムの間で外部データを授受するためにデータ変換を行うデータ入出力部59と、データ入出力部59が変換したアドレス信号に応じてデータ授受を行うフラッシュメモリ60とを含む。データ入出力部59はフラッシュメモリ60が入出力するデータと外部データとの間のデータの変換を行う。

【0084】

データ入出力部59は、ホストシステム12とデータ転送を行なうホストインタフェイス部52と、ホストインタフェイス部52がホストシステム12とデータ転送を行なうために記憶データを一時的に格納する512バイトの容量を持つバッファメモリ54と、ホストインタフェイス部52からの指令に応じてバッファメモリ54とフラッシュメモリ60とのデータ授受のコントロールを行なうフラッシュインタフェイス部57とを含む。

【0085】

フラッシュインタフェイス部57は、フラッシュメモリの仕様にあわせたシーケンスで、読出や書込等の動作を設定するコマンドや、読出や書込時にメモリ領域を指定するためのアドレスをフラッシュメモリに送出するシーケンサ部56と、ホストシステム12から与えられたメディアセクタアドレスからフラッシュメモリのセクタアドレスとセクタアドレスで指定されたカラムの読出開始位置を指定するスタートカラムアドレスとを生成するカラムアドレス制御部58とを含む。

【0086】

図15において、フラッシュメモリ60は、データのリードおよびプログラムをセクタの任意のカラムアドレスから読出および書込開始をすることができる分割リード/プログラム機能を有する。

【0087】

フラッシュメモリ60は、各々が2048バイトの容量を持つ複数のセクタを有する。フラッシュメモリは、セクタアドレスが指定されると、指定されたセクタ容量分だけのデータをクロック信号に同期してシリアルに出力することができる。そして、スタートカラムアドレスがさらに指定されると、指定されたセクタのカラムアドレスに該当するデータからセクタの最終アドレスに該当するデータまでをクロック信号に同期してシリアルに出力することができる。

【0088】

図16は、実施の形態2におけるフラッシュメモリとバッファメモリとの対応関係を示すメモリマップである。

【0089】

図16に示されるメモリマップは、図2に示した実施の形態1に用いられるメモリマップと同様の割付を示しているため説明は繰返さない。

【0090】

図17は、メディアセクタアドレスがフラッシュセクタアドレスとスタートカラムアドレスとに変換されることを説明するための図である。

【0091】

図17を参照して、メディアセクタアドレスMA15〜MA0の上位14ビットは、フラッシュセクタアドレスSA13〜SA0として使用される。また、メディアセクタアドレスのうち下位2ビットであるMA1、MA0は、スタートカラムアドレスのうちそれぞれCA10、CA9として使用される。また、スタートカラムアドレスの他のビットであるCA11、CA8〜CA0はすべて“0h”に設定される。

【0092】

図18は、フラッシュメモリのスタートカラムアドレスとメディアセクタアドレスの下位2ビットとの関係を示す図である。

【0093】

図18を参照して、MA1、MA0がともに0であるときは、スタートカラムアドレスは0hに設定され、MA1、MA0がそれぞれ0、1であるときは、スタートカラムアドレスは200hに設定される。

【0094】

MA1、MA0がそれぞれ1、0であるときは、スタートカラムアドレスは400hに設定され、MA1、MA0がともに1であるときは、スタートカラムアドレスは600hに設定される。このアドレス変換は図15のカラムアドレス制御部58で行われるが、図18に対応する配線の接続をするだけで容易に実現できる。

【0095】

図19は、スタートカラムアドレスの説明をするための概念図である。

図19を参照して、1セクタが2048バイトであるときは、フラッシュセクタアドレスSAに対応して0h〜7FFhのカラムアドレスが存在する。スタートカラムアドレスCAを設定すると、設定したフラッシュセクタアドレスSA中のスタートカラムアドレスに対応するカラムのデータからクロック信号に同期して読出が開始される。

【0096】

図20は、分割リード/プログラム機能を有するフラッシュメモリからデータを読出す際のコマンド設定とアドレス設定とを説明するための動作波形図である。

【0097】

図20を参照して、時刻t1において、コマンドデータイネーブル信号/CDE♯がLレベルのときに、ライトイネーブル信号/WE♯の立上がりが検出されると、そのタイミングにおいて、リードコマンドがフラッシュメモリに取込まれる。

【0098】

時刻t2において、ライトイネーブル信号/WE♯の立上がりエッジにおいて、セクタアドレスの下位8ビットであるSA(1)が取込まれる。次いで時刻t3において、ライトイネーブル信号/WE♯の立上がりエッジにおいて、セクタアドレスの上位6ビットであるSA(2)がフラッシュメモリに取込まれる。

【0099】

次いで、時刻t4において、ライトイネーブル信号/WE♯の立上がりエッジでスタートカラムアドレスCAの下位8ビットであるCA(1)がフラッシュメモリに取込まれる。続いて、時刻t5において、ライトイネーブル信号/WE♯の立上がりエッジでスタートカラムアドレスの上位4ビットであるCA(2)が取込まれる。

【0100】

時刻t6以降は、クロック信号SCに同期してアドレス/データ入出力端子から指定されたスタートカラムアドレスのデータを先頭にしてフラッシュメモリからデータが出力される。

【0101】

図21は、実施の形態2においてフラッシュメモリにデータを書込む入力波形を示す図である。

【0102】

図21を参照して、時刻t1において、コマンドデータイネーブル入力/CDE♯がLレベルのときに、ライトイネーブル信号/WE♯の立上がりエッジが検出されると、プログラムコマンドがフラッシュメモリに読込まれる。

【0103】

続いて、時刻t2において、ライトイネーブル信号/WE♯の立上がりエッジでセクタアドレスの下位8ビットであるSA(1)がフラッシュメモリに取込まれる。続いて、時刻t3において、ライトイネーブル信号/WE♯の立上がりエッジでセクタアドレスの上位6ビットであるSA(2)がフラッシュメモリに取込まれる。

【0104】

時刻t4において、ライトイネーブル信号/WE♯の立上がりエッジでスタートカラムアドレスの下位8ビットであるCA(1)がフラッシュメモリに取込まれる。続いて、時刻t5において、ライトイネーブル信号/WE♯の立上がりエッジでスタートカラムアドレスの上位4ビットであるCA(2)がフラッシュメモリに取込まれる。以上でアドレス設定が終了する。

【0105】

時刻t6以降は、設定されたセクタアドレスのスタートカラムアドレスに対応するデータを先頭としてクロック信号SCに同期してシリアルにデータ入力がされ対応するアドレスにデータが書込まれる。

【0106】

図20、図21で示したフラッシュメモリに対するコマンドやアドレス信号を与える制御は、図15におけるフラッシュインタフェイスシーケンサ部56で行なわれる。

【0107】

図22は、実施の形態2の記憶装置の処理のメインフローを示す図である。

図22を参照して、実施の形態2の記憶装置の処理のメインフローは、図5に示した実施の形態1の読出処理ステップS04に代えてステップS104を含み、書込処理ステップS05に代えてステップS105を含む点が図5で示したフローと異なる。他の部分は図5で示したフローと同様であるので説明は繰返さない。

【0108】

図23は、図22に示したステップS104の読出処理の詳細を示すフローチャートである。

【0109】

図23を参照して、ステップS111において、読出が開始される。

次いで、ステップS112において、メディアセクタアドレスがホストシステムから受信される。続いて、ステップS113において、受信したメディアセクタアドレスを変換してフラッシュメモリのセクタアドレスSAおよびスタートカラムアドレスCAが発生される。続いて、ステップS114において、フラッシュメモリの分割リードコマンドが設定されセクタアドレスSAおよびスタートカラムアドレスCAも指定される。そして、ステップS115において、データがフラッシュメモリから読出され、バッファメモリに書込まれる。

【0110】

バッファメモリへの書込が終了すると、ステップS116においてホストシステムに対して割込信号が送出される。

【0111】

続いて、ステップS117において、バッファメモリに書込まれたデータはホストシステムに対して読出データとして送出される。そして、ステップS118において、読出が終了する。

【0112】

図24は、図23で示した読出処理の各ステップが記憶装置内のどのブロックで実施されているかを示す図である。

【0113】

図24を参照して、まずホストシステムからコントローラやバッファメモリに対してメディアセクタアドレスの読出要求が発信される。コントローラというのは、図15におけるホストインタフェイス部52およびフラッシュインタフェイスシーケンサ部56に該当する。

【0114】

これを受けてコントローラではメディアセクタアドレスからフラッシュメモリのセクタアドレスSAとスタートカラムアドレスCAとが生成される。そしてコントローラからはリードコマンドとセクタアドレスおよびスタートカラムアドレスとがフラッシュメモリに送出される。応じて、フラッシュメモリでは、分割リード動作が行なわれ、512バイトのデータがバッファメモリへと出力される。バッファメモリへのデータ書込が終了すると、コントローラは指定されたメディアセクタアドレスのデータ読出をホストシステムに対して要求する。そして、バッファメモリからはホストシステムに対してデータの読出が行なわれ、読出動作は終了する。

【0115】

図25は、図22に示したステップS105における書込処理の詳細を示すフローチャートである。

【0116】

図25を参照して、まずステップS121において書込が開始される。

続いてステップS122においてホストシステムから発信されたメディアセクタアドレスが受信される。

【0117】

続いて、ステップS123において、記憶装置がホストシステムに対してデータを要求する。そして、ステップS124においてホストシステムからデータを受信する。このデータは、ステップS125においてバッファメモリに書込まれる。

【0118】

そして、ステップS126において、ステップS122で受信したメディアセクタアドレスからフラッシュメモリのセクタアドレスSAおよびスタートカラムアドレスCAが生成される。続いてステップS127において、フラッシュメモリに対して分割プログラムコマンドが設定され、続いてセクタアドレスSAおよびスタートカラムアドレスCAの指定がされる。

【0119】

そして、ステップS128において、データが、バッファメモリから読出されフラッシュメモリに書込まれる。そしてステップS129において、データの書込が終了する。

【0120】

図26は、図25に示した書込処理の各ステップがホストシステムとコントローラおよびバッファメモリとフラッシュメモリとの間でどのように行なわれるかを示す図である。

【0121】

図26を参照して、まずホストシステムからメディアセクタアドレスの書込要求がコントローラに向けて発信される。続いて、コントローラはこれを受けてメディアセクタアドレスのデータ書込要求をホストシステムに対して行なう。応じてホストシステムはメディアセクタアドレスに対するデータの書込を行なう。このデータはコントローラを経由してバッファメモリに入力される。

【0122】

続いて、コントローラでは、受信していたメディアセクタアドレスからフラッシュメモリのセクタアドレスSAおよびスタートカラムアドレスCAが生成される。そして、コントローラがフラッシュメモリに対してプログラムコマンドとセクタアドレス/SAおよびスタートカラムアドレス/CAの設定を行なう。応じて、フラッシュメモリは、分割プログラム動作を行なう。そしてバッファからは512バイトのデータがフラッシュメモリに対して入力され、所定のカラムアドレスを先頭にしてデータ書込が行なわれる。フラッシュメモリへバッファメモリから512バイトの書込データが入力されると、その後、所定のウエイト時間経過後書込が終了する。

【0123】

実施の形態2においては、バッファメモリのアドレス制御およびメディアセクタアドレスからフラッシュメモリに与えるアドレス信号の生成は図15におけるカラムアドレス制御部58で行なわれる。

【0124】

図27は、図15におけるカラムアドレス制御部58の詳細を示すブロック図である。

【0125】

図27を参照して、カラムアドレス制御部58は、記憶装置内部で生成されるリードセクタイネーブル信号RSE♯をクロック信号SCの立上がりに同期してラッチするフリップフロップ72と、フリップフロップ72の出力と記憶装置内部で生成されるライトセクタイネーブル信号WSE♯との論理和をリセット信号RSTとして出力するAND回路74と、リセット信号RSTによってリセットされその後クロック信号SCの立上がりに応答してカウントアップを開始する9ビットのSCカウンタ76と、ホストシステムより16ビットのメディアセクタアドレスをラッチして上位14ビット、下位2ビットをそれぞれセクタアドレスSA0〜SA15、スタートカラムアドレスCA0〜1としてシーケンサ部6へ出力するメディアセクタアドレスラッチ部30と、フリップフロップ72の出力とクロック信号SCとを受けてライトイネーブル信号/WE♯を出力するゲート回路78とを含む。

【0126】

尚、説明の便宜のため、図27にはバッファメモリ54が記載されている。バッファメモリ54は、SCカウンタ76の計数値9ビットをアドレス信号ADRとして受け、ライトセクタイネーブル信号WSE♯をアウトプットイネーブル信号/OE♯として受け、ゲート回路78の出力をライトイネーブル信号/WE♯として受けこれらに応答してフラッシュメモリからのデータ入力DIを受けて保持し、またはフラッシュメモリへデータ出力DOを送出する。

【0127】

以上説明したように、実施の形態2においては、ホストインタフェイス部がホストシステムとデータ転送を行なうときにデータを一時的に格納するバッファメモリの容量をフラッシュメモリの1セクタの容量よりも小さくできるため、コストメリットのある記憶装置を提供することができる。さらに、分割リード/プログラム可能なフラッシュメモリを搭載し使用することで、メディアセクタ単位で読出および再書込が可能である。

【0128】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【0129】

【発明の効果】

本発明のある局面に従うフラッシュメモリを搭載する記憶装置は、セクタ読出をするフラッシュメモリを記憶用半導体装置として用いる場合小容量のバッファメモリを搭載するのでコスト的に有利である。

【0130】

本発明の他のフラッシュメモリを搭載する記憶装置は、ダミーデータとしてフラッシュメモリが消去された直後のデータと同じデータを書込むため、既にデータ保持が行なわれた部分のデータが失われることはない。

【0131】

本発明のさらに他のフラッシュメモリを搭載する記憶装置は、フラッシュメモリのセクタ容量を外部のメディアセクタ容量で区切って使用することができ、効率的にフラッシュメモリを使用することができる。

【0132】

本発明のさらに他のフラッシュメモリを搭載する記憶装置は、セクタデータの読出をする際にも小容量のバッファメモリを使用することができる。

【0133】

本発明のさらに他のフラッシュメモリを搭載する記憶装置は、フラッシュメモリのセクタ容量を外部のメディアセクタ容量で区切って使用することができ、効率的にフラッシュメモリを使用することができる。

【0134】

本発明のさらに他のフラッシュメモリを搭載する記憶装置は、小容量のバッファメモリを搭載するのでコスト的に有利であり、さらに、メディアセクタ単位でデータの再書込が可能である。

【図面の簡単な説明】

【図1】 フラッシュメモリを搭載した記憶装置1の概略構成を示すブロック図である。

【図2】 実施の形態1におけるフラッシュメモリとバッファメモリとのアドレスの対応関係を示すメモリマップである。

【図3】 メディアセクタアドレスをフラッシュセクタアドレスとカラムアドレスオフセット生成ビットとに変換する説明をするための図である。

【図4】 スタートフラッシュカラムアドレスオフセットとメディアセクタアドレスの下位2ビットとの関係を示す図である。

【図5】 実施の形態1の記憶装置の処理のメインフローを示す図である。

【図6】 図5に示したステップS04の読出処理の詳細を示すフローチャートである。

【図7】 図6に示した読出処理の各ステップが記憶装置内のどのブロックで実施されているかを示す図である。

【図8】 図5に示したステップS05における書込処理の詳細を示すフローチャートである。

【図9】 図8に示した書込処理の各ステップがホストシステムとコントローラおよびバッファメモリとフラッシュメモリとの間でどのように行なわれるかを示す図である。

【図10】 図1に示したデータ転送制御部8の詳細を示すブロック図である。

【図11】 フラッシュメモリからバッファメモリへのデータ転送の様子を示すタイミング図である。

【図12】 図11に示したバッファメモリへのデータ書込の動作をより詳細に示した動作波形図である。

【図13】 バッファメモリからフラッシュメモリへのデータ転送の様子を示すタイミング図である。

【図14】 図13に示したバッファメモリからフラッシュメモリへのデータ転送の様子をさらに詳しく説明するための動作波形図である。

【図15】 実施の形態2の記憶装置51の概略構成を示すブロック図である。

【図16】 実施の形態2におけるフラッシュメモリとバッファメモリとの対応関係を示すメモリマップである。

【図17】 メディアセクタアドレスをフラッシュセクタアドレスとスタートカラムアドレスとに変換を説明するための図である。

【図18】 スタートカラムアドレスとメディアセクタアドレスの下位2ビットとの関係を示す図である。

【図19】 スタートカラムアドレスの説明をするための概念図である。

【図20】 分割リード/プログラム機能を有するフラッシュメモリからデータを読出す際のコマンド設定とアドレス設定とを説明するための動作波形図である。

【図21】 実施の形態2においてフラッシュメモリにデータを書込む入力波形を示す図である。

【図22】 実施の形態2の記憶装置の処理のメインフローを示す図である。

【図23】 図22に示したステップS104の読出処理の詳細を示すフローチャートである。

【図24】 図23で示した読出処理の各ステップが記憶装置内のどのブロックで実施されているかを示す図である。

【図25】 図22に示したステップS105における書込処理の詳細を示すフローチャートである。

【図26】 図25に示した書込処理の各ステップがホストシステムとコントローラおよびバッファメモリとフラッシュメモリとの間でどのように行なわれるかを示す図である。

【図27】 図15におけるカラムアドレス制御部58の詳細を示すブロック図である。

【符号の説明】

1,51 記憶装置、2,52 ホストインタフェイス部、4,54 バッファメモリ、6,56 フラッシュインタフェイスシーケンサ、8 データ転送制御部、10,60 フラッシュメモリ、58 カラムアドレス制御部、22 フリップフロップ、24 AND回路、26 SCカウンタ、28 ゲート回路、30 メディアセクタアドレスラッチ部、32 比較器、34 セレクタ。

Claims (8)

- ホストシステムから外部書込アドレス信号と外部書込データとを受けてデータ記憶を行う書込モードを備える記憶装置であって、

外部書込データ容量より容量の大きい内部書込データ容量を単位として複数のデータの書込がなされるフラッシュメモリを備え、

前記フラッシュメモリは、前記書込モードにおいて、内部書込アドレス信号を受けて、内部書込データに含まれる複数のデータを取込み保持し、

前記書込モードにおいて、前記外部書込アドレス信号を受けて前記内部書込アドレス信号を発生し、前記外部書込データを受けて保持して前記外部書込データと前記外部書込アドレス信号とに基づいて前記内部書込データを出力するデータ入出力部をさらに備え、

前記データ入出力部は、

前記書込モードにおいて、前記ホストシステムから前記外部書込データおよび前記外部書込アドレス信号を受ける第1のインタフェイス部と、

前記外部書込データ容量以上で、かつ、前記内部書込データ容量より小さい記憶容量を有し、前記書込モードにおいて前記第1のインタフェイス部から前記外部書込データを受け取る、バッファメモリと、

前記書込モードにおいて、前記第1のインタフェイス部から前記外部書込アドレス信号を受けて前記内部書込アドレス信号を発生し、前記バッファメモリから読出した前記外部書込データに、前記フラッシュメモリを構成するメモリセルの消去状態に対応するデータを加えて前記内部書込データを発生する、第2のインタフェイス部とを含む、フラッシュメモリを搭載する記憶装置。 - 前記フラッシュメモリは、前記内部書込アドレス信号に対応し、前記内部書込データ容量と同じ容量を持つメモリ領域単位を有し、前記メモリ領域単位はオフセット信号に対応する複数の領域を含み、

前記第2のインタフェイス部は、前記外部書込アドレス信号に含まれる前記オフセット信号を出力し、前記外部書込データに対応する前記内部書込データを前記メモリ領域単位の前記オフセット信号に対応する領域に書き込む、請求項1に記載のフラッシュメモリを搭載する記憶装置。 - 前記第2のインタフェイス部は、前記メモリ領域単位の前記外部書込データに対応する前記内部書込データを書き込んだ残りの領域に、前記フラッシュメモリ

を構成するメモリセルの消去状態に対応するデータを書き込む、請求項2に記載のフラッシュメモリを搭載する記憶装置。 - 前記内部書込データ容量は、前記外部書込データ容量の整数倍である、請求項3に記載のフラッシュメモリを搭載する記憶装置。

- 前記フラッシュメモリは、クロックに同期して前記内部書込データを順次取込み、

前記第2のインタフェイス部は、

前記バッファメモリに対する読出制御信号を発生して前記バッファメモリから前記外部書込データを受けて前記内部書込データを発生し、前記外部書込アドレス信号から前記内部書込アドレス信号を発生する、データ転送制御部を有し、

前記データ転送制御部は、

前記フラッシュメモリに前記内部書込データの書込が開始されるときに、前記クロックのカウントを開始するカウンタと、

前記外部書込アドレス信号に含まれるオフセット信号と前記カウンタのカウント値の上位から所定数ビットとが一致した時に一致信号を出力する比較器と、

前記バッファメモリが前記クロックに同期して前記外部書込データを出力するように前記一致信号に応じて読出制御信号を前記バッファメモリに与えるゲート回路と、

前記一致信号が非活性化されている時は、前記フラッシュメモリを構成するメモリセルの消去状態に対応するデータを前記フラッシュメモリに与え、前記一致信号が活性化した時は前記バッファメモリから読出された前記外部書込データを前記フラッシュメモリに与える選択回路とを有する、請求項2に記載のフラッシュメモリを搭載する記憶装置。 - 前記記憶装置は、前記ホストシステムから外部読出アドレス信号を受けて前記ホストシステムに外部読出データを出力する読出モードをさらに備え、

前記データ入出力部は、前記読出モード時に、前記外部読出アドレス信号を受けて内部読出アドレス信号を発生して前記フラッシュメモリに与え、前記フラッシュメモリから読出される内部読出データの一部を選択して前記外部読出データとして保持した後、前記ホストシステムに対して前記外部読出データを出力し、

前記第1のインタフェイス部は、前記読出モード時に、前記ホストシステムから受けた前記外部読出アドレス信号に応じた前記外部読出データを前記ホストシステムに出力し、

前記バッファメモリは、前記外部読出データ容量以上で、かつ、前記内部読出データ容量より小さい記憶容量を有し、前記読出モード時に、前記第1のインタフェイス部に対して保持していた前記外部読出データを出力し、

前記第2のインタフェイス部は、前記読出モード時に、前記第1のインタフェイス部から前記外部読出アドレス信号を受けて前記内部読出アドレス信号を発生して前記フラッシュメモリに与えて前記フラッシュメモリから前記内部読出データが含む複数のデータを読出し、前記内部読出しデータの一部を前記外部読出データとしてバッファメモリに送出する、請求項1に記載のフラッシュメモリを搭載する記憶装置。 - 前記フラッシュメモリは、クロックに同期して前記内部読出データを順次出力し、

前記第2のインタフェイス部は、

前記外部読出アドレス信号から前記内部読出アドレス信号を発生し、前記内部読出データの一部を選択して前記外部読出データとして前記バッファメモリが格納するように前記バッファメモリへ書込制御信号を発生する、データ転送制御部を有し、

前記データ転送制御部は、

前記フラッシュメモリから前記内部読出データの読出が開始されるときに、前記クロックのカウントを開始するカウンタと、

前記外部書込アドレス信号に含まれるオフセット信号と前記カウンタのカウント値の上位から所定数ビットとが一致した時に一致信号を出力する比較器と、

前記バッファメモリが前記クロックに同期して前記内部読出データの一部を前記外部読出データとして格納するように前記一致信号に応じて前記書込制御信号を前記バッファメ

モリに与えるゲート回路とを有する、請求項6に記載のフラッシュメモリを搭載する記憶装置。 - フラッシュメモリと、

ホストシステムから入力される外部アドレスに対応する内部主アドレスおよび内部副アドレスを発生し、前記ホストシステムから入力される外部データを前記フラッシュメモリに出力、または前記フラッシュメモリから入力されるデータを前記外部データとしてホストシステムへ出力する、データ入出力部とを備え、

前記データ入出力部は、

前記内部主アドレスによって前記フラッシュメモリの前記外部データの容量より大きい容量を持つメモリ領域単位を選択し、前記内部副アドレスによって前記メモリ領域単位内のデータ入出力開始位置を指定し、前記データ入出力開始位置から前記フラッシュメモリのデータ読出、または前記データ入出力開始位置から前記フラッシュメモリへのデータの書込を行い、

前記データ入出力部は、

前記ホストシステムと前記フラッシュメモリとの間のタイミング調整をするために前記外部データを一時的に保持するバッファメモリを含み、

前記バッファメモリの記憶容量は、前記外部データの容量以上で、前記メモリ領域単位の容量より小さい、フラッシュメモリを搭載する記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP09801999A JP4141581B2 (ja) | 1999-04-05 | 1999-04-05 | フラッシュメモリを搭載する記憶装置 |

| US09/395,941 US6434658B1 (en) | 1999-04-05 | 1999-09-14 | Memory device operable with a small-capacity buffer memory and having a flash memory |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP09801999A JP4141581B2 (ja) | 1999-04-05 | 1999-04-05 | フラッシュメモリを搭載する記憶装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008122579A Division JP4731584B2 (ja) | 2008-05-08 | 2008-05-08 | フラッシュメモリを搭載する記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000293427A JP2000293427A (ja) | 2000-10-20 |

| JP2000293427A5 JP2000293427A5 (ja) | 2005-11-04 |

| JP4141581B2 true JP4141581B2 (ja) | 2008-08-27 |

Family

ID=14208160

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP09801999A Expired - Fee Related JP4141581B2 (ja) | 1999-04-05 | 1999-04-05 | フラッシュメモリを搭載する記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6434658B1 (ja) |

| JP (1) | JP4141581B2 (ja) |

Families Citing this family (61)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6684289B1 (en) * | 2000-11-22 | 2004-01-27 | Sandisk Corporation | Techniques for operating non-volatile memory systems with data sectors having different sizes than the sizes of the pages and/or blocks of the memory |

| JP4711531B2 (ja) * | 2001-03-23 | 2011-06-29 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| JP4082913B2 (ja) * | 2002-02-07 | 2008-04-30 | 株式会社ルネサステクノロジ | メモリシステム |

| WO2003085677A1 (fr) * | 2002-04-05 | 2003-10-16 | Renesas Technology Corp. | Memoire non volatile |

| US7174348B1 (en) * | 2002-11-26 | 2007-02-06 | Unisys Corporation | Computer program having an object module and a software development tool integration module which automatically interlink artifacts generated in different phases of a software project |

| US7406628B2 (en) * | 2003-07-15 | 2008-07-29 | Seagate Technology Llc | Simulated error injection system in target device for testing host system |

| US7173852B2 (en) * | 2003-10-03 | 2007-02-06 | Sandisk Corporation | Corrected data storage and handling methods |

| KR100528482B1 (ko) * | 2003-12-31 | 2005-11-15 | 삼성전자주식회사 | 데이타를 섹터 단위로 랜덤하게 입출력할 수 있는 플래시메모리 시스템 |

| US7600087B2 (en) * | 2004-01-15 | 2009-10-06 | Hitachi, Ltd. | Distributed remote copy system |

| KR100606242B1 (ko) * | 2004-01-30 | 2006-07-31 | 삼성전자주식회사 | 불휘발성 메모리와 호스트간에 버퍼링 동작을 수행하는멀티 포트 휘발성 메모리 장치, 이를 이용한 멀티-칩패키지 반도체 장치 및 이를 이용한 데이터 처리장치 |

| JP2005285191A (ja) * | 2004-03-29 | 2005-10-13 | Nec Electronics Corp | 不揮発性半導体記憶装置及びその駆動方法 |

| JP4713867B2 (ja) * | 2004-09-22 | 2011-06-29 | 株式会社東芝 | メモリコントローラ,メモリ装置及びメモリコントローラの制御方法 |

| US7412560B2 (en) * | 2004-12-16 | 2008-08-12 | Sandisk Corporation | Non-volatile memory and method with multi-stream updating |

| US7315916B2 (en) * | 2004-12-16 | 2008-01-01 | Sandisk Corporation | Scratch pad block |

| US7386655B2 (en) * | 2004-12-16 | 2008-06-10 | Sandisk Corporation | Non-volatile memory and method with improved indexing for scratch pad and update blocks |

| US7395404B2 (en) * | 2004-12-16 | 2008-07-01 | Sandisk Corporation | Cluster auto-alignment for storing addressable data packets in a non-volatile memory array |

| US7366826B2 (en) * | 2004-12-16 | 2008-04-29 | Sandisk Corporation | Non-volatile memory and method with multi-stream update tracking |

| KR100666169B1 (ko) * | 2004-12-17 | 2007-01-09 | 삼성전자주식회사 | 플래쉬 메모리 데이터 저장장치 |

| KR100737913B1 (ko) * | 2005-10-04 | 2007-07-10 | 삼성전자주식회사 | 반도체 메모리 장치의 읽기 방법 |

| KR100660553B1 (ko) | 2005-10-18 | 2006-12-22 | 삼성전자주식회사 | 데이터 버스트 주파수를 증가시킬 수 있는 원낸드 플래시메모리 장치 |

| US20070100893A1 (en) * | 2005-10-31 | 2007-05-03 | Sigmatel, Inc. | System and method for accessing data from a memory device |

| JP4661748B2 (ja) * | 2006-09-22 | 2011-03-30 | Tdk株式会社 | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法 |

| JP2008112285A (ja) * | 2006-10-30 | 2008-05-15 | Toshiba Corp | 不揮発性メモリシステム |

| JP4498341B2 (ja) * | 2006-11-20 | 2010-07-07 | 株式会社東芝 | メモリシステム |

| KR100898653B1 (ko) * | 2007-07-25 | 2009-05-22 | 주식회사 하이닉스반도체 | 플래시 메모리 소자 및 프로그램 방법 |

| US9201790B2 (en) * | 2007-10-09 | 2015-12-01 | Seagate Technology Llc | System and method of matching data rates |

| US8959307B1 (en) | 2007-11-16 | 2015-02-17 | Bitmicro Networks, Inc. | Reduced latency memory read transactions in storage devices |

| US8665601B1 (en) | 2009-09-04 | 2014-03-04 | Bitmicro Networks, Inc. | Solid state drive with improved enclosure assembly |

| US9135190B1 (en) | 2009-09-04 | 2015-09-15 | Bitmicro Networks, Inc. | Multi-profile memory controller for computing devices |

| US8447908B2 (en) | 2009-09-07 | 2013-05-21 | Bitmicro Networks, Inc. | Multilevel memory bus system for solid-state mass storage |

| US8560804B2 (en) | 2009-09-14 | 2013-10-15 | Bitmicro Networks, Inc. | Reducing erase cycles in an electronic storage device that uses at least one erase-limited memory device |

| US9372755B1 (en) | 2011-10-05 | 2016-06-21 | Bitmicro Networks, Inc. | Adaptive power cycle sequences for data recovery |

| US9043669B1 (en) | 2012-05-18 | 2015-05-26 | Bitmicro Networks, Inc. | Distributed ECC engine for storage media |

| KR20140082173A (ko) * | 2012-12-24 | 2014-07-02 | 에스케이하이닉스 주식회사 | 어드레스 카운팅 회로 및 이를 이용한 반도체 장치 |

| US9652376B2 (en) * | 2013-01-28 | 2017-05-16 | Radian Memory Systems, Inc. | Cooperative flash memory control |

| US9423457B2 (en) | 2013-03-14 | 2016-08-23 | Bitmicro Networks, Inc. | Self-test solution for delay locked loops |

| US9720603B1 (en) | 2013-03-15 | 2017-08-01 | Bitmicro Networks, Inc. | IOC to IOC distributed caching architecture |

| US10489318B1 (en) | 2013-03-15 | 2019-11-26 | Bitmicro Networks, Inc. | Scatter-gather approach for parallel data transfer in a mass storage system |

| US9798688B1 (en) | 2013-03-15 | 2017-10-24 | Bitmicro Networks, Inc. | Bus arbitration with routing and failover mechanism |

| US9934045B1 (en) | 2013-03-15 | 2018-04-03 | Bitmicro Networks, Inc. | Embedded system boot from a storage device |

| US9672178B1 (en) | 2013-03-15 | 2017-06-06 | Bitmicro Networks, Inc. | Bit-mapped DMA transfer with dependency table configured to monitor status so that a processor is not rendered as a bottleneck in a system |

| US9430386B2 (en) | 2013-03-15 | 2016-08-30 | Bitmicro Networks, Inc. | Multi-leveled cache management in a hybrid storage system |

| US9501436B1 (en) | 2013-03-15 | 2016-11-22 | Bitmicro Networks, Inc. | Multi-level message passing descriptor |

| US10120694B2 (en) | 2013-03-15 | 2018-11-06 | Bitmicro Networks, Inc. | Embedded system boot from a storage device |

| US9400617B2 (en) | 2013-03-15 | 2016-07-26 | Bitmicro Networks, Inc. | Hardware-assisted DMA transfer with dependency table configured to permit-in parallel-data drain from cache without processor intervention when filled or drained |

| US9875205B1 (en) | 2013-03-15 | 2018-01-23 | Bitmicro Networks, Inc. | Network of memory systems |

| US9734067B1 (en) | 2013-03-15 | 2017-08-15 | Bitmicro Networks, Inc. | Write buffering |

| US9971524B1 (en) | 2013-03-15 | 2018-05-15 | Bitmicro Networks, Inc. | Scatter-gather approach for parallel data transfer in a mass storage system |

| US9842024B1 (en) | 2013-03-15 | 2017-12-12 | Bitmicro Networks, Inc. | Flash electronic disk with RAID controller |

| US9916213B1 (en) | 2013-03-15 | 2018-03-13 | Bitmicro Networks, Inc. | Bus arbitration with routing and failover mechanism |

| US10055150B1 (en) | 2014-04-17 | 2018-08-21 | Bitmicro Networks, Inc. | Writing volatile scattered memory metadata to flash device |

| US9811461B1 (en) | 2014-04-17 | 2017-11-07 | Bitmicro Networks, Inc. | Data storage system |

| US9952991B1 (en) | 2014-04-17 | 2018-04-24 | Bitmicro Networks, Inc. | Systematic method on queuing of descriptors for multiple flash intelligent DMA engine operation |

| US10025736B1 (en) | 2014-04-17 | 2018-07-17 | Bitmicro Networks, Inc. | Exchange message protocol message transmission between two devices |

| US10042792B1 (en) | 2014-04-17 | 2018-08-07 | Bitmicro Networks, Inc. | Method for transferring and receiving frames across PCI express bus for SSD device |

| US10078604B1 (en) | 2014-04-17 | 2018-09-18 | Bitmicro Networks, Inc. | Interrupt coalescing |

| US10552050B1 (en) | 2017-04-07 | 2020-02-04 | Bitmicro Llc | Multi-dimensional computer storage system |

| FR3065303B1 (fr) * | 2017-04-12 | 2019-06-07 | Stmicroelectronics (Rousset) Sas | Procede d'ecriture dans un dispositif de memoire non volatile et dispositif de memoire non volatile correspondant |

| US11030148B2 (en) * | 2018-04-04 | 2021-06-08 | Lawrence Livermore National Security, Llc | Massively parallel hierarchical control system and method |

| JP2022074450A (ja) * | 2020-11-04 | 2022-05-18 | キオクシア株式会社 | メモリカード、メモリシステム、及びファイルの断片化解消方法 |

| KR20220060372A (ko) * | 2020-11-04 | 2022-05-11 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 그것의 동작방법 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08137634A (ja) * | 1994-11-09 | 1996-05-31 | Mitsubishi Electric Corp | フラッシュディスクカード |

| JPH08212019A (ja) * | 1995-01-31 | 1996-08-20 | Mitsubishi Electric Corp | 半導体ディスク装置 |

| US5765002A (en) * | 1995-03-13 | 1998-06-09 | Intel Corporation | Method and apparatus for minimizing power consumption in a microprocessor controlled storage device |

| JPH09244961A (ja) * | 1996-03-08 | 1997-09-19 | Mitsubishi Electric Corp | フラッシュata−pcカード |

| JPH10207726A (ja) | 1997-01-23 | 1998-08-07 | Oki Electric Ind Co Ltd | 半導体ディスク装置 |

| JP3544859B2 (ja) * | 1998-05-11 | 2004-07-21 | 富士通株式会社 | 不揮発性半導体メモリを使用した2次記憶装置 |

-

1999

- 1999-04-05 JP JP09801999A patent/JP4141581B2/ja not_active Expired - Fee Related

- 1999-09-14 US US09/395,941 patent/US6434658B1/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20020083262A1 (en) | 2002-06-27 |

| US6434658B1 (en) | 2002-08-13 |

| JP2000293427A (ja) | 2000-10-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4141581B2 (ja) | フラッシュメモリを搭載する記憶装置 | |

| US7334080B2 (en) | Nonvolatile memory with independent access capability to associated buffer | |

| US7392343B2 (en) | Memory card having a storage cell and method of controlling the same | |

| US8036040B2 (en) | Memory system with improved efficiency of data transfer between host, buffer, and nonvolatile memory | |

| US7409473B2 (en) | Off-chip data relocation | |

| US5822251A (en) | Expandable flash-memory mass-storage using shared buddy lines and intermediate flash-bus between device-specific buffers and flash-intelligent DMA controllers | |

| US5920884A (en) | Nonvolatile memory interface protocol which selects a memory device, transmits an address, deselects the device, subsequently reselects the device and accesses data | |

| US20060221719A1 (en) | Semiconductor memory card, semiconductor memory control apparatus, and semiconductor memory control method | |

| US20070300011A1 (en) | Memory card, semiconductor device, and method of controlling semiconductor memory | |

| JP2010152913A (ja) | セクタ書き込み操作時間を効果的に減少させるための不揮発性メモリユニット内のブロックの構成 | |

| JP2009259253A (ja) | パイプラインメモリのための効率的な読出し、書込み方法 | |

| JPH1185609A (ja) | 半導体記憶装置及びそのデータ管理方法 | |

| JP4034971B2 (ja) | メモリコントローラおよびメモリシステム装置 | |

| JP2019121370A (ja) | メモリ装置 | |

| US7427031B2 (en) | Semiconductor memory device | |

| JP2003036205A (ja) | 記憶装置 | |

| JP2002312232A (ja) | 半導体記憶装置 | |

| JP2000298992A (ja) | 多値記憶不揮発性半導体メモリの制御装置 | |

| US6829195B2 (en) | Semiconductor memory device and information processing system | |

| US20020136079A1 (en) | Semiconductor memory device and information processing system | |

| JPH09171486A (ja) | Pcカード | |

| JP2001051896A (ja) | 記憶装置 | |

| US10261714B2 (en) | Memory controller and memory system including same | |

| JP4731584B2 (ja) | フラッシュメモリを搭載する記憶装置 | |

| JPH1139245A (ja) | 半導体デバイス制御装置および半導体デバイス制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050811 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050811 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080117 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080129 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080318 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080415 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080508 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080603 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080611 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110620 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110620 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110620 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120620 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120620 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130620 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130620 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140620 Year of fee payment: 6 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |