JP4037561B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4037561B2 JP4037561B2 JP18187899A JP18187899A JP4037561B2 JP 4037561 B2 JP4037561 B2 JP 4037561B2 JP 18187899 A JP18187899 A JP 18187899A JP 18187899 A JP18187899 A JP 18187899A JP 4037561 B2 JP4037561 B2 JP 4037561B2

- Authority

- JP

- Japan

- Prior art keywords

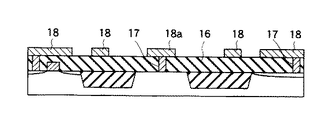

- alignment mark

- barrier metal

- aluminum

- deposited

- interlayer insulating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/525—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections

- H01L23/5256—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections comprising fuses, i.e. connections having their state changed from conductive to non-conductive

- H01L23/5258—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections comprising fuses, i.e. connections having their state changed from conductive to non-conductive the change of state resulting from the use of an external beam, e.g. laser beam or ion beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/544—Marks applied to semiconductor devices or parts, e.g. registration marks, alignment structures, wafer maps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54426—Marks applied to semiconductor devices or parts for alignment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54453—Marks applied to semiconductor devices or parts for use prior to dicing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54453—Marks applied to semiconductor devices or parts for use prior to dicing

- H01L2223/5446—Located in scribe lines

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18187899A JP4037561B2 (ja) | 1999-06-28 | 1999-06-28 | 半導体装置の製造方法 |

| US09/604,791 US6392300B1 (en) | 1999-06-28 | 2000-06-28 | Semiconductor device having an alignment mark formed on the uppermost layer of a multilayer wire |

| CN00122585.5A CN1199265C (zh) | 1999-06-28 | 2000-06-28 | 半导体器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18187899A JP4037561B2 (ja) | 1999-06-28 | 1999-06-28 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001015403A JP2001015403A (ja) | 2001-01-19 |

| JP2001015403A5 JP2001015403A5 (enExample) | 2005-04-28 |

| JP4037561B2 true JP4037561B2 (ja) | 2008-01-23 |

Family

ID=16108456

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP18187899A Expired - Fee Related JP4037561B2 (ja) | 1999-06-28 | 1999-06-28 | 半導体装置の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6392300B1 (enExample) |

| JP (1) | JP4037561B2 (enExample) |

| CN (1) | CN1199265C (enExample) |

Families Citing this family (40)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6965165B2 (en) | 1998-12-21 | 2005-11-15 | Mou-Shiung Lin | Top layers of metal for high performance IC's |

| US7381642B2 (en) | 2004-09-23 | 2008-06-03 | Megica Corporation | Top layers of metal for integrated circuits |

| US7405149B1 (en) * | 1998-12-21 | 2008-07-29 | Megica Corporation | Post passivation method for semiconductor chip or wafer |

| US6784516B1 (en) * | 2000-10-06 | 2004-08-31 | International Business Machines Corporation | Insulative cap for laser fusing |

| US6559042B2 (en) * | 2001-06-28 | 2003-05-06 | International Business Machines Corporation | Process for forming fusible links |

| US7053495B2 (en) * | 2001-09-17 | 2006-05-30 | Matsushita Electric Industrial Co., Ltd. | Semiconductor integrated circuit device and method for fabricating the same |

| US20030071323A1 (en) * | 2001-10-15 | 2003-04-17 | Taiwan Semiconductor Manufacturing Co., Ltd. | Microelectronic fabrication with upper lying aluminum fuse layer in copper interconnect semiconductor technology and method for fabrication thereof |

| KR100429881B1 (ko) * | 2001-11-02 | 2004-05-03 | 삼성전자주식회사 | 셀 영역 위에 퓨즈 회로부가 있는 반도체 소자 및 그제조방법 |

| KR100451506B1 (ko) * | 2001-12-24 | 2004-10-06 | 주식회사 하이닉스반도체 | 오버레이 마크의 구조 및 형성 방법 |

| US6614091B1 (en) * | 2002-03-13 | 2003-09-02 | Motorola, Inc. | Semiconductor device having a wire bond pad and method therefor |

| TW531776B (en) * | 2002-03-21 | 2003-05-11 | Nanya Technology Corp | Metal pad structure suitable for connection pad and inspection pad |

| TWI272641B (en) * | 2002-07-16 | 2007-02-01 | Semiconductor Energy Lab | Method of manufacturing a semiconductor device |

| JP4357862B2 (ja) * | 2003-04-09 | 2009-11-04 | シャープ株式会社 | 半導体装置 |

| US6717270B1 (en) * | 2003-04-09 | 2004-04-06 | Motorola, Inc. | Integrated circuit die I/O cells |

| US6787443B1 (en) * | 2003-05-20 | 2004-09-07 | Intel Corporation | PCB design and method for providing vented blind vias |

| JP2005109145A (ja) | 2003-09-30 | 2005-04-21 | Toshiba Corp | 半導体装置 |

| US6975040B2 (en) * | 2003-10-28 | 2005-12-13 | Agere Systems Inc | Fabricating semiconductor chips |

| CN100382263C (zh) * | 2004-03-05 | 2008-04-16 | 沈育浓 | 具有多层布线结构的半导体晶片装置及其封装方法 |

| JP4689244B2 (ja) * | 2004-11-16 | 2011-05-25 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US8405216B2 (en) * | 2005-06-29 | 2013-03-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Interconnect structure for integrated circuits |

| JP4501806B2 (ja) * | 2005-07-27 | 2010-07-14 | 株式会社デンソー | 半導体装置の製造方法 |

| JP2007123509A (ja) * | 2005-10-27 | 2007-05-17 | Seiko Epson Corp | 半導体装置およびその製造方法 |

| KR100660893B1 (ko) * | 2005-11-22 | 2006-12-26 | 삼성전자주식회사 | 정렬 마크막을 구비하는 반도체 소자 및 그 제조 방법 |

| KR100735757B1 (ko) * | 2006-01-12 | 2007-07-06 | 삼성전자주식회사 | 퓨즈 영역 및 그의 제조방법 |

| US7692230B2 (en) * | 2006-12-06 | 2010-04-06 | Taiwan Semiconductor Manufacturing Co. Ltd. | MRAM cell structure |

| US8030733B1 (en) | 2007-05-22 | 2011-10-04 | National Semiconductor Corporation | Copper-compatible fuse target |

| US7964934B1 (en) * | 2007-05-22 | 2011-06-21 | National Semiconductor Corporation | Fuse target and method of forming the fuse target in a copper process flow |

| JP5064157B2 (ja) * | 2007-09-18 | 2012-10-31 | 新光電気工業株式会社 | 半導体装置の製造方法 |

| TWI394260B (zh) * | 2007-10-31 | 2013-04-21 | 群成科技股份有限公司 | 具有多晶粒之半導體元件封裝結構及其方法 |

| JP5268618B2 (ja) | 2008-12-18 | 2013-08-21 | 株式会社東芝 | 半導体装置 |

| US8278733B2 (en) * | 2009-08-25 | 2012-10-02 | Mediatek Inc. | Bonding pad structure and integrated circuit chip using such bonding pad structure |

| US8896136B2 (en) | 2010-06-30 | 2014-11-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | Alignment mark and method of formation |

| CN102157497B (zh) * | 2011-01-26 | 2016-03-09 | 上海华虹宏力半导体制造有限公司 | 多层堆栈的半导体器件的结构及形成方法 |

| JP5953974B2 (ja) * | 2011-09-15 | 2016-07-20 | 富士通セミコンダクター株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP2014216377A (ja) * | 2013-04-23 | 2014-11-17 | イビデン株式会社 | 電子部品とその製造方法及び多層プリント配線板の製造方法 |

| CN105845659B (zh) * | 2015-01-15 | 2019-04-26 | 中芯国际集成电路制造(上海)有限公司 | 引线焊垫结构及其形成方法 |

| CN113394193B (zh) * | 2020-03-13 | 2022-03-22 | 长鑫存储技术有限公司 | 半导体结构及其形成方法、激光熔丝的熔断方法 |

| US20220254718A1 (en) * | 2021-02-07 | 2022-08-11 | Changxin Memory Technologies, Inc. | Method for fusing and filling semiconductor structure, and semiconductor structure |

| JP7719608B2 (ja) * | 2021-02-08 | 2025-08-06 | ローム株式会社 | 半導体素子、当該半導体素子を備えた半導体装置、および、半導体素子の製造方法 |

| CN115831865A (zh) * | 2023-02-24 | 2023-03-21 | 广州粤芯半导体技术有限公司 | 一种减小晶圆标记区域电弧放电的结构及方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3512225B2 (ja) * | 1994-02-28 | 2004-03-29 | 株式会社日立製作所 | 多層配線基板の製造方法 |

| US5976971A (en) * | 1995-07-19 | 1999-11-02 | Ricoh Company, Ltd. | Fabrication process of a semiconductor device having an interconnection structure |

| JP2956571B2 (ja) * | 1996-03-07 | 1999-10-04 | 日本電気株式会社 | 半導体装置 |

| US5783490A (en) | 1997-04-21 | 1998-07-21 | Vanguard International Semiconductor Corporation | Photolithography alignment mark and manufacturing method |

| US5933744A (en) * | 1998-04-02 | 1999-08-03 | Taiwan Semiconductor Manufacturing Co., Ltd. | Alignment method for used in chemical mechanical polishing process |

-

1999

- 1999-06-28 JP JP18187899A patent/JP4037561B2/ja not_active Expired - Fee Related

-

2000

- 2000-06-28 US US09/604,791 patent/US6392300B1/en not_active Expired - Fee Related

- 2000-06-28 CN CN00122585.5A patent/CN1199265C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1281257A (zh) | 2001-01-24 |

| JP2001015403A (ja) | 2001-01-19 |

| US6392300B1 (en) | 2002-05-21 |

| CN1199265C (zh) | 2005-04-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4037561B2 (ja) | 半導体装置の製造方法 | |

| US7067928B2 (en) | Method of forming a bonding pad structure | |

| US6656826B2 (en) | Semiconductor device with fuse to be blown with energy beam and method of manufacturing the semiconductor device | |

| US5470793A (en) | Method of via formation for the multilevel interconnect integrated circuits | |

| CN1326221C (zh) | 半导体功率器件和形成方法 | |

| US6417087B1 (en) | Process for forming a dual damascene bond pad structure over active circuitry | |

| JP2005109145A (ja) | 半導体装置 | |

| US6951781B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP2002093911A (ja) | 半導体装置および製造方法 | |

| US6750129B2 (en) | Process for forming fusible links | |

| KR100691051B1 (ko) | 반도체 디바이스 및 본드 패드 형성 프로세스 | |

| JP2003060036A (ja) | 半導体装置およびその製造方法 | |

| US6717272B2 (en) | Reinforced bond-pad substructure and method for fabricating the same | |

| JP3530073B2 (ja) | 半導体装置及びその製造方法 | |

| US6838769B1 (en) | Dual damascene bond pad structure for lowering stress and allowing circuitry under pads | |

| US20080014742A1 (en) | Method of manufacturing a semiconductor device with through-chip vias | |

| US8278754B2 (en) | Metal line in semiconductor device and method for forming the same | |

| KR100579863B1 (ko) | 반도체 소자상 퓨주부 형성 방법 및 퓨주부를 포함하는반도체 소자 | |

| US6372555B1 (en) | Semiconductor integrated circuit device and method of manufacturing the same | |

| KR100866687B1 (ko) | 퓨즈를 갖는 반도체 소자의 제조 방법 | |

| KR100835428B1 (ko) | 퓨즈를 갖는 반도체 소자의 제조 방법 | |

| KR100458472B1 (ko) | 반도체 소자의 제조방법 | |

| KR100607748B1 (ko) | 반도체소자의 연결배선 제조 방법 | |

| KR20070018520A (ko) | 다층 패드, 다층 패드를 구비하는 반도체 장치 및 그 제조방법 | |

| JPH04334010A (ja) | 半導体集積回路装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040623 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040623 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060509 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060710 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071030 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071101 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101109 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |