JP4037561B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4037561B2 JP4037561B2 JP18187899A JP18187899A JP4037561B2 JP 4037561 B2 JP4037561 B2 JP 4037561B2 JP 18187899 A JP18187899 A JP 18187899A JP 18187899 A JP18187899 A JP 18187899A JP 4037561 B2 JP4037561 B2 JP 4037561B2

- Authority

- JP

- Japan

- Prior art keywords

- alignment mark

- barrier metal

- aluminum

- deposited

- interlayer insulating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/525—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections

- H01L23/5256—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections comprising fuses, i.e. connections having their state changed from conductive to non-conductive

- H01L23/5258—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections comprising fuses, i.e. connections having their state changed from conductive to non-conductive the change of state resulting from the use of an external beam, e.g. laser beam or ion beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/544—Marks applied to semiconductor devices or parts, e.g. registration marks, alignment structures, wafer maps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54426—Marks applied to semiconductor devices or parts for alignment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54453—Marks applied to semiconductor devices or parts for use prior to dicing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54453—Marks applied to semiconductor devices or parts for use prior to dicing

- H01L2223/5446—Located in scribe lines

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Description

【発明の属する技術分野】

本発明は、半導体装置の製造方法に係り、特に多層配線の最上層にアライメントマークが形成された半導体装置の製造方法に関する。

【0002】

【従来の技術】

半導体メモリの高密度化、大容量に伴って、チップ全体が無欠陥であることを要求することは不可能になっており、不良救済回路を内蔵した冗長構成(リダンダンシー)を採用することがメモリLSIおよびメモリ混載LSIの常識となっている。

【0003】

不良セルに替わってスペアセルを使用するためには、通常、テスターによって検出した不良セルの番地を記憶した後、ポリシリコンやアルミなどの配線層で形成されたヒューズをレーザーによって溶断(ブロー)し、不良セルに替わってスペアセルが選択されるようにする技術が一般的である。

【0004】

このヒューズをブローするために、位置合わせのためのアライメントマークが最上層のメタル配線層で形成されている。

【0005】

図9乃至図17は、アライメントマークを4層メタル配線構造を有するLSIに適用した場合の従来の製造工程を示している。

【0006】

まず、図9に示すように、シリコン基板11上に素子分離領域13を形成し、さらに拡散層14のような受動素子やMOSFET(ゲート電極を15で示す)のような能動素子を素子分離領域13以外の領域に形成する。なお、12の領域は、後にダイシングラインとなるチップ間領域であり、このダイシングライン領域12上に各種アライメントマークが配置される。

【0007】

次に、図10に示すように、BPSG膜のような第1層間絶縁膜16を堆積し、CMP(化学機械研磨)法を用いて第1層間絶縁膜16を平坦化する。その後、フォトリソグラフイー法を用いて第1コンタクトホールを開口し、第1タングステン17をCVD(化学気相成長)法を用いてコンタクトホールに埋め込む。さらに、第1アルミ18を全面に堆積し、フォトリソグラフイー法を用いて所定の形状にパターニングする。

【0008】

次に、図11に示すように、SiO2 膜のような第2層間絶縁膜19を堆積し、CMP法を用いて第2層間絶縁膜19を平坦化する。その後、フォトリソグラフイ一法を用いて第2コンタクトホールを開口し、第2タングステン20をCVD法を用いてコンタクトホールに埋め込む。さらに、第2アルミ21を全面に堆積し、フォトリソグラフイー法を用いて所定の形状にパターニングする。

【0009】

次に、図12に示すように、SiO2 膜のような第3層間絶縁膜22を堆積し、CMP法を用いて第3層間絶縁膜22を平坦化する。その後、フォトリソグラフイ一法を用いて第3コンタクトホールを開口し、第3タングステン23をCVD法を用いてコンタクトホールに埋め込む。さらに、第3アルミ24を全面に堆積し、フォトリソグラフイー法を用いて所定の形状にパターニングする。

【0010】

次に、図13に示すように、SiO2 膜のような第4層間絶縁膜25を堆積し、CMP法を用いて第4層間絶縁膜25を平坦化する。その後、フォトリソグラフイー法を用いて第4コンタクトホールを開口し、第4タングステン26をCVD法を用いてコンタクトホールに埋め込む。さらに、第4アルミ27を全面に堆積し、フォトリソグラフイー法を用いて所定の形状にパターニングする。

【0011】

これにより、第4アルミ27からなるメタルヒューズあるいはボンデイングパッドが形成され、また、第4アルミ27の一部27a がアライメントマークとなる。

【0012】

次に、図14に示すように、Si3 N4 膜のようなパッシベーション膜28を堆積し、フォトリソグラフイー法を用いて、ボンデイングパッド29上のパッシベーション膜28をエッチングし、開口する。この時、ダイシングライン領域12のアライメントマーク27a 上のパッシベーション膜28も、クラックを防止するためにエッチングされるので、アライメントマーク27a はオーバーエッチングされ露出する。

【0013】

上記したようにパッド開口工程に際してアライメントマーク27a が側面までオーバーエッチングされて露出すると、その後の工程で、図15に示すようにアライメントマーク27a が剥がれてしまうことがたびたび起きる。アライメントマーク27a が剥がれた結果、ヒューズブロー用のアライメントマーク27a を検出できなくなり、ヒューズブローができなくなると言う問題が発生する。

【0014】

また、図14に示した工程の後に、バンプ(電極形成)工程を行うと、別の問題点も発生する。これについて、図16乃至図17を参照して説明する。

【0015】

図14に示した工程の後、図16に示すように、Ti/Ni/Pdのようなバリアメタル30を堆積し、バンプを形成しようとするボンデイングパッド29の上方のバリアメタル30を開口するようにフォトレジスト31を形成する。そして、電解メッキ法などの手法により、ボンデイングパッド29上のバリアメタル30上にAuバンプ32を成長させる。

【0016】

次に、図17に示すように、フォトレジスト31を除去した後、パッシベーション膜28上に露出しているバリアメタル30を王水、エチレンジアミンテトラ酢酸などの溶液で除去し、Auバンプ32は残す。

【0017】

この際、これまでの工程で第4アルミのみで形成されたアライメントマーク27a は、電気的にフローティング状態になっており、チャージアップが可能な状態になっている。したがって、図17に示したように、パッシベーション膜28上に露出しているバリアメタル30を王水、エチレンジアミンテトラ酢酸などの溶液で除去する時に、前記アライメントマーク27a がチャージアップした状態になっていると、バリアメタル30下のアルミ(アライメントマーク27a )までエッチングされてしまう。

【0018】

これにより、これまでの工程で形成されたアライメントマーク27a が腐食状態のアライメントマーク33になってしまう。したがって、ヒューズブロー用のアライメントマーク33を検出できなくなり、ヒューズブローができなくなるという問題が発生する。

【0019】

【発明が解決しようとする課題】

上記したように従来の半導体装置は、パッド開口工程に際してアライメントマークが側面までオーバーエッチングされて露出し、その後の工程でアライメントマークが剥がれてしまうことがたびたび起き、ヒューズブロー時にヒューズブロー用のアライメントマークを検出できなくなり、ヒューズブローができなくなるという問題があった。

【0020】

また、バンプ工程に際して、バンプ電極部以外の領域に露出しているバリアメタルを溶液で除去する時にバリアメタル下のアライメントマークまでエッチングされ、ヒューズブロー時にヒューズブロー用のアライメントマークを検出できなくなり、ヒューズブローができなくなるという問題があった。

【0021】

本発明は上記の問題点を解決すべくなされたもので、パッド開口工程に際してアライメントマークが側面までオーバーエッチングされて露出しても、その後の工程でアライメントマークが剥がれてしまうことを防止し、ヒューズブロー時にヒューズブロー用のアライメントマークの検出を可能とする半導体装置を提供することを目的とする。

【0022】

また、本発明の他の目的は、バンプ電極部以外の領域に露出しているバリアメタルを溶液で除去する時にバリアメタル下のアライメントマークまでエッチングされてしまうことを防止し、ヒューズブロー時にヒューズブロー用のアライメントマークの検出を可能とする半導体装置を提供することにある。

【0023】

【課題を解決するための手段】

本発明の半導体装置の製造方法は、半導体基板上に絶縁層を形成し、前記絶縁層内に第1、第2のコンタクトホールを形成し、この第1、第2のコンタクトホールに第1、第2の導電性プラグを埋め込み形成し、前記第1、第2の導電性プラグを含む前記絶縁層上に配線層を堆積し、前記配線層をパターニングして、前記第1の導電性プラグ上にボンデイングパッドを形成すると共に前記第2の導電性プラグ上にアライメントマークを形成し、前記ボンデイングパッド上及びアライメントマーク上を含む全面にバリアメタルを堆積し、前記ボンデイングパッド上の前記バリアメタル上にハンプ電極を形成し、前記アライメントマーク上の前記バリアメタルを除去することを特徴とする。

【0025】

【発明の実施の形態】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

【0026】

<第1の実施の形態>

図1乃至図8は、本発明の第1の実施の形態に係るアライメントマークを4層メタル配線構造を有するLSIに適用した場合の製造工程を示している。

【0027】

まず、図1に示すように、シリコン基板11上に素子分離領域13を形成し、さらに拡散層14のような受動素子やMOSFET(ゲート電極を15で示す)ような能動素子を素子分離領域13以外の領域に形成する。なお、12の領域は、後にダイシングラインとなるチップ間領域であり、このダイシングライン領域12上に各種アライメントマークが配置される。

【0028】

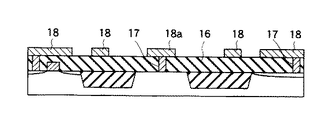

次に、図2に示すように、BPSG膜のような第1層間絶縁膜16を堆積し、CMP法を用いて第1層間絶縁膜16を平坦化する。その後、フォトリソグラフイー法を用いて、拡散層14上やMOSFETのソース領域あるいはドレイン領域上に対応して第1層間絶縁膜16に第1コンタクトホールを開口し、第1タングステン17をCVD法を用いてコンタクトホールに埋め込む。この際、ダイシングライン領域12の第1層間絶縁膜16にも第1コンタクトホールを開口し、第1タングステン17を埋め込む。

【0029】

さらに、第1アルミ18を全面に堆積し、フォトリソグラフイー法を用いて所定の形状にパターニングすることにより、第1アルミ18からなる配線を形成するとともに、ダイシングライン領域12の第1コンタクトホールに埋め込まれた第1タングステン17上にも接続パターン部18a を形成する。

【0030】

次に、図3に示すように、SiO2 膜のような第2層間絶縁膜19を堆積し、CMP法を用いて第2層間絶縁膜19を平坦化する。その後、フォトリソグラフイ一法を用いて、前記第1アルミ18からなる配線および接続パターン部18a 上に対応して第2層間絶縁膜19に第2コンタクトホールを開口し、第2タングステン20をCVD法を用いてコンタクトホールに埋め込む。

【0031】

さらに、第2アルミ21を全面に堆積し、フォトリソグラフイー法を用いて所定の形状にパターニングすることにより、第2アルミ21からなる配線を形成するとともに、ダイシングライン領域12の第2コンタクトホールに埋め込まれた第2タングステン20上にも接続パターン部21a を形成する。

【0032】

次に、図4に示すように、SiO2 膜のような第3層間絶縁膜22を堆積し、CMP法を用いて第3層間絶縁膜22を平坦化する。その後、フォトリソグラフイ一法を用いて、前記第2アルミ21からなる配線および接続パターン部21a 上に対応して第3層間絶縁膜22に第3コンタクトホールを開口し、第3タングステン23をCVD法を用いてコンタクトホールに埋め込む。

【0033】

さらに、第3アルミ24を全面に堆積し、フォトリソグラフイー法を用いて所定の形状にパターニングすることにより、第3アルミ24からなる配線を形成するとともに、ダイシングライン領域12の第3コンタクトホールに埋め込まれた第3タングステン23上にも接続パターン部24a を形成する。

【0034】

次に、図5に示すように、SiO2 膜のような第4層間絶縁膜25を堆積し、CMP法を用いて第4層間絶縁膜25を平坦化する。その後、フォトリソグラフイー法を用いて、前記第3アルミ24からなる配線および接続パターン部24a 上に対応して第4層間絶縁膜25に第4コンタクトホールを開口し、第4タングステン26をCVD法を用いてコンタクトホールに埋め込む。

【0035】

さらに、第4アルミ27を全面に堆積し、フォトリソグラフイー法を用いて所定の形状にパターニングすることにより、第4アルミ27からなるメタルヒューズあるいはボンデイングパッドを形成するとともに、ダイシングライン領域12の第4コンタクトホールに埋め込まれた第4タングステン26上にはアライメントマーク27a を形成する。

【0036】

この段階で、アライメントマーク27a は、下層のコンタクトホールに埋め込まれた導電性のプラグにコンタクトしており、しかも、このプラグおよび下層のアルミ配線(接続パターン)を通してシリコン基板51に電気的に接続された構造となっている。

【0037】

次に、図6に示すように、Si3 N4 膜のようなパッシベーション膜28を堆積し、フォトリソグラフイー法を用いて、ボンデイングパッド29上のパッシベーション膜28をエッチングし、開口する。この時、ダイシングライン領域12のアライメントマーク27a 上のパッシベーション膜28も、クラックを防止するためにエッチングされるので、アライメントマーク27a はオーバーエッチングされ露出する。

【0038】

上記したようにアライメントマーク27a が側面までオーバーエッチングされて露出したとしても、アライメントマーク27a は下層のコンタクトホールに埋め込まれた導電性プラグに連なった構造となっているので、その後の工程でアライメントマーク27a が剥がれてしまうような問題は起きない。

【0039】

即ち、上記第1の実施の形態のLSIによれば、最上層のメタル配線層で形成されているアライメントマーク27a は、下層の導電性プラグに連なった構造を有するので、アライメントマーク27a の形成後の工程でアライメントマーク27a が剥がれてしまうような問題は起きない。

【0040】

したがって、ヒューズブロー用のアライメントマーク27a を検出できなくなるおそれはなくなり、ヒューズブローができなくなるという問題は発生しない。

【0041】

<第2の実施の形態>

第2の実施の形態では、第1の実施の形態によりアライメントマーク27a を形成した後、バンプ電極形成工程を行う。

【0042】

図1乃至図8は、本発明の第2の実施の形態に係るアライメントマークを4層メタル配線構造を有するLSIに適用した場合の製造工程を示している。

【0043】

即ち、第1の実施の形態で説明した図1乃至図6に示したような工程を経た後、図7に示すように、Ti/Ni/Pdのようなバリアメタル30を堆積し、バンプを形成しようとするボンデイングパッド29の上方のバリアメタル30を開口するようにフォトレジスト31を形成する。そして、電解メッキ法などの手法により、ボンデイングパッド29上のバリアメタル30上にAuバンプ32を成長させる。

【0044】

次に、図8に示すように、フォトレジスト31を除去した後、パッシベーション膜28上に露出しているバリアメタル30を王水、エチレンジアミンテトラ酢酸などの溶液で除去し、Auバンプ32は残す。

【0045】

この際、図6までの工程でアライメントマーク27a は、下層のコンタクトホールに埋め込まれた導電性プラグおよび下層のアルミ配線(接続パターン)を通してシリコン基板11に電気的に接続された(接地された)構造となっている。

【0046】

したがって、前記アライメントマーク27a はチャージアップしないので、図8に示したように、パッシベーション膜28上に露出しているバリアメタル30を王水、エチレンジアミンテトラ酢酸などの溶液で除去する時に、バリアメタル30下のアルミからなるアライメントマークはエッチングされることがなく、アライメントマークが腐食することはない。したがって、ヒューズブロー用のアライメントマーク27a を検出できなくなってヒューズブローができなくなるという問題を回避することができる。

【0047】

即ち、上記第2の実施の形態のLSIによれば、最上層のメタル配線層で形成されているアライメントマークは、下層のコンタクトホールに埋め込まれた導電性プラグおよび下層のアルミ配線(接続パターン)を通してシリコン基板11に電気的に接続された(接地された)構造を有する。

【0048】

したがって、ボンデイングパッド形成以降の工程でアライメントマークが剥がれたり、バンプ形成工程でのチャージアップによりアライメントマークが腐食するといった問題を回避することができる。

【0049】

【発明の効果】

上述したように本発明の半導体装置の製造方法によれば、パッド開口工程に際してアライメントマークが側面までオーバーエッチングされて露出しても、その後の工程でアライメントマークが剥がれてしまうことを防止し、ヒューズブロー時にヒューズブロー用のアライメントマークの検出を可能とすることができる。

【0050】

また、本発明の半導体装置の製造方法によれば、バンプ電極部以外の領域に露出しているバリアメタルを溶液で除去する時にバリアメタル下のアライメントマークまでエッチングされてしまうことを防止し、ヒューズブロー時にヒューズブロー用のアライメントマークの検出を可能とすることができる。

【0051】

即ち、本発明によれば、アライメントマークが下層のコンタクトホールに埋め込まれたプラグと接続されているので、ボンデイングパッド開口時にアライメントマークが側面までオーバーエッチングされて露出されたとしても、その後の工程でアライメントマークが剥がれてしまうような問題は起きない。

【0052】

本発明によれば、アライメントマークは、導電性プラグおよび下層の配線を通して半導体基板に電気的に接続された(接地された)状態となっていてチャージアップしないので、アライメントマーク上のバリアメタルを溶液で除去する工程時にアライメントマークまでエッチングされることがない。

【0053】

本発明によれば、アライメントマークは、導電性プラグおよび下層の配線を通して半導体基板に電気的に接続された(接地された)状態となっていてチャージアップしないので、バンプ工程に際して、バンプ電極部以外の領域に露出しているバリアメタルを溶液で除去する時にバリアメタル下のアライメントマークまでエッチングされることがない。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態に係る半導体装置の製造工程の一部を示す断面図。

【図2】図1の工程に続く工程を示す断面図。

【図3】図2の工程に続く工程を示す断面図。

【図4】図3の工程に続く工程を示す断面図。

【図5】図4の工程に続く工程を示す断面図。

【図6】図5の工程に続く工程を示す断面図。

【図7】本発明の第2の実施の形態に係る半導体装置の製造工程の一部を示す断面図。

【図8】図7の工程に続く工程を示す断面図。

【図9】従来の半導体装置の製造工程の一部を示す断面図。

【図10】図9の工程に続く工程を示す断面図。

【図11】図10の工程に続く工程を示す断面図。

【図12】図11の工程に続く工程を示す断面図。

【図13】図12の工程に続く工程を示す断面図。

【図14】図13の工程に続く工程を示す断面図。

【図15】図14の工程に続く工程を示す断面図。

【図16】図15の工程に続く工程を示す断面図。

【図17】図16の工程に続く工程を示す断面図。

【符号の説明】

11…シリコン基板、

12…ダイシングライン領域、

13…素子分離領域、

14…拡散層、

15…MOSFETのゲート電極、

16…第1層間絶縁膜、

17…第1タングステン、

18…第1アルミ、

19…第2層間絶縁膜、

20…第2タングステン、

21…第2アルミ、

22…第3層間絶縁膜、

23…第3タングステン、

24…第3アルミ、

25…第4層間絶縁膜、

26…第4タングステン、

27…第4アルミ、

27a …第4アルミ(アライメントマーク)、

28…パッシベーション膜、

29…ボンデイングパッド、

30…バリアメタル、

32…Auバンプ。

Claims (3)

- 半導体基板上に絶縁層を形成し、

前記絶縁層内に第1、第2のコンタクトホールを形成し、この第1、第2のコンタクトホールに第1、第2の導電性プラグを埋め込み形成し、

前記第1、第2の導電性プラグを含む前記絶縁層上に配線層を堆積し、

前記配線層をパターニングして、前記第1の導電性プラグ上にボンデイングパッドを形成すると共に前記第2の導電性プラグ上にアライメントマークを形成し、

前記ボンデイングパッド上及びアライメントマーク上を含む全面にバリアメタルを堆積し、

前記ボンデイングパッド上の前記バリアメタル上にハンプ電極を形成し、

前記アライメントマーク上の前記バリアメタルを除去する

ことを特徴とする半導体装置の製造方法。 - 前記第2の導電性プラグを形成する際に、前記半導体基板に電気的に接続されるように前記第2の導電性プラグを形成することを特徴とする請求項1記載の半導体装置の製造方法。

- 王水、エチレンジアミンテトラ酢酸の溶液を用いて前記アライメントマーク上の前記バリアメタルを除去することを特徴とする請求項1記載の半導体装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18187899A JP4037561B2 (ja) | 1999-06-28 | 1999-06-28 | 半導体装置の製造方法 |

| US09/604,791 US6392300B1 (en) | 1999-06-28 | 2000-06-28 | Semiconductor device having an alignment mark formed on the uppermost layer of a multilayer wire |

| CN00122585.5A CN1199265C (zh) | 1999-06-28 | 2000-06-28 | 半导体器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18187899A JP4037561B2 (ja) | 1999-06-28 | 1999-06-28 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001015403A JP2001015403A (ja) | 2001-01-19 |

| JP2001015403A5 JP2001015403A5 (ja) | 2005-04-28 |

| JP4037561B2 true JP4037561B2 (ja) | 2008-01-23 |

Family

ID=16108456

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP18187899A Expired - Fee Related JP4037561B2 (ja) | 1999-06-28 | 1999-06-28 | 半導体装置の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6392300B1 (ja) |

| JP (1) | JP4037561B2 (ja) |

| CN (1) | CN1199265C (ja) |

Families Citing this family (39)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7405149B1 (en) * | 1998-12-21 | 2008-07-29 | Megica Corporation | Post passivation method for semiconductor chip or wafer |

| US7381642B2 (en) | 2004-09-23 | 2008-06-03 | Megica Corporation | Top layers of metal for integrated circuits |

| US6965165B2 (en) | 1998-12-21 | 2005-11-15 | Mou-Shiung Lin | Top layers of metal for high performance IC's |

| US6784516B1 (en) * | 2000-10-06 | 2004-08-31 | International Business Machines Corporation | Insulative cap for laser fusing |

| US6559042B2 (en) * | 2001-06-28 | 2003-05-06 | International Business Machines Corporation | Process for forming fusible links |

| US7053495B2 (en) * | 2001-09-17 | 2006-05-30 | Matsushita Electric Industrial Co., Ltd. | Semiconductor integrated circuit device and method for fabricating the same |

| US20030071323A1 (en) * | 2001-10-15 | 2003-04-17 | Taiwan Semiconductor Manufacturing Co., Ltd. | Microelectronic fabrication with upper lying aluminum fuse layer in copper interconnect semiconductor technology and method for fabrication thereof |

| KR100429881B1 (ko) * | 2001-11-02 | 2004-05-03 | 삼성전자주식회사 | 셀 영역 위에 퓨즈 회로부가 있는 반도체 소자 및 그제조방법 |

| KR100451506B1 (ko) * | 2001-12-24 | 2004-10-06 | 주식회사 하이닉스반도체 | 오버레이 마크의 구조 및 형성 방법 |

| US6614091B1 (en) * | 2002-03-13 | 2003-09-02 | Motorola, Inc. | Semiconductor device having a wire bond pad and method therefor |

| TW531776B (en) * | 2002-03-21 | 2003-05-11 | Nanya Technology Corp | Metal pad structure suitable for connection pad and inspection pad |

| TWI272641B (en) * | 2002-07-16 | 2007-02-01 | Semiconductor Energy Lab | Method of manufacturing a semiconductor device |

| US6717270B1 (en) * | 2003-04-09 | 2004-04-06 | Motorola, Inc. | Integrated circuit die I/O cells |

| JP4357862B2 (ja) * | 2003-04-09 | 2009-11-04 | シャープ株式会社 | 半導体装置 |

| US6787443B1 (en) * | 2003-05-20 | 2004-09-07 | Intel Corporation | PCB design and method for providing vented blind vias |

| JP2005109145A (ja) | 2003-09-30 | 2005-04-21 | Toshiba Corp | 半導体装置 |

| US6975040B2 (en) * | 2003-10-28 | 2005-12-13 | Agere Systems Inc | Fabricating semiconductor chips |

| CN100382263C (zh) * | 2004-03-05 | 2008-04-16 | 沈育浓 | 具有多层布线结构的半导体晶片装置及其封装方法 |

| JP4689244B2 (ja) * | 2004-11-16 | 2011-05-25 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US8405216B2 (en) * | 2005-06-29 | 2013-03-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Interconnect structure for integrated circuits |

| JP4501806B2 (ja) * | 2005-07-27 | 2010-07-14 | 株式会社デンソー | 半導体装置の製造方法 |

| JP2007123509A (ja) * | 2005-10-27 | 2007-05-17 | Seiko Epson Corp | 半導体装置およびその製造方法 |

| KR100660893B1 (ko) * | 2005-11-22 | 2006-12-26 | 삼성전자주식회사 | 정렬 마크막을 구비하는 반도체 소자 및 그 제조 방법 |

| KR100735757B1 (ko) * | 2006-01-12 | 2007-07-06 | 삼성전자주식회사 | 퓨즈 영역 및 그의 제조방법 |

| US7692230B2 (en) * | 2006-12-06 | 2010-04-06 | Taiwan Semiconductor Manufacturing Co. Ltd. | MRAM cell structure |

| US8030733B1 (en) | 2007-05-22 | 2011-10-04 | National Semiconductor Corporation | Copper-compatible fuse target |

| US7964934B1 (en) * | 2007-05-22 | 2011-06-21 | National Semiconductor Corporation | Fuse target and method of forming the fuse target in a copper process flow |

| JP5064157B2 (ja) * | 2007-09-18 | 2012-10-31 | 新光電気工業株式会社 | 半導体装置の製造方法 |

| TWI394260B (zh) * | 2007-10-31 | 2013-04-21 | Adl Engineering Inc | 具有多晶粒之半導體元件封裝結構及其方法 |

| JP5268618B2 (ja) | 2008-12-18 | 2013-08-21 | 株式会社東芝 | 半導体装置 |

| US8278733B2 (en) * | 2009-08-25 | 2012-10-02 | Mediatek Inc. | Bonding pad structure and integrated circuit chip using such bonding pad structure |

| US8896136B2 (en) | 2010-06-30 | 2014-11-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | Alignment mark and method of formation |

| CN102157497B (zh) * | 2011-01-26 | 2016-03-09 | 上海华虹宏力半导体制造有限公司 | 多层堆栈的半导体器件的结构及形成方法 |

| JP5953974B2 (ja) * | 2011-09-15 | 2016-07-20 | 富士通セミコンダクター株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP2014216377A (ja) * | 2013-04-23 | 2014-11-17 | イビデン株式会社 | 電子部品とその製造方法及び多層プリント配線板の製造方法 |

| CN105845659B (zh) * | 2015-01-15 | 2019-04-26 | 中芯国际集成电路制造(上海)有限公司 | 引线焊垫结构及其形成方法 |

| CN113394193B (zh) * | 2020-03-13 | 2022-03-22 | 长鑫存储技术有限公司 | 半导体结构及其形成方法、激光熔丝的熔断方法 |

| JP2022121116A (ja) * | 2021-02-08 | 2022-08-19 | ローム株式会社 | 半導体素子、当該半導体素子を備えた半導体装置、および、半導体素子の製造方法 |

| CN115831865A (zh) * | 2023-02-24 | 2023-03-21 | 广州粤芯半导体技术有限公司 | 一种减小晶圆标记区域电弧放电的结构及方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3512225B2 (ja) * | 1994-02-28 | 2004-03-29 | 株式会社日立製作所 | 多層配線基板の製造方法 |

| US5976971A (en) * | 1995-07-19 | 1999-11-02 | Ricoh Company, Ltd. | Fabrication process of a semiconductor device having an interconnection structure |

| JP2956571B2 (ja) * | 1996-03-07 | 1999-10-04 | 日本電気株式会社 | 半導体装置 |

| US5783490A (en) | 1997-04-21 | 1998-07-21 | Vanguard International Semiconductor Corporation | Photolithography alignment mark and manufacturing method |

| US5933744A (en) * | 1998-04-02 | 1999-08-03 | Taiwan Semiconductor Manufacturing Co., Ltd. | Alignment method for used in chemical mechanical polishing process |

-

1999

- 1999-06-28 JP JP18187899A patent/JP4037561B2/ja not_active Expired - Fee Related

-

2000

- 2000-06-28 US US09/604,791 patent/US6392300B1/en not_active Expired - Fee Related

- 2000-06-28 CN CN00122585.5A patent/CN1199265C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001015403A (ja) | 2001-01-19 |

| US6392300B1 (en) | 2002-05-21 |

| CN1281257A (zh) | 2001-01-24 |

| CN1199265C (zh) | 2005-04-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4037561B2 (ja) | 半導体装置の製造方法 | |

| US7067928B2 (en) | Method of forming a bonding pad structure | |

| US6656826B2 (en) | Semiconductor device with fuse to be blown with energy beam and method of manufacturing the semiconductor device | |

| US5470793A (en) | Method of via formation for the multilevel interconnect integrated circuits | |

| US5707894A (en) | Bonding pad structure and method thereof | |

| US6417087B1 (en) | Process for forming a dual damascene bond pad structure over active circuitry | |

| US6951781B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP2005109145A (ja) | 半導体装置 | |

| US6750129B2 (en) | Process for forming fusible links | |

| KR100691051B1 (ko) | 반도체 디바이스 및 본드 패드 형성 프로세스 | |

| JP2003060036A (ja) | 半導体装置およびその製造方法 | |

| US6717272B2 (en) | Reinforced bond-pad substructure and method for fabricating the same | |

| JP3530073B2 (ja) | 半導体装置及びその製造方法 | |

| US6838769B1 (en) | Dual damascene bond pad structure for lowering stress and allowing circuitry under pads | |

| US7781334B2 (en) | Method of manufacturing a semiconductor device with through-chip vias | |

| KR100866687B1 (ko) | 퓨즈를 갖는 반도체 소자의 제조 방법 | |

| KR100579863B1 (ko) | 반도체 소자상 퓨주부 형성 방법 및 퓨주부를 포함하는반도체 소자 | |

| US6372555B1 (en) | Semiconductor integrated circuit device and method of manufacturing the same | |

| US8278754B2 (en) | Metal line in semiconductor device and method for forming the same | |

| KR100458472B1 (ko) | 반도체 소자의 제조방법 | |

| KR100835428B1 (ko) | 퓨즈를 갖는 반도체 소자의 제조 방법 | |

| KR100607748B1 (ko) | 반도체소자의 연결배선 제조 방법 | |

| KR100861305B1 (ko) | 반도체 소자의 제조방법 | |

| KR20070018520A (ko) | 다층 패드, 다층 패드를 구비하는 반도체 장치 및 그 제조방법 | |

| JPH04334010A (ja) | 半導体集積回路装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040623 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040623 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060509 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060710 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071030 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071101 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101109 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |