JP4010425B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP4010425B2 JP4010425B2 JP06678997A JP6678997A JP4010425B2 JP 4010425 B2 JP4010425 B2 JP 4010425B2 JP 06678997 A JP06678997 A JP 06678997A JP 6678997 A JP6678997 A JP 6678997A JP 4010425 B2 JP4010425 B2 JP 4010425B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- insulating film

- spacer

- insulating

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Description

【発明の属する技術分野】

本発明は、半導体装置及びその製造方法に関し、特に半導体基板上に配置された配線及びこれに交差する局所配線を有する半導体装置及びその製造方法に関する。

【0002】

【従来の技術】

図5A〜5Cを参照して、従来の局所配線形成方法について説明する。

【0003】

図5Aに示すように、半導体基板上の絶縁層100の上に、紙面に垂直な方向に延在する配線101及び102が形成されている。配線101及び102は、例えばポリシリコンにより形成される。配線101の上面上には、SiO2 からなる絶縁膜103が形成されている。ここで、配線101に関して配線102と反対側の領域に形成されている半導体基板表面の低抵抗領域(図示せず)と配線102とを、配線101と交差する局所配線で接続する場合を考える。

【0004】

配線101及び102、絶縁膜103を覆うように、基板表面の全領域上にSiO2 膜104を等方的に堆積する。

【0005】

図5Bに示すように、SiO2 膜104を異方的にエッチングし、配線101及び102の側面上にそれぞれスペーサ領域104a及び104bを残す。配線102の上面を完全に露出させるためにやや過度のエッチングを行うと、配線101の上面に形成された絶縁膜103の上層部もエッチングされ、その膜厚が減少する。

【0006】

図5Cに示すように、配線102の上面から配線101と交差して反対側まで延在する局所配線105を形成する。局所配線105は、スペーサ領域104aと絶縁膜103により、配線101と電気的に絶縁される。

【0007】

【発明が解決しようとする課題】

図5Bに示す異方性エッチングの工程において、配線102の上面を確実に露出させ、配線101の上に十分な厚さの絶縁膜103を安定して残すためには、エッチング条件を厳密に制御する必要がある。過度のエッチングが行われると、絶縁膜103の膜厚の減少量が大きくなり、局所配線105と配線101との間の十分な絶縁性を確保することが困難になる。

【0008】

本発明の目的は、基板上に形成された配線と、それに交差する局所配線との間の十分な絶縁性を安定して確保することができる半導体装置及びその製造方法を提供することである。

【0009】

本発明の一観点によると、絶縁性表面を有する半導体基板の該絶縁性表面上に、導電性材料からなる第1の配線、該第1の配線の上に配置された第1の絶縁膜、及び該第1の絶縁膜の上に配置され、該第1の絶縁膜とはエッチング耐性の異なる第2の絶縁膜からなる積層構造を形成する工程と、前記積層構造の上面及び側面を含む基板表面上に等方的に、前記第2の絶縁膜とはエッチング耐性の異なる絶縁材料からなる第1のスペーサ絶縁層を堆積し、該第1のスペーサ絶縁層を異方的にエッチングして前記積層構造の側面上に、第1のスペーサ領域を残す工程と、前記第2の絶縁膜を除去する工程と、前記第1のスペーサ領域の表面を含む基板表面上に、第2のスペーサ絶縁層を堆積し、該第2のスペーサ絶縁層を異方的にエッチングし、前記第1のスペーサ領域の外側の側面上、及び前記第1の絶縁膜の上面よりも上方に位置する内側の側面上に第2のスペーサ領域を残す工程と、前記第1の配線と交差し、前記第1及び第2のスペーサ領域と前記第1の絶縁膜とにより前記第1の配線と電気的に絶縁された第2の配線を形成する工程とを有する半導体装置の製造方法が提供される。

【0010】

第1のスペーサ絶縁層の異方性エッチング時に、第1の絶縁膜が第2の絶縁膜で覆われている。第1のスペーサ絶縁層と第2の絶縁膜とは、相互にエッチング耐性を異にするため、第2の絶縁膜が露出した時点で第1のスペーサ絶縁層のエッチングが停止する。このため、第2の絶縁膜に覆われた第1の絶縁膜を安定して残すことができ、第1の配線と第2の配線との間の十分な電気的絶縁を確保することができる。

【0011】

第2の絶縁膜を除去したのち、第1のスペーサ領域の上端が第1の絶縁膜の上面よりも上方に突出する。この突出部の内側の側面は基板表面に対してほぼ垂直であり、基板表面に傾斜度の大きな段差が形成される。第2のスペーサ領域を形成することにより、この段差の傾斜度が緩和される。このため、第2の配線形成時における段差部へのエッチング残りを抑制できる。

【0012】

本発明の他の観点によると、絶縁性表面を有する半導体基板と、前記絶縁性表面上に形成された第1の配線と、前記第1の配線の上面上に形成された第1の絶縁膜と、前記第1の配線と第1の絶縁膜との積層構造の両側の側面上に形成された絶縁材料からなる第1のスペーサ領域であって、その最上端が前記第1の絶縁膜の上面よりも高い前記第1のスペーサ領域と、前記第1のスペーサ領域の外側の側面上、及び前記第1の絶縁膜の上面よりも上方に位置する内側の側面上に形成された絶縁材料からなる第2のスペーサ領域と、前記第2のスペーサ領域の表面の一部の領域上、及び前記第1の絶縁膜の上面の一部の領域上に配置され、前記第1の配線と交差するように形成された第2の配線とを有する半導体装置が提供される。

【0013】

第1の配線と第2の配線とが、第1の絶縁膜、第1及び第2のスペーサ領域とにより電気的に絶縁される。第2のスペーサ領域が、第1のスペーサ領域の側面からなる段差の傾斜度を緩和するため、第2の配線形のパターニングを容易に行うことができる。

【0014】

本発明の他の観点によると、絶縁性表面を有する半導体基板の該絶縁性表面上に、導電性材料からなる第1の配線、該第1の配線の上に配置された第1の絶縁膜、及び該第1の絶縁膜の上に配置され、該第1の絶縁膜とはエッチング耐性の異なる第2の絶縁膜からなる積層構造を形成する工程と、前記積層構造の上面及び側面を含む基板表面上に等方的に、前記第2の絶縁膜とはエッチング耐性の異なる絶縁材料からなる第1のスペーサ絶縁層を堆積し、該第1のスペーサ絶縁層を異方的にエッチングして前記積層構造の側面上に、第1のスペーサ領域を残す工程と、前記第2の絶縁膜を除去する工程と、前記第1の配線、第1の絶縁膜、第1のスペーサ領域を覆うように、基板上に層間絶縁膜を形成する工程と、前記層間絶縁膜に、前記第1の配線と交差する溝を形成し、該溝の底面に、前記絶縁性表面の一部、前記第1の絶縁膜の表面の一部及び第1のスペーサ領域の表面の一部を露出させる工程と、前記溝内を埋め尽くすように、前記層間絶縁膜の上に導電性材料からなる配線層を形成する工程と、前記配線層をエッチバックして、前記溝の中に配線層の一部を残す工程とを有する半導体装置の製造方法が提供される。

【0015】

第1のスペーサ絶縁層の異方性エッチング時に、第1の絶縁膜が第2の絶縁膜で覆われている。第1のスペーサ絶縁層と第2の絶縁膜とは、相互にエッチング耐性を異にするため、第2の絶縁膜が露出した時点で第1のスペーサ絶縁層のエッチングが停止する。このため、第2の絶縁膜に覆われた第1の絶縁膜を安定して残すことができ、第1の配線と第2の配線との間の十分な電気的絶縁を確保することができる。

【0016】

本発明の他の観点によると、絶縁性表面を有する半導体基板と、前記絶縁性表面上に形成された第1の配線と、前記第1の配線の上面上に形成された第1の絶縁膜と、前記第1の配線と第1の絶縁膜との積層構造の両側の側面上に形成された絶縁材料からなるスペーサ領域であって、その最上端が前記第1の絶縁膜の上面よりも高い前記スペーサ領域と、前記第1の絶縁膜及び前記スペーサ領域を覆うように基板上に形成され、前記第1の配線と交差する溝を有する層間絶縁膜であって、前記溝の底面の一部に前記第1の絶縁膜の表面の一部と前記スペーサ領域の表面の一部が露出する前記層間絶縁膜と、前記層間絶縁膜の溝内に埋め込まれた第2の配線とを有する半導体装置が提供される。

【0017】

第1の配線と第2の配線とが、第1の絶縁膜とスペーサ領域とにより電気的に絶縁される。

【0018】

【発明の実施の形態】

本発明の実施例を、スタティックRAMのメモリセルを例にとって説明する。

【0019】

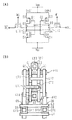

図1Aは、スタティックRAMの1ビット分のメモリセルの等価回路を示す。2つの電源線VDDとVSSとの間に、2つのインバータ回路INV1とINV2が接続されている。第1のインバータ回路INV1は、pMOSトランジスタQ1とnMOSトランジスタQ2との直列回路により構成され、第2のインバータ回路INV2は、pMOSトランジスタQ3とnMOSトランジスタQ4との直列回路により構成されている。

【0020】

第1のインバータ回路INV1のドレインD1、D2は、第2のインバータ回路INV2のゲート電極G2に局所配線LI1によって接続されている。第2のインバータ回路INV2のドレインD3、D4を接続する出力線が、局所配線LI2によって第1のインバータ回路INV1のゲート電極G1に帰還されている。

【0021】

さらに、第1のインバータ回路の出力線は、転送トランジスタQ5を介してビット線−BL(BLバー)に接続され、第2のインバータ回路INV2の出力線は、転送トランジスタQ6を介してビット線BLに接続されている。2つの転送トランジスタQ5、Q6のゲートは、共に同一のワード線WLに接続されている。

【0022】

図1Bは、図1Aに示すスタティックRAM回路の構成例を示す半導体装置の平面図である。

【0023】

図1Bにおいて、上側にはnウェルが形成され、下側にはpウェルが形成されている。nウェル中の活性領域AR1がフィールド酸化膜に囲まれて画定され、pウェル中の活性領域AR2が同様にフィールド酸化膜によって画定されている。これらの活性領域AR1、AR2以外のSi表面は、フィールド酸化膜によって覆われている。

【0024】

nウェルの活性領域AR1は、図中において倒立したT型形状を有し、pウェルの活性領域AR2は、倒立したU型形状を有する。T型の活性領域AR1の水平部分及びU型の活性領域AR2の水平部分を貫通するように、2つのゲート電極G1、G2が配置されている。なお、ゲート電極G1、G2は、共に活性領域AR1及びAR2内に位置するゲート電極部と、これらを相互に接続する配線部とから構成されるが、ゲート電極部と配線部とをまとめてゲート電極を呼ぶ。なお、本明細書において、この配線部を単に「配線」と呼ぶ場合もある。さらに図中下方にU型活性領域AR2の2つの垂直部分を貫通するようにゲート電極G3が形成されている。ゲート電極G3はワードラインWLを兼ねる。

【0025】

さらに、ゲート電極G3の図中下方にゲート電極G4がゲート電極G3と平行に配置されている。ゲート電極G4は、図には示さない他のメモリセルのトランジスタを制御する。

【0026】

これらゲート電極G1、G2、G3及びG4をマスクとしてイオン注入することにより、ゲート電極G1、G2に覆われていない活性領域AR1の表面層にはp型不純物がドープされてp型領域とされ、活性領域AR2のゲート電極G1、G2、G3及びG4に覆われていない表面層にはn型不純物がドープされてn型領域とされている。このようにして、活性領域AR1内に2つのMOSトランジスタQ1、Q3が形成され、活性領域AR2内の水平部分に2つのMOSトランジスタQ2、Q4、垂直部分に2つのMOSトランジスタQ5、Q6が形成されている。

【0027】

本構成においては、MOSトランジスタQ1、Q3のソース領域S1は共通領域とされている。また、2つのMOSトランジスタQ2、Q4のソース領域S2も共通領域とされている。さらに、2つのMOSトランジスタQ5、Q6の各々のドレイン領域D2、D4は、それぞれ2つのMOSトランジスタQ2、Q4のドレイン領域と共通領域で形成されている。

【0028】

ゲート電極G1、G2、G3及びG4の表面が絶縁膜で覆われ、コンタクト領域CT1、CT2の領域でのみその絶縁膜が剥離されている。すなわち、ゲート電極はコンタクト領域CT1及びCT2の部分でのみ露出され、基板表面は活性領域AR1、AR2のうちゲート電極G1、G2、G3及びG4で覆われていない部分でのみ露出する。

【0029】

ゲート電極G1のうちコンタクト領域CT1よりもMOSトランジスタQ1側の部分はp型導電性を付与され、MOSトランジスタQ2側の部分はn型導電性を付与されている。同様に、ゲート電極G2のうちコンタクト領域CT2よりもMOSトランジスタQ3側の部分はp型導電性を付与され、MOSトランジスタQ4側の部分はn型導電性を付与されている。

【0030】

局所配線LI1が、ドレイン領域D1、D2及びゲート電極G2のコンタクト領域CT2を結ぶように形成され、局所配線LI2はドレイン領域D3、D4及びゲート電極G1のコンタクト領域CT1を結ぶように形成される。局所配線LI1及びLI2は、それぞれゲート電極G1及びG2と交差する。

【0031】

これらの局所配線LI1、LI2は、3つの端部において下地半導体表面と接触するが、その他の領域においては絶縁膜上に配置される。したがって、局所配線LI1、LI2を形成する際に、特に層間絶縁膜を設ける必要はない。

【0032】

局所配線LI1、LI2の上に層間絶縁膜が形成され、ソース領域S1、S2、S5、S6の表面を露出するように、それぞれコンタクトホールCT3、CT4、CT5、CT6が形成されている。各コンタクトホールCT3、CT4、CT5、CT6の底面には、それぞれ局所配線LI1、LI2と同時に形成されたCoシリサイド膜SF3、SF4、SF5、SF6が形成されている。コンタクトホールCT5及びCT6にそれぞれ接続され、図中の縦方向に延在するビット線−BL及びBLが、層間絶縁膜の上に配置される。また、コンタクトホールCT3及びCT4にそれぞれ接続され、図中の横方向に延在するVdd線及びVss線が、層間絶縁膜の上に配置される。

【0033】

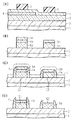

次に、図2A〜2D、図3A〜3Cを参照して、本発明の実施例による半導体装置の製造方法について説明する。図2A〜2D、図3A〜3Cは、図1Bの一点鎖線B1−B1における断面図に相当する。

【0034】

図2Aにおいて、LOCOS法によりシリコン基板1の表面を選択的に酸化して、フィールド酸化膜2を形成する。例えば、ウェット酸素雰囲気中で基板温度を950℃とし6時間の酸化を行うことにより、厚さ250nmのフィールド酸化膜2が形成される。フィールド酸化膜2によって、図1Bに示す活性領域AR1及びAR2が画定される。活性領域AR1及びAR2に対応する表面層に、それぞれn型不純物及びp型不純物をドープし、n型ウェル及びp型ウェルを形成する。活性領域AR1及びAR2の表面上にゲート絶縁膜を形成する。

【0035】

図2Aに示すように、フィールド酸化膜2の上に、アモルファスシリコンからなる厚さ180nmのゲート電極層3を堆積する。ゲート電極層3の堆積は、SiH4 をソースガスとし、成長温度を650℃とした化学気相堆積(CVD)により行う。

【0036】

ゲート電極層3の上にSiO2 からなる厚さ82nmの絶縁層を堆積する。この絶縁層のうち、図1Bに示すコンタクト領域CT1及びCT2に対応する部分を除去し、その他の領域に絶縁膜4を残す。この絶縁層のエッチングは、流量60sccmのCHF3 、流量60sccmのCF4 及び流量800sccmのArガスを用い、RF印加電力を750W、雰囲気圧力を1700mTorrとした反応性イオンエッチング(RIE)により行う。

【0037】

絶縁膜4及びゲート電極層3の露出した表面を覆うように、SiNからなるエッチング保護層5を堆積する。エッチング保護層5の堆積は、原料ガスとして流量18sccmのSiH4 と流量60sccmのNH3 を用い、印加電力を50W、圧力を1.5Torrとしたプラズマ励起型CVDにより行う。

【0038】

エッチング保護層5の上に、図1Bに示すゲート電極G1及びG2に対応するレジストパターン6を形成する。レジストパターン6を形成するための露光時に、エッチング保護層5が反射防止膜として作用する。レジストパターン6をエッチングマスクとして、エッチング保護層5と絶縁膜4をエッチングする。このエッチングは、流量90sccmのCF4 と流量900sccmのArガスを用い、RF印加電力を1000W、雰囲気圧力を500mTorrとしたRIEにより行う。

【0039】

続いて、ゲート電極層3をエッチングする。このエッチングは、例えば流量100sccmのHBrを用い、RF印加電力を250W、雰囲気圧力を0.1TorrとしたRIEにより行う。エッチング後にレジストパターン6を除去する。

【0040】

図2Bは、レジストパターン6を除去した後の基板断面図を示す。配線G1とG2が形成される。なお、配線G1及びG2は、それぞれ図1Bに示すゲート電極G1及びG2に相当する。配線G1の上には、SiO2 からなる絶縁膜4aとSiNからなるエッチング保護膜5aの2層が残る。配線G2の上には、SiNからなるエッチング保護膜5bが残る。

【0041】

図2Cに示すように、CVDにより、基板全面にSiO2 からなるスペーサ絶縁層7を堆積する。このスペーサ絶縁層7を異方性エッチングし、配線G1、絶縁膜4a及びエッチング保護膜5aからなる積層構造の側面上にスペーサ領域7aを残し、配線G2とエッチング保護膜5bからなる積層構造の側面上にスペーサ領域7bを残す。スペーサ絶縁層の異方性エッチングは、例えば流量40sccmのCHF3 、流量40sccmのCF4 、及び流量650sccmのArガスを用い、RF印加電力を300W、雰囲気圧力を1000mTorrとしたRIEにより行う。

【0042】

このエッチング条件では、SiNに対するSiO2 のエッチング選択比が大きくなり、3〜4程度になるため、過度のエッチングを行ってもエッチング保護膜5a及び5bのエッチング量は少ない。配線G1上の絶縁膜4aがエッチング保護膜5aにより保護されているため、絶縁膜4aの膜厚の減少を防止できる。なお、絶縁膜4aの膜厚減少を防止するためには、絶縁膜4aに対するエッチング保護膜5aのエッチング選択比が4以上になるように、スペーサ絶縁層7の異方性エッチングの条件を選択することが好ましい。

【0043】

スペーサ領域7a、7bの形成後、露出しているシリコン基板1の表面を熱酸化し、厚さ約5nmのSiO2 膜を形成する。このSiO2 膜は、後工程においてシリコン基板表面を保護する役目を果たす。

【0044】

図2Dに示すように、温度約140℃の熱リン酸を用いてエッチング保護膜5a及び5bを除去する。スペーサ領域7a及び7bの最上端がそれぞれ絶縁膜4a及び配線G2の上面よりも上方に突出し、各スペーサ領域7a及び7bの突出部の内側に、基板面に対してほぼ垂直に切り立った側壁が形成される。

【0045】

図3Aに示すように、基板全面にSiO2 膜を堆積し、このSiO2 膜を異方性エッチングすることにより、スペーサ領域7a及び7bの側壁上にそれぞれスペーサ領域8a及び8bを形成する。SiO2 膜の堆積及び異方性エッチングの条件は、図2Cのスペーサ絶縁層7の場合と同様である。

【0046】

スペーサ領域8a及び8bは、スペーサ領域7a及び7bの切り立った内側の側壁上にも形成される。このため、基板表面に現れる段差部の傾斜度が緩和される。ここで、流量300sccmのArを用い、RF印加電力を500W、雰囲気圧力を0.06TorrとしたArスパッタエッチングを行なってもよい。Arスパッタエッチングを行なうことにより、傾斜度をさらに緩和することができる。

【0047】

図3Bに示すように、基板の表面上に厚さ8nmのコバルト(Co)膜9を堆積する。Co膜9の堆積は、例えばスパッタリングガスとして流量100sccmのArガス、ターゲットとして金属Coを用い、圧力を0.1Pa程度、RF入力パワーを約3.7W/cm2 程度としたRFスパッタリングにより行う。

【0048】

N2 またはAr雰囲気中で、温度400〜450℃、時間30秒間の熱処理を行い、Co膜9とそれに接するシリコンとのシリサイド化反応を起こさせる。シリサイド化反応後、未反応のCo膜9を硫酸過水(硫酸と過酸化水素水との混合液)により除去する。

【0049】

シリサイド化反応により、配線G2の上面にCoシリサイド膜10が形成される。さらに、N2 またはAr雰囲気中で、温度600〜900℃、時間30秒間の熱処理を行う。Coシリサイド膜10が、Co2 SiまたはCoSiからCoSi2 に変化し、低抵抗化する。なお、シリサイド化反応中におけるCo膜9の変質を防止するために、Co膜9の上にTiN膜を形成しておいてもよい。

【0050】

図3Aに示したスペーサ領域8a、8bを形成する工程と、図3Bに示したCoシリサイド膜10を形成する工程の順番を入れ換えてもよい。本実施例の場合には、配線G2の上面のうちスペーサ領域8bで覆われていない領域にのみCoシリサイド膜10が形成されるが、工程順を入れ換えると、配線G2の上面の全領域にCoシリサイド膜10が形成される。

【0051】

このシリサイド化工程で、シリコン基板1の露出している領域でもシリサイド化反応が起こる。例えば、図1Bに示す各トランジスタのソース/ドレイン領域の表面にもCoシリサイド膜が形成される。

【0052】

図3Cに示すように、配線G2の上面から図の左方に延在する局所配線LI1を形成する。以下、局所配線LI1の形成方法を説明する。

【0053】

まず、基板の表面上に厚さ8nmのCo膜を堆積し、続いて、厚さ約30nmのアモルファスシリコン膜を堆積する。このアモルファスシリコン膜を、図1Bに示す局所配線LI1の形状にパターニングする。アモルファスシリコン膜のエッチングは、例えば、平行平板型RIE装置を用いて行う。SF6 ガスの流量を200sccm、圧力を0.2Torr、印加RF電力を300Wとすることにより、表面段差部にシリコン膜を残留させることなく良好なエッチングを行うことができた。

【0054】

次に、アモルファスシリコン膜で覆われていない領域のCo膜を希硫酸を用いて除去する。温度500℃、時間20分間の熱処理を行いCo膜とアモルファスシリコン膜とを反応させ、Coシリサイドからなる局所配線LI1を形成する。

【0055】

基板表面の段差部の傾斜度が、スペーサ領域8a及び8bにより緩和されているため、アモルファスシリコン膜及びCo膜のエッチング時に、段差部におけるエッチング残りの発生を抑制することができる。

【0056】

また、図2Cに示すスペーサ絶縁層7の異方性エッチング工程において、エッチング保護膜5aによって絶縁膜4aが保護されているため、十分な厚さの絶縁膜4aを安定して残すことができる。このため、図3Cにおいて、配線G1と局所配線LI1との間の絶縁を容易に確保することができる。

【0057】

次に、図4A〜4Cを参照して、本発明の他の実施例による半導体装置の製造方法について説明する。図2Dの工程までは、上述の実施例の場合と同様である。以下、図2D以降の工程について説明する。

【0058】

図4Aに示すように、基板全面にCo膜20を堆積し、熱処理を行うことによって、配線G2の上面にCoシリサイド膜21を形成する。シリサイド化反応の条件は、図3Bに示すCoシリサイド膜10の形成の場合と同様である。

【0059】

図4Bに示すように、SiO2 保護膜22、SiNエッチング停止膜23、SiO2 膜24及びSOG(スピンオングラス)膜25がこの順番に積層された層間絶縁膜26を堆積する。SiO2 保護膜22の厚さは20nm、SiNエッチング停止膜23の厚さは70nm、SiO2 膜24の厚さは150nmである。SOG膜25は、基板表面を平坦化する。

【0060】

図4Cに示すように、図1Bに示す局所配線LI1に対応する溝27を層間絶縁膜26に形成する。溝27の底面に、スペーサ領域7a及び絶縁膜4aの表面の一部が露出する。溝27の形成時において、SOG膜25及びSiO2 膜24のエッチングがエッチング停止膜23で停止する。その後、比較的薄いSiNエッチング停止膜23とSiO2 保護膜22を順番にエッチングする。SiO2 保護膜22は、エッチング停止膜23の除去時に基板表面を保護する。比較的厚いSOG膜25及びSiO2 膜24のエッチング時に、スペーサ領域7a及び絶縁膜4aが露出しないため、これらの過度のエッチングを防止できる。

【0061】

次に、溝27内を埋め尽くすように、基板全面にタングステン(W)膜28を堆積する。W膜28の厚さは、溝27内を埋め込んでほぼ平坦な表面が得られる程度とする。W膜28をエッチバックし、溝27内にのみWからなる局所配線LI1を残す。

【0062】

図4Cにおいても、図3Cの場合と同様に絶縁膜4aの厚さが十分確保されているため、局所配線LI1と配線G1との絶縁を容易に確保することができる。なお、スペーサ領域7a及び7bの突出部の内側にエッチング残りが生ずる場合もあるが、このエッチング残りは絶縁物であるため、短絡等の不良の原因にならない。

【0063】

上記2つの実施例では、スタティックRAMを作製する場合を例に説明したが、局所配線を有する他の半導体装置に適用することも可能である。また、上記実施例では、図2Cにおいて、絶縁膜4a及びスペーサ領域7a、7bをSiO2 で形成し、エッチング保護膜5a及び5bをSiNで形成した場合を説明したが、その他の材料を使用してもよい。図2Cの異方性エッチングの工程で、エッチング保護膜5aに対してスペーサ絶縁層7を優先的にエッチングするため、エッチング保護膜5aとスペーサ絶縁層7とを相互に異なるエッチング耐性を有する材料で形成する。また、図2Dの工程において、絶縁膜4aに対してエッチング保護膜5aを選択的に除去するため、絶縁膜4aとエッチング保護膜5aも、相互に異なるエッチング耐性を有する材料で形成する。

【0064】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【0065】

【発明の効果】

以上説明したように、本発明によれば、半導体基板上に形成された配線の側面及び上面を、十分な厚さの絶縁膜で覆うことができる。このため、この配線と、それに交差する局所配線との絶縁を容易に確保することができる。

【図面の簡単な説明】

【図1】図1Aは、スタティックRAMのメモリセルの等価回路図、図1Bは、半導体基板上に構成したメモリセルの平面図である。

【図2】本発明の実施例によるメモリセルの製造方法を説明するための半導体基板の断面図である。

【図3】本発明の実施例によるメモリセルの製造方法を説明するための半導体基板の断面図である。

【図4】本発明の他の実施例によるメモリセルの製造方法を説明するための半導体基板の断面図である。

【図5】従来例による局所配線を形成する方法を説明するための基板の断面図である。

【符号の説明】

1 シリコン基板

2 フィールド酸化膜

3 ゲート電極層

4 SiO2 絶縁層

4a SiO2 絶縁膜

5 SiNエッチング保護層

5a、5b SiNエッチング保護膜

6 レジストパターン

7 SiO2 スペーサ絶縁層

7a、7b、8a、8b SiO2 スペーサ領域

9、20 Co膜

10、21 Coシリサイド膜

22 SiO2 保護膜

23 SiNエッチング停止膜

24 SiO2 膜

25 SOG膜

26 層間絶縁膜

27 溝

28 W膜

Claims (14)

- 絶縁性表面を有する半導体基板の該絶縁性表面上に、導電性材料からなる第1の配線、該第1の配線の上に配置された第1の絶縁膜、及び該第1の絶縁膜の上に配置され、該第1の絶縁膜とはエッチング耐性の異なる第2の絶縁膜からなる積層構造を形成する工程と、

前記積層構造の上面及び側面を含む基板表面上に等方的に、前記第2の絶縁膜とはエッチング耐性の異なる絶縁材料からなる第1のスペーサ絶縁層を堆積し、該第1のスペーサ絶縁層を異方的にエッチングして前記積層構造の側面上に、第1のスペーサ領域を残す工程と、

前記第2の絶縁膜を除去する工程と、

前記第1のスペーサ領域の表面を含む基板表面上に、第2のスペーサ絶縁層を堆積し、該第2のスペーサ絶縁層を異方的にエッチングし、前記第1のスペーサ領域の外側の側面上、及び前記第1の絶縁膜の上面よりも上方に位置する内側の側面上に第2のスペーサ領域を残す工程と、

前記第1の配線と交差し、前記第1及び第2のスペーサ領域と前記第1の絶縁膜とにより前記第1の配線と電気的に絶縁された第2の配線を形成する工程と

を有する半導体装置の製造方法。 - 前記積層構造を形成する工程が、前記絶縁性表面上の前記積層構造の形成されていない領域に、前記第1の配線と同一材料からなる第3の配線、及び該第3の配線の上に配置され、前記第2の絶縁膜と同一材料からなる第3の絶縁膜を含む他の積層構造を形成する工程を含み、

前記第1のスペーサ領域を形成する工程が、前記他の積層構造の側面上に、前記第1のスペーサ絶縁層からなる第3のスペーサ領域を残す工程を含み、

前記第2の絶縁膜を除去する工程が、前記第3の絶縁膜を除去する工程を含み、

前記第2のスペーサ領域を残す工程が、前記第3のスペーサ領域の側面上に、前記第2のスペーサ絶縁層からなる第4のスペーサ領域を残す工程を含み、

前記第2の配線を形成する工程において、前記第3の配線に前記第2の配線が電気的に接続されるように該第2の配線を形成する請求項1に記載の半導体装置の製造方法。 - 前記半導体基板が前記絶縁性表面以外の領域にシリコン表面を有し、

前記第2の絶縁膜を除去する工程の後、前記第2の配線を形成する工程の前に、さらに前記シリコン表面をシリサイド化する工程を含み、

前記第2の配線を形成する工程において、前記第2の配線がシリサイド化された前記シリコン表面と前記第3の配線とを接続するように前記第2の配線を形成する請求項2に記載の半導体装置の製造方法。 - 前記第2の絶縁膜を除去する工程の前に、さらに、前記半導体装置のシリコン表面を熱酸化する工程を含む請求項3に記載の半導体装置の製造方法。

- 前記第1のスペーサ領域を残す工程において、前記第1のスペーサ絶縁層のエッチング速度が、前記第2の絶縁膜のエッチング速度の4倍以上となるエッチング条件で、前記第1のスペーサ絶縁層を異方的にエッチングする請求項1〜4のいずれかに記載の半導体装置の製造方法。

- 絶縁性表面を有する半導体基板と、

前記絶縁性表面上に形成された第1の配線と、

前記第1の配線の上面上に形成された第1の絶縁膜と、

前記第1の配線と第1の絶縁膜との積層構造の両側の側面上に形成された絶縁材料からなる第1のスペーサ領域であって、その最上端が前記第1の絶縁膜の上面よりも高い前記第1のスペーサ領域と、

前記第1のスペーサ領域の外側の側面上、及び前記第1の絶縁膜の上面よりも上方に位置する内側の側面上に形成された絶縁材料からなる第2のスペーサ領域と、

前記第2のスペーサ領域の表面の一部の領域上、及び前記第1の絶縁膜の上面の一部の領域上に配置され、前記第1の配線と交差するように形成された第2の配線と

を有する半導体装置。 - さらに、前記絶縁性表面の前記第1の配線の形成されていない領域上に形成された第3の配線と、

前記第3の配線の両側の側面上に形成され、前記第1のスペーサ領域と同一材料からなる第3のスペーサ領域であって、その最上端が前記第3の配線の上面よりも高い前記第3のスペーサ領域と、

前記第3のスペーサ領域の外側の側面上、及び前記第3の配線の上面よりも上方に位置する内側の側面上に形成され、前記第2のスペーサ領域と同一材料からなる第4のスペーサ領域とを有し、

前記第2の配線が、前記第3の配線の上面領域まで延在し、第3の配線と電気的に接続されている請求項6に記載の半導体装置。 - 前記半導体基板が、前記絶縁性表面とは異なる領域に金属シリサイド領域を有し、

前記第2の配線が前記金属シリサイド領域と前記第3の配線とを接続する請求項7に記載の半導体装置。 - 絶縁性表面を有する半導体基板の該絶縁性表面上に、導電性材料からなる第1の配線、該第1の配線の上に配置された第1の絶縁膜、及び該第1の絶縁膜の上に配置され、該第1の絶縁膜とはエッチング耐性の異なる第2の絶縁膜からなる積層構造を形成する工程と、

前記積層構造の上面及び側面を含む基板表面上に等方的に、前記第2の絶縁膜とはエッチング耐性の異なる絶縁材料からなる第1のスペーサ絶縁層を堆積し、該第1のスペーサ絶縁層を異方的にエッチングして前記積層構造の側面上に、第1のスペーサ領域を残す工程と、

前記第2の絶縁膜を除去する工程と、

前記第1の配線、第1の絶縁膜、第1のスペーサ領域を覆うように、基板上に層間絶縁膜を形成する工程と、

前記層間絶縁膜に、前記第1の配線と交差する溝を形成し、該溝の底面に、前記絶縁性表面の一部、前記第1の絶縁膜の表面の一部及び第1のスペーサ領域の表面の一部を露出させる工程と、

前記溝内を埋め尽くすように、前記層間絶縁膜の上に導電性材料からなる配線層を形成する工程と、

前記配線層をエッチバックして、前記溝の中に配線層の一部を残す工程とを有する半導体装置の製造方法。 - 前記層間絶縁膜が、前記第1の絶縁膜及び前記第1のスペーサ領域とエッチング耐性の異なるエッチング停止膜、及び該エッチング停止膜の上に形成され、エッチング停止膜とはエッチング耐性の異なる層間絶縁膜上層部を含む請求項9に記載の半導体装置の製造方法。

- 前記層間絶縁膜が、さらに、前記エッチング停止膜の下に配置され、エッチング停止膜とはエッチング耐性の異なるエッチング保護膜を含む請求項10に記載の半導体装置の製造方法。

- 絶縁性表面を有する半導体基板と、

前記絶縁性表面上に形成された第1の配線と、

前記第1の配線の上面上に形成された第1の絶縁膜と、

前記第1の配線と第1の絶縁膜との積層構造の両側の側面上に形成された絶縁材料からなるスペーサ領域であって、その最上端が前記第1の絶縁膜の上面よりも高い前記スペーサ領域と、

前記第1の絶縁膜及び前記スペーサ領域を覆うように基板上に形成され、前記第1の配線と交差する溝を有する層間絶縁膜であって、前記溝の底面の一部に前記第1の絶縁膜の表面の一部と前記スペーサ領域の表面の一部が露出する前記層間絶縁膜と、

前記層間絶縁膜の溝内に埋め込まれた第2の配線とを有する半導体装置。 - 前記層間絶縁膜が、前記第1の絶縁膜及び前記スペーサ領域とエッチング耐性の異なるエッチング停止膜、及び該エッチング停止膜の上に形成され、エッチング停止膜とはエッチング耐性の異なる層間絶縁膜上層部を含む請求項12に記載の半導体装置。

- 前記層間絶縁膜が、さらに、前記エッチング停止膜の下に配置され、エッチング停止膜とはエッチング耐性の異なるエッチング保護膜を含む請求項13に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP06678997A JP4010425B2 (ja) | 1997-03-19 | 1997-03-19 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP06678997A JP4010425B2 (ja) | 1997-03-19 | 1997-03-19 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH10261646A JPH10261646A (ja) | 1998-09-29 |

| JP4010425B2 true JP4010425B2 (ja) | 2007-11-21 |

Family

ID=13325986

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP06678997A Expired - Lifetime JP4010425B2 (ja) | 1997-03-19 | 1997-03-19 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4010425B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001332633A (ja) * | 2000-05-24 | 2001-11-30 | Sony Corp | 半導体メモリ |

| JP4530552B2 (ja) * | 2001-01-29 | 2010-08-25 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

-

1997

- 1997-03-19 JP JP06678997A patent/JP4010425B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JPH10261646A (ja) | 1998-09-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6388296B1 (en) | CMOS self-aligned strapped interconnection | |

| EP0562207B1 (en) | Method of forming thin film pseudo-planar PFET devices and structures resulting therefrom | |

| JPH10189483A (ja) | 半導体装置の製造方法及び半導体装置 | |

| JPH11251457A (ja) | 半導体デバイス,メモリ・セル,およびその形成方法 | |

| JP2000357749A (ja) | 2重仕事関数ドーピング及び保護絶縁キャップを提供する方法 | |

| KR20000053397A (ko) | 반도체 집적 회로 장치 및 그 제조 방법 | |

| KR970003953A (ko) | 고집적 dram 셀 및 그 제조방법 | |

| JP2689038B2 (ja) | 半導体装置およびその製造方法 | |

| KR100247933B1 (ko) | 버티드 콘택을 갖는 반도체 소자 및 그 제조방법 | |

| JPH10223770A (ja) | 半導体装置及びその製造方法 | |

| US7176096B1 (en) | Transistor gate and local interconnect | |

| JP3324648B2 (ja) | 半導体装置の製造方法 | |

| US6372641B1 (en) | Method of forming self-aligned via structure | |

| JP4010425B2 (ja) | 半導体装置及びその製造方法 | |

| US5290728A (en) | Method for producing a semiconductor device | |

| KR100589490B1 (ko) | 반도체 소자의 제조 방법 | |

| KR0144413B1 (ko) | 반도체소자 및 그 제조방법 | |

| JP2000269461A (ja) | 半導体記憶装置及びその製造方法 | |

| JPH1197529A (ja) | 半導体装置の製造方法 | |

| JP4331276B2 (ja) | 半導体装置の製造方法 | |

| KR100480577B1 (ko) | 버티드콘택을갖는반도체장치및그제조방법 | |

| JP2798001B2 (ja) | 半導体装置の製造方法 | |

| JPH11195787A (ja) | 半導体装置 | |

| JPH09260509A (ja) | デュアルゲートおよびその製造方法 | |

| JPH09120964A (ja) | 配線の形成方法及び半導体素子の形成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20031216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20031216 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050322 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070612 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070806 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070828 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070830 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100914 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100914 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100914 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110914 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110914 Year of fee payment: 4 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110914 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120914 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120914 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130914 Year of fee payment: 6 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |