JP3957178B2 - パターン化薄膜形成方法 - Google Patents

パターン化薄膜形成方法 Download PDFInfo

- Publication number

- JP3957178B2 JP3957178B2 JP2002222799A JP2002222799A JP3957178B2 JP 3957178 B2 JP3957178 B2 JP 3957178B2 JP 2002222799 A JP2002222799 A JP 2002222799A JP 2002222799 A JP2002222799 A JP 2002222799A JP 3957178 B2 JP3957178 B2 JP 3957178B2

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- layer

- frame

- patterned thin

- width

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000010409 thin film Substances 0.000 title claims description 125

- 238000000034 method Methods 0.000 title claims description 69

- 238000007747 plating Methods 0.000 claims description 29

- 239000000463 material Substances 0.000 claims description 11

- 239000010410 layer Substances 0.000 description 110

- 239000010408 film Substances 0.000 description 40

- 239000010949 copper Substances 0.000 description 17

- 239000000758 substrate Substances 0.000 description 17

- 238000010438 heat treatment Methods 0.000 description 12

- 238000004544 sputter deposition Methods 0.000 description 9

- 238000004528 spin coating Methods 0.000 description 8

- 238000000992 sputter etching Methods 0.000 description 8

- 238000009713 electroplating Methods 0.000 description 7

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 6

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 6

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 6

- 239000004020 conductor Substances 0.000 description 5

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000007864 aqueous solution Substances 0.000 description 3

- 229910000365 copper sulfate Inorganic materials 0.000 description 3

- ARUVKPQLZAKDPS-UHFFFAOYSA-L copper(II) sulfate Chemical compound [Cu+2].[O-][S+2]([O-])([O-])[O-] ARUVKPQLZAKDPS-UHFFFAOYSA-L 0.000 description 3

- 238000001312 dry etching Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 239000003960 organic solvent Substances 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 238000001020 plasma etching Methods 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 238000005192 partition Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 206010037660 Pyrexia Diseases 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000020169 heat generation Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- -1 polyethylene terephthalate Polymers 0.000 description 1

- 229920000139 polyethylene terephthalate Polymers 0.000 description 1

- 239000005020 polyethylene terephthalate Substances 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/02—Electroplating of selected surface areas

- C25D5/022—Electroplating of selected surface areas using masking means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F17/00—Fixed inductances of the signal type

- H01F17/0006—Printed inductances

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F41/00—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties

- H01F41/02—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for manufacturing cores, coils, or magnets

- H01F41/04—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for manufacturing cores, coils, or magnets for manufacturing coils

- H01F41/041—Printed circuit coils

- H01F41/042—Printed circuit coils by thin film techniques

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/108—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern by semi-additive methods; masks therefor

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/16—Printed circuits incorporating printed electric components, e.g. printed resistor, capacitor, inductor

- H05K1/165—Printed circuits incorporating printed electric components, e.g. printed resistor, capacitor, inductor incorporating printed inductors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09654—Shape and layout details of conductors covering at least two types of conductors provided for in H05K2201/09218 - H05K2201/095

- H05K2201/098—Special shape of the cross-section of conductors, e.g. very thick plated conductors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/05—Patterning and lithography; Masks; Details of resist

- H05K2203/0562—Details of resist

- H05K2203/0577—Double layer of resist having the same pattern

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/11—Treatments characterised by their effect, e.g. heating, cooling, roughening

- H05K2203/1184—Underetching, e.g. etching of substrate under conductors or etching of conductor under dielectrics; Means for allowing or controlling underetching

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12333—Helical or with helical component

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12431—Foil or filament smaller than 6 mils

- Y10T428/12438—Composite

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12493—Composite; i.e., plural, adjacent, spatially distinct metal components [e.g., layers, joint, etc.]

- Y10T428/12528—Semiconductor component

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12493—Composite; i.e., plural, adjacent, spatially distinct metal components [e.g., layers, joint, etc.]

- Y10T428/12639—Adjacent, identical composition, components

- Y10T428/12646—Group VIII or IB metal-base

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/12—All metal or with adjacent metals

- Y10T428/12493—Composite; i.e., plural, adjacent, spatially distinct metal components [e.g., layers, joint, etc.]

- Y10T428/12771—Transition metal-base component

- Y10T428/12861—Group VIII or IB metal-base component

- Y10T428/12903—Cu-base component

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Organic Chemistry (AREA)

- Materials Engineering (AREA)

- Metallurgy (AREA)

- Electrochemistry (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Manufacturing Cores, Coils, And Magnets (AREA)

- Magnetic Heads (AREA)

- Coils Or Transformers For Communication (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

【発明の属する技術分野】

本発明は、線状部分を有するパターン化薄膜およびその形成方法に関する。

【0002】

【従来の技術】

パターン化された薄膜(本出願においてパターン化薄膜と言う。)を形成する方法の一つとして、例えば特公昭56−36706号公報に示されるようなフレームめっき法がある。このフレームめっき法では、例えば基板の上に電極膜を形成し、その上にレジスト層を形成し、このレジスト層をフォトリソグラフィによりパターニングして、めっきのためのフレーム(外枠)を形成する。そして、このフレームを用い、先に形成した電極膜を電極およびシード層として用いて電気めっきを行って、導電材料よりなるパターン化薄膜を形成する。

【0003】

フレームめっき法によって形成されるパターン化薄膜は、例えばマイクロデバイスに使用される。このようなマイクロデバイスとしては、薄膜インダクタ、薄膜磁気ヘッド、半導体デバイス、薄膜を用いたセンサ、薄膜を用いたアクチュエータ等がある。

【0004】

【発明が解決しようとする課題】

パターン化薄膜には、コイルや配線のように、隣接する複数の線状部分を有するものがある。このようなパターン化薄膜では、その集積度を高めるために、線状部分の幅や、隣接する線状部分の間隔を小さくすることが要求される場合がある。

【0005】

しかしながら、パターン化薄膜における線状部分の幅を小さくし過ぎると、線状部分の抵抗値が増大し、その結果、線状部分が発熱する等の問題が生じる。

【0006】

一方、パターン化薄膜における隣接する線状部分の間隔を小さくすることには、以下のような問題がある。すなわち、フレームめっき法によってパターン化薄膜を形成する場合には、パターン化薄膜における隣接する線状部分の間隔は、フレームにおいて隣接する溝部分の間の仕切り部分の幅によって決まる。この仕切り部分の幅の最小限度は、フレームを形成するために用いられるレジストの解像度によって決まる。なお、レジストの解像度は、レジストの材料と露光方法によって決まる。このように、フレームめっき法によってパターン化薄膜を形成する場合には、パターン化薄膜における隣接する線状部分の間隔は、レジストの解像度によって決まる限度を超えて小さくすることが困難である。

【0007】

本発明はかかる問題点に鑑みてなされたもので、その第1の目的は、フレームめっき法を用いて、幅が小さく且つ抵抗値の小さい線状部分を有するパターン化薄膜を形成できるようにしたパターン化薄膜形成方法を提供することにある。

【0008】

また、本発明の第2の目的は、幅が小さく且つ抵抗値の小さい線状部分を有するパターン化薄膜を提供することにある。

【0009】

【課題を解決するための手段】

本発明のパターン化薄膜形成方法は、フレームめっき法によって、線状部分を有するパターン化薄膜を形成する方法であって、

下地の上に、底部近傍においてアンダーカットの入った形状のフレームを形成する工程と、

フレームを用いてめっきを行って、線状部分において下地に近い一部分の幅が残りの部分の幅よりも大きくなるようにパターン化薄膜を形成するめっき工程とを備えたものである。

【0010】

本発明のパターン化薄膜形成方法によれば、パターン化薄膜の線状部分の幅を小さくし、且つ線状部分の抵抗値を小さくすることができる。

【0011】

本発明のパターン化薄膜形成方法において、パターン化薄膜は、隣接する複数の線状部分を有するものであってもよい。

【0012】

本発明のパターン化薄膜は、下地の上に配置され、線状部分を有するものであって、線状部分において下地に近い一部分の幅が残りの部分の幅よりも大きいものである。

【0013】

本発明のパターン化薄膜によれば、線状部分の幅を小さくし、且つ線状部分の抵抗値を小さくすることができる。

【0014】

本発明のパターン化薄膜は、隣接する複数の線状部分を有するものであってもよい。

【0015】

【発明の実施の形態】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

[第1の実施の形態]

まず、図1を参照して、本発明の第1の実施の形態に係るパターン化薄膜形成方法が適用されるマイクロデバイスの一例としての薄膜インダクタについて説明する。図1は本実施の形態における薄膜インダクタの斜視図である。

【0016】

図1に示した薄膜インダクタは、基板101と、この基板101の上に形成された薄膜コイル102と、薄膜コイル102の各端部に接続された2つのリード103とを備えている。薄膜コイル102は、めっき法によって形成される。薄膜コイル102は、本実施の形態に係るパターン化薄膜に対応する。

【0017】

次に、図2ないし図9を参照して、本実施の形態に係るパターン化薄膜形成方法について詳しく説明する。本実施の形態では、底部近傍においてアンダーカットの入った形状のフレームを用いて、フレームめっき法によってパターン化薄膜を形成する。本実施の形態では、いわゆる2層レジストを用いて上記のフレームを形成する。2層レジストとは、下層である第1層と上層である第2層とを有する2層構造の膜であって、少なくとも第2層がレジストからなるものである。なお、2層レジストについては、例えば特開平9−96909号公報に記載されている。

【0018】

本実施の形態に係るパターン化薄膜形成方法では、まず、図2に示したように、基板1の上に、例えばスパッタ法によって電極膜2を形成する。基板1の材料は、シリコン(Si)等の半導体でもよいし、アルティック(Al2O3・TiC)等のセラミックでもよいし、ポリエチレンテレフタレート等の樹脂でもよい。電極膜2は、金属等の導電材料によって形成される。また、電極膜2の材料は、電極膜2の上に形成されるパターン化薄膜の材料と同じ組成のものを用いるのが好ましい。また、電極膜2は、一層で構成されていてもよいし、複数の層で構成されていてもよい。電極膜2の材料としては、例えば銅(Cu)が用いられる。

【0019】

次に、図3に示したように、パターン化薄膜の下地となる電極膜2の上に、スピンコート法等により、現像液によって溶解される材料を塗布して、フレームの形成のために用いられる第1層3Aを形成する。第1層3Aの材料としては、例えばポリメチルグルタルイミドが用いられる。次に、必要に応じて、第1層3Aに対して熱処理を施す。

【0020】

次に、図4に示したように、第1層3Aの上に、スピンコート法等により、レジストを塗布して、フレームの形成のために用いられる第2層4Aを形成する。次に、必要に応じて、第2層4Aに対して熱処理を施す。第1層3Aおよび第2層4Aによって2層レジストが構成される。

【0021】

次に、図5に示したように、マスク5を介して第2層4Aの露光を行い、第2層4Aに、マスク5のパターンに対応した潜像を形成する。次に、必要に応じて、第2層4Aに対して熱処理を施す。

【0022】

次に、図6に示したように、第2層4Aを現像液によって現像する。このとき、現像液によって、第2層4Aの一部が溶解されると共に第1層3Aの一部も溶解される。これにより、残った第1層3Aによってパターン化された第1フレーム層3Bが形成され、残った第2層4Aによってパターン化された第2フレーム層4Bが形成される。第1フレーム層3Bの幅は、第2フレーム層4Bの幅よりも小さい。なお、図6には、第2層4Aの形成に用いられるレジストがポジ型で、そのため、第2層4Aのうち、露光された部分が現像後に除去される例を示している。次に、第1フレーム層3Bおよび第2フレーム層4Bを水洗し、乾燥させる。

【0023】

このようにして、第1層3Aおよび第2層4Aがパターニングされて、第1フレーム層3Bおよび第2フレーム層4Bよりなり、底部近傍においてアンダーカットの入った形状のフレーム6が形成される。

【0024】

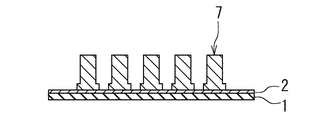

次に、必要に応じてめっき前処理を行った後、図7に示したように、フレーム6を用い、電極膜2に電流を流して電気めっきを行って、フレーム6の溝部内にパターン化薄膜7を形成する。パターン化薄膜7は、金属等の導電材料によって形成される。パターン化薄膜7の材料としては、例えば銅(Cu)が用いられる。

【0025】

次に、例えば、図7に示した積層体を有機溶剤に浸漬し、揺動することによって、図8に示したように、第1フレーム層3Bおよび第2フレーム層4Bを溶解させて除去する。

【0026】

最後に、図9に示したように、パターン化薄膜7をマスクとして、ウェットエッチングによって、あるいはイオンミリング、反応性イオンエッチング等のドライエッチングによって、電極膜2のうち、パターン化薄膜7の下に存在する部分以外の部分を除去する。

【0027】

このようにして形成されたパターン化薄膜7は、隣接する複数の線状部分71を有している。このパターン化薄膜7では、線状部分71において、下地である電極膜2に近い一部分(以下、第2の部分と言う。)71bの幅W2が、残りの部分(以下、第1の部分と言う。)71aの幅W1よりも大きくなっている。

【0028】

なお、図6ないし図9には、第2フレーム層4Bの壁部が、基板1の上面に対して垂直であり、その結果、線状部分71の第1の部分71aの側壁も基板1の上面に対して垂直になっている例を示している。しかし、本実施の形態は、図10および図11に示した各例も含む。図10および図11は、いずれも、フレーム6を用いて、めっきによってパターン化薄膜7を形成した直後の状態を示している。図10および図11に示した各例では、いずれも、第2フレーム層4Bの壁部および第1の部分71aの側壁が、基板1の上面に垂直な方向に対して傾いている。図10に示した例では、第2フレーム層4Bにおいて、フレーム6の溝部を挟んで対向する2つ壁部の間隔は上側ほど小さくなっている。その結果、図10に示した例では、第1の部分71aの幅は上側ほど小さくなっている。図10に示した例では、第2の部分71bの幅W2は、第1の部分71aと第2の部分71bとの境界位置における第1の部分71aの幅W1よりも大きくなっている。図11に示した例では、第2フレーム層4Bにおいて、フレーム6の溝部を挟んで対向する2つ壁部の間隔は上側ほど大きくなっている。その結果、図11に示した例では、第1の部分71aの幅は上側ほど大きくなっている。図11に示した例では、第2の部分71bの幅W2は、第1の部分71aと第2の部分71bとの境界位置における第1の部分71aの幅W1よりも大きくなっている。

【0029】

以上説明したように、本実施の形態に係るパターン化薄膜形成方法は、下地である電極膜2の上に、底部近傍においてアンダーカットの入った形状のフレーム6を形成する工程と、フレーム6を用いてめっきを行って、パターン化薄膜7を形成するめっき工程とを備えている。パターン化薄膜7は、隣接する複数の線状部分71を有し、線状部分71において電極膜2に近い第2の部分71bの幅W2が第1の部分71aの幅W1よりも大きくなっている。従って、本実施の形態によれば、パターン化薄膜7の線状部分71の全体が一定の幅W1を有する場合に比べて、線状部分71の抵抗値を小さくすることができる。

【0030】

また、本実施の形態では、隣接する第1の部分71aの間隔は、第2層4Aに用いられるレジストの解像度によって決まる限度を超えて小さくすることは困難である。しかしながら、隣接する第2の部分71bの間隔は、レジストの解像度によって決まる限度を超えて小さくすることができる。従って、本実施の形態によれば、線状部分71の全体が一定の幅W1を有する場合に比べて線状部分71のピッチを変えることなく、第2の部分71bの幅W2を第1の部分71aの幅W1よりも大きくして、線状部分71の抵抗値を小さくすることができる。

【0031】

以上のことから、本実施の形態によれば、フレームめっき法を用いて、線状部分71のピッチを大きくすることなく、幅が小さく且つ抵抗値の小さい線状部分71を有するパターン化薄膜7を形成することができる。これにより、本実施の形態によれば、線状部分71が発熱することを防止することができる。

【0032】

ところで、線状部分71の全体が一定の幅を有する場合において、隣接する線状部分71の間隔が小さくなると、隣接する線状部分71の間に位置する電極膜2をエッチングによって良好に除去できなくなる場合がある。これに対し、本実施の形態では、隣接する第1の部分71aの間隔は、隣接する第2の部分71bの間隔よりも大きい。従って、隣接する第2の部分71bの間隔が小さくても、隣接する線状部分71の間に位置する電極膜2をエッチングによって良好に除去することができる。

【0033】

次に、本実施の形態に係るパターン化薄膜形成方法の実施例について説明する。本実施例では、基板1として、直径3インチ(76.2mm)、厚さ0.4mmのシリコン基板を用いた。本実施例のパターン化薄膜形成方法では、まず、スパッタ装置を用いて、基板1の上に、以下の条件でCuをスパッタリングして、Cuよりなる厚さ100nmの電極膜2を形成した。スパッタ装置としては、日電アネルバ社製の直流スパッタ装置SPF−740H(製品名)を用いた。スパッタ装置におけるターゲットはCuとした。スパッタ装置の出力は1000Wとした。スパッタ装置におけるスパッタ室内には、Arガスを50sccmの流量で供給した。スパッタ室内におけるArガスの圧力は、2.0mTorr(約0.266Pa)とした。

【0034】

次に、電極膜2の上に、スピンコート法によりポリメチルグルタルイミドを塗布して、第1層3Aを形成した。ポリメチルグルタルイミドとしては、Shipley社製LOL−1000(製品名)を使用した。第1層3Aの厚みは100nmとした。次に、第1層3Aに対して、ホットプレートを用いて180℃の温度で、600秒間の熱処理を施し、その後、第1層3Aを室温まで冷却した。

【0035】

次に、第1層3Aの上に、スピンコート法によりレジストを塗布して、第2層4Aを形成した。レジストとしては、信越化学工業社製SIPR−9740(製品名)を使用した。第2層4Aの厚みは3μmとした。次に、第2層4Aに対して、ホットプレートを用いて100℃の温度で、180秒間の熱処理を施した。

【0036】

次に、露光装置を用いて、以下の条件で、マスク5を介して第2層4Aの露光を行い、第2層4Aに、マスク5のパターンに対応した潜像を形成した。露光装置としては、ニコン製NSR−i12TFH(製品名)を用いた。マスク5のパターンは、透光部が10ターンの渦巻き状をなし、遮光部の幅が1.0μmで、透光部の幅が1.5μmで、透光部のピッチが2.5μmとなるパターンとした。露光量(Dose)は、300mJ/cm2とした。

【0037】

次に、現像液として2.38%のテトラメチルアンモニウムヒドロキシドの水溶液を用いて、パドル法によって、第2層4Aに対して、50秒間の現像を2回行った。これにより、現像液によって、第2層4Aの一部が溶解されると共に第1層3Aの一部も溶解されて、第1フレーム層3Bおよび第2フレーム層4Bが形成された。次に、第1フレーム層3Bおよび第2フレーム層4Bを水洗し、乾燥させて、フレーム6を完成させた。

【0038】

次に、フレーム6を用いて電気めっきを行って、フレーム6の溝部内に、Cuよりなるパターン化薄膜7を形成した。めっき浴としては、Cuのめっきに用いられる一般的な硫酸銅浴を用いた。パターン化薄膜7の厚さは2.8μmとした。

【0039】

次に、パターン化薄膜7を含む積層体を、アセトン中に浸漬し、揺動することによって、フレーム6を溶解させて除去した。

【0040】

次に、イオンミリング装置を用いて、下記の条件で、電極膜2を選択的にエッチングして、電極膜2のうち、パターン化薄膜7の下に存在する部分以外の部分を除去した。イオンミリング装置としては、コモンウェルス社製8C(製品名)を用いた。イオンミリング装置における出力は、500W、500mAとした。エッチング室内のガスの圧力は3mTorr(約0.399Pa)とした。イオン照射角度は0°(イオン照射方向が基板に垂直)とした。

【0041】

このようにして、パターン化薄膜7からなり、ピッチが2.5μm、厚さが2.8μmで、10ターンの薄膜コイルが得られた。パターン化薄膜7の線状部分71において、第1の部分71aの幅W1は1.7μmで、第2の部分71bの幅W2は2.1μmであった。第2の部分71bのうち、第1の部分71aの側壁よりも外側に張り出した2つの部分の断面形状は、それぞれ、幅が0.2μmで、高さが0.1μmの矩形であった。

【0042】

[第2の実施の形態]

次に、図12ないし図20を参照して、本発明の第2の実施の形態に係るパターン化薄膜形成方法について説明する。本実施の形態では、マイクログルーブを利用して、底部近傍においてアンダーカットの入った形状のフレームを形成する。なお、マイクログルーブを利用して、底部近傍においてアンダーカットの入った形状のレジスト層を形成する方法については、特開平8−69111号公報に記載されている。

【0043】

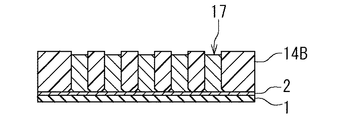

本実施の形態に係るパターン化薄膜形成方法では、図2に示したように、電極膜2を形成する工程までは、第1の実施の形態と同様である。本実施の形態では、次に、図12に示したように、電極膜2の上に、スピンコート法等によりレジストを塗布して、レジスト層14Aを形成する。レジストとしては、ポジ型で、特にマイクログルーブを発生しやすいレジストを用いる。このようなレジストとしては、具体的には、特開平8−69111号公報に示された種々のレジストを用いることができる。次に、必要に応じて、レジスト層14Aに対して熱処理を施す。

【0044】

次に、図13に示したように、マスク5を介してレジスト層14Aの露光を行い、レジスト層14Aに、マスク5のパターンに対応した潜像を形成する。次に、必要に応じて、レジスト層14Aに対して熱処理を施す。

【0045】

次に、図14に示したように、レジスト層14Aを現像液によって現像する。これにより、残ったレジスト層14Aによってフレーム14Bが形成される。次に、フレーム14Bを水洗し、乾燥させる。

【0046】

フレーム14Bには、底部近傍においてマイクログルーブが形成される。このようにして、底部近傍においてアンダーカットの入った形状のフレーム14Bが形成される。

【0047】

次に、必要に応じてめっき前処理を行った後、図15に示したように、フレーム14Bを用い、電極膜2に電流を流して電気めっきを行って、フレーム14Bの溝部内にパターン化薄膜17を形成する。パターン化薄膜17は、金属等の導電材料によって形成される。パターン化薄膜17の材料としては、例えば銅(Cu)が用いられる。

【0048】

次に、例えば、図15に示した積層体を有機溶剤に浸漬し、揺動することによって、図16に示したように、フレーム14Bを溶解させて除去する。

【0049】

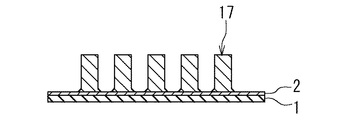

最後に、図17に示したように、パターン化薄膜17をマスクとして、ウェットエッチングによって、あるいはイオンミリング、反応性イオンエッチング等のドライエッチングによって、電極膜2のうち、パターン化薄膜17の下に存在する部分以外の部分を除去する。

【0050】

このようにして形成されたパターン化薄膜17は、隣接する複数の線状部分72を有している。このパターン化薄膜17では、線状部分72において、下地である電極膜2に近い一部分である第2の部分72bの最大幅が、残りの部分である第1の部分72aの幅よりも大きくなっている。

【0051】

図18ないし図20は、それぞれ、本実施の形態における線状部分72の形状の例を示している。これらの例では、いずれも、第2の部分72bの幅は、線状部分72の底部において最大であり、第1の部分72aに近い位置ほど小さくなっている。また、図18に示した例では、第2の部分72bの側壁は、基板1の上面に垂直な方向に対して傾いた斜面になっている。図19に示した例では、第2の部分72bの側壁は、基板1の上面に垂直な方向に対して傾いた凹面になっている。図20に示した例では、第2の部分72bの側壁は、基板1の上面に垂直な方向に対して傾いた凸面になっている。

【0052】

次に、本実施の形態に係るパターン化薄膜形成方法の実施例について説明する。本実施例では、電極膜2を形成する工程までは、第1の実施の形態における実施例と同様である。

【0053】

本実施例では、次に、電極膜2の上に、スピンコート法によりレジストを塗布して、レジスト層14Aを形成した。レジストとしては、信越化学工業社製SIPR−9691(製品名)を使用した。レジスト層14Aの厚みは3μmとした。次に、レジスト層14Aに対して、ホットプレートを用いて100℃の温度で、180秒間の熱処理を施した。

【0054】

次に、露光装置を用いて、以下の条件で、マスク5を介してレジスト層14Aの露光を行い、レジスト層14Aに、マスク5のパターンに対応した潜像を形成した。露光装置としては、ニコン製NSR−i12TFH(製品名)を用いた。マスク5のパターンは、第1の実施の形態における実施例と同様である。露光量(Dose)は、400mJ/cm2とした。

【0055】

次に、現像液として2.38%のテトラメチルアンモニウムヒドロキシドの水溶液を用いて、パドル法によって、レジスト層14Aに対して、50秒間の現像を2回行った。その後、レジスト層14Aを水洗し、乾燥させて、フレーム14Bを完成させた。

【0056】

次に、フレーム14Bを用いて電気めっきを行って、フレーム14Bの溝部内に、Cuよりなるパターン化薄膜17を形成した。めっき浴としては、Cuのめっきに用いられる一般的な硫酸銅浴を用いた。パターン化薄膜17の厚さは2.8μmとした。

【0057】

次に、パターン化薄膜17を含む積層体を、アセトン中に浸漬し、揺動することによって、フレーム14Bを溶解させて除去した。

【0058】

次に、イオンミリング装置を用いて、第1の実施の形態における実施例と同じ条件で、電極膜2を選択的にエッチングして、電極膜2のうち、パターン化薄膜17の下に存在する部分以外の部分を除去した。

【0059】

このようにして、パターン化薄膜17からなり、ピッチが2.5μm、厚さが2.8μmで、10ターンの薄膜コイルが得られた。パターン化薄膜17の線状部分72において、第1の部分72aの幅は1.7μmで、第2の部分72bの最大幅は1.9μmであった。第2の部分72bのうち、第1の部分72aの側壁よりも外側に張り出した2つの部分の断面形状は、それぞれ、最大幅が0.1μmで、最大高さが0.1μmの楔形であった。

【0060】

本実施の形態におけるその他の構成、作用および効果は、第1の実施の形態と同様である。

【0061】

[第3の実施の形態]

次に、図21ないし図28を参照して、本発明の第3の実施の形態に係るパターン化薄膜形成方法について説明する。本実施の形態では、画像反転機能を有するレジストを用いて、底部近傍においてアンダーカットの入った形状のフレームを形成する。なお、画像反転機能を有するレジストを用いて、底部近傍においてアンダーカットの入った形状のレジスト層を形成する方法については、特開平9−96909号公報に記載されている。

【0062】

本実施の形態に係るパターン化薄膜形成方法では、図2に示したように、電極膜2を形成する工程までは、第1の実施の形態と同様である。本実施の形態では、次に、図21に示したように、電極膜2の上に、スピンコート法等により、画像反転機能を有するレジストを塗布して、レジスト層24Aを形成する。画像反転機能を有するレジストとは、ポジ型レジストであるが、露光によって現像液に対して可溶性となった部分が、加熱されることにより現像液に対して不溶性に変化するレジストである。このようなレジストとしては、具体的には、特開平9−96909号公報に示された種々のレジストを用いることができる。次に、必要に応じて、レジスト層24Aに対して熱処理を施す。

【0063】

次に、図22に示したように、マスク25を介してレジスト層24Aの露光を行い、レジスト層24Aに、マスク25のパターンに対応した潜像を形成する。次に、必要に応じて、レジスト層24Aに対して熱処理を施す。マスク25のパターンは、レジスト層24Aのうち、現像後に残す部分が露光されるようなパターンである。図22において、符号24Bは、レジスト層24Aのうちの露光された部分を示している。

【0064】

次に、図23に示したように、レジスト層24Aを加熱して、レジスト層24Aのうちの露光された部分24Bを、現像液に対して不溶性となるように変化させる。

【0065】

次に、図24に示したように、レジスト層24Aの全面を露光し、レジスト層24Aのうち、最初の露光時に露光された部分24B以外の部分を、現像液に対して可溶性となるようにする。

【0066】

次に、図25に示したように、レジスト層24Aを現像液によって現像する。これにより、残ったレジスト層24Aによってフレーム24Cが形成される。次に、フレーム24Cを水洗し、乾燥させる。

【0067】

画像反転機能を有するレジストを用い、露光、露光後の熱処理および現像の各条件を調整することにより、底部近傍においてアンダーカットの入った形状のフレーム24Cを形成することができる。

【0068】

次に、必要に応じてめっき前処理を行った後、図26に示したように、フレーム24Cを用い、電極膜2に電流を流して電気めっきを行って、フレーム24Cの溝部内にパターン化薄膜27を形成する。パターン化薄膜27は、金属等の導電材料によって形成される。パターン化薄膜27の材料としては、例えば銅(Cu)が用いられる。

【0069】

次に、例えば、図26に示した積層体を有機溶剤に浸漬し、揺動することによって、図27に示したように、フレーム24Cを溶解させて除去する。

【0070】

最後に、図28に示したように、パターン化薄膜27をマスクとして、ウェットエッチングによって、あるいはイオンミリング、反応性イオンエッチング等のドライエッチングによって、電極膜2のうち、パターン化薄膜27の下に存在する部分以外の部分を除去する。

【0071】

このようにして形成されたパターン化薄膜27は、隣接する複数の線状部分73を有している。このパターン化薄膜27では、線状部分73において、下地である電極膜2に近い一部分である第2の部分73bの最大幅が、残りの部分である第1の部分73aの幅よりも大きくなっている。

【0072】

なお、本実施の形態における線状部分73の形状は、第2の実施の形態における線状部分72の形状と同様である。

【0073】

次に、本実施の形態に係るパターン化薄膜形成方法の実施例について説明する。本実施例では、電極膜2を形成する工程までは、第1の実施の形態における実施例と同様である。

【0074】

本実施例では、次に、電極膜2の上に、スピンコート法によりレジストを塗布して、レジスト層24Aを形成した。レジストとしては、クラリアント社製AZ5214E(製品名)を使用した。レジスト層24Aの厚みは3μmとした。次に、レジスト層24Aに対して、ホットプレートを用いて100℃の温度で、180秒間の熱処理を施した。

【0075】

次に、露光装置を用いて、以下の条件で、マスク25を介してレジスト層24Aの露光を行い、レジスト層24Aに、マスク25のパターンに対応した潜像を形成した。露光装置としては、ニコン製NSR−i12TFH(製品名)を用いた。マスク25のパターンは、遮光部が10ターンの渦巻き状をなし、遮光部の幅が1.5μmで、透光部の幅が1.0μmで、遮光部のピッチが2.5μmとなるパターンとした。露光量(Dose)は、50mJ/cm2とした。

【0076】

次に、レジスト層24Aに対して、ホットプレートを用いて100℃の温度で、180秒間の熱処理を施して、レジスト層24Aのうちの露光された部分24Bを、現像液に対して不溶性となるように変化させた。

【0077】

次に、露光装置を用いて、以下の条件で、レジスト層24Aの全面を露光し、レジスト層24Aのうち、最初の露光時に露光された部分24B以外の部分を、現像液に対して可溶性となるようにした。露光装置としては、ニコン製NSR−i12TFH(製品名)を用いた。露光量(Dose)は、100mJ/cm2とした。

【0078】

次に、現像液として2.38%のテトラメチルアンモニウムヒドロキシドの水溶液を用いて、パドル法によって、レジスト層24Aに対して、50秒間の現像を4回行った。その後、レジスト層24Aを水洗し、乾燥させて、フレーム24Cを完成させた。

【0079】

次に、フレーム24Cを用いて電気めっきを行って、フレーム24Cの溝部内に、Cuよりなるパターン化薄膜27を形成した。めっき浴としては、Cuのめっきに用いられる一般的な硫酸銅浴を用いた。パターン化薄膜27の厚さは2.8μmとした。

【0080】

次に、パターン化薄膜27を含む積層体を、アセトン中に浸漬し、揺動することによって、フレーム24Cを溶解させて除去した。

【0081】

次に、イオンミリング装置を用いて、第1の実施の形態における実施例と同じ条件で、電極膜2を選択的にエッチングして、電極膜2のうち、パターン化薄膜27の下に存在する部分以外の部分を除去した。

【0082】

このようにして、パターン化薄膜27からなり、ピッチが2.5μm、厚さが2.8μmで、10ターンの薄膜コイルが得られた。パターン化薄膜27の線状部分73において、第1の部分73aの幅は1.7μmで、第2の部分73bの最大幅は2.0μmであった。第2の部分73bのうち、第1の部分73aの側壁よりも外側に張り出した2つの部分の断面形状は、それぞれ、最大幅が0.15μmで、最大高さが0.2μmの楔形であった。

【0083】

本実施の形態におけるその他の構成、作用および効果は、第1の実施の形態と同様である。

【0084】

なお、本発明は上記各実施の形態に限定されず、種々の変更が可能である。例えば、本発明は、第1の実施の形態で示した薄膜インダクタに限らず、薄膜磁気ヘッド、半導体デバイス、薄膜を用いたセンサ、薄膜を用いたアクチュエータ等の他のマイクロデバイスにおけるパターン化薄膜を形成する場合にも適用することができる。また、パターン化薄膜は、コイルに限らず、配線等であってもよい。

【0085】

【発明の効果】

以上説明したように請求項1記載のパターン化薄膜形成方法では、底部近傍においてアンダーカットの入った形状のフレームを用いてめっきを行って、パターン化薄膜を形成する。従って、本発明によれば、フレームめっき法を用いて、幅が小さく且つ抵抗値の小さい線状部分を有するパターン化薄膜を形成することができるという効果を奏する。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態に係るパターン化薄膜形成方法が適用されるマイクロデバイスの一例としての薄膜インダクタを示す斜視図である。

【図2】本発明の第1の実施の形態に係るパターン化薄膜形成方法における一工程を説明するための断面図である。

【図3】図2に示した工程に続く工程を説明するための断面図である。

【図4】図3に示した工程に続く工程を説明するための断面図である。

【図5】図4に示した工程に続く工程を説明するための断面図である。

【図6】図5に示した工程に続く工程を説明するための断面図である。

【図7】図6に示した工程に続く工程を説明するための断面図である。

【図8】図7に示した工程に続く工程を説明するための断面図である。

【図9】図8に示した工程に続く工程を説明するための断面図である。

【図10】本発明の第1の実施の形態におけるパターン化薄膜の他の形状を示す断面図である。

【図11】本発明の第1の実施の形態におけるパターン化薄膜の更に他の形状を示す断面図である。

【図12】本発明の第2の実施の形態に係るパターン化薄膜形成方法における一工程を説明するための断面図である。

【図13】図12に示した工程に続く工程を説明するための断面図である。

【図14】図13に示した工程に続く工程を説明するための断面図である。

【図15】図14に示した工程に続く工程を説明するための断面図である。

【図16】図15に示した工程に続く工程を説明するための断面図である。

【図17】図16に示した工程に続く工程を説明するための断面図である。

【図18】本発明の第2の実施の形態におけるパターン化薄膜の線状部分の形状の一例を示す断面図である。

【図19】本発明の第2の実施の形態におけるパターン化薄膜の線状部分の形状の他の例を示す断面図である。

【図20】本発明の第2の実施の形態におけるパターン化薄膜の線状部分の形状の更に他の例を示す断面図である。

【図21】本発明の第3の実施の形態に係るパターン化薄膜形成方法における一工程を説明するための断面図である。

【図22】図21に示した工程に続く工程を説明するための断面図である。

【図23】図22に示した工程に続く工程を説明するための断面図である。

【図24】図23に示した工程に続く工程を説明するための断面図である。

【図25】図24に示した工程に続く工程を説明するための断面図である。

【図26】図25に示した工程に続く工程を説明するための断面図である。

【図27】図26に示した工程に続く工程を説明するための断面図である。

【図28】図27に示した工程に続く工程を説明するための断面図である。

【符号の説明】

1…基板、2…電極膜、3A…第1層、3B…第1フレーム層、4A…第2層、4B…第2フレーム層、5…マスク、6…フレーム、7…パターン化薄膜、71…線状部分、71a…第1の部分、71b…第2の部分、101…基板、102…薄膜コイル、103…リード。

Claims (1)

- フレームめっき法によって、隣接する複数の線状部分を有するパターン化薄膜を形成する方法であって、

下地の上に、底部近傍においてアンダーカットの入った形状のフレームを形成する工程と、

前記フレームを用いてめっきを行って、前記線状部分において前記下地に近い一部分の幅が残りの部分と前記一部分との境界位置における前記残りの部分の幅よりも大きくなり、隣接する前記一部分の間隔が隣接する前記残りの部分の間隔よりも小さくなるように前記パターン化薄膜を形成するめっき工程とを備え、

前記フレームは、前記下地の上に配置された第1フレーム層と、前記第1フレーム層の上に配置された第2フレーム層とを有し、

前記第1フレーム層の幅は、前記第2フレーム層の幅よりも小さく、

前記フレームを形成する工程は、

前記下地の上に、現像液によって溶解される材料よりなる第1層を形成する工程と、

前記第1層の上にレジストよりなる第2層を形成する工程と、

前記第2層を露光する工程と、

前記第2層を現像する工程とを含み、

前記第2層を現像する工程において、現像液によって前記第2層の一部が溶解されると共に前記第1層の一部も溶解され、残った前記第1層によって前記第1フレーム層が形成され、残った前記第2層によって前記第2フレーム層が形成されることを特徴とするパターン化薄膜形成方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002222799A JP3957178B2 (ja) | 2002-07-31 | 2002-07-31 | パターン化薄膜形成方法 |

| US10/617,169 US20040023057A1 (en) | 2002-07-31 | 2003-07-11 | Patterned thin film and method of forming same |

| US11/699,549 US7655282B2 (en) | 2002-07-31 | 2007-01-30 | Method of forming patterned film |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002222799A JP3957178B2 (ja) | 2002-07-31 | 2002-07-31 | パターン化薄膜形成方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004063965A JP2004063965A (ja) | 2004-02-26 |

| JP2004063965A5 JP2004063965A5 (ja) | 2005-02-03 |

| JP3957178B2 true JP3957178B2 (ja) | 2007-08-15 |

Family

ID=31184933

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002222799A Expired - Fee Related JP3957178B2 (ja) | 2002-07-31 | 2002-07-31 | パターン化薄膜形成方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US20040023057A1 (ja) |

| JP (1) | JP3957178B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7519608B2 (en) | 2004-03-22 | 2009-04-14 | Sliccware | Secure virtual data warehousing system and method |

| US8679860B1 (en) * | 2006-08-07 | 2014-03-25 | Sandia Corporation | Lateral electrodeposition of compositionally modulated metal layers |

| US20130002685A1 (en) * | 2011-06-30 | 2013-01-03 | Qualcomm Mems Technologies, Inc. | Bonded double substrate approach to solve laser drilling problems |

| WO2014068612A1 (ja) * | 2012-10-30 | 2014-05-08 | 株式会社Leap | コイル素子の製造方法 |

| CN103600529A (zh) * | 2013-10-30 | 2014-02-26 | 苏州米达思精密电子有限公司 | 一种黑色补强钢片结构 |

| JP6716866B2 (ja) * | 2015-06-30 | 2020-07-01 | Tdk株式会社 | コイル部品 |

| US11705624B2 (en) | 2017-11-29 | 2023-07-18 | Dai Nippon Printing Co., Ltd. | Wiring board and method for manufacturing wiring board |

| JP7211323B2 (ja) * | 2019-10-08 | 2023-01-24 | 株式会社村田製作所 | インダクタ部品、及びインダクタ部品の製造方法 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3093502A (en) * | 1959-12-30 | 1963-06-11 | Johnson & Johnson | Nonwoven fabrics and methods of manufacturing the same |

| US3853715A (en) * | 1973-12-20 | 1974-12-10 | Ibm | Elimination of undercut in an anodically active metal during chemical etching |

| JPS5636706A (en) | 1979-09-04 | 1981-04-10 | Fanuc Ltd | Sequence program translation system of programmable sequence controller |

| JP2629293B2 (ja) | 1988-08-30 | 1997-07-09 | 日本電気株式会社 | 薄膜磁気ヘッド |

| JPH02281623A (ja) | 1989-04-21 | 1990-11-19 | Nec Corp | メッキ配線の形成方法 |

| US5043043A (en) * | 1990-06-22 | 1991-08-27 | Massachusetts Institute Of Technology | Method for fabricating side drive electrostatic micromotor |

| US5773200A (en) * | 1994-06-23 | 1998-06-30 | Shin-Etsu Chemical Co., Ltd. | Positive resist composition suitable for lift-off technique and pattern forming method |

| JP2973874B2 (ja) | 1994-06-23 | 1999-11-08 | 信越化学工業株式会社 | パターン形成方法 |

| US5622761A (en) * | 1995-02-27 | 1997-04-22 | Cole; Roger J. | Double-sided releaseable adhesive tape or note |

| JP2922855B2 (ja) | 1995-07-26 | 1999-07-26 | ティーディーケイ株式会社 | T形断面のレジストパターンおよびその製造方法ならびに磁気抵抗効果型薄膜素子 |

| US5725997A (en) * | 1995-07-26 | 1998-03-10 | Tdk Corporation | Method for preparing a resist pattern of t-shaped cross section |

| JPH09252087A (ja) | 1996-03-14 | 1997-09-22 | Sony Corp | Icのリアクタンス形成方法 |

| JPH10116402A (ja) | 1996-10-11 | 1998-05-06 | Hitachi Ltd | 薄膜磁気ヘッドの製造方法 |

| US5989667A (en) * | 1997-02-10 | 1999-11-23 | Tayebi; Amad | Opaque sticker for temporary posting applications and subsequent saving without exhibiting inconvenient sticking to other surfaces |

| JPH10334410A (ja) * | 1997-05-29 | 1998-12-18 | Tdk Corp | 薄膜磁気ヘッド及びその製造方法 |

| JPH11148861A (ja) * | 1997-09-09 | 1999-06-02 | Honda Motor Co Ltd | マイクロブリッジ構造 |

| US6201243B1 (en) * | 1998-07-20 | 2001-03-13 | Institut National D'optique | Microbridge structure and method for forming the microbridge structure |

| JP3363841B2 (ja) * | 1999-06-28 | 2003-01-08 | アルプス電気株式会社 | 薄膜磁気ヘッド及びその製造方法 |

| JP3522595B2 (ja) * | 1999-07-14 | 2004-04-26 | Tdk株式会社 | 薄膜磁気ヘッドおよびその製造方法 |

| US6655207B1 (en) * | 2000-02-16 | 2003-12-02 | Honeywell International Inc. | Flow rate module and integrated flow restrictor |

| US6586841B1 (en) * | 2000-02-23 | 2003-07-01 | Onix Microsystems, Inc. | Mechanical landing pad formed on the underside of a MEMS device |

| US6683387B1 (en) * | 2000-06-15 | 2004-01-27 | Advanced Micro Devices, Inc. | Flip chip carrier package with adapted landing pads |

-

2002

- 2002-07-31 JP JP2002222799A patent/JP3957178B2/ja not_active Expired - Fee Related

-

2003

- 2003-07-11 US US10/617,169 patent/US20040023057A1/en not_active Abandoned

-

2007

- 2007-01-30 US US11/699,549 patent/US7655282B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US20070122553A1 (en) | 2007-05-31 |

| JP2004063965A (ja) | 2004-02-26 |

| US20040023057A1 (en) | 2004-02-05 |

| US7655282B2 (en) | 2010-02-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7655282B2 (en) | Method of forming patterned film | |

| EP0341843A2 (en) | A process of forming a conductor pattern | |

| US8546048B2 (en) | Forming sloped resist, via, and metal conductor structures using banded reticle structures | |

| US6605412B2 (en) | Resist pattern and method for forming wiring pattern | |

| JP3818188B2 (ja) | マスクパターンの形成方法、該マスクパターンを用いたパターニング方法及び薄膜磁気ヘッドの製造方法 | |

| JPH10229153A (ja) | リードフレームの製造方法 | |

| JP3874268B2 (ja) | パターン化薄膜およびその形成方法 | |

| JP3563809B2 (ja) | パターン形成方法 | |

| JP4023236B2 (ja) | 金属配線の形成方法 | |

| JP2004063740A (ja) | パターン化薄膜形成方法 | |

| JPS59155921A (ja) | レジストパタ−ンの形成方法 | |

| JP2003017474A (ja) | 薄膜パターニング方法、薄膜デバイスの製造方法及び薄膜磁気ヘッドの製造方法 | |

| JP2000181077A (ja) | リフトオフ法による配線パターン形成方法 | |

| JPS6015920A (ja) | 半導体装置の製造方法 | |

| JPH02156244A (ja) | パターン形成方法 | |

| JP2713061B2 (ja) | レジストパターンの形成方法 | |

| JPS61216110A (ja) | 金属パタ−ン形成方法 | |

| JPH0786119A (ja) | 半導体装置の製造方法 | |

| JPH03142466A (ja) | 半導体装置の製造方法及びそれに用いられるマスク | |

| KR19990057381A (ko) | 반도체 소자의 미세패턴 제조방법 | |

| JP2003332212A (ja) | マスクパターン形成方法および半導体装置の製造方法 | |

| JPH04332118A (ja) | パターンの形成方法 | |

| JP2006100289A (ja) | 段差付き凹部の形成方法 | |

| JPH01302841A (ja) | 半導体装置の配線形成方法 | |

| JPS60106132A (ja) | パタ−ン形成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040226 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040226 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050517 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050524 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050629 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060228 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060327 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061113 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061129 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070427 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070502 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3957178 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110518 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130518 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140518 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |