JP3901432B2 - 強誘電体キャパシタを有するメモリセルアレイおよびその製造方法 - Google Patents

強誘電体キャパシタを有するメモリセルアレイおよびその製造方法 Download PDFInfo

- Publication number

- JP3901432B2 JP3901432B2 JP2000251436A JP2000251436A JP3901432B2 JP 3901432 B2 JP3901432 B2 JP 3901432B2 JP 2000251436 A JP2000251436 A JP 2000251436A JP 2000251436 A JP2000251436 A JP 2000251436A JP 3901432 B2 JP3901432 B2 JP 3901432B2

- Authority

- JP

- Japan

- Prior art keywords

- signal electrode

- layer

- ferroelectric

- region

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000003990 capacitor Substances 0.000 title claims description 73

- 238000004519 manufacturing process Methods 0.000 title claims description 42

- 239000000463 material Substances 0.000 claims description 91

- 230000004048 modification Effects 0.000 claims description 57

- 238000012986 modification Methods 0.000 claims description 57

- 239000000758 substrate Substances 0.000 claims description 50

- 238000000059 patterning Methods 0.000 claims description 20

- 239000011159 matrix material Substances 0.000 claims description 10

- 239000010410 layer Substances 0.000 description 252

- 238000000034 method Methods 0.000 description 90

- 239000007772 electrode material Substances 0.000 description 22

- 230000015572 biosynthetic process Effects 0.000 description 18

- 230000008569 process Effects 0.000 description 18

- 238000005530 etching Methods 0.000 description 13

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 12

- 238000005229 chemical vapour deposition Methods 0.000 description 11

- 239000004642 Polyimide Substances 0.000 description 9

- 239000007791 liquid phase Substances 0.000 description 9

- 229920001721 polyimide Polymers 0.000 description 9

- 238000000151 deposition Methods 0.000 description 8

- 239000012808 vapor phase Substances 0.000 description 8

- CPLXHLVBOLITMK-UHFFFAOYSA-N Magnesium oxide Chemical compound [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 7

- 229910010272 inorganic material Inorganic materials 0.000 description 6

- 239000011147 inorganic material Substances 0.000 description 6

- 239000011368 organic material Substances 0.000 description 6

- 238000001020 plasma etching Methods 0.000 description 6

- 229910052726 zirconium Inorganic materials 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 5

- 230000008021 deposition Effects 0.000 description 5

- 230000006870 function Effects 0.000 description 5

- 238000001459 lithography Methods 0.000 description 5

- 238000000992 sputter etching Methods 0.000 description 5

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- 239000006087 Silane Coupling Agent Substances 0.000 description 4

- 229910052746 lanthanum Inorganic materials 0.000 description 4

- 229910052745 lead Inorganic materials 0.000 description 4

- 239000000395 magnesium oxide Substances 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 239000000203 mixture Substances 0.000 description 4

- 229910052758 niobium Inorganic materials 0.000 description 4

- 239000010955 niobium Substances 0.000 description 4

- 239000011295 pitch Substances 0.000 description 4

- 229910052697 platinum Inorganic materials 0.000 description 4

- 238000004528 spin coating Methods 0.000 description 4

- 238000004544 sputter deposition Methods 0.000 description 4

- -1 thiol compound Chemical class 0.000 description 4

- YMWUJEATGCHHMB-UHFFFAOYSA-N Dichloromethane Chemical compound ClCCl YMWUJEATGCHHMB-UHFFFAOYSA-N 0.000 description 3

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- 125000000217 alkyl group Chemical group 0.000 description 3

- 238000005137 deposition process Methods 0.000 description 3

- 239000003989 dielectric material Substances 0.000 description 3

- 230000005621 ferroelectricity Effects 0.000 description 3

- 150000002430 hydrocarbons Chemical group 0.000 description 3

- 229910052741 iridium Inorganic materials 0.000 description 3

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 3

- 229910052749 magnesium Inorganic materials 0.000 description 3

- 239000011777 magnesium Substances 0.000 description 3

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- 125000003178 carboxy group Chemical group [H]OC(*)=O 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000004090 dissolution Methods 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 2

- 239000003595 mist Substances 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 239000012071 phase Substances 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 125000003396 thiol group Chemical group [H]S* 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- 239000004215 Carbon black (E152) Substances 0.000 description 1

- HEDRZPFGACZZDS-UHFFFAOYSA-N Chloroform Chemical compound ClC(Cl)Cl HEDRZPFGACZZDS-UHFFFAOYSA-N 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- 229910019897 RuOx Inorganic materials 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- 238000001311 chemical methods and process Methods 0.000 description 1

- 229960001701 chloroform Drugs 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- NKZSPGSOXYXWQA-UHFFFAOYSA-N dioxido(oxo)titanium;lead(2+) Chemical compound [Pb+2].[O-][Ti]([O-])=O NKZSPGSOXYXWQA-UHFFFAOYSA-N 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 125000001153 fluoro group Chemical group F* 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 229930195733 hydrocarbon Natural products 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000010884 ion-beam technique Methods 0.000 description 1

- 238000000608 laser ablation Methods 0.000 description 1

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 description 1

- 229910052451 lead zirconate titanate Inorganic materials 0.000 description 1

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910000480 nickel oxide Inorganic materials 0.000 description 1

- 150000002894 organic compounds Chemical class 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 150000003961 organosilicon compounds Chemical class 0.000 description 1

- ZBSCCQXBYNSKPV-UHFFFAOYSA-N oxolead;oxomagnesium;2,4,5-trioxa-1$l^{5},3$l^{5}-diniobabicyclo[1.1.1]pentane 1,3-dioxide Chemical compound [Mg]=O.[Pb]=O.[Pb]=O.[Pb]=O.O1[Nb]2(=O)O[Nb]1(=O)O2 ZBSCCQXBYNSKPV-UHFFFAOYSA-N 0.000 description 1

- GNRSAWUEBMWBQH-UHFFFAOYSA-N oxonickel Chemical compound [Ni]=O GNRSAWUEBMWBQH-UHFFFAOYSA-N 0.000 description 1

- 238000005240 physical vapour deposition Methods 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

- 238000007738 vacuum evaporation Methods 0.000 description 1

- 238000001947 vapour-phase growth Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/55—Capacitors with a dielectric comprising a perovskite structure material

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/22—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using ferroelectric elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Semiconductor Memories (AREA)

Description

【発明の属する技術分野】

本発明は、強誘電体キャパシタを有するメモリセルアレイ、特に、セルトランジスタを有せず、強誘電体キャパシタのみを用いた単純マトリクス型のメモリセルアレイおよびその製造方法、さらに前記メモリセルアレイを含む強誘電体メモリ装置に関する。

【0002】

【背景技術および発明が解決しようとする課題】

セルトランジスタを有せず、強誘電体キャパシタのみを用いた単純マトリクス型のメモリセルアレイは、非常に簡単な構造を有し、高い集積度を得ることができることから、その開発が期待されている。

【0003】

本発明の目的は、強誘電体キャパシタを構成する強誘電体層が特定のパターンを有し、信号電極の浮遊容量を小さくすることができるメモリセルアレイ、およびその製造方法、さらには本発明のメモリセルアレイを含む強誘電体メモリ装置を提供することにある。

【0004】

【課題を解決するための手段】

本発明にかかる第1のメモリセルアレイは、強誘電体キャパシタからなるメモリセルがマトリクス状に配列され、

前記強誘電体キャパシタは、第1信号電極と、該第1信号電極と交差する方向に配列された第2信号電極と、少なくとも前記第1信号電極と前記第2信号電極との交差領域に配置された強誘電体層と、を含み、

前記強誘電体層は、第1信号電極または第2信号電極に沿ってライン状に配置される。

【0005】

このメモリセルアレイは、具体的には、

(1)前記強誘電体層は、前記第1信号電極上に選択的に配置された構造、および

(2)前記強誘電体層は、前記第2信号電極下に選択的に配置された構造、を有する。

【0006】

これらのメモリセルアレイは、いずれも強誘電体層が信号電極の一方に沿ってライン状に形成されているため、他方の信号電極の浮遊容量を小さくできる。

【0007】

さらに、本発明にかかる第2のメモリセルアレイは、強誘電体キャパシタからなるメモリセルがマトリクス状に配列され、

前記強誘電体キャパシタは、第1信号電極と、該第1信号電極と交差する方向に配列された第2信号電極と、少なくとも前記第1信号電極と前記第2信号電極との交差領域に配置された強誘電体層と、を含み、

前記強誘電体層は、前記第1信号電極と前記第2信号電極との交差領域のみにブロック状に配置されている。

【0008】

このメモリセルアレイは、強誘電体キャパシタを構成する強誘電体層が最小の領域で形成されるため、さらに信号電極の浮遊容量を小さくできる。

【0009】

上記メモリセルアレイは、いずれも以下の態様を有することが望ましい。

【0010】

(A) 基体上に前記強誘電体キャパシタが配置され、前記基体の露出面が覆われるように、信号電極および強誘電体層からなる積層体の相互間に、誘電体層が設けられている。このとき、前記誘電体層は、前記強誘電体層より小さい誘電率を有する材料からなることが望ましい。このような誘電体層を設けることにより、信号電極の浮遊容量を効果的に小さくできる。

【0011】

(B) 前記基体上に、該基体の表面と異なる表面特性を有する表面修飾層が形成されることができる。このような表面修飾層を設けることで、エッチングを用いずに選択的に信号電極および強誘電体層の少なくとも一方を形成できる。このような表面修飾層は、前記強誘電体キャパシタが形成されない領域に配置され、該表面修飾層の表面が前記強誘電体キャパシタの材料に対して前記基体の表面より低い親和性を有することができる。あるいは、前記表面修飾層は、前記強誘電体キャパシタが形成される領域に配置され、該表面修飾層の表面が前記強誘電体キャパシタの材料に対して前記基体の表面より高い親和性を有することができる。

【0012】

本発明にかかるメモリセルアレイの製造方法は、強誘電体キャパシタからなるメモリセルがマトリクス状に配列されたメモリセルアレイの製造方法であって、

基体上に、所定パターンの第1信号電極を形成する工程、

前記第1信号電極上に、該第1信号電極に沿ってライン状の強誘電体層を選択的に形成する工程、および

前記第1信号電極と交差する方向に第2信号電極を形成する工程、

を含むことができる。

【0013】

この方法において、前記基体上に、前記第1信号電極および前記強誘電体層の少なくとも一方を形成するための材料が優先的に堆積される表面特性を有する第1の領域と、前記第1の領域に比較して前記第1信号電極および前記強誘電体層の少なくとも一方を形成するための材料が堆積され難い表面特性を有する第2の領域と、を形成する工程、および

前記第1信号電極および前記強誘電体層の少なくとも一方を形成するための材料を付与し、前記第1の領域に該部材を選択的に形成する工程、を含むことができる。そして、前記基体の表面に、前記第1および第2の領域を形成することができる。

【0014】

さらに、この製造方法おいて、前記第1の領域では、前記基体の表面を露出させ、前記第2の領域では、前記第1信号電極および前記強誘電体層の材料に対する親和性が、前記基体の第1の領域での露出面より低い表面特性を有する表面修飾層を形成することができる。あるいは、この製造方法において、前記第2の領域では、前記基体の表面を露出させ、前記第1の領域では、前記第1信号電極および前記強誘電体層の材料に対する親和性が、前記基体の第2の領域での露出面より高い表面特性を有する表面修飾層を形成することができる。

【0015】

本発明にかかる他の製造方法は、強誘電体キャパシタからなるメモリセルがマトリクス状に配列されたメモリセルアレイの製造方法であって、

基体上に、所定パターンの第1信号電極を形成する工程、および

前記第1信号電極と交差する方向に、強誘電体層および第2信号電極を形成する工程であって、前記強誘電体層は前記第2信号電極に沿ってライン状に形成される工程、

を含むことができる。

【0016】

この製造方法では、前記強誘電体層および前記第2信号電極を、同一マスクを用いたエッチングによってパターニングすることができる。

【0017】

さらに、本発明にかかる他の製造方法は、強誘電体キャパシタからなるメモリセルがマトリクス状に配列されたメモリセルアレイの製造方法であって、

基体上に、所定パターンの第1信号電極を形成する工程、

前記第1信号電極上に、該第1信号電極に沿ってライン状に強誘電体層を形成する工程、

前記第1信号電極と交差する方向に第2信号電極を形成する工程、および

前記強誘電体層をさらにパターニングして、前記第1信号電極と前記第2信号電極との交差領域のみにブロック状に形成する工程、

を含むことができる。

【0018】

この製造方法においても、前述した表面修飾層を用いて信号電極および強誘電体層の少なくとも一方を形成できる。さらに、強誘電体層および一方の信号電極を、同一マスクを用いたエッチングによってパターニングすることができる。

【0019】

さらに、上記各製造方法においては、少なくとも前記基体の露出面が覆われるように、信号電極および強誘電体層からなる積層体の相互間に、誘電体層を設けることができる。

【0020】

本発明にかかる強誘電体メモリ装置は、本発明にかかるメモリセルアレイを含んで構成される。

【0021】

【発明の実施の形態】

[第1の実施の形態]

(デバイス)

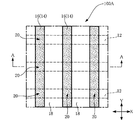

図1は、本実施の形態に係るメモリセルアレイを模式的に示す平面図であり、図2は、本実施の形態に係る強誘電体メモリ装置を示す図であり、図3は、図1に示すメモリセルアレイの一部(図1の符号「A」で示す部分)を拡大して示す平面図であり、図4は、図3のA−A線に沿った断面図である。平面図において、( )内の数字は最上層の下の層を示す。

【0022】

本実施の形態の強誘電体メモリ装置1000は、図2に示すように、メモリセル20が単純マトリクス状に配列されたメモリセルアレイ100Aと、メモリセル20に対して選択的に情報の書き込みもしくは読み出しを行うための各種回路、例えば、第1信号電極12を選択的に制御するための第1駆動回路50と、第2信号電極16を選択的に制御するための第2駆動回路52と、センスアンプなどの信号検出回路(図示せず)とを含む。

【0023】

メモリセルアレイ100Aは、行選択のための第1信号電極(ワード線)12と、列選択のための第2信号電極(ビット線)16とが直交するように配列されている。すなわち、X方向に沿って第1信号電極12が所定ピッチで配列され、X方向と直交するY方向に沿って第2信号電極16が所定ピッチで配列されている。なお、信号電極は、上記の逆でもよく、第1信号電極がビット線、第2信号電極がワード線でもよい。

【0024】

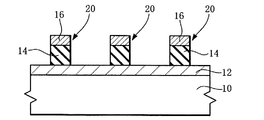

本実施の形態に係るメモリセルアレイ100Aは、図3および図4に示すように、絶縁性の基体10上に、第1信号電極(下電極)12、強誘電体キャパシタを構成する強誘電体層14および第2信号電極(上電極)16が積層され、第1信号電極12,強誘電体層14および第2信号電極16によって強誘電体キャパシタ20が構成される。すなわち、第1信号電極12と第2信号電極16との交差領域において、それぞれ強誘電体キャパシタ20からなるメモリセルが構成されている。

【0025】

また、強誘電体層14と第2信号電極16とからなる積層体の相互には、基体10および第1信号電極12の露出面を覆うように、誘電体層18が形成されている。この誘電体層18は、強誘電体層14に比べて小さい誘電率を有することが望ましい。このように強誘電体層14および第2信号電極16からなる積層体の相互間に、強誘電体層14より誘電率の小さい誘電体層18を介在させることにより、第2信号電極16の浮遊容量を小さくすることができる。その結果、強誘電体メモリ装置1000における書き込みおよび読み出しの動作をより高速に行うことが可能となる。

【0026】

そして、本実施の形態では、強誘電体層14は、第2の信号電極16に沿ってライン状に形成されている。強誘電体層14をライン状に形成することで、第1信号電極12の浮遊容量を小さくすることができる。

【0027】

また、このようなライン状の強誘電体層14は、後述するように、第2の信号電極16のパターニングに用いられるマスクを用いてパターニングして形成することができる。

【0028】

さらに、誘電体層18および第2信号電極16を覆うように、必要に応じて絶縁層からなる保護層が形成されていてもよい。

【0029】

(強誘電体メモリ装置の動作)

次に、本実施の形態の強誘電体メモリ装置1000における書き込み,読み出し動作の一例について述べる。

【0030】

まず、読み出し動作においては、選択セルのキャパシタに読み出し電圧「V0」が印加される。これは、同時に‘0’の書き込み動作を兼ねている。このとき、選択されたビット線を流れる電流またはビット線をハイインピーダンスにしたときの電位をセンスアンプにて読み出す。さらにこのとき、非選択セルのキャパシタには、読み出し時のクロストークを防ぐため、所定の電圧が印加される。

【0031】

書き込み動作においては、‘1’の書き込みの場合は、選択セルのキャパシタに「−V0」の電圧が印加される。‘0’の書き込みの場合は、選択セルのキャパシタに、該選択セルの分極を反転させない電圧が印加され、読み出し動作時に書き込まれた‘0’状態を保持する。このとき、非選択セルのキャパシタには、書き込み時のクロストークを防ぐため、所定の電圧が印加される。

【0032】

(デバイスの製造方法)

次に、上述した強誘電体メモリ装置1000の製造方法の一例について述べる。図5および図6は、強誘電体メモリ装置1000の製造工程を模式的に示す断面図である。

【0033】

(1)第1信号電極の形成工程

まず、図5に示すように、基体10上に、所定パターンで配列する第1信号電極(下電極)12を形成する。第1信号電極12の形成方法は、例えば、基体10上に第1信号電極12を形成するための電極材料を成膜し、成膜された電極材料をパターニングする。

【0034】

電極材料は、強誘電体キャパシタの一部となるための機能を有するものであれば特に限定されるものではない。例えば、強誘電体層14を構成する材料としてPZTを用いる場合には、第1信号電極12を構成する電極材料として、白金、イリジウムおよびその化合物等を用いることができる。第1信号電極12の材質としては、たとえばIr,IrOx,Pt,RuOx,SrRuOx,LaSrCoOxを挙げることができる。また、第1信号電極12は、単層または複数の層を積層したものを用いることができる。

【0035】

電極材料の成膜方法としては、スパッタリング、真空蒸着、CVD等の方法が利用できる。パターニング方法としては、リソグラフィ技術を利用することができる。成膜された電極材料を選択的に除去する方法としては、RIE、スパッタエッチング、プラズマエッチングなどのエッチング方法を用いることができる。

【0036】

電極材料の形成方法としては、上記エッチングによるパターニングを用いずに、第2の実施の形態で述べる表面修飾層を用いた方法(第2の実施の形態における(デバイスの製造方法)の欄の工程(1)、(2)参照)を用いることもできる。

【0037】

(2)強誘電体層の成膜工程

図5に示すように、所定パターンの第1信号電極12が形成された基体10上に、強誘電体からなる連続層140(以下、これを「強誘電体層140」という)を全面的に形成する。強誘電体層140の成形方法としては、たとえば、ゾルゲル材料やMOD(Metal Organic Decomposition)材料を用いたスピンコート法やディッピング法、スパッタ法、MOCVD(Metal Organic Chemical Vapor Deposition)法、レーザアブレーション法を挙げることができる。

【0038】

強誘電体層の材質としては、強誘電性を示してキャパシタ絶縁層として使用できれば、その組成は任意のものを適用することができる。このような強誘電体としては、たとえばPZT(PbZrzTi1-zO3)、SBT(SrBi2Ta2O9)を挙げることができ、さらに、これらの材料にニオブやニッケル、マグネシウム等の金属を添加したもの等が適用できる。強誘電体としては、具体的には、チタン酸鉛(PbTiO3)、ジルコン酸チタン酸鉛(Pb(Zr,Ti)O3)、ジルコン酸鉛(PbZrO3)、チタン酸鉛ランタン((Pb,La),TiO3)、ジルコン酸チタン酸鉛ランタン((Pb,La)(Zr,Ti)O3)またはマグネシウムニオブ酸ジルコニウムチタン酸鉛(Pb(Zr,Ti)(Mg,Nb)O3)等を使用することができる。

【0039】

上述した強誘電体の材料としては、例えばPZTの場合、PbについてはPb(C2H5)4、(C2H5)3PbOCH2C(CH3)3、Pb(C11H19O2)2等を、Zrについては、Zr(n−OC4H9)4、Zr(t−OC4H9)4、Zr(C11H19O2)4、Zr(C11H19O2)4等を、TiについてはTi(i−C3H7)4等を用いることができ、SBTの場合、SrについてはSr(C11H10O2)2等を、BiについてはBi(C6H5)3等を、TaについてはTa(OC2H5)5等を用いることができる。

【0040】

(3)第2信号電極の形成工程

図5に示すように、強誘電体層140上に、所定パターンの第2信号電極(上部電極)16を形成する。その形成方法は、例えば、強誘電体層140上に第2信号電極16を形成するための電極材料を成膜し、成膜された電極材料をパターニングする。具体的には、成膜された電極材料層上に所定パターンのレジスト層30を形成し、このレジスト層30をマスクとして電極材料層を選択的にエッチングすることで、第2信号電極16が形成される。

【0041】

第2信号電極16の材料、成膜方法、リソグラフィーを用いたパターニング方法については、前述した工程(1)の第1信号電極12の形成工程と同様であるので、記載を省略する。

【0042】

(4)強誘電体層のパターニング工程

図5および図6に示すように、レジスト層30をマスクとして、さらに強誘電体層140を選択的に除去して強誘電体層14をパターニングする。成膜された強誘電体材料を選択的に除去する方法としては、RIE、スパッタエッチング、プラズマエッチングなどのエッチング方法を用いることができる。その後、レジスト層30を公知の方法、例えば溶解あるいはアッシングによって除去する。

【0043】

(5)誘電体層の形成工程

図4に示すように、強誘電体層14と第2信号電極16とからなる積層体の相互間に、誘電体層18を形成する。誘電体層18の形成方法としては、CVD、特にMOCVDなどの気相法、あるいはスピンコート法やディップ法等の液相を用いた方法を用いることができる。

【0044】

誘電体層18は、前述したように、強誘電体キャパシタを構成する強誘電体層14より小さな誘電率を有する誘電体材料を用いることが好ましい。たとえば、強誘電体層としてPZT材料を用いた場合には、誘電体層18の材料としては、たとえばSiO2,Ta2O5,SrTiO3,MgOなどの無機材料あるいはポリイミドなどの有機材料を用いることができ、強誘電体層14としてSBTを用いた場合には、誘電体層18の材料として、SiO2,Ta2O5,SrTiO3,SrTa2O6,SrSnO3などの無機材料あるいはポリイミドなどの有機材料を用いることができる。

【0045】

以上の工程によって、メモリセルアレイ100Aが形成される。この製造方法によれば、強誘電体キャパシタ20を構成する強誘電体層14は、第2信号電極16のパターニングで用いたレジスト層30をマスクとして連続的にパターニングされるので、工程数を少なくできる。さらにこの場合、各層を別々のマスクでパターニングする場合に比べて、1つのマスクの合わせ余裕が不要となるので、メモリセルアレイの高集積化も可能となる。

【0046】

[第2の実施の形態]

図7は、本実施の形態に係る強誘電体キャパシタを有するメモリセルアレイの要部を模式的に示す平面図であり、図8は、図7のB−B線に沿った断面図である。

【0047】

本実施の形態において、第1の実施の形態のメモリセルアレイと実質的に同じ機能を有する部材には同一の符号を付して説明する。

【0048】

本実施の形態は、強誘電体キャパシタを構成する強誘電体層が第1信号電極(下電極)上にライン状に積層されて形成されている点で、第1の実施の形態と異なる。

【0049】

本実施の形態に係るメモリセルアレイ100Bは、絶縁性の基体10上に、第1信号電極12、強誘電体キャパシタを構成する第1強誘電体層14および第2信号電極16が積層されている。そして、第1信号電極12,強誘電体層14および第2信号電極16によって強誘電体キャパシタ20が構成される。すなわち、第1信号電極12と第2信号電極16との交差領域において、それぞれ強誘電体キャパシタ20からなるメモリセルが構成されている。

【0050】

第1信号電極12および第2信号電極16は、図7に示すように、X方向およびY方向にそれぞれ所定のピッチで配列されている。

【0051】

強誘電体層14は、第1信号電極12上に選択的に形成されている。また、基体10上において、第1信号電極12の相互間には、後に詳述する表面修飾層22が配置されている。この表面修飾層22上には誘電体層18が形成されている。この誘電体層18は、強誘電体層14に比べて小さい誘電率を有することが望ましい。このように第1信号電極12および強誘電体層14からなる積層体の相互間に、強誘電体層14より誘電率の小さい誘電体層18を介在させることにより、第2信号電極16の浮遊容量を小さくすることができる。その結果、強誘電体メモリ装置における書き込みおよび読み出しの動作をより高速に行うことが可能となる。

【0052】

(デバイスの製造方法)

図9〜図12は、本実施の形態に係るメモリセルアレイ100Bの製造工程を模式的に示す断面図である。

【0053】

(1)表面修飾層の形成

まず、基体10の表面特性に選択性を付与する工程を行う。ここで、基体10の表面特性に選択性を付与するとは、基体10の表面の、当該表面に堆積させるための材料に対してぬれ性等の表面特性の異なる領域を形成することである。

【0054】

本実施の形態において、図9に示すように、具体的には、基体10の表面に、強誘電体キャパシタを構成する部材を形成するための材料、特に電極を形成するための材料に対して親和性を有する第1の領域24と、第1の領域24よりも強誘電体キャパシタを構成する部材を形成するための材料、特に電極を形成するための材料に対して親和性の小さい第2の領域26と、を形成する。そして、後続の工程で、この表面特性の差を利用し、各領域間での材料の堆積速度や基体との密着性における選択性により、第1の領域24には、強誘電体キャパシタが選択的に形成される。

【0055】

すなわち、後続の工程で、強誘電体キャパシタの第1信号電極12および強誘電体層14の少なくとも一つを、例えば化学的気相成長法(CVD法)、物理的気相成長法または液相法を適用して、第1の領域24に選択的な堆積プロセスで形成することができる。この場合であって、例えば基体10の表面が、強誘電体キャパシタを構成する部材を形成するための材料が堆積され易い性質を有する場合には、第1の領域24では表面を露出させ、第2の領域26では上記材料が堆積されにくい表面修飾層22を形成し、強誘電体キャパシタを構成する部材を形成するための材料の堆積に対する選択性を付与することができる。

【0056】

本実施の形態では、基体10の表面の全面に表面修飾層を形成してから、図9に示すように、第1の領域24で表面修飾層を除去して、第2の領域26に表面修飾層22を残す。詳しくは、次の工程を行う。

【0057】

表面修飾層22は、CVD等の気相成長法によって形成してもよいし、スピンコート法やディップ法等の液相を用いた方法によって形成してもよく、その場合には液体または溶媒に溶かした物質を使用する。このような物質としては、例えば、シランカップリング剤(有機ケイ素化合物)やチオール化合物を使用することができる。

【0058】

ここで、チオール化合物とは、メルカプト基(−SH)を持つ有機化合物(R1−SH;R1はアルキル基等の置換可能な炭化水素基)の総称をいう。このようなチオール化合物を、例えば、ジクロロメタン、トリクロロメタン等の有機溶剤に溶かして0.1〜10mM程度の溶液とする。

【0059】

また、シランカップリング剤とは、R2 nSiX4-n(nは自然数、R2は水素、アルキル基等の置換可能な炭化水素基)で表される化合物であり、Xは−OR3、−COOH、−OOCR3、−NH3-nR3n、−OCN、ハロゲン等である(R3はアルキル基等の置換可能な炭化水素基)。これらシランカップリング剤およびチオール化合物の中で、特にR1やR3がCnF2n+1CmH2m(n、mは自然数)であるようなフッ素原子を有する化合物は、表面自由エネルギーが高くなり他材料との親和性が小さくなるため、好適に用いられる。

【0060】

または、メルカプト基や−COOH基を有する化合物による上述した方法で得られる膜を用いることもできる。以上の材料による膜は、適切な方法により単分子膜やその累積膜の形で用いることができる。

【0061】

本実施の形態では、図9に示すように、第1の領域24では、表面修飾層が形成されない。表面修飾層22として例えばシランカップリング剤を使用した場合、光を当てることで、基体10との界面で、分子の結合が切れて除去される場合がある。このような光によるパターニングには、リソグラフィで行われるマスク露光を適用することができる。あるいは、マスクを使用せずに、レーザ、電子線またはイオンビームなどによって直接的にパターニングしてもよい。

【0062】

なお、表面修飾層22自体を他の基体上に形成し、これを転写することにより第2の領域26に表面修飾層22を選択的に形成し、成膜と同時にパターニングすることもできる。

【0063】

こうして、図9に示すように、第1の領域24と、表面修飾層22で被覆された状態となっている第2の領域26との間で、表面状態が異なるようにして、後続の工程における強誘電体キャパシタを構成する部材を形成するための材料との親和性に差を生じさせることができる。特に、表面修飾層22が、フッ素分子を有するなどの理由で、撥水性を有していれば、例えば強誘電体キャパシタを構成する部材の材料を液相にて提供する場合に、第1の領域24に選択的に当該材料を付与することができる。また、表面修飾層22の材料によっては、これが存在しない第1の領域24では、上層の部材を形成するための材料との親和性で気相法による成膜がされるようにすることができる。このように、第1の領域24と第2の領域26の表面の性質に選択性を付与し、後続の工程で、強誘電体メモリ装置の強誘電体キャパシタの部材(本実施の形態では第1信号電極12および強誘電体層14)を形成することができる。

【0064】

(2)第1信号電極の形成工程

図10に示すように、強誘電体キャパシタの下部電極となる第1信号電極12を、第1の領域24に対応して形成する。例えば、基体10の表面の全体に対して、気相法による成膜工程を行う。こうすることで、選択堆積プロセスが行われる。すなわち、第1の領域24では成膜がされ、第2の領域26では成膜がされにくいので、第1の領域24のみに第1信号電極12が形成される。ここで、気相法としてCVD、特にMOCVDを適用することが好ましい。第2の領域26では、全く成膜されないことが好ましいが、第1の領域24での成膜よりも、成膜スピードにおいて2桁以上遅ければよい。

【0065】

また、第1信号電極12の形成には、その材料の溶液を液相の状態で第1の領域24に選択的に供給する方法、またはその材料の溶液を超音波等によりミスト化して第1の領域24に選択的に供給するミストデポジション法を採用することもできる。

【0066】

第1信号電極12を構成する材料としては、第1の実施の形態で述べたと同様に、例えば白金、イリジウム等を用いることができる。基体10上に第1の領域24と、前述したような材料を含む表面修飾層22(第2の領域26)とを形成し、表面特性の選択性を形成した場合、白金については、例えば(C5H7O2)2Pt、(C5HFO2)2Pt、(C3H5)(C5H5)Ptを電極を形成するための材料として、イリジウムについては、例えば(C3H5)3Irを電極を形成するための材料として用いて、選択的に堆積させることができる。

【0067】

(3)強誘電体層の形成工程

図11に示すように、第1信号電極12上に強誘電体層14を形成する。詳しくは、基体10の表面の全体に対して、例えば気相法による成膜工程を行う。こうすることで、第1信号電極12上では成膜がされ、第2の領域26では成膜がされにくいので、第1信号電極12上のみに強誘電体層14が形成される。ここで、気相法としてCVD、特にMOCVDを適用することができる。

【0068】

また、強誘電体層14の形成には、その材料の溶液を液相の状態で第2の領域26以外の領域に形成された第1信号電極12上にインクジェット法等で選択的に供給する方法、またはその材料の溶液を超音波等によりミスト化して第2の領域26以外の部分に選択的に供給するミストデポジション法を採用することもできる。

【0069】

強誘電体層14としては、強誘電性を示してキャパシタ絶縁層として使用できれば、その組成は任意のものを適用することができる。例えば、SBT系材料、PZT系材料の他、ニオブや酸化ニッケル、酸化マグネシウム等の金属酸化物を添加したもの等が適用できる。強誘電体の具体例としては、第1の実施の形態で述べたものと同様のものを例示できる。さらに、強誘電体の材料の具体例としては、第1の実施の形態で述べたものと同様のものを例示できる。

【0070】

(4)誘電体層の形成工程

図12に示すように、第2の領域26上に、すなわち、第1の領域24に形成された、第1信号電極12と強誘電体層14とからなる積層体の相互間の領域に、誘電体層18を形成する。誘電体層18の形成方法としては、CVD、特にMOCVDなどの気相法、あるいはスピンコート法やディップ法等の液相を用いた方法を用いることができる。誘電体層18は、たとえばCMP(Chemical Mechanical Polishing)法などによって、強誘電体層14と同一レベルの表面を有するように平坦化されることが好ましい。このように誘電体層18を平坦化することにより、第2信号電極16の形成が容易かつ正確に行われる。

【0071】

誘電体層18は、強誘電体キャパシタを構成する強誘電体層14より小さな誘電率を有する誘電体材料を用いることが好ましい。たとえば、強誘電体層としてPZT材料を用いた場合には、誘電体層18の材料としては、たとえばSiO2,Ta2O5,SrTiO3,MgOなどの無機材料あるいはポリイミドなどの有機材料を用いることができ、強誘電体層14としてSBTを用いた場合には、誘電体層18の材料として、SiO2,Ta2O5,SrTiO3,SrTa2O6,SrSnO3などの無機材料あるいはポリイミドなどの有機材料を用いることができる。

【0072】

(5)第2信号電極の形成工程

図8に示すように、強誘電体層14および誘電体層18上に所定パターンの第2信号電極(上部電極)16を形成する。その形成方法は、例えば、強誘電体層14および誘電体層18上に第2信号電極16を形成するための電極材料を成膜し、成膜された電極材料をパターニングする。

【0073】

電極材料は、強誘電体キャパシタの一部となるための機能を有するものであれば特に限定されるものではない。例えば、強誘電体層14を構成する材料としてPZTを用いる場合には、第1の実施の形態と同様に、第2信号電極16を構成する電極材料として、白金、イリジウムおよびその化合物等を用いることができる。第2信号電極16は、単層または複数の層を積層したものを用いることができる。

【0074】

電極材料の成膜方法としては、第1の実施の形態と同様に、スパッタリング、真空蒸着、CVD等の方法が利用できる。パターニング方法としては、リソグラフィ技術を利用することができる。

【0075】

さらに、必要に応じて、強誘電体層14、誘電体層18および第2信号電極16の表面に絶縁性の保護層を全体的に形成する。このようにして、本実施の形態に係るメモリセルアレイ100Bを形成することができる。

【0076】

本実施の形態の製造方法によれば、第1の領域24には強誘電体キャパシタを構成する少なくとも一部材を選択的に形成することができ、第2の領域26にはこれが形成されにくい。こうして、エッチングを行うことなく、第1信号電極(下電極)および強誘電体層の少なくとも1つ(本実施の形態では第1信号電極12および強誘電体層14)を形成することができる。この方法によれば、第1信号電極のパターニングとしてスパッタエッチングを用いた場合のように、エッチングにより生ずる二次生成物に起因する再付着物の問題を回避することができる。

【0077】

本実施の形態の製造方法においては、図11に示す工程の後に、第2の領域26上で、表面修飾層22を除去してもよい。この工程は、第1信号電極12および強誘電体層14の成膜工程が完了してから行う。例えば、表面修飾層のパターニング工程で説明した方法で、表面修飾層22を除去することができる。表面修飾層22を除去するときに、その上に付着した物質も除去することが好ましい。例えば、表面修飾層22上に、第1信号電極12または強誘電体層14の材料が付着したときに、これらを除去してもよい。なお、表面修飾層22を除去する工程は、本発明の必須要件ではなく、表面修飾層22を残してもよい。

【0078】

また、第1信号電極12の側面に強誘電体層14が形成されている場合には、これらを除去することが好ましい。除去工程では、例えば、ドライエッチングを適用することができる。

【0079】

上記実施の形態では、表面修飾層22を第2の領域26に形成し、第1の領域24および第2の領域26の表面のそれぞれを、続いて形成される強誘電体キャパシタの少なくとも一部材(第1信号電極および強誘電体層の少なくとも一方)を形成するための材料の堆積性、すなわち堆積され易さが異なるような表面特性にした。その変形例として、表面修飾層22を第1の領域24に形成し、強誘電体キャパシタの少なくとも一部材を形成するための材料を表面修飾層22の表面に対して優先的に堆積されるように液相または気相の組成に調製して、第1の領域24に選択的に強誘電体キャパシタを形成してもよい。

【0080】

また、例えば第2の領域26の表面に前述したような表面修飾層の薄い層を選択的に形成し、第1の領域24および第2の領域26を含む全面に強誘電体キャパシタの少なくとも一部材を形成するための材料を気相または液相で供給し、全面に当該部材の材料の層を形成し、ポリッシングや化学的な手法で表面修飾膜の薄い層上の当該部材の材料層のみを選択的に除去し、第1の領域24上に選択的に当該部材の材料層を得ることもできる。

【0081】

その他、第1の領域24および第2の領域26の表面のそれぞれには、特に明確に層を設けず、選択的に表面処理を行い、第1の領域24上に強誘電体キャパシタの少なくとも一部材を形成するための材料が優先的に堆積されるようにしてもよい。

【0082】

本実施の形態で特徴とする、表面修飾層を用いた第1信号電極(下電極)および強誘電体層の形成については、本願出願人による特許協力条約に基づく国際出願(出願番号PCT/JP00/03590)に記載されている。

【0083】

[第3の実施の形態]

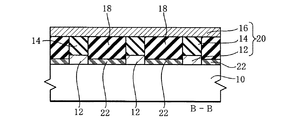

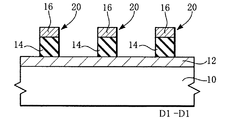

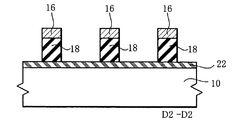

図13は、本実施の形態に係る強誘電体キャパシタを有するメモリセルアレイの要部を模式的に示す平面図であり、図14は、図13のC−C線に沿った断面図であり、図15は、図13のD1−D1線に沿った断面図であり、図16は、図13のD2−D2線に沿った断面図である。

【0084】

本実施の形態において、第1の実施の形態のメモリセルアレイと実質的に同じ機能を有する部材には同一の符号を付して説明する。

【0085】

本実施の形態は、強誘電体キャパシタを構成する強誘電体層が第1信号電極と第2信号電極との交差領域にのみ形成されている点で、第1および第2の実施の形態と異なる。

【0086】

本実施の形態に係るメモリセルアレイ100Cは、絶縁性の基体10上に、第1信号電極12、強誘電体キャパシタを構成する強誘電体層14および第2信号電極16が積層されている。そして、第1信号電極12,強誘電体層14および第2信号電極16によって強誘電体キャパシタ20が構成される。すなわち、第1信号電極12と第2信号電極16との交差領域において、それぞれ強誘電体キャパシタ20からなるメモリセルが構成されている。第1信号電極12および第2信号電極16は、図13に示すように、X方向およびY方向にそれぞれ所定のピッチで配列されている。

【0087】

強誘電体層14は、第1信号電極12および第2信号電極16の交差領域にのみ選択的に形成されている。図14に示すように、第2信号電極16に沿ってみると、基体10上において、第1信号電極12上に強誘電体層14および第2信号電極16が積層され、さらに、第1信号電極12の相互間には表面修飾層22が配置され、この表面修飾層22上には誘電体層18が形成されている。また、図15に示すように、第1信号電極12に沿ってみると、第1信号電極12の所定位置において、強誘電体層14と第2信号電極16とが積層されている。そして、強誘電体層14および第2信号電極16の積層体の相互間には何もない状態である。図15に示すように、第1信号電極12上に沿ってみると、第1信号電極12の所定位置において、強誘電体層14と第2信号電極16とが積層されている。図16に示すように、X方向であって第1信号電極12が形成されていない部分についてみると、表面修飾層22上の所定位置において、誘電体層18と第2信号電極16とが積層されている。そして、強誘電体層14および第2信号電極16の積層体の相互間、ならびに誘電体層18および第2信号電極16の積層体の相互間には、必要に応じて誘電体層を形成することができる。

【0088】

誘電体層18ならびに必要に応じて形成される上記誘電体層は、強誘電体層14に比べて小さい誘電率を有することが望ましい。このように第1信号電極12および強誘電体層14からなる積層体の相互間、あるいは強誘電体層14および第2信号電極16からなる積層体の相互間に、強誘電体層14より誘電率の小さい誘電体層を介在させることにより、第1信号電極12および第2信号電極16の浮遊容量を小さくすることができる。その結果、強誘電体メモリ装置における書き込みおよび読み出しの動作をより高速に行うことが可能となる。

【0089】

また、本実施の形態では、強誘電体キャパシタ20を構成する強誘電体層14は、第1信号電極12と第2信号電極16との交差領域にのみ形成されている。このような構造によれば、第1信号電極12および第2信号電極16双方の浮遊容量を小さくすることができる点で有利である。

【0090】

(デバイスの製造方法)

図17〜図24は、本実施の形態に係るメモリセルアレイ100Cの製造工程を模式的に示す断面図である。

【0091】

(1)表面修飾層の形成

まず、基体10の表面特性に選択性を付与する工程を行う。ここで、基体10の表面特性に選択性を付与するとは、基体10の表面の、当該表面に堆積させるための材料に対してぬれ性等の表面特性の異なる領域を形成することである。この点については第2の実施の形態で詳細に説明したので、簡単に説明する。

【0092】

本実施の形態において、図9に示すように、具体的には、基体10の表面に、強誘電体キャパシタを構成する部材を形成するための材料、特に電極を形成するための材料に対して親和性を有する第1の領域24と、第1の領域24よりも強誘電体キャパシタを構成する部材を形成するための材料、特に電極を形成するための材料に対して親和性の小さい第2の領域26と、を形成する。そして、後続の工程で、この表面特性の差を利用し、各領域間での材料の堆積速度や基体との密着性における選択性により、第1の領域24には、強誘電体キャパシタが選択的に形成される。

【0093】

すなわち、例えば基体10の表面が、強誘電体キャパシタを構成する部材を形成するための材料が堆積され易い性質を有する場合には、第1の領域24では表面を露出させ、第2の領域26では上記材料が堆積されにくい表面修飾層22を形成し、強誘電体キャパシタを構成する部材を形成するための材料の堆積に対する選択性を付与することができる。

【0094】

本実施の形態では、基体10の表面の全面に表面修飾層を形成してから、図18に示すように、第1の領域24で表面修飾層を除去して、第2の領域26に表面修飾層22を残す。表面修飾層22の形成方法については、第2の実施の形態で述べた方法と同様の方法を採用できる。

【0095】

(2)第1信号電極の形成工程

図19に示すように、強誘電体キャパシタの下部電極となる第1信号電極12を、第1の領域24に対応して形成する。第1信号電極12の形成方法および電極材料については、第2の実施の形態で述べた方法および材料と同様のものを採用できる。

【0096】

(3)強誘電体層の形成工程

図20に示すように、第1信号電極12上に強誘電体層140を形成する。詳しくは、基体10の表面の全体に対して、例えば気相法による成膜工程を行う。こうすることで、第1信号電極12上では成膜がされ、第2の領域26では成膜がされにくいので、第1信号電極12上のみに強誘電体層140が形成される。強誘電体層140の成膜方法としては、第2の実施の形態で述べたと同様の方法を採用できる。

【0097】

強誘電体層14としては、強誘電性を示してキャパシタ絶縁層として使用できれば、その組成は任意のものを適用することができる。例えば、SBT系材料、PZT系材料の他、ニオブやニッケル、マグネシウム等の金属を添加したもの等が適用できる。強誘電体の具体例としては、第1の実施の形態で述べたものと同様のものを例示できる。さらに、強誘電体の材料の具体例としては、第1の実施の形態で述べたものと同様のものを例示できる。

【0098】

(4)誘電体層の形成工程

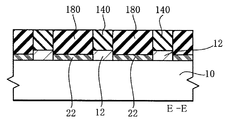

図17および図21に示すように、第2の領域26上に、すなわち、第1の領域24に形成された、第1信号電極12と強誘電体層14とからなる積層体の相互間の領域に、誘電体層180を形成する。図21は、図17のE−E線に沿った断面図である。

【0099】

誘電体層180の形成方法としては、第1の実施の形態で述べたと同様の方法を採用できる。さらに、誘電体層180は、たとえばCMP法などによって、強誘電体層140と同一レベルの表面を有するように平坦化されることが好ましい。このように誘電体層180を平坦化することにより、第2信号電極16の形成が容易かつ正確に行われる。

【0100】

誘電体層180は、強誘電体キャパシタを構成する強誘電体層14より小さな誘電率を有する誘電体材料を用いることが好ましい。たとえば、強誘電体層としてPZT材料を用いた場合には、誘電体層180の材料としては、たとえばSiO2,Ta2O5,SrTiO3,MgOなどの無機材料あるいはポリイミドなどの有機材料を用いることができ、強誘電体層14としてSBTを用いた場合には、誘電体層180の材料として、SiO2,Ta2O5,SrTiO3,SrTa2O6,SrSnO3などの無機材料あるいはポリイミドなどの有機材料を用いることができる。

【0101】

以上の工程(1)〜(4)によって、第1の領域24に第1信号電極12および強誘電体層140が積層され、第2の領域26に表面修飾層22および誘電体層180が積層される。

【0102】

(5)第2信号電極の形成工程

図22〜図24に示すように、強誘電体層140および誘電体層180上に所定パターンの第2信号電極(上部電極)16を形成する。その形成方法は、例えば、強誘電体層140および誘電体層180上に、第2信号電極16を形成するための電極材料を成膜し、成膜された電極材料をパターニングする。

【0103】

電極材料は、強誘電体キャパシタの一部となるための機能を有するものであれば特に限定されるものではない。強誘電体層140を構成する材料としては、第1の実施の形態で述べたと同様なものを採用できる。また、電極材料の成膜方法としては、第1の実施の形態と同様に、スパッタリング、真空蒸着、CVD等の方法が利用でき、パターニング方法としては、リソグラフィ技術を利用することができる。

【0104】

例えば、第1の実施の形態と同様に、図示しないレジスト層を第2信号電極16のための電極材料層上に形成し、これをマスクとしてエッチングを行うことで、第2信号電極16をパターニングできる。

【0105】

(6)強誘電体層のパターニング工程

図15および図16に示すように、図示しないレジスト層をマスクとして、さらに強誘電体層140を選択的に除去して強誘電体層14をパターニングする。成膜された強誘電体材料を選択的に除去する方法としては、第1の実施の形態と同様に、RIE、スパッタエッチング、プラズマエッチングなどのエッチング方法を用いることができる。その後、レジスト層を公知の方法、例えば溶解あるいはアッシングによって除去する。

【0106】

(7)誘電体層の形成工程

さらに、必要に応じて、強誘電体層14と第2信号電極16とからなる積層体の相互間、ならびに表面修飾層22と第2信号電極16とからなる積層体の相互間に、図示しない誘電体層を形成する。誘電体層の形成方法としては、工程(4)の誘電体層180と同様の方法を用いることができる。

【0107】

以上の工程によって、メモリセルアレイ100Cが形成される。この製造方法によれば、第1の実施の形態および第2の実施の形態での利点を有する。すなわち、エッチングを行うことなく、第1信号電極(下電極)および強誘電体層の少なくとも1つ(本実施の形態では第1信号電極12および強誘電体層14)を形成することができる。したがって、第1信号電極のパターニングとしてスパッタエッチングを用いた場合のように、エッチングにより生ずる二次生成物に起因する再付着物の問題を回避することができる。また、第2信号電極16のパターニングで用いたレジスト層をマスクとして連続的にパターニングされるので、工程数を少なくできる。さらにこの場合、各層を別々のマスクでパターニングする場合に比べて、1つのマスクの合わせ余裕が不要となるので、メモリセルアレイの高集積化も可能となる。

【0108】

以上、強誘電体キャパシタの存在しない領域に誘電体層18または180を形成する例を示してきたが、もちろん、本発明は、誘電体層18または180を設けない構成にも適用できる。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態にかかるメモリセルアレイを模式的にしめす平面図である。

【図2】本発明の第1の実施の形態にかかる強誘電体メモリ装置を示す図である。

【図3】図1に示すメモリセルアレイの要部を拡大して示す平面図である。

【図4】図3のA−A線に沿った断面図である。

【図5】本発明の第1の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示す断面図である。

【図6】本発明の第1の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示す断面図である。

【図7】本発明の第2の実施の形態にかかるメモリセルアレイを模式的にしめす平面図である。

【図8】図7のB−B線に沿った断面図である。

【図9】本発明の第2の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示す断面図である。

【図10】本発明の第2の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示す断面図である。

【図11】本発明の第2の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示す断面図である。

【図12】本発明の第2の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示す断面図である。

【図13】本発明の第3の実施の形態にかかるメモリセルアレイを模式的にしめす平面図である。

【図14】図13のC−C線に沿った断面図である。

【図15】図13のD1−D1線に沿った断面図である。

【図16】図13のD2−D2線に沿った断面図である。

【図17】本発明の第3の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的にしめす平面図である。

【図18】本発明の第3の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示す断面図である。

【図19】本発明の第3の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示す断面図である。

【図20】本発明の第3の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示す断面図である。

【図21】本発明の第3の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示し、図17のE−E線に沿った断面図である。

【図22】本発明の第3の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示す平面図である。

【図23】本発明の第3の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示し、図22のF1−F1線に沿った断面図である。

【図24】本発明の第3の実施の形態にかかるメモリセルアレイの製造方法の一工程を模式的に示し、図22のF2−F2線に沿った断面図である。

【符号の説明】

10 基体

12 第1信号電極

14,140 強誘電体層

16 第2信号電極

18,180 誘電体層

20 強誘電体キャパシタ

22 表面修飾層

24 第1の領域

26 第2の領域

30 レジスト層

50 第1駆動回路

52 第2駆動回路

100A,100B,100C メモリセルアレイ

1000 強誘電体メモリ装置

Claims (3)

- 基体上に、強誘電体キャパシタからなるメモリセルがマトリクス状に配列され、

前記強誘電体キャパシタは、前記基体上に形成された第1信号電極と、該第1信号電極と交差する方向に配列された第2信号電極と、少なくとも前記第1信号電極と前記第2信号電極との交差領域に配置された強誘電体層と、を含み、

前記基体上に、該基体の表面と異なる表面特性を有する表面修飾層が形成され、該表面修飾層は、前記第1信号電極の相互間に配置され、該表面修飾層の表面が前記第1信号電極を構成する材料に対して前記基体の表面より低い親和性を有する、メモリセルアレイ。 - 請求項1において、

前記強誘電体層は、前記第1信号電極と前記第2信号電極との交差領域のみにブロック状に配置された、メモリセルアレイ。 - 強誘電体キャパシタからなるメモリセルがマトリクス状に配列されたメモリセルアレイの製造方法であって、

基体上に、第1信号電極を形成するための材料が優先的に堆積される表面特性を有する第1の領域と、前記第1の領域に比較して前記第1信号電極を形成するための材料が堆積され難い表面特性を有する第2の領域と、を形成する工程であって、前記第1の領域では、前記基体の表面を露出させ、前記第2の領域では、前記第1信号電極の材料に対する親和性が、前記基体の第1の領域での露出面より低い表面特性を有する表面修飾層を形成する工程、

前記第1信号電極を形成するための材料を付与し、前記第1の領域に該第1信号電極を選択的に形成する工程、

前記第1信号電極上に、該第1信号電極に沿ってライン状に強誘電体層を形成する工程、

前記第1信号電極と交差する方向に第2信号電極を形成する工程、および

前記強誘電体層をさらにパターニングして、前記第1信号電極と前記第2信号電極との交差領域のみにブロック状に強誘電体層を形成する工程、

を含む、メモリセルアレイの製造方法。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000251436A JP3901432B2 (ja) | 2000-08-22 | 2000-08-22 | 強誘電体キャパシタを有するメモリセルアレイおよびその製造方法 |

| US09/931,915 US6617627B2 (en) | 2000-08-22 | 2001-08-20 | Memory cell array having ferroelectric capacitors, method of fabricating the same, and ferroelectric memory device. |

| CN01802501.3A CN1246905C (zh) | 2000-08-22 | 2001-08-21 | 存储单元阵列及其制造方法以及强电介质存储装置 |

| PCT/JP2001/007143 WO2002017403A1 (fr) | 2000-08-22 | 2001-08-21 | Reseau de cellules memoire a condensateur ferroelectrique, son procede de fabrication, et dispositif a memoire ferroelectrique |

| EP01958382A EP1263049A4 (en) | 2000-08-22 | 2001-08-21 | FERROELECTRIC CAPACITOR MEMORY CELL ARRAY, METHOD FOR MANUFACTURING THE SAME, AND FERROELECTRIC MEMORY DEVICE |

| US10/618,688 US6913937B2 (en) | 2000-08-22 | 2003-07-15 | Memory cell array having ferroelectric capacity, method of manufacturing the same and ferroelectric memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000251436A JP3901432B2 (ja) | 2000-08-22 | 2000-08-22 | 強誘電体キャパシタを有するメモリセルアレイおよびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002064187A JP2002064187A (ja) | 2002-02-28 |

| JP2002064187A5 JP2002064187A5 (ja) | 2006-10-26 |

| JP3901432B2 true JP3901432B2 (ja) | 2007-04-04 |

Family

ID=18740844

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000251436A Expired - Fee Related JP3901432B2 (ja) | 2000-08-22 | 2000-08-22 | 強誘電体キャパシタを有するメモリセルアレイおよびその製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US6617627B2 (ja) |

| EP (1) | EP1263049A4 (ja) |

| JP (1) | JP3901432B2 (ja) |

| CN (1) | CN1246905C (ja) |

| WO (1) | WO2002017403A1 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3901432B2 (ja) * | 2000-08-22 | 2007-04-04 | セイコーエプソン株式会社 | 強誘電体キャパシタを有するメモリセルアレイおよびその製造方法 |

| US6858482B2 (en) * | 2002-04-10 | 2005-02-22 | Micron Technology, Inc. | Method of manufacture of programmable switching circuits and memory cells employing a glass layer |

| KR20060123376A (ko) * | 2003-12-22 | 2006-12-01 | 코닌클리즈케 필립스 일렉트로닉스 엔.브이. | 강유전성 중합체 층의 패턴화 방법 |

| US20050156217A1 (en) * | 2004-01-13 | 2005-07-21 | Matsushita Electric Industrial Co., Ltd. | Semiconductor memory device and method for fabricating the same |

| JP2005285190A (ja) * | 2004-03-29 | 2005-10-13 | Sanyo Electric Co Ltd | メモリ |

| JP2005327919A (ja) * | 2004-05-14 | 2005-11-24 | Seiko Epson Corp | デバイスの製造方法及びデバイス、電気光学素子、プリンタ |

| US7253502B2 (en) * | 2004-07-28 | 2007-08-07 | Endicott Interconnect Technologies, Inc. | Circuitized substrate with internal organic memory device, electrical assembly utilizing same, and information handling system utilizing same |

| DE102005017071B4 (de) | 2004-12-29 | 2011-09-15 | Hynix Semiconductor Inc. | Schwebe-Gate-Speichereinrichtung |

| NO322202B1 (no) * | 2004-12-30 | 2006-08-28 | Thin Film Electronics Asa | Fremgangsmate i fremstillingen av en elektronisk innretning |

| NO324539B1 (no) * | 2005-06-14 | 2007-11-19 | Thin Film Electronics Asa | Fremgangsmate i fabrikasjonen av en ferroelektrisk minneinnretning |

| GB2436893A (en) * | 2006-03-31 | 2007-10-10 | Seiko Epson Corp | Inkjet printing of cross point passive matrix devices |

| GB0809840D0 (en) * | 2008-05-30 | 2008-07-09 | Univ Catholique Louvain | Ferroelectric organic memories with ultra-low voltage operation |

| US8357582B2 (en) | 2010-11-01 | 2013-01-22 | Micron Technology, Inc. | Methods of forming electrical components and memory cells |

| TWI463641B (zh) * | 2012-02-24 | 2014-12-01 | Nat Applied Res Laboratories | Ultra - high density resistive memory structure and its manufacturing method |

| DE102020108366A1 (de) | 2020-03-26 | 2021-09-30 | Bayerische Motoren Werke Aktiengesellschaft | Informationsspeicher und Verfahren zum Programmieren und Auslesen von Informationen |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2788265B2 (ja) | 1988-07-08 | 1998-08-20 | オリンパス光学工業株式会社 | 強誘電体メモリ及びその駆動方法,製造方法 |

| US5530667A (en) * | 1991-03-01 | 1996-06-25 | Olympus Optical Co., Ltd. | Ferroelectric memory device |

| JP3480110B2 (ja) | 1995-03-15 | 2003-12-15 | ソニー株式会社 | 半導体メモリ及びその作製方法 |

| US5874364A (en) * | 1995-03-27 | 1999-02-23 | Fujitsu Limited | Thin film deposition method, capacitor device and method for fabricating the same, and semiconductor device and method for fabricating the same |

| JP3176840B2 (ja) * | 1996-03-15 | 2001-06-18 | 富士通株式会社 | 半導体装置の製造方法 |

| AU6774996A (en) * | 1995-08-18 | 1997-03-12 | President And Fellows Of Harvard College | Self-assembled monolayer directed patterning of surfaces |

| JPH0991970A (ja) | 1995-09-26 | 1997-04-04 | Olympus Optical Co Ltd | 非破壊型強誘電体メモリ及びその駆動方法 |

| JPH09102587A (ja) | 1995-10-05 | 1997-04-15 | Olympus Optical Co Ltd | 強誘電体薄膜素子 |

| TW322635B (ja) * | 1996-04-19 | 1997-12-11 | Matsushita Electron Co Ltd | |

| KR100370416B1 (ko) | 1996-10-31 | 2003-04-08 | 삼성전기주식회사 | 고밀도 데이터의 기록/재생을 위한 부호화/복호화 방법 및 그에 따른 장치 |

| KR100413805B1 (ko) * | 1996-10-31 | 2004-06-26 | 삼성전자주식회사 | 누설전류를이용한매트릭스형다진법강유전체랜덤액세서메모리 |

| NO309500B1 (no) | 1997-08-15 | 2001-02-05 | Thin Film Electronics Asa | Ferroelektrisk databehandlingsinnretning, fremgangsmåter til dens fremstilling og utlesing, samt bruk av samme |

| US6316801B1 (en) * | 1998-03-04 | 2001-11-13 | Nec Corporation | Semiconductor device having capacitive element structure and multilevel interconnection structure and method of fabricating the same |

| US5963466A (en) * | 1998-04-13 | 1999-10-05 | Radiant Technologies, Inc. | Ferroelectric memory having a common plate electrode |

| US6239028B1 (en) * | 1998-09-03 | 2001-05-29 | Micron Technology, Inc. | Methods for forming iridium-containing films on substrates |

| US6174735B1 (en) * | 1998-10-23 | 2001-01-16 | Ramtron International Corporation | Method of manufacturing ferroelectric memory device useful for preventing hydrogen line degradation |

| KR100457121B1 (ko) | 1999-06-04 | 2004-11-16 | 세이코 엡슨 가부시키가이샤 | 강유전체 메모리 소자 및 그 제조 방법 |

| JP3901432B2 (ja) * | 2000-08-22 | 2007-04-04 | セイコーエプソン株式会社 | 強誘電体キャパシタを有するメモリセルアレイおよびその製造方法 |

-

2000

- 2000-08-22 JP JP2000251436A patent/JP3901432B2/ja not_active Expired - Fee Related

-

2001

- 2001-08-20 US US09/931,915 patent/US6617627B2/en not_active Expired - Lifetime

- 2001-08-21 WO PCT/JP2001/007143 patent/WO2002017403A1/ja active Application Filing

- 2001-08-21 EP EP01958382A patent/EP1263049A4/en not_active Withdrawn

- 2001-08-21 CN CN01802501.3A patent/CN1246905C/zh not_active Expired - Fee Related

-

2003

- 2003-07-15 US US10/618,688 patent/US6913937B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US6617627B2 (en) | 2003-09-09 |

| JP2002064187A (ja) | 2002-02-28 |

| WO2002017403A1 (fr) | 2002-02-28 |

| US20020031005A1 (en) | 2002-03-14 |

| EP1263049A4 (en) | 2005-08-31 |

| CN1246905C (zh) | 2006-03-22 |

| EP1263049A1 (en) | 2002-12-04 |

| US20040014247A1 (en) | 2004-01-22 |

| CN1388990A (zh) | 2003-01-01 |

| US6913937B2 (en) | 2005-07-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3940883B2 (ja) | 強誘電体メモリ装置の製造方法 | |

| JP3901432B2 (ja) | 強誘電体キャパシタを有するメモリセルアレイおよびその製造方法 | |

| JP4045406B2 (ja) | 強誘電体メモリ素子及びその製造方法 | |

| JP2007103722A (ja) | キャパシタおよびその製造方法、強誘電体メモリ装置、アクチュエータ、並びに、液体噴射ヘッド | |

| JP2005327920A (ja) | デバイスの製造方法及びデバイス、電気光学素子 | |

| JP2002198496A (ja) | 強誘電体キャパシタおよびその製造方法ならびに強誘電体メモリ装置 | |

| JP4031619B2 (ja) | 強誘電体膜、強誘電体膜の製造方法、強誘電体キャパシタ、強誘電体キャパシタの製造方法、強誘電体メモリ装置、強誘電体メモリ装置の製造方法 | |

| JP3998916B2 (ja) | 強誘電体膜、強誘電体膜の製造方法、強誘電体キャパシタ、強誘電体キャパシタの製造方法、強誘電体メモリ装置および強誘電体メモリ装置の製造方法 | |

| JP4466876B2 (ja) | 強誘電体メモリ素子の製造方法 | |

| JP4400750B2 (ja) | 強誘電体メモリ素子の製造方法 | |

| JP2005510879A (ja) | 1つ以上のメモリ装置付きマトリクス・アドレッサブル機器 | |

| US20040173827A1 (en) | Memory cell array including ferroelectric capacitors, method for making the same, and ferroelectric memory device | |

| JP4038641B2 (ja) | 強誘電体メモリ素子の製造方法 | |

| JP4400749B2 (ja) | 強誘電体メモリ素子の製造方法 | |

| JP2007096346A (ja) | 強誘電体キャパシタおよびその製造方法 | |

| JP2001168293A (ja) | メモリデバイス及びその製造方法並びに電子機器 | |

| JP2003243626A (ja) | 強誘電体メモリ装置の製造方法 | |

| JP2010129962A (ja) | 半導体記憶装置およびその製造方法 | |

| JP2003243623A (ja) | 強誘電体キャパシタを有するメモリセルアレイおよびその製造方法ならびに強誘電体メモリ装置 | |

| JP2003282834A (ja) | キャパシタ、強誘電体メモリおよび電子機器 | |

| JP2003243624A (ja) | 強誘電体メモリ装置の製造方法 | |

| JP2004281537A (ja) | 強誘電体キャパシタとその製造方法および強誘電体キャパシタを含む強誘電体メモリ装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20051220 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060908 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061011 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061121 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061213 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061226 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 3901432 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100112 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110112 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110112 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120112 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120112 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130112 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130112 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140112 Year of fee payment: 7 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |