JP3892588B2 - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP3892588B2 JP3892588B2 JP18530298A JP18530298A JP3892588B2 JP 3892588 B2 JP3892588 B2 JP 3892588B2 JP 18530298 A JP18530298 A JP 18530298A JP 18530298 A JP18530298 A JP 18530298A JP 3892588 B2 JP3892588 B2 JP 3892588B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- gate electrode

- gate

- film

- source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 44

- 238000004519 manufacturing process Methods 0.000 title claims description 22

- 239000010410 layer Substances 0.000 claims description 74

- 239000000758 substrate Substances 0.000 claims description 74

- 238000009792 diffusion process Methods 0.000 claims description 69

- 238000000034 method Methods 0.000 claims description 57

- 239000011229 interlayer Substances 0.000 claims description 25

- 238000002955 isolation Methods 0.000 claims description 19

- 230000015572 biosynthetic process Effects 0.000 claims description 18

- 108091006146 Channels Proteins 0.000 description 90

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 42

- 229910052710 silicon Inorganic materials 0.000 description 40

- 239000010703 silicon Substances 0.000 description 40

- 239000012535 impurity Substances 0.000 description 33

- 230000000694 effects Effects 0.000 description 20

- 229910052751 metal Inorganic materials 0.000 description 16

- 239000002184 metal Substances 0.000 description 16

- 238000005468 ion implantation Methods 0.000 description 13

- 238000005530 etching Methods 0.000 description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 9

- 238000001020 plasma etching Methods 0.000 description 9

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 9

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 9

- 229910052681 coesite Inorganic materials 0.000 description 8

- 229910052906 cristobalite Inorganic materials 0.000 description 8

- 230000007423 decrease Effects 0.000 description 8

- 229920005591 polysilicon Polymers 0.000 description 8

- 239000000377 silicon dioxide Substances 0.000 description 8

- 229910052682 stishovite Inorganic materials 0.000 description 8

- 229910052905 tridymite Inorganic materials 0.000 description 8

- 238000010438 heat treatment Methods 0.000 description 7

- 239000000463 material Substances 0.000 description 7

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- 238000001994 activation Methods 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 4

- 238000009413 insulation Methods 0.000 description 4

- 238000001459 lithography Methods 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- 230000001133 acceleration Effects 0.000 description 3

- 230000004913 activation Effects 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 238000004151 rapid thermal annealing Methods 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 229910008479 TiSi2 Inorganic materials 0.000 description 2

- 229910008814 WSi2 Inorganic materials 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 239000012528 membrane Substances 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- -1 tungsten nitride Chemical class 0.000 description 2

- 230000005641 tunneling Effects 0.000 description 2

- 229910018182 Al—Cu Inorganic materials 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 108010075750 P-Type Calcium Channels Proteins 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 230000001154 acute effect Effects 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000000280 densification Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 230000001737 promoting effect Effects 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

Description

【発明の属する技術分野】

本発明は、ゲート電極の一部が基板に埋め込まれた、いわゆる溝型チャネル構造のMOSトランジスタを有する半導体装置およびその製造方法に関する。

【0002】

【従来の技術】

シリコン酸化膜(SiO2 膜)をゲート酸化膜として用いるMOSトランジスタにおいて、ゲート酸化膜の薄膜化はトランジスタのショートチャネル効果抑制を進める上で重要な役割を果たしている。しかし、ダイレクト・トンネリングが起こる膜厚よりゲート酸化膜を薄くすること(例えば3nm程度より薄い膜厚)は、トランジスタの信頼性上問題であると考えられている。

【0003】

また、従来のポリサイドゲート構造(ポリシリコン膜とシリサイド膜の積層構造)では、ゲート電極幅が微細化するに従ってゲート電極の膜厚が大きくなり、ゲート電極の段差が増加するので問題となっている。

【0004】

そこで、これらの問題に対する解決策としてメタルゲート電極を採用したり、あるいはTa2 O5 膜などの高誘電体膜をゲート絶縁膜として用い、リーク電流(ダイレクト・トンネリング)を抑えつつ酸化膜換算膜厚を小さくする方法等が提案されている。

【0005】

しかし、メタルゲート電極は耐熱性の点で問題がある。一方、ゲート絶縁膜に高誘電体膜を使ったMOSトランジスタには以下のような問題がある。

【0006】

ゲート絶縁膜(高誘電体膜)を形成した後の800℃から1000℃におよぶ高温熱工程(例えばソース/ドレイン拡散層の形成、層間絶縁膜のリフロー等)を経ると、シリコン基板とゲート絶縁膜との間の界面反応、あるいはゲート絶縁膜とゲート電極との間の界面反応が起こる。

【0007】

しかし、ゲート絶縁膜(高誘電体膜)は、このような高温工程に耐えることは困難である。その結果、ゲート絶縁膜は劣化し、電気的に特性の良いMOSトランジスタを得ることが難しいといった問題があった。

【0008】

また、他の解決策として、溝型チャネル構造のMOS型トランジスタ(例えば西松他、Groove Gate MOSFET、8th Conf.On Solid State Device,pp.179−183,1976)が提案されている。

【0009】

図13に、従来の溝型チャネル構造のMOS型トランジスタの断面図を示す。図中、201はp型シリコン基板、202は素子分離絶縁膜(STI)、203はゲート絶縁膜、204はLDD、205は高不純物濃度のソース・ドレイン拡散層、206は層間絶縁膜、207はゲート電極(ポリシリコン膜)、208はソース・ドレイン配線電極を示している。

【0010】

この種の溝型チャネル構造のMOSトランジスタは、ゲート電極207がソース・ドレイン拡散層205の上まで張り出しているため、例えば合わせずれによるゲート電極207とソース・ドレイン配線電極208との短絡を防止する必要がある。

【0011】

そのためには、ゲート電極207とソース・ドレイン配線電極208との間の距離を離せば良いが、今度は素子の微細化が困難になるという問題が起こる。

【0012】

また、シリコン基板201をエッチングして形成した凹部のシリコン表面をチャネルに使用するので、エッチングダメージを除去することが求められる。しかし、エッチングダメージを除去することは困難であるため、素子の特性が向上しないという問題があった。

【0013】

【発明が解決しようとする課題】

上述の如く、従来の溝型チャネル構造のMOSトランジスタは、ゲート電極がソース・ドレイン拡散層の上まで張り出しているため、ゲート電極とソース・ドレイン配線電極との間の距離を離す必要があり、素子の微細化が困難になるという問題があった。

【0014】

また、従来のポリサイド(ポリシリコン膜とシリサイド膜との積層膜)からなるゲート構造では、ゲート電極の幅が微細化するに従って、ゲート電極の配線抵抗を低下させるために、ゲート電極の膜厚を厚くしていた。このため、ゲート電極のチャネル長(L)方向の寸法が小さくなるに従って、ゲート電極の段差が増加するので、ゲート電極へのコンタクトの形成の際に、コンタクト孔のアスペクト比が大きくなり、問題となっていた。

【0015】

本発明は、上記事情を考慮してなされたもので、その目的は、素子の微細化を可能とした半導体装置およびその製造方法を提供することにある。

【0016】

本発明の他の目的は、ゲート電極の抵抗を下げるとともに、ゲート電極による段差を緩和した半導体装置およびその製造方法を提供することにある。

【0017】

【課題を解決するための手段】

上記課題を解決するため、本発明は、半導体基板と、この半導体基板に形成された溝の底面および側面に形成されたゲート絶縁膜と、前記底面および側面にゲート絶縁膜が形成された溝内に下部が埋め込まれ、上部が前記半導体基板の表面から突出するゲート電極と、前記ゲート電極を挟むように、前記半導体基板の表面領域に形成されたソース領域およびドレイン領域とを具備し、前記溝に沿って形成されたチャネル領域のチャネル長をL、前記ゲート絶縁膜の厚さをt OX 、前記ゲート電極の厚さをH、ゲート電極の長さをL gate 、ソース・ドレイン拡散層の接合深さをXjとすると、下記式を満たすことを特徴とする半導体装置を提供する。

【0019】

L+Xj−tOX<H<3.125×Lgate+Xj−tOX

かかる半導体装置において、前記ゲート絶縁膜は、堆積絶縁膜とすることが出来る。

【0020】

また、前記ゲート電極は、素子分離絶縁膜よりも深く前記半導体基板内に形成することが出来る。

【0021】

更に、 前記半導体基板内の前記溝の底部を、丸みを持って形成することが出来る。

【0023】

また、本発明は、半導体基板の表面に1対のソース・ドレイン拡散層となる拡散層を形成する工程と、前記半導体基板上に層間絶縁膜を形成する工程と、前記層間絶縁膜および前記半導体基板を選択的に除去して溝を形成するとともに、この溝によって前記拡散層を2つに分離することによりソース・ドレイン拡散層を形成する工程と、前記溝の底面および側面にゲート絶縁膜を形成する工程と、前記底面および側面にゲート絶縁膜が形成された溝内に、下部が埋め込まれ、上部が前記半導体基板の表面から突出するように、ゲート電極を形成する工程とを具備し、前記溝に沿って形成されたチャネル領域のチャネル長をL、前記ゲート絶縁膜の厚さをtOX、前記ゲート電極の厚さをH、ゲート電極の長さをLgate 、ソース・ドレイン拡散層の接合深さをXjとすると、下記式を満たすことを特徴とする半導体装置の製造方法を提供する。

【0024】

L+Xj−tOX<H<3.125×Lgate+Xj−tOX

これらの半導体装置の製造方法において、前記ソース・ドレイン拡散層の形成後に、前記溝を充填するように全面に導電膜を形成し、次に前記溝の外部の前記導電膜をCMP法を用いて研磨除去することにより、前記導電膜からなるゲート電極を埋込み形成することが出来る。

【0025】

本発明のより具体的な構成は以下の通りである。

【0026】

(1)ゲート絶縁膜がTa2 O5 膜の単層膜、またはTa2 O5 膜を含む積層膜である。

【0027】

(2)ゲート絶縁膜がBaとSrとTiを含む単層膜、またはBaとSrとTiを含む積層膜である。

【0028】

(3)ゲート電極がメタルゲート電極である。

【0029】

(4)同一チップ内で膜厚の異なるゲート絶縁膜が用いられている。

【0030】

(5)同一チップ内で材料の異なるゲート絶縁膜が用いられている。

【0031】

(6)本発明、(4)または(5)において、ゲート絶縁膜として強誘電体膜が用いられた領域とゲート絶縁膜として高誘電体膜が用いられた領域が存在する。

【0032】

(7)ゲート電極が不純物をドープした多結晶シリコン膜である。

【0033】

(8)低不純物濃度の拡散層(LDD)を形成した後、この拡散層の表面に高不純物濃度の拡散層(ソース・ドレイン)を形成することにより、LDD構造を有するソース・ドレイン拡散層を形成する。

【0034】

以上のように、本発明に係る半導体装置によれば、ゲート電極の一部が基板中に埋め込まれているので、ゲート電極の抵抗を下げるためにゲート電極の膜厚を厚くしても、ゲート電極による段差を緩和することが出来る。

【0035】

また、ゲート電極の基板中に埋め込まれている部分の寸法と基板の表面から突出している部分の寸法とを所定の範囲に規定することにより、最適な性能を有する半導体装置を得ることが可能である。

【0036】

特に、ゲート絶縁膜として堆積絶縁膜(例えばCVD絶縁膜)を用いることにおより、熱酸化膜等に比べて、膜が凹部内側に張り出して形成される。すなわち、リソグラフィの限界で決まる寸法よりも堆積絶縁膜の膜厚の約2倍分だけチャネル長を短くできる。その結果、短チャネル化が実現され、これによりトランジスタの性能を向上させることができる。

【0037】

また、STI等の溝掘り型の素子分離を行った場合には、素子分離絶縁膜と素子分離溝との境界部に微少な窪みが生じても、その窪みはゲート絶縁膜(堆積絶縁膜)で埋め込まれる。これにより、いわゆるコーナーデバイス(寄生トランジスタ)の発生を防止でき、素子特性の劣化を防止できるようになる。

【0038】

また、ゲート電極を前記素子分離絶縁膜よりも深く半導体基板内に形成することにより、トランジスタの平面積を増加させずにチャネル幅を増加できる。したがって、微細化を図れるという効果を維持したままチャネル電流の増加を図ることができる。

【0039】

更に、溝の底部を丸みをもって形成することにより、鋭角な角部が無くなるので、ゲート絶縁膜の耐圧が向上したり、チャネルが丸くなってチャネル電流が増加するなどのトランジスタ特性の向上を図ることができる。

【0040】

更にまた、ソース・ドレイン拡散層の底面を溝の底面よりも上にあるようにすることにより、ソース・ドレイン拡散層の接合深さが実質的にマイナスになり、これにより微細化を進めてもショートチャネル効果を抑制できるようになる。

【0041】

また、本発明の半導体装置の製造方法によれば、本発明に係る溝型チャネル構造のMOSトランジスタのソース・ドレイン拡散層をゲート電極と自己整合的に形成できるようになる。

【0042】

また、ゲート絶縁膜は高温熱処理工程(例えばソース・ドレイン拡散層の活性化工程、メタルゲート電極の形成工程、ゲート電極の後酸化工程、リフロー工程)の後に形成できるので、ゲート絶縁膜として、強誘電体膜や高誘電体膜のように熱によって劣化しやすい絶縁膜を用いることができるようになる。これにより、例えば強誘電体膜を用いることによりゲート絶縁膜の酸化膜換算膜厚を薄くでき、トランジスタの素子特性の改善を図ることができる。

【0043】

また、特に、CMP法を用いてゲート電極を埋込み形成することにより、RIE法を用いてゲート電極を埋込み形成する場合とは異なり、ゲート電極形成時のプラズマプロセスダメージ(例えばゲート絶縁膜の絶縁破壊)の問題はない。また、CMP法を用いた場合とは異なり、メタル電極の材料の制約(例えば耐熱性)が無くなる。

【0044】

【発明の実施の形態】

以下、図面を参照しながら、本発明の実施の形態(以下、実施形態)について説明する。

【0045】

(第1の実施形態)

図1は、本発明の第1の実施形態に係る溝型チャネル構造のMOSトランジスタを示す図であり、図1(a)は平面図、図1(b)は同平面図のA−A’断面図、図1(b)は同平面図のB−B’断面図である。以下の実施形態では、nチャネルのMOSトランジスタについて説明するが、pチャネルのMOSトランジスタの場合には各導電型を逆にすれば良い。

【0046】

図中、101はp型のシリコン基板を示しており、このシリコン基板101の表面にはトレンチ型の素子分離絶縁膜102が形成されている。シリコン基板101上には層間絶縁膜106が形成されている。ここで、素子形成領域(AA:Active Area)のシリコン基板101の不純物濃度は、5×1015cm-3程度である。

【0047】

素子分離絶縁膜102で規定された素子形成領域の層間絶縁膜106からその下のシリコン基板101にかけては凹部107が形成されている。この凹部107は層間絶縁膜106を貫通し、シリコン基板101の途中の深さまで達している。

【0048】

凹部107内にはゲート絶縁膜109を介してゲート電極110が埋込み形成されている。ゲート絶縁膜109は例えば厚さ4.0nm程度の熱酸化膜である。

【0049】

ゲート絶縁膜109はシリコン基板101とゲート電極110との界面に形成されている。したがって、シリコン基板101内に埋め込まれた部分のゲート電極110の底面および側面はゲート絶縁膜109で覆われている。

【0050】

また、ゲート電極110は、例えばポリシリコン膜、またはTiN膜やRu膜等のメタル膜で構成されている。ゲート電極110のチャネル方向の幅は、例えば0.1〜0.15μm程度である。凹部107の底面下のチャネル領域には、しきい値電圧を調整するために、不純物濃度5×1017cm-3程度のチャネルイオン注入層108が形成されている。

【0051】

低不純物濃度のn型のソース・ドレイン拡散層104およびその上の高不純物濃度のn型のソース・ドレイン拡散層105は、ゲート電極110と自己整合的に形成されている。

【0052】

ここで、ソース・ドレイン拡散層104のシリコン基板101の表面からの拡散深さ、不純物濃度は、それぞれ0.2μm程度、5×1019cm-3程度である。一方、ソース・ドレイン拡散層105の拡散深さ、不純物濃度は、それぞれ0.15μm程度、5×1020cm-3程度である。

【0053】

層間絶縁膜106,111にはゲート電極110、ソース・ドレイン拡散層105に対してのコンタクトホール112が開孔されており、このコンタクトホール112を介して配線113がゲート電極110、n型ソース・ドレイン拡散層105にコンタクトしている。

【0054】

ここで、層間絶縁膜106,111は例えばSiO2 膜であり、配線113は例えばAl膜で形成されている。

【0055】

このように構成された溝型チャネル構造のMOSトランジスタによれば、層間絶縁膜106を貫通し、かつ素子形成領域のシリコン基板101の途中の深さまで達した凹部107内にゲート絶縁膜109を介してゲート電極110が埋め込まれ、かつ凹部107を挟むようにシリコン基板101の表面にソース・ドレイン拡散層104,105が形成されているので、ゲート電極110がソース・ドレイン拡散層104,105の上まで張り出すことはない。したがって、本実施形態によれば、溝型チャネル構造のMOSトランジスタの微細化を図れる。

【0056】

また、本実施形態によれば、ソース・ドレイン拡散層104,105の底面が凹部の底面のチャネルよりも上にあるので、ソース・ドレイン拡散層104,105の接合深さが実質的にマイナスになり、これにより微細化を進めてもショートチャネル効果を抑制できるようになる。

【0057】

また、ソース・ドレイン拡散層104,105の接合深さを実質的にマイナスに保ったままソース・ドレイン拡散層104,105の接合深さを深くすれば、ソース・ドレイン拡散層104,105の低抵抗化を図ることができる。

【0058】

また、ゲート電極110の抵抗を下げるためにゲート電極110の高さを増加させても、ゲート電極110の一部がシリコン基板101中に埋め込み形成されているため、ゲート電極110によって形成される段差を緩和できる。

【0059】

次に本実施形態の溝型チャネル構造のMOSトランジスタの製造方法について説明する。図2〜図7はその製造方法を示す工程図である。各図(a)は平面図、各図(b)は同平面図のA−A’断面図を示している。

【0060】

まず、図2に示すように、不純物濃度5×1015cm-3程度のp型のシリコン基板101を用意する。あるいはp型シリコン基板の表面に例えば厚さ1μm程度のpまたはn型シリコン層をエピタキシャル成長させてなる、いわゆるエピタキシャル基板を用いても良い。

【0061】

なお、同一基板にnチャネルおよびpチャネルのMOSトランジスタを形成するいわゆるCMOS構造の場合には、シリコン基板101の(100)面のnチャネルトランジスタ形成領域にはp型ウェルを形成し、pチャネルトランジスタ形成領域にはn型ウェルを形成する。以下では、nチャネルトランジスタの場合について説明する。pチャネルMOSトランジスタの場合には、不純物の型を逆に変えれ良い。

【0062】

次に同図に示すように、例えば反応性イオンエッチング(RIE)法を用いてシリコン基板101の表面に深さ約0.35μm程度のトレンチを掘り、そのトレンチ内にSiO2 膜などの素子分離絶縁膜102を埋め込むことにより、STI(Shallow Trench Isolation)と呼ばれる素子分離を行う。

【0063】

次に同図に示すように、厚さ8.0nm程度のSiO2 膜103を形成した後、このSiO2 膜103上に例えばフォトレジストパターン(図示せず)を形成し、これをマスクに用いて所望の領域にイオン注入を行うことにより、低不純物濃度のソース・ドレイン拡散層(LDD)となる低不純物濃度のn型拡散層104を形成する。イオン注入の条件は、例えばリン(P+ )のイオン注入であれば加速電圧70KeV程度、ドーズ量4×1013cm-2程度である。

【0064】

続いて同レジストパターンをマスクに用いてイオン注入を行うことにより、高不純物濃度のソース・ドレイン拡散層となる高不純物濃度のn型拡散層105を低不純物濃度のn型拡散層104の表面に形成する。イオン注入の条件は、例えば砒素(As)のイオン注入であれば、加速電圧30KeV程度、ドーズ量5×1015cm-2程度である。この後、マスクとして用いたフォトレジストパターンを剥離する。

【0065】

なお、本実施形態では、ドレイン基板の電界を緩和するためにLDD構造のソース・ドレイン拡散層を形成するが、低不純物濃度または高不純物濃度のソース・ドレイン拡散層のみのを形成しても良い(シングル・ソース・ドレイン方式)。

【0066】

次に同図に示すように、全面にSiO2 からなる厚さ200nm程度の層間絶縁膜106を例えばCVD法を用いて形成した後、例えば800℃程度のN2 雰囲気中で30分程度デンシファイを行う。

【0067】

この熱工程はn型拡散層104,105中の不純物の活性化も兼ねている。また、n型拡散層104,105の深さ(Xj)を抑えたいときは、デンシファイの温度を750℃程度に低温化して、950℃で10秒程度のRTA(Rapid Thermal Anneal)プロセスを併用してn型拡散層104,105中の不純物の活性化を行っても良い。

【0068】

次に図3に示すように、ゲート電極が形成される領域に、層間絶縁膜106を貫通し、シリコン基板101の途中の深さまで達した凹部107をレジスト(図示せず)をマスクにエッチングにより形成するとともに、凹部107によりn型拡散層104,105を2つに分離することによって、1対の低不純物濃度のソース・ドレイン拡散層(LDD)104およびその上に1対の高不純物濃度のソース・ドレイン拡散層105を形成する。

【0069】

具体的には、例えばフォトレジストパターン(図示せず)をマスクに用いて、ゲート電極が形成される領域のSiO2 膜103、層間絶縁膜106、シリコン基板101をRIE法にてエッチングすることにより、底面が基板表面から0.30μm程度の位置にある凹部107を形成する。

【0070】

その後、凹部107を形成する際のエッチング時に生じたエッチングポリマー層(図示せず)等を除去した後、シリコン基板101のシリコン表面を露出させ、例えば900℃の水素雰囲気中で3分程度熱処理を行うことにより、凹部107表面のSi原子を動かす。

【0071】

このとき、シリコン原子はシリコン表面積が最小になるように動くので、凹部107を形成する際のエッチング時に生じたダメージ等を回復させることができる。もちろん、これ以外のエッチング・ダメージ回復および除去の手段を用いても良い。

【0072】

次に同図に示すように、凹部107の底面の露出したシリコン表面に厚さ5nm程度のダミーSiO2 膜(図示せず)を例えば熱酸化法により形成した後、層間絶縁膜106等またはフォトレジスト(図示せず)をマスクに用いて、凹部107の底面下のシリコン基板101(チャネル領域)に対して選択的にチャネルイオン注入を行って、チャネルイオン注入層108を形成する。

【0073】

nチャネルトランジスタの場合、例えば0.7V程度のしきい値電圧(Vth)を設定するためには、例えば加速電圧10KeV、ドーズ量5×1012cm-2程度の条件でボロン(B+ )をイオン注入し、チャネル領域にp型のチャネルイオン注入層108を選択的に形成する。

【0074】

この工程は、図2の工程の段階でSiO2膜103を通して全面にイオン注入を行なうようにしても良いが、その場合には選択的なチャネルイオン注入を行うことができない。

【0075】

また、チャネルイオン注入層108中の不純物の活性化は、この後、例えばRTA(Rapid Thermal Anneal)を用いて800℃、10秒程度の熱処理で行っても良い。

【0076】

この後の熱工程を考慮して、トランジスタのショート・チャネル効果を抑制できるように、チャネル領域(チャネルイオン注入層108)の不純物プロファイルを最適化する。

【0077】

次に図4に示すように、ダミーSiO2膜(図示せず)を除去した後、熱酸化により基板表面の凹部107の内面(底面、側面)にゲート絶縁膜(熱酸化膜)109を形成する。また、酸化膜の表面を熱窒化した膜をゲート絶縁膜に用いても良い。さらに、CVD−SiO2 膜、CVD−SiON膜、またはCVD−Si3 N4 膜を含む積層膜をゲート絶縁膜に用いても良い。

【0078】

次に図5に示すように、凹部107の内部を充填するように、ゲート電極となる導電膜110を全面に形成する。導電膜110としては、例えば不純物を高濃度にドープしたポリシリコン膜やメタル膜を用いる。メタル膜としては、例えばRu膜、TiN膜、W膜、タングステンナイトライド膜(WNx )膜、WSi2 膜、TiSi2 膜またはこれらの積層膜があげられる。もちろん、CVD−SiO2 膜、CVD−SiON膜、CVD−Si3 N4 膜を含む積層膜をゲート絶縁膜に用いた場合には、不純物をドープしたポリシリコン膜をゲート電極として用いても良い。

【0079】

次に図6に示すように、凹部107の外部の導電膜110をCMP法により研磨除去することにより、凹部107の内部にゲート電極110を埋込み形成する。

【0080】

次に図7に示すように、全面にSiO2 膜からなる厚さ150nm程度の層間絶縁膜111を形成した後、ソース・ドレイン拡散105、ゲート電極110に対してのコンタクトホール112を層間絶縁膜106,111に開孔する。

【0081】

最後に、Al膜またはAl−Cu膜等のメタル膜を全面に形成し、このメタル膜をパターニングして、図1に示すように配線113を形成した後、パッシベーション膜(図示せず)を全面に形成して、トランジスタの基本構造が完了する。

【0082】

本実施形態の製造方法によれば、ソース・ドレイン拡散層104,105をゲート電極110と自己整合的に形成できるようになる。

【0083】

また、CMP法を用いてゲート電極110を埋込み形成しているので、RIE法を用いてゲート電極を埋込み形成する場合とは異なり、ゲート電極形成時のプラズマプロセスダメージ(例えばゲート絶縁膜109の絶縁破壊、ゲート絶縁膜109の信頼性低下)の問題はない。

【0084】

また、CMP法を用いてゲート電極110を埋込み形成しているので、RIE法を用いた場合とは異なり、メタルゲート電極を用いてもその材料の制約(例えばエッチング性についての制約)はない。

【0085】

また、チャネル領域に不純物イオンを選択的に注入することにより、チャネルイオン注入層108を形成できるので、つまりソース・ドレイン拡散層104,105にはよけいな不純物が導入されないので、ソース・ドレインの接合容量およびソース・ドレイン拡散層と基板間の逆方向PN接合リーク電流の増加を防止できる。

【0086】

また、チャネルイオン注入層108はソース・ドレイン拡散層104,105の活性化アニールの高温熱工程を受けないので、急峻な不純物プロファイルを維持でき、短チャネル効果を抑えるのに最適な不純物プロファイルを有するチャネルイオン注入層108を実現できる。

【0087】

また、ソース・ドレイン拡散層104を得るために、RIE法による側壁残し工程が不要になるので、工程が簡略化する。

【0088】

(第2の実施形態)

図8は、本発明の第2の実施形態に係る溝型チャネル構造のMOSトランジスタを示す断面図である。なお、図1と対応する部分には図1と同一符号を付してあり、詳細な説明は省略する(他の実施形態も同様)。

【0089】

本実施形態が第1の実施形態と主として異なる点は、熱酸化膜の代わりに堆積絶縁膜(例えばCVD絶縁膜)をゲート絶縁膜114に用いたことにある

本実施形態によれば、ゲート絶縁膜114として堆積絶縁膜を用いているので、熱酸化膜等に比べて、凹部内側に張り出して形成される。すなわち、リソグラフィの限界で決まる寸法よりもゲート絶縁膜114の膜厚の約2倍分だけ、チャネル長を短くできる。その結果、短チャネル化が実現され、これによりランジスタの性能をさらに向上させることができる。

【0090】

また、STI等の溝掘り型の素子分離を行った場合には、素子分離絶縁膜102と素子分離溝との境界部に微少な窪みが生じても、その窪みはゲート絶縁膜114(堆積絶縁膜)で埋め込まれる。

【0091】

これにより、いわゆるコーナーデバイス(寄生トランジスタ)の発生を防止でき、しきい値電圧の変動等の素子特性の劣化を防止できるようになる。また、溝型チャネル構造のMOSトランジスタを集積形成した場合には、MOSトランジスタ間のしきい値電圧等の素子特性のばらつきを抑制できるようになる。

【0092】

次に本実施形態の溝型チャネル構造のMOSトランジスタの製造方法について説明する。なお、ゲート絶縁膜114を形成する前までの工程(ダミーSiO2 膜を除去するまでの工程)は同じなので省略する。

【0093】

まず、CVD法等の堆積法を用いて堆積型のゲート絶縁膜114を全面に形成する。例えば、CVD法を用いて厚さ20nm程度の高誘電体膜(例えばTa2 O5 膜)をゲート絶縁膜114として形成する。

【0094】

このとき、凹部107のシリコン表面と高誘電体膜(ゲート絶縁膜114)との界面に、いわゆる界面準位等ができ難くするために、また、凹部107のシリコン表面と高誘電体膜との界面での反応を防止するためには以下のようにすれば良い。

【0095】

すなわち、凹部107のシリコン表面に薄い(例えば1nm程度)SiO2 膜を形成した後に高誘電体膜を形成したり、あるいはNH3 ガス雰囲気中でRTP(Rapid Thermal Process)により凹部107のシリコン表面に直接窒化した膜を形成した後に高誘電体膜を形成したり、あるいは厚さ1nm程度のSiO2 膜の表面をNO2 ガス等を用いて表面窒化した、いわゆるオキシナイトライド膜などを介して高誘電体膜(例えばTa2 O5 膜、(Ba,Sr)TiO3 膜)を形成すると良い。

【0096】

また、CVD−SiO2 膜や、CVD−SiON膜や、CVD−Si3 N4 膜を含む積層絶縁膜をゲート絶縁膜114に用いても同じような効果が得られる。すなわち、成膜後に、例えば1000℃、10秒程度のRTPによる熱処理を行ってデンシファイすると、凹部107のSi表面と積層絶縁膜(ゲート絶縁膜114)との界面の界面準位が減少したり、リーク電流が減少するなど絶縁膜としての絶縁特性が改善されたりする。

【0097】

次にゲート絶縁膜114を介して凹部107内にゲート電極110をCMP法を用いて埋込み形成する。このときは、ゲート電極110の幅は、ゲート絶縁膜114の膜厚の2倍分だけ細くなっている。すなわち、トランジスタのチャネル長がリソグラフィーで決まる寸法よりさらに細くすることができる。

【0098】

ゲート電極110としては、例えば不純物をドープしたポリシリコン膜や、メタル膜(例えばRu膜、TiN膜、W膜、タングステンナイトライド(WNx )膜、WSi2 膜、TiSi2 膜またはこれらの積層膜)があげられる。もちろん、CVD−SiO2 膜、CVD−SiON膜、CVD−Si3 N4 膜を含む積層膜をゲート絶縁膜に用いた場合には、不純物をドープしたポリシリコン膜をゲート電極として用いても良い。

【0099】

この後の工程は第1の実施形態と同じである。

【0100】

このような製造方法によれば、ソース・ドレイン拡散層104,105の活性化およびリフロー工程などの高温熱処理工程をゲート絶縁膜114の形成前に行うことができる。

【0101】

したがって、ゲート絶縁膜114およびゲート電極110としてそれぞれ高誘電体膜およびメタル膜を使用してもこれらの膜はソース・ドレイン拡散層の活性化や平坦化のための高温工程を受けることがないので、リーク電流増加などのゲート絶縁膜114の劣化を抑えることができる。ゲート絶縁膜114として高誘電体膜を用いれば、ゲート絶縁膜114の酸化膜換算膜厚を薄くできるので、トランジスタの素子特性の改善を図ることができるようになる。

【0102】

また、CMP法を用いてゲート電極110を埋込み形成しているので、RIE法を用いた場合とは異なり、メタルゲート電極の材料の制約(例えば耐熱性)が無くなるので、高誘電体膜のリーク電流が下げられるようなメタルゲート電極を用いることができるようになる。

【0103】

その他、第1の実施形態と同様な効果が得られる。

【0104】

(第3の実施形態)

図9は、本発明の第3の実施形態に係る溝型チャネル構造のMOSトランジスタを示す図であり、図9(a)は平面図、図9(b)は同平面図のA−A’断面図である。

【0105】

第1の実施形態では、コンタクトホール112内にAl等の金属からなる配線113を直接埋込み形成したが、コンタクトホール112の開孔径が小さくなるとAl膜がコンタクトホール112の中に入っていかないので、配線113の信頼性が低下する。

【0106】

そこで、本実施形態では、コンタクトホール112の内面を覆うように例えばTi膜/TiN膜を全面に形成し、続いてコンタクトホール112の内部を充填するようにW膜を全面に形成した後、コンタクトホール112の外部のTi膜/TiN膜およびW膜をCMP法等を用いて除去することにより、プラグ電極(コンタクトプラグ)115を埋込み形成する。この後、配線113を形成すれば、コンタクトホールのアスペクトが高くても配線113の信頼性は高くなる。

【0107】

(第4の実施形態)

図10は、本発明の第4の実施形態に係る溝型チャネル構造のMOSトランジスタを示す図であり、図10(a)は平面図、図10(b)は同平面図のA−A’断面図、図10(b)は同平面図のB−B‘断面図である。

【0108】

本実施形態が第1の実施形態と異なる点は、ゲート電極110が素子分離絶縁膜102よりも深くシリコン基板101内に形成されていることにある。言い換えれば凹部107の底が素子分離溝の底より下にある。例えば、凹部107の深さは0.4μm、素子分離溝の深さは0.25μmである。

【0109】

このような構成であれば、図10(c)に示すようにチャネル幅を3次元的に形成できるため、トランジスタの平面積を増加させずにチャネル幅を増加できる。したがって、微細化を図れるという効果を維持したままチャネル電流の増加を図ることができる。

【0110】

(第5の実施形態)

図11は、本発明の第5の実施形態に係る溝型チャネル構造のMOSトランジスタを示す図であり、図11(a)は平面図、図11(b)は同平面図のA−A’断面図、図11(b)は同平面図のB−B‘断面図である。

【0111】

第1の実施形態では、凹部107のシリコン表面のエッチングダメージを除去するために、特別な高温工程(例えば、凹部107のシリコン表面を露出させた後、例えば900℃の水素雰囲気で3分程度の熱処理)を行って、凹部107のシリコン表面のSi原子を動かした。

【0112】

このとき、シリコン原子は凹部107のシリコン表面の面積が最小になるように動くので、凹部107のシリコン表面のエッチングダメージ等を回復させることができるが、この熱処理条件を調整(例えば、凹部107のシリコン表面を露出させた後、950℃の水素雰囲気で5分程度の熱処理に変更)することによって凹部107の形状を変化させることができる。

【0113】

すなわち、図11(b)に示すように、凹部107の底部をなだらかな円弧状に変形させることができる。このような構造をとると、凹部107の底部(ゲート絶縁膜109が形成される領域)に鋭角な角部が無くなるので、ゲート絶縁膜109の耐圧の向上を図ることができるとともに、チャネル部をなだらかにできるために電子の移動度の劣化を抑制することができ、これによりトランジスタ特性の向上を図ることができるようになる。

【0114】

(第6の実施形態)

図12は、本発明の第6の実施形態に係る溝型チャネル構造のMOSトランジスタの製造方法を示す工程断面図である。

【0115】

本実施形態が第1の実施形態と異なる点は、図12(a)に示すように層間絶縁膜106をエッチングして溝を形成し、その溝の側壁にSiO2 膜からなるサイドウォール117を形成した後、図12(b)に示すように、層間絶縁膜106およびサイドウォール117をマスクにしてシリコン基板101をエッチングすることにより、凹部107を形成することにある。

【0116】

サイドウォール117は、全面に例えば厚さ20nm程度のSiO2 膜を堆積した後、このSiO2 膜をRIE法にて全面エッチングするという、いわゆる側壁残しにより形成する。

【0117】

このような形成方法によれば、凹部107のチャネル長方向の幅の寸法を、リソグラフィの限界で決まる寸法よりも小さくできる。したがって、ゲート長の短いゲート電極を実現できる

通常のトランジスタでは、ゲート長(チャネル長さ)を短くすると、ショートチャネル効果が起こり、しきい値電圧(Vth)が低下してリーク電流が増加するなどの問題が発生する。

【0118】

しかし、本実施形態は、第1の実施形態と同様に、ソース・ドレイン拡散層104,105の接合深さが実質的にマイナスになるなどの理由により、ショートチャネル効果を抑えることができる。

【0119】

したがって、本実施形態によれば、サイドウォール117を形成して、チャネル長を短くすることにより、トランジスタの特性を向上させることが可能となる。

【0120】

(第7の実施形態)

本実施形態は、ゲート電極の、半導体基板の表面から突出する上部の厚さと、溝に埋め込まれた下部の厚さを、最適なトランジスタの性能が得られるように規定した例である。

【0121】

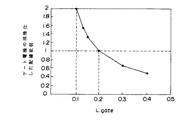

図14は、膜厚が一定(例えばH=0.10μm)でゲート長(L)が異なる3種類のゲート電極を示し、図15は、これらのゲート電極(タングステンからなる)のゲート長(Lgate)とゲート電極の配線抵抗との関係を示すグラフである。

【0122】

図15から、ゲート長(Lgate)が0.2μmから0.1μmに、1/2に短くなった場合、ゲート電極の配線抵抗は、約2倍となっていることがわかる。従って、ゲート電極の配線抵抗が素子性能(駆動速度等)に大きく影響する場合には、これまで、素子の微細化のためのLgateの短縮の要請に対して、ゲート電極の厚さを2倍にして素子性能の低下を防止していた。しかし、ゲート電極を厚くすると、ゲート電極が上方に突出し、段差が大きくなるため、平坦化のための層間絶縁膜を厚くしなければならず、そうすると層間絶縁膜に形成されるコンタクト孔のアスペクト比が大きくなり、コンタクトの形成が困難となるという問題があった。

【0123】

本実施形態に係るコンケーブ構造のトランジスタでは、ゲート電極の一部をSi基板中に埋め込むことにより、上記問題を解決しており、埋め込みの深さとして、次の3つの形がある。

【0124】

(1)トランジスタ特性を劣化させることなく、最適な深さにゲート電極70の一部がSi基板61中に埋め込まれている(図16(a))。

【0125】

(2)浅く埋め込まれている(図16(b))。

【0126】

(3)深く埋め込まれている(図16(c))。

【0127】

ここで、ゲート電極70のトータルの膜厚をH、ゲート電極70がSi基板61上に突出している寸法をh、ソース・ドレイン拡散領域の接合深さをXj、ゲート絶縁膜69の厚さをtOX、ソース・ドレイン拡散領域の底部のレベルとゲート電極70の下方のチャネル領域のレベルとの差をdとすると、図65A〜65Cから分かるように、以下の式(1)が成立する。

【0128】

H=h+Xj+d−tOX …(1)

本実施形態では、hとdの最適値について検討する。

【0129】

図17は、ゲート長Lgateとドレイン電流Idとの関係を示すグラフである。なお、ドレイン電流Idは、ゲート長Lgate=0.20μmの場合を1として規格化した値である。ここでは、Lgate=0.20μmのトランジスタとして、Xj、tOX等の値は、最適化されている。

【0130】

図17から、ゲート長Lgateが長くなるに従って、ドレイン電流Idは低下していることがわかる。ドレイン電流Idが20%以上低下すると、素子の動作に影響が生ずるので、ドレイン電流Idの20%の低下、即ちチャネル長L=0.25μm(Lgateの25%増)がチャネル長Lの上限であることがわかる。

【0131】

図16(a)〜(c)に示すようなコンケーブ構造のトランジスタの場合、ゲート電極70の埋め込みの深さが深ければ深いほど、トータルのチャネル長さ(l1 、l2 、l3 )は長くなる。これは、溝の側面もチャネル長に寄与するからである。

【0132】

これらの結果から、トランジスタの性能上、ゲート長Lgate(溝底部のチャネル長)およびdは、次の式を満たすことが望ましい。

【0133】

d<Lgate×0.25/2 …(2)

次に、図18を参照して、dの下限について検討する。

【0134】

ゲートがコンケーブ構造ではない平面構造のトランジスタの場合、ショートチャネル効果を防止するために、ソース・ドレイン拡散領域の接合深さXjを浅くすることが重要である。例えば、Xj=0.1μmのトランジスタに比べ、Xj=0.05μmのトランジスタの方がショートチャネル効果を低減出来ることが知られている。しかし、従来の平面構造のトランジスタでは、Xj=0μmとすることは原理的に不可能である。

【0135】

これに対し、本実施形態のようなコンケーブ構造のトランジスタでは、dの値を変えることにより、Xjを見掛上、マイナスにすることが可能である。このことは、コンケーブ構造のトランジスタにおいて、ショートチャネル効果を著しく低減できることを示している。即ち、図18に示すように、d=0(Xj=0に相当)からd=0.01μm、d=0.02μmと、dを増加させることにより、ショートチャネル効果を低減できることがわかる。従って、ショートチャネル効果を抑制するためには、d>0であることが重要である。なお、d>0.02μmでは、ショートチャネル効果の抑制効果は飽和している。

【0136】

次に、ゲート電極のSi基板上に突出している部分の高さhについて考える。図19は、hがh1 の場合、図20は、hがh1 より大きいh2 である場合をそれぞれ示す。L=0.20μmの場合を例にとって、L=0.20μmの設計ルールに従って、コンタクト孔80のアスペクト比(図中のh/Wに相当)を計算すると、図21に示すようになる。

【0137】

図19において、h1 =0.20μmの場合、コンタクト孔80のアスペクト比は1である。しかし、図21において、h2 =0.6μmの場合、コンタクト孔80のアスペクト比は3にもなる。このように大きなアスペクト比では、コンタクト孔80の形成およびコンタクトプラグの埋め込みが困難となるばかりか、コンタクトプラグの抵抗も増加してしまう。

【0138】

しかし、hが大きければ大きいほど、ゲート電極70の配線抵抗を低下させることが出来る。このことから、hは、トランジスタ特性において、ゲート電極の配線抵抗の低下と、コンタクトプラグの抵抗増加および埋め込み困難性とのトレードオフによって決定される値であることがわかる。

【0139】

従来のコンタクト形成の例およびトランジスタの特性の点から、コンタクト孔のアスペクト比は3以下にすることが望ましいことがわかっている。従って、ゲート電極の配線抵抗を考慮して、最低膜厚がゲート長Lより大きいことにすると、ゲート長Lを最小の設計寸法(デザインルール)として、次の式が成立する。

【0140】

Lgate<h<ゲート長L×3 …(3)

以上の関係をまとめると、以下のようになる。

【0141】

L+Xj−tOX<H<3×Lgate

L+Xj−tOX<H<3.125×Lgate+Xj−tOX …(4)

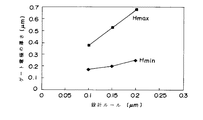

各デザインルール(L=0.20μm,0.15μm,0.10μm)におけるXj、dmax 、hmax 、tOX、Hmin 、Hmax の値は、以下の表のようになる。

【0142】

【表1】

【0143】

(注)ソース/ドレイン領域の抵抗を下げるために、Xjは、一定値0.10μmとした。

【0144】

Hmin とHmax とをまとめたのが、図22である。図22に示すように、Hmin とHmax との間に入るように、各設計ルールにおいてゲート電極の厚みを調整することが必要である。

【0145】

図23(a)〜(c)は、ゲート電極70の厚みおよびSi基板61内に埋め込まれた部分の深さを種々変化させたトランジスタを示す。以上のことを考慮すると、図23(a)に示すように、Si基板61内に埋め込まれた部分の深さが浅過ぎると、ショートチャネル効果を抑制することが困難であり、図23(c)に示すように、Si基板61内に埋め込まれた部分の深さが深過ぎると、トランジスタのドレイン電流が低下し、図23(d)に示すように、ゲート電極70の厚みが薄いと、ゲート電極70の配線抵抗が大きくなってしまう。従って、図23(b)に示すような構造が最適である。

【0146】

図23(b)に示すような構造とすることにより、ゲート電極70の配線抵抗の増大による素子特性の劣化、コンタクト孔のアスペクト比の増大によるコンタクトの形成の困難さ、およびコンタクト抵抗の増大による素子特性の劣化を防止することが出来る。

【0147】

なお、本発明は、上記実施形態に限定されるものではない。例えば、上記実施形態では、ゲート絶縁膜の膜厚に関して、詳述しなかったが、例えば3.3V系と2.5V系などのように異なる複数の電圧に対応するために、ゲート絶縁膜の膜厚が異なる複数種のMOSトランジスタを形成しても良い。

【0148】

このようにするには、例えばゲート電極の工程前に、所望の膜厚のゲート絶縁膜を形成するトランジスタ領域外をマスクで覆って上記所望のトランジスタ領域に所望のゲート絶縁膜を選択的に形成する工程を繰り返せば良い。

【0149】

あるいは、所望の膜厚のゲート絶縁膜およびゲート電極を全てのトランジスタ領域に形成した後、上記所望の膜厚のゲート絶縁膜を形成するべきトランジスタ領域をマスクで覆って他のトランジスタ領域のゲート絶縁膜およびゲート電極を除去する工程を繰り返しても良い。

【0150】

このように同一チップ内にゲート絶縁膜の膜厚が異なる複数種のMOSトランジスタを形成すれば、例えばpチャネルMOSトランジスタおよびnチャネルMOSトランジスタのパフォーマンスをそれぞれ最大にできたり、あるいはメモリセル部のMOSトランジスタおよび周辺回路制御部のMOSトランジスタのパフォーマンスをそれぞれ最大にできる。

【0151】

また、ゲート絶縁膜の材料が異なる複数種のMOSトランジスタを形成しても良い。

【0152】

このようにするには、例えばまず第1のゲート絶縁膜(例えばSiO2 膜とその上に形成されたTa2 O5 膜との積層絶縁膜)を形成した後、この第1のゲート絶縁膜上にゲート電極(例えばRu膜)を全てのトランジスタ領域に形成する。

【0153】

次に、第2のゲート絶縁膜(例えばPZT膜等の強誘電体膜)を形成したい領域のトランジスタ領域の第1のゲート絶縁膜および第1のゲート電極を選択的に除去した後、そのトランジスタ領域に第2のゲート絶縁膜および第1のゲート電極を選択的に形成する。このとき、必要であれば、第1のゲート電極と材料が異なる第2のゲート電極を第2のゲート絶縁膜上に形成しても良い。以上の工程を必要な数だけ繰り返す。

【0154】

このように同一チップ内にゲート絶縁膜の材料が異なる複数種のMOSトランジスタを形成すれば、例えばpチャネルMOSトランジスタおよびnチャネルMOSトランジスタのパフォーマンスをそれぞれ最大にできたり、あるいはメモリセル部のMOSトランジスタおよび周辺回路制御部のMOSトランジスタのパフォーマンスをそれぞれ最大にできる。

【0155】

また、強誘電体膜をゲート絶縁膜に用いた強誘電体メモリ素子と高誘電体膜をゲート絶縁膜に用いたトランジスタを同じトランジスタ構造で一連のプロセスで連続して形成でき、これにより高集積メモリチップを簡単なプロセス工程実現できるようになる。

【0156】

その他、本発明の要旨を逸脱しない範囲で、種々変形して実施できる。

【0157】

【発明の効果】

以上説明したように、本発明によれば、層間絶縁膜を貫通し、かつ素子形成領域の半導体基板の途中の深さまで達した凹部内にゲート電極を埋め込み、かつ上記凹部を挟むように半導体基板の表面にソース・ドレイン拡散層を形成することにより、ゲート電極のソース・ドレイン拡散層上への張り出しを無くすことができるので、溝型チャネル構造のMOSトランジスタの微細化を図れる半導体装置およびその製造方法を実現できるようになる。

【0158】

また、ゲート電極の一部が基板中に埋め込まれているので、ゲート電極の抵抗を下げるためにゲート電極の膜厚が厚くしても、ゲート電極による段差を緩和することが出来る。

【0159】

更に、ゲート電極の基板中に埋め込まれている部分の寸法と基板の表面から突出している部分の寸法とを所定の範囲に規定することにより、最適な性能を有する半導体素子を得ることが可能である。

【図面の簡単な説明】

【図1】本発明の第1の実施形態に係る溝型チャネル構造のMOSトランジスタを示す平面図および断面図

【図2】本発明の第1の実施形態に係る溝型チャネル構造のMOSトランジスタの製造方法を示す平面図および断面図

【図3】本発明の第1の実施形態に係る溝型チャネル構造のMOSトランジスタの製造方法を示す平面図および断面図

【図4】本発明の第1の実施形態に係る溝型チャネル構造のMOSトランジスタの製造方法を示す平面図および断面図

【図5】本発明の第1の実施形態に係る溝型チャネル構造のMOSトランジスタの製造方法を示す平面図および断面図

【図6】本発明の第1の実施形態に係る溝型チャネル構造のMOSトランジスタの製造方法を示す平面図および断面図

【図7】本発明の第1の実施形態に係る溝型チャネル構造のMOSトランジスタの製造方法を示す平面図および断面図

【図8】本発明の第2の実施形態に係る溝型チャネル構造のMOSトランジスタを示す断面図

【図9】本発明の第3の実施形態に係る溝型チャネル構造のMOSトランジスタを示す平面図および断面図

【図10】本発明の第4の実施形態に係る溝型チャネル構造のMOSトランジスタを示す平面図および断面図

【図11】本発明の第5の実施形態に係る溝型チャネル構造のMOSトランジスタを示す平面図および断面図

【図12】本発明の第6の実施形態に係る溝型チャネル構造のMOSトランジスタを示す工程断面図

【図13】従来の溝型チャネル構造のMOSトランジスタを示す断面図

【図14】本発明の第7の実施形態における膜厚が一定でゲート長が異なる3種類のゲート電極を示す斜視図

【図15】本発明の第7の実施形態におけるゲート電極のゲート長(Lgate)とゲート電極の配線抵抗との関係を示す特性図

【図16】本発明の第7の実施形態におけるゲート電極のSi基板内に埋め込まれた深さが異なるトランジスタを示す断面図

【図17】本発明の第7の実施形態におけるゲート長Lgateとドレイン電流Idとの関係を示す特性図

【図18】本発明の第7の実施形態におけるゲート長Lgateとしきい値電圧との関係を示す特性図

【図19】本発明の第7の実施形態におけるゲート電極のSi基板上に突出している部分の高さが異なるトランジスタを示す断面図

【図20】本発明の第7の実施形態におけるゲート電極のSi基板上に突出している部分の高さが異なるトランジスタを示す断面図

【図21】本発明の第7の実施形態におけるゲート電極のSi基板上に突出している部分の高さとコンタクト孔のアスペクト比との関係を示す特性図

【図22】各デザインルールにおけるHmin とHmax を示す特性図

【図23】ゲート電極の厚みおよびSi基板内に埋め込まれた部分の深さを種々変化させたトランジスタを示す断面図。

【符号の説明】

61,101…シリコン基板

66,107,111…層間絶縁膜

69,109,114…ゲート絶縁膜

70,110…ゲート電極

80,112…コンタクトホール

73,113…配線

102…素子分離絶縁膜

103…SiO2 膜

104…ソース・ドレイン拡散層

105…ソース・ドレイン拡散層(LDD)

106…層間絶縁膜

107…凹部

108…チャネルイオン注入層

115…プラグ電極

117…サイドウォール

Claims (6)

- 半導体基板と、

この半導体基板に形成された溝の底面および側面に形成されたゲート絶縁膜と、

前記底面および側面にゲート絶縁膜が形成された溝内に下部が埋め込まれ、上部が前記半導体基板の表面から突出するゲート電極と、

前記ゲート電極を挟むように、前記半導体基板の表面領域に形成されたソース領域およびドレイン領域と

を具備し、前記溝に沿って形成されたチャネル領域のチャネル長をL、前記ゲート絶縁膜の厚さをtOX、前記ゲート電極の厚さをH、ゲート電極の長さをLgate、ソース・ドレイン拡散層の接合深さをXjとすると、下記式を満たすことを特徴とする半導体装置。

L+Xj−tOX<H<3.125×Lgate+Xj−tOX - 前記ゲート絶縁膜は、堆積絶縁膜であることを特徴とする請求項1に記載の半導体装置。

- 前記ゲート電極は、素子分離絶縁膜よりも深く前記半導体基板内に形成されていることを特徴とする請求項1に記載の半導体装置。

- 前記半導体基板内の前記溝の底部は、丸みを持って形成されていることを特徴とする請求項1に記載の半導体装置。

- 半導体基板の表面に1対のソース・ドレイン拡散層となる拡散層を形成する工程と、前記半導体基板上に層間絶縁膜を形成する工程と、前記層間絶縁膜および前記半導体基板を選択的に除去して溝を形成するとともに、この溝によって前記拡散層を2つに分離することによりソース・ドレイン拡散層を形成する工程と、前記溝の底面および側面にゲート絶縁膜を形成する工程と、前記底面および側面にゲート絶縁膜が形成された溝内に、下部が埋め込まれ、上部が前記半導体基板の表面から突出するように、ゲート電極を形成する工程とを具備し、前記溝に沿って形成されたチャネル領域のチャネル長をL、前記ゲート絶縁膜の厚さをtOX、前記ゲート電極の厚さをH、ゲート電極の長さをLgate、ソース・ドレイン拡散層の接合深さをXjとすると、下記式を満たすことを特徴とする半導体装置の製造方法。

L+Xj−tOX<H<3.125×Lgate+Xj−tOX - 前記ソース・ドレイン拡散層の形成後に、前記溝を充填するように全面に導電膜を形成し、次に前記溝の外部の前記導電膜をCMP法を用いて研磨除去することにより、前記導電膜からなるゲート電極を埋込み形成することを特徴する請求項5に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18530298A JP3892588B2 (ja) | 1997-12-26 | 1998-06-30 | 半導体装置およびその製造方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP9-366810 | 1997-12-26 | ||

| JP36681097 | 1997-12-26 | ||

| JP18530298A JP3892588B2 (ja) | 1997-12-26 | 1998-06-30 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH11243195A JPH11243195A (ja) | 1999-09-07 |

| JP3892588B2 true JP3892588B2 (ja) | 2007-03-14 |

Family

ID=26503022

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP18530298A Expired - Fee Related JP3892588B2 (ja) | 1997-12-26 | 1998-06-30 | 半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3892588B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001144032A (ja) * | 1999-11-17 | 2001-05-25 | Tokyo Electron Ltd | TiSiN薄膜およびその成膜方法、半導体装置およびその製造方法、ならびにTiSiN薄膜の成膜装置 |

| KR100338783B1 (en) | 2000-10-28 | 2002-06-01 | Samsung Electronics Co Ltd | Semiconductor device having expanded effective width of active region and fabricating method thereof |

| JP2002184957A (ja) * | 2000-12-13 | 2002-06-28 | Sony Corp | 半導体装置およびその製造方法 |

| US20030098489A1 (en) | 2001-11-29 | 2003-05-29 | International Business Machines Corporation | High temperature processing compatible metal gate electrode for pFETS and methods for fabrication |

| JP4567969B2 (ja) * | 2003-10-28 | 2010-10-27 | 東部エレクトロニクス株式会社 | 半導体素子のトランジスタ製造方法 |

| JP2006253547A (ja) * | 2005-03-14 | 2006-09-21 | Oki Electric Ind Co Ltd | 半導体記憶装置及びその製造方法 |

| JP5063913B2 (ja) * | 2005-04-04 | 2012-10-31 | 三星電子株式会社 | 多層ゲート構造を備える半導体素子及びそれの製造方法 |

| KR100680415B1 (ko) * | 2005-05-31 | 2007-02-08 | 주식회사 하이닉스반도체 | 반도체 소자의 제조 방법 |

| JP4309872B2 (ja) | 2005-06-17 | 2009-08-05 | 株式会社東芝 | 不揮発性半導体記憶装置およびその製造方法 |

| JP2007194333A (ja) * | 2006-01-18 | 2007-08-02 | Elpida Memory Inc | 半導体装置の製造方法 |

| CN103187256B (zh) * | 2011-12-29 | 2015-07-08 | 中芯国际集成电路制造(上海)有限公司 | 金属栅极的形成方法 |

-

1998

- 1998-06-30 JP JP18530298A patent/JP3892588B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH11243195A (ja) | 1999-09-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100385408B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| KR100296004B1 (ko) | 반도체장치및그제조방법 | |

| JP4931267B2 (ja) | 半導体装置 | |

| US6992358B2 (en) | Semiconductor device and method for manufacturing the same | |

| US7968924B2 (en) | Semiconductor device and a method of manufacturing the same | |

| JP3600476B2 (ja) | 半導体装置の製造方法 | |

| JP2002118255A (ja) | 半導体装置およびその製造方法 | |

| JP3132435B2 (ja) | 半導体装置の製造方法 | |

| JP2008529279A (ja) | パワーダイオードを包含する集積回路 | |

| JPH118379A (ja) | 半導体装置及びその製造方法 | |

| JP2001217403A (ja) | 半導体集積回路装置およびその製造方法 | |

| JP3892588B2 (ja) | 半導体装置およびその製造方法 | |

| US20030151098A1 (en) | Semiconductor device having dual-gate structure and method of manufacturing the same | |

| US8004050B2 (en) | Semiconductor device comprising gate electrode having arsenic and phosphorous | |

| JPH1174508A (ja) | 半導体装置及びその製造方法 | |

| JP4134001B2 (ja) | 半導体装置の製造方法 | |

| US7238975B2 (en) | Nonvolatile semiconductor memory device and manufacturing method therefor | |

| US7279367B1 (en) | Method of manufacturing a thyristor semiconductor device | |

| JPH0697190A (ja) | Mosトランジスタの製造方法 | |

| JP3937894B2 (ja) | 半導体装置 | |

| JPH10163338A (ja) | 半導体装置とその製造方法 | |

| JP2001024186A (ja) | 半導体装置の製造方法 | |

| US20220157972A1 (en) | Fin-based laterally-diffused metal-oxide semiconductor field effect transistor | |

| JP4564467B2 (ja) | Mis型トランジスタおよびその製造方法 | |

| JP3725137B2 (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040728 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040728 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060908 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060912 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061110 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061205 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061207 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091215 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101215 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111215 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |