JP3786142B2 - インバータ装置 - Google Patents

インバータ装置 Download PDFInfo

- Publication number

- JP3786142B2 JP3786142B2 JP22750996A JP22750996A JP3786142B2 JP 3786142 B2 JP3786142 B2 JP 3786142B2 JP 22750996 A JP22750996 A JP 22750996A JP 22750996 A JP22750996 A JP 22750996A JP 3786142 B2 JP3786142 B2 JP 3786142B2

- Authority

- JP

- Japan

- Prior art keywords

- phase

- current detection

- inverter

- command

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Measurement Of Current Or Voltage (AREA)

- Control Of Voltage And Current In General (AREA)

- Control Of Ac Motors In General (AREA)

- Inverter Devices (AREA)

Description

【発明が属する技術分野】

本発明は、電動機を駆動するインバータの出力電流を精度良く検出する方法に関する。

【0002】

【従来の技術】

従来の三相アナログ電流検出回路を備えたインバータの出力電流検出方法の一例として、図6にインバータの回路構成図を示す。

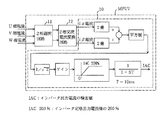

図6において、1は直流電源で、例えば三相の交流電源をダイオードで構成されたコンバータで順変換して得られる直流電源である。2は電動機で、例えば三相の誘導電動機である。3は直流電源1の正・負極間(P−N線間)に接続されたパワーデバイスで、例えばP−N線間にIGBT(絶縁ゲート型バイポーラトランジスタ)Q1ーQ6とその各IGBTに逆並列接続されたフリーホイールダイオードD1−D6の組が三相ブリッジに接続されたものである。この三相ブリッジの上アームと下アームのIGBTの接続ノードから電動機2への三相(U相、V相、W相)出力が得られる。また、下アームのQ2、Q4、Q6各IGBTのエミッタと直流電源1の負極(N線)との間にアナログ電流検出用抵抗RCT1ーRCT3が挿入されている。4はパワーデバイス3を駆動するパワーデバイス制御装置である。この制御装置は、例えば、6個のIGBTQ1ーQ6を独立にオン・オフ駆動するパワーデバイス駆動回路5と、アナログ電流検出用抵抗RCT1ーRCT3の両端電圧を入力とする三相アナログ電流検出回路6とを備えている。

【0003】

7はインバータ制御用のマイクロコンピュータ(以下MPUという)である。MPUは電動機2を駆動するために必要なPWM信号を演算する。パワーデバイス3をオン・オフ駆動する指令(PUL−PWL、NUL−NWL)をパワーデバイス制御装置4に与える。

また、MPU7はアナログ電流検出用抵抗RCT1ーRCT3の両端電圧を三相アナログ電流検出回路6を介して読み込むことにより、MPU7の制御演算に必要なインバータのフィードバック信号を得る。

次に動作について説明する。MPU7は電動機2を駆動するためのPWM信号を演算し、パワーデバイス3をオン・オフ駆動する指令(PUL−PWL、NUL−NWL)をパワーデバイス制御装置4に与える。

パワーデバイス制御装置4はMPU7からの指令に応じてパワーデバイス3をオン・オフ駆動する。パワーデバイス3の上アームIGBTQ1、Q3、Q5と下アームIGBTQ2、Q4、Q6は交互にオン・オフされ、直流電源1の直流電力が電動機2を駆動するための交流電力に変換される。

【0004】

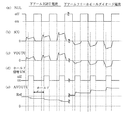

次に三相アナログ電流検出回路6の動作について図7を参照して説明する。図7は三相アナログ電流検出回路の動作を示すタイミングチャートである。まず、三相のうちの一相であるU相について説明する。MPU7からパワーデバイス制御装置4に与えられる指令NUL(U相の下アームIGBTQ2駆動信号)はパルス信号として与えられ(図7(a)参照)、前記指令NULによって動作するIGBTQ2およびフリーホイールダイオードD2に流れる電流ICUは、図7(b)のようになる。電流ICUをアナログ電流検出用抵抗RCT1により電流/電圧変換して得られる電圧VOUTUは図7(c)のようになる。この電圧VOUTUは、前記三相アナログ電流検出回路6でアナログ信号に近い形状に処理され、アナログ出力電圧AVOUTUとして出力される(図7(d)参照)。

すなわち、前記三相アナログ電流検出回路6における前記アナログ信号に近い形状に処理する回路(図示せず)により、MPU7の指令NULがOFFからONに変化した時点からディレイを追加したホールド信号VHによりホールド用コンデンサ(図示せず)の充電電圧を前記電流ICUに追従させるか、充電電圧を保持させるかを制御し、この制御された充電電圧を前記アナログ出力電圧AVOUTUとして外部に出力する。このアナログ出力電圧AVOUTUはIGBTQ2およびフリーホイールダイオードD2に流れるアナログ電流出力としてMPU7に与えられる。

【0005】

さて、図7(d)に示すように、MPU7からの指令NULがONの状態では、アナログ出力電圧AVOUTU(図6の三相アナログ電流検出回路6の出力電圧)はIGBTQ2およびフリーホイールダイオードD2に流れるアナログ電流ICUに追従した電圧となり、指令NULがOFFの状態では、指令NULがONからOFFに変化した時点の電圧が短時間(例えば500μsec間)保持される。図7(d)のホールド期間中のAVOUTUがこの状態を表してる。V相及びW相についてもU相と同様である。

MPU7は、このように変化する三相アナログ電流検出回路6からの三相のアナログ出力電圧AVOUTU、AVOUTV、AVOUTWを読み込んで、ディジタル変換することによりインバータの出力電流を検出する。

【0006】

【発明が解決しようとする課題】

ところが、従来のインバータの出力電流検出方法によると、MPU7からの指令NUL(NVL、NWL)がOFFの状態では、三相のアナログ出力電圧AVOUTU(AVOUTV、AVOUTW)は、IGBTQ2(IGBTQ4、IGBTQ6)およびフリーホイールダイオードD2(D4、D6)に流れるアナログ電流に追従した電圧とならず、MPU7は精度の良い三相のアナログ出力電圧AVOUTU(AVOUTV、AVOUTW)を読み込むことができないという問題があった。

【0007】

その原因は、MPU7からの指令NUL(NVL、NWL)のOFF時間が長い場合(例えば500μsec以上の場合)、前記指令NUL(NVL、NWL)がONからOFFになった時点の三相のアナログ出力電圧AVOUTU(AVOUTV、AVOUTW)は、図6の三相のアナログ電流検出回路6のホールド用コンデンサーによって一定時間(例えば500μsec間)保持されるが、前記一定時間以後は保持されない。この結果、三相のアナログ出力電圧AVOUTU(AVOUTV、AVOUTW)はIGBTQ2(IGBTQ4、IGBTQ6)およびフリーホイールダイオードD2(D4、D6)に流れるアナログ電流に追従した電圧とならず、MPU7は精度の良い三相のアナログ出力電圧AVOUTU(AVOUTV、AVOUTW)を読み込むことができないという問題があった。

特に、2アーム変調方式の場合は、MPU7からの指令NUL(NVL、NWL)のOFF時間が、インバータの出力電圧指令の電気角で60゜区間(インバータの出力周波数が60Hzの場合は約2.8msec期間)となる状態が発生するため前述のように図6の三相アナログ電流検出回路6の出力電圧が保持できないため、この区間ではインバータの出力電流を検出することができないという問題があった。

そこで本発明は、以上のような問題点を解決するためになされたもので、MPU7がパワーデバイス制御装置4に与える指令NUL(NVL、NWL)のOFF時間が長くなって、三相アナログ電流検出回路6のホールド用コンデンサで出力電圧を保持できない場合が生じても、インバータの出力電流を精度良く検出することができるインバータの出力電流検出方法を提供することを目的とする。

【0008】

【課題を解決するための手段】

上記課題を解決するため、直列接続した半導体スイッチング素子をオンオフ制御し、直流電圧を3相交流電圧に変換出力するインバータ装置において、3相全ての前記各下段側半導体スイッチング素子と前記直流電圧の負極側との間に接続された3相の各電流検出用抵抗と、前記3相の各電流検出用抵抗に基づいて得られる各相電流検出値のうち、電流検出値として用いる2相をインバータ装置の動作制御中に順次切替選択していく電流検出相切替手段を備えたことを特徴としている。

また、前記インバータ装置において、前記電流検出相切替手段が選択した2相の各電流検出値を、各々につき当該相の下段側半導体スイッチング素子へのオン指令期間中に検出する電流検出タイミング手段を備えたことを特徴としている。

また、前記各インバータ装置において、前記電流検出相切替手段は、出力電圧指令の電圧位相に基づいて電流検出値として用いる2相を選択することを特徴としている。

あるいは、前記電流検出相切替手段は、出力電圧指令値に基づいて電流検出値として用いる2相を選択することを特徴としている。

あるいは、前記電流検出相切替手段は、前記下段側半導体スイッチング素子のオフ指令時間に基づいて電流検出値として用いる2相を選択することを特徴としている。

【0009】

【発明の実施の形態】

上記手段により、運転中のインバータの出力電流を三相アナログ電流検出回路6で電流/電圧変換し、MPU7は前記インバータの出力電圧指令の電気角に応じて、パワーデバイス制御装置4に与える指令NUL(NVL、NWL)のOFF時間が短い(例えばIGBTのスイッチング時間100μsec以下の)二相を順次選択してディジタル変換する。

前記選択された二相のアナログ出力電圧は、IGBTQ2(IGBTQ4、IGBTQ6)およびフリーホイールダイオードD2(D4、D6)に流れるアナログ電流に追従した電圧であるので、このアナログ出力電圧をディジタル変換することによりインバータの出力電流を精度良く検出することができる。

特に問題となる、変調アーム数が2アーム変調方式の場合でも、インバータの出力電流を精度良く検出することができる。

以下、本発明の実施例を図に基づいて説明する。図6に示すインバータの回路は本発明が実施される回路で、従来の回路構成と同じである。

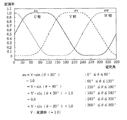

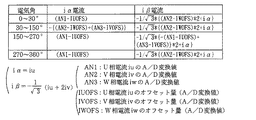

図1は本発明の実施例を示す制御テーブルである。前記制御テーブルは、インバータの三相出力電流のうちアナログ/ディジタル変換する特定の二相を選択する相を予め設定したテーブルである。運転中のインバータの出力電流を三相アナログ電流検出回路6で電流/電圧変換し、MPU7はインバータの出力電圧指令の電気角に応じて、MPU7からパワーデバイス制御装置4に与える指令NUL(NVL、NWL)のOFF時間が短い(例えばIGBTのスイッチング時間100μsec以下の)二相を順次選択してアナログ/ディジタル変換する。

前記制御テーブルにおいて、項目「電気角」はU相の出力電圧指令の電気角を表わし、0゜〜360゜を30゜刻みで分割している。項目「A/D変換1」はアナログ/ディジタル変換する二相のうちの一相を表わし、二相のうちPWMの変調率の高い方の変換対称相である。項目「A/D変換2」は、アナログ/ディジタル変換する二相のうちの前記項目「A/D変換1」の相とは別の一相を表わしている。制御テーブルの項目「A/D変換1」の相と「A/D変換2」の相とでは、「A/D変換1」の相が先にアナログ/ディジタル変換される。

図2は本発明の実施例を説明するための図で、インバータの出力電圧指令の信号波eu、ev、ewである。前記信号波eu、ev、ewは電動機2に与える三相(U相、V相、W相)の出力電圧指令であり、変調アーム数は2アーム変調方式で変調率1.0の場合を示している。なお、図2の式は、変調率V=1.0のときの信号波euを表している。

【0010】

図3は本発明の実施例を説明する図で、図1のA/D変換1とA/D変換2の動作タイミングチャートである。A/D変換1の起動は、MPU7からの項目「A/D変換1」の相への指令NUL(NVL、NWL)がONの期間に行い、A/D変換2の起動はA/D変換1の実行完了後、項目「A/D変換2」の相への指令がONの期間に行う。

図4は本発明の実施例を説明する図で、MPU7は、図6の三相アナログ電流検出回路6により得られたインバータの出力電流U相電流、V相電流、W相電流(図6のAVOUTU,AVOUTV,AVOUTWそれぞれに対応)を読み込んでインバータの出力電流を演算する。2相選択回路11は、前記U相電流、V相電流、W相電流の三相の内2相を順次選択してディジタル変換するブロックで、2相交流電流変換回路12は、直交固定子座標系の二相交流電流への変換ブロックである。なお10の部分は従来技術の演算処理である。

【0011】

図5は、図4の処理ブロック12において、インバータの出力電圧指令の電気角に応じて直交固定子座標系の二相交流電流iα、iβに変換する計算式を表わしている。図5において、項目「電気角]はU相の出力電圧指令の電気角を表わしている。

次に動作について説明する。MPU7は現在出力している前記信号波euの電気角に応じて図1の制御テーブルの項目「A/D変換1」と「A/D変換2」からアナログ/ディジタル変換する二相を選択して、アナログ/ディジタル変換を実行する。この実行において、A/D変換1の相を先にアナログ/ディジタル変換する。

前記A/D変換1とA/D変換2の実行タイミングは、図3に示すように、A/D変換1の実行はMPU7からの項目「A/D変換1」の相への指令NUL(NVL、NWL)がONの期間に行い、A/D変換2の実行はA/D変換1の実行完了後、項目「A/D変換2」の相への指令がONの期間に行う。すなわち、ONの期間のアナログ出力電圧AVOUTU(AVOUTV、AVOUTW)は、IGBTQ2(IGBTQ4、IGBTQ6)およびフリーホイールダイオードD2(D4、D6)に流れるアナログ電流に追従した電圧であるので、このアナログ出力電圧をディジタル変換することにより、インバータの出力電流を精度良く検出することができる。

A/D変換1とA/D変換2の実行で得られた数値を、インバータの出力電圧指令の電気角に応じて直交固定子座標系の二相交流の電流iα、iβに変換する方法は、MPU7が現在出力している前記信号波euの電気角に応じて図5に示す電流iα、iβに変換する計算式を選択して実行する。

【0012】

【発明の効果】

以上述べたように、本発明のインバータの出力電流検出方法によれば、運転中のインバータの三相出力電流を三相アナログ電流検出回路で電流/電圧変換し、インバータの出力電圧指令の電気角に応じて三相のインバータ主回路のうち、下アーム半導体スイッチング素子駆動信号のOFF時間が短い(例えばIGBTのスイッチング時間100μsec以下の)二相を順次選択して、前記三相アナログ電流をディジタル変換することにより、半導体スイッチング素子およびその素子に逆並列接続されたフリーホイールダイオードに流れるアナログ電流に追従したディジタル変換値を得ることができるので、インバータの出力電流を精度良く検出することができる。

特に問題となる、変調アーム数が2アーム変調方式の場合でも、インバータの出力電流を精度良く検出することができる。

【図面の簡単な説明】

【図1】本発明の実施例である制御テーブル

【図2】インバータの出力電圧指令の信号波eu、ev、ewを示す図

【図3】A/D変換1とA/D変換2の実行タイミングチャート

【図4】二相交流の電流iα、iβに変換する処理ブロック図

【図5】二相交流の電流iα、iβに変換する計算式を示す図

【図6】インバータの回路構成図

【図7】三相アナログ電流検出回路の動作を示すタイミングチャート

【符号の説明】

1 直流電源

2 電動機

3 パワーデバイス

4 パワーデバイス制御装置

5 パワーデバイス駆動回路

6 三相アナログ電流検出回路

7 MPU

Claims (5)

- 直列接続した半導体スイッチング素子をオンオフ制御し、直流電圧を3相交流電圧に変換出力するインバータ装置において、

3相全ての前記各下段側半導体スイッチング素子と前記直流電圧の負極側との間に接続された3相の各電流検出用抵抗と、

前記3相の各電流検出用抵抗に基づいて得られる各相電流検出値のうち、電流検出値として用いる2相をインバータ装置の動作制御中に順次切替選択していく電流検出相切替手段を備えたことを特徴とするインバータ装置。 - 前記電流検出相切替手段が選択した2相の各電流検出値を、各々につき当該相の下段側半導体スイッチング素子へのオン指令期間中に検出する電流検出タイミング手段を備えたことを特徴とする請求項1記載のインバータ装置。

- 前記電流検出相切替手段は、出力電圧指令の電圧位相に基づいて電流検出値として用いる2相を選択することを特徴とする請求項1または請求項2記載のインバータ装置。

- 前記電流検出相切替手段は、出力電圧指令値に基づいて電流検出値として用いる2相を選択することを特徴とする請求項1または請求項2記載のインバータ装置。

- 前記電流検出相切替手段は、前記下段側半導体スイッチング素子のオフ指令時間に基づいて電流検出値として用いる2相を選択することを特徴とする請求項1または請求項2記載のインバータ装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP22750996A JP3786142B2 (ja) | 1996-08-09 | 1996-08-09 | インバータ装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP22750996A JP3786142B2 (ja) | 1996-08-09 | 1996-08-09 | インバータ装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH1054852A JPH1054852A (ja) | 1998-02-24 |

| JP3786142B2 true JP3786142B2 (ja) | 2006-06-14 |

Family

ID=16862022

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP22750996A Expired - Fee Related JP3786142B2 (ja) | 1996-08-09 | 1996-08-09 | インバータ装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3786142B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001147243A (ja) | 1999-11-24 | 2001-05-29 | Mitsubishi Electric Corp | アナログ信号検出回路及び半導体電力変換装置の交流側電流検出器 |

| JP2003079157A (ja) * | 2001-08-31 | 2003-03-14 | Fuji Electric Co Ltd | インバータの出力電流検出方法 |

| DE10204423B4 (de) * | 2002-02-04 | 2016-09-01 | Vacuumschmelze Gmbh & Co. Kg | Stromsensor |

| JP4736719B2 (ja) * | 2005-10-31 | 2011-07-27 | 日本精工株式会社 | 電動パワーステアリング装置の制御装置 |

| JP4893248B2 (ja) * | 2006-11-09 | 2012-03-07 | 日本精工株式会社 | 電動パワーステアリング装置 |

| JP5784750B2 (ja) | 2011-12-06 | 2015-09-24 | 三菱電機株式会社 | 電力変換装置 |

| JP7096792B2 (ja) * | 2019-07-19 | 2022-07-06 | 株式会社日立製作所 | 電流計測器および電力変換装置 |

| WO2023120546A1 (ja) * | 2021-12-24 | 2023-06-29 | ニデック株式会社 | 制御装置及び制御方法 |

-

1996

- 1996-08-09 JP JP22750996A patent/JP3786142B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH1054852A (ja) | 1998-02-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3666432B2 (ja) | 電力変換装置及び多相負荷の駆動制御方法 | |

| US6069809A (en) | Resonant inverter apparatus | |

| US5821707A (en) | Inverter controller for brushless direct current motor | |

| KR100960043B1 (ko) | 2상 영구자석 동기 전동기의 공간전압벡터 제어 장치 | |

| JP3786142B2 (ja) | インバータ装置 | |

| JP4031965B2 (ja) | 電動機の制御装置 | |

| JP2018026905A (ja) | モータ制御装置 | |

| JP3808583B2 (ja) | インバータ装置 | |

| JPH11262269A (ja) | パルス幅変調形インバータ装置の制御方法 | |

| JP2006246649A (ja) | インバータ装置 | |

| US20050281068A1 (en) | Control of the mains bridge of a frequency converter | |

| Mahlein et al. | New concepts for matrix converter design | |

| JP2004304925A (ja) | インバータ装置 | |

| JP2004023938A (ja) | インバータ装置及びプロセッサ | |

| JP3774329B2 (ja) | インバータ装置 | |

| JP2012182874A (ja) | モータ制御装置 | |

| JP2003079157A (ja) | インバータの出力電流検出方法 | |

| JP3815034B2 (ja) | 共振形インバータ装置 | |

| JP3788346B2 (ja) | 電圧形pwmインバータの制御装置 | |

| US20200044579A1 (en) | Power conversion device and control method | |

| JPH0698564A (ja) | 電流制御装置 | |

| JP4375506B2 (ja) | インバータ装置およびその電流制限方法 | |

| JP4419312B2 (ja) | 半導体電力変換器 | |

| JP6471670B2 (ja) | 電力制御方法、及び、電力制御装置 | |

| JP2019216566A (ja) | モータ用制御装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040423 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20051226 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060125 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060301 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060314 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090331 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100331 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110331 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120331 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130331 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130331 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140331 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150331 Year of fee payment: 9 |

|

| LAPS | Cancellation because of no payment of annual fees |