JP3784301B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP3784301B2 JP3784301B2 JP2001344484A JP2001344484A JP3784301B2 JP 3784301 B2 JP3784301 B2 JP 3784301B2 JP 2001344484 A JP2001344484 A JP 2001344484A JP 2001344484 A JP2001344484 A JP 2001344484A JP 3784301 B2 JP3784301 B2 JP 3784301B2

- Authority

- JP

- Japan

- Prior art keywords

- column

- bit line

- circuit

- common bit

- bit lines

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/12—Group selection circuits, e.g. for memory block selection, chip selection, array selection

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Static Random-Access Memory (AREA)

- Dram (AREA)

Description

【発明の属する技術分野】

本発明は半導体記憶装置に関し、特に、メモリセルが接続されるビット線が列方向に複数に分割された分割ビット線と、分割ビット線に出力された電圧を列単位で取り出す共通ビット線とを有する半導体記憶装置に関する。

【0002】

【従来の技術】

RAM(Random Access Memory)の低消費電力化、高速化を可能とするビット線階層方式が提案されている。ビット線階層方式では、メモリアレイを複数のバンクに分割する。各バンク内の分割ビット線は実際にメモリセルに接続される。この分割ビット線と平行して共通ビット線が各バンクをまたがって設けられる。共通ビット線はメモリセルに接続されていないため、単位長さあたりの負荷容量が分割ビット線よりも小さい。従って、ビット線階層方式を用いると、階層化しない場合と比較して高速かつ低消費電力な読み出しおよび書き込み動作が可能となる。

【0003】

なお、従来のビット線階層方式は、例えば、「低消費電力、高速LSI技術」(リアライズ社、1998)のP187や、特開2000−207886号公報に開示されている。

【0004】

ビット線分割方式を用いたスタティック型RAM(以下、SRAMと称する)のブロック図の一例を図15に示す。この図に示すように、従来のSRAMは、タイミング制御回路1、ローデコーダ2、ワード線ドライバ3、バンクデコーダ4、カラムデコーダ5、バンクB1〜Bn、プリチャージ回路PC1〜PCp、カラムスイッチCS1〜CSp、および、I/O回路6によって構成されている。

【0005】

ここで、タイミング制御回路1は、アドレス信号、クロック信号、および、制御信号を入力し、これらの信号に基づいて、ローデコーダ2、バンクデコーダ4、カラムデコーダ5、および、プリチャージ回路PC1〜PCpを制御する。

【0006】

ローデコーダ2は、タイミング制御回路1から供給された行入力アドレス信号をデコードし、その結果に応じてワード線ドライバ3を制御して行方向の所定のメモリセル群を選択する。

【0007】

カラムデコーダ5は、タイミング制御回路1から供給された列入力アドレス信号をデコードし、その結果に応じてカラムスイッチCS1〜CSpを制御し、所定のメモリセル群を選択する。

【0008】

ワード線ドライバ3は、ローデコーダ2の制御に応じて、行方向の所定のメモリセル群を選択する。

バンクデコーダ4は、タイミング制御回路1の制御に応じて、バンクB1〜Bnを選択するために各バンクに具備されているバンク制御回路BC1〜BCpを制御する。

【0009】

バンクB1〜Bnは、メモリセル群が列方向に所定の個数単位(この例ではm個単位)で分割されて構成されている。データを読み出す場合またはデータを書き込む場合には、ワード線ドライバ3によって所定のメモリセルが選択され、対応する分割ビット線BL11〜BLp1および補分割ビット線BLX11〜BLXp1と接続され、また、バンク制御回路BC1〜BCpによって所定のバンクが選択され、共通ビット線GBL1〜GBLp、および、補共通ビット線GBLX1〜GBLXpに接続される。

【0010】

メモリセル(MC)C11〜C1m,・・・,Cp1〜Cpmは、データを記憶する最小単位である。

バンク制御回路BC1〜BCpは、バンクデコーダ4の制御に応じてONまたはOFFの状態となり、分割ビット線BL11〜BLp1および補分割ビット線BLX11〜BLXp1を、共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpに接続する。

【0011】

プリチャージ回路PC1〜PCpは、タイミング制御回路1の制御に応じて、読み出し動作の終了後、電荷を失った共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpに対して電荷を補充するプリチャージ動作を行う。

【0012】

カラムスイッチCS1〜CSpは、カラムデコーダ5の制御に応じて、ONまたはOFFの状態になり、所定の列の共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpを、データバスDBおよび補データバスDBXにそれぞれ接続する。

【0013】

I/O回路6は、センスアンプ、ライトアンプ、および、入出力回路から構成され、読み出されたデータをセンスアンプによって増幅して出力するとともに、入力されたデータをライトアンプで増幅してデータバスDBおよび補データバスDBXに送出する。

【0014】

なお、この図においては、バンクB1のみの詳細を示してあるが、バンクB2〜BnについてもバンクB1と同様の構成とされている。

次に、以上の従来例の動作について説明する。

【0015】

先ず、メモリセルC11からデータを読み出す場合を例に挙げて説明する。タイミング制御回路1に読み出し対象となるアドレスが入力されると、タイミング制御回路1は、このアドレスに基づいて、所定の制御信号をローデコーダ2、バンクデコーダ4、および、カラムデコーダ5に供給する。

【0016】

ローデコーダ2は、タイミング制御回路1から供給された行入力アドレス信号をデコードし、ワード線ドライバ3にどのワード線を選択すべきかを通知する。

ワード線ドライバ3は、ローデコーダ2の制御に応じて、所定のワード線をアクティブの状態にする。いまの例では、メモリセルC11が読み出しの対象になっているので、メモリセルC11〜Cp1に接続されているワード線がアクティブの状態にされ、その他はインアクティブの状態にされる。

【0017】

すると、メモリセルC11〜Cp1からデータが読み出され、分割ビット線BL11〜BLp1および補分割ビット線BLX11〜BLXp1に出力電圧が印加されることになる。

【0018】

バンクデコーダ4は、バンクB1に含まれている全てのバンク制御回路BC1〜BCpをONの状態にする。その結果、バンクB1に含まれている分割ビット線BL11〜BLp1および補分割ビット線BLX11〜BLXp1が共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpにそれぞれ接続されるので、メモリセルC11のデータは共通ビット線GBL1および補共通ビット線GBLX1に供給される。このとき、バンク制御回路BC2〜BCpについてもONの状態になるので、メモリセルC21〜Cp1に格納されているデータも読み出されて共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpに出力される。

【0019】

カラムデコーダ5は、タイミング制御回路1から供給された列入力アドレス信号をデコードし、その結果に応じてカラムスイッチCS1〜CSpのうち該当するものをONの状態にする。いまの例では、メモリセルC11が読み出し対象であるので、カラムスイッチCS1がONの状態になり、その他は全てOFFの状態になる。

【0020】

カラムスイッチCS1から出力されたデータは、データバスDBおよび補データバスDBXを経由して、I/O回路6に供給される。

I/O回路6は、このようにして読み出されたデータを内蔵されているセンスアンプで所定の電圧まで昇圧した後、出力する。

【0021】

なお、その他のメモリセルに対する読み出し動作も、前述の場合と同様であるのでその説明は省略する。また、書き込み動作については、I/O回路6側からデータが読み込まれてメモリセルに供給される以外は、前述の場合と同様であるのでその説明も省略する。

【0022】

次に、SRAMにおけるビット線に対する充放電電流について考える。例えば、ビット線階層方式を用いない場合、ビット線の充放電電流は、次式で表される。

【0023】

【数1】

Io = Cb・Vb・f・N ・・・(1)

ここで、

Cb: ビット線容量

Vb: ビット線電位振幅

f: 動作周波数

N: 全列数

である。一方、ビット線階層方式によりメモリアレイをNb個のバンクに分割すると、ビット線の充放電電流は、次式で表される。

【0024】

【数2】

Ib = (Cb/Nb・Vb + Cg・Vg) ・f・N ・・・(2)

ここで、

Cg: 共通ビット線容量

Vg: 共通ビット線電位振幅

である。仮に、メモリアレイを4分割(Nb=4)し、共通ビット線の容量がビット線の半分(Cg=Cb/2)になったとすると、Ibは以下の式で表される。

【0025】

【数3】

Ib = (Cb/4・Vb + Cb/2・Vg) ・f・N ・・・(3)

更に、分割ビット線と共通ビット線の電位振幅が同じ(Vb=Vg)であるとすると、以下の式で表される。

【0026】

【数4】

Ib=3/4・Cb ・ Vb・f・N

=3/4・Io ・・・(4)

となり、1/4(25%)の電流削減となる。

【0027】

【発明が解決しようとする課題】

従来のSRAMでは、カラムデコーダとカラムスイッチによって列選択を行い(カラムマルチプレクス方式)、選択された列のビット線電位振幅をカラムスイッチを通して、共通データバス上に伝え、それをセンスアンプもしくはアウトプットバッファに入力する。センスアンプやアウトプットバッファは、所定の列数Ncに対して一つ共通に設けられる。ビット線階層方式の場合も同様である。

【0028】

しかしながら、実際に選択されるのは一対のビット線であり、残りの(N−1)本のビット線の振幅は利用されることはなく、従って、その分の充放電電流が無駄になるという問題点があった。

【0029】

また、この問題は、共通ビット線の電圧振幅が大きい場合はさらに深刻になる。例えば、図15のバンク制御回路BC1〜BCp中に、ローカルセンスアンプを設けて、分割ビット線BL11〜BLp1および補分割ビット線BLX11〜BLXp1に現れた微小な電圧振幅を増幅して、共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpに大きな電圧振幅を発生させるような場合である。仮に、電源電圧をVddとして、Vb=Vdd/20, Vg=Vdd/2=10Vbとして式(3)と同様の場合を計算すると、以下の式を得る。

【0030】

【数5】

Ib=(Cb/4・Vb + Cb/2・10・Vb) ・f・N

=(1/4 + 5)・Cb ・ Vb・f・N

=21/4 ・Io ・・・(5)

となり、5倍以上の電流増加となる。

【0031】

本発明は、以上のような点に鑑みてなされたものであり、チップ面積を増加することなく、回路を安定動作させて、以上のような無駄な充放電電流を削減することを課題とする。

【0032】

【課題を解決するための手段】

本発明では上記課題を解決するために、図1に示す、メモリセルC11〜C1m,・・・,Cp1〜Cpmが接続されるビット線が列方向に複数に分割された分割ビット線BL11〜BLp1,BLX11〜BLXp1と、分割ビット線BL11〜BLp1,BLX11〜BLXp1に出力された電圧を列単位で取り出す共通ビット線GBL1〜GBLp,GBLX1〜GBLXpとを有する半導体記憶装置において、行入力アドレス信号に応じて行方向の所定のメモリセル群を選択する行方向選択回路RSと、列入力アドレス信号に応じて列方向の所定のメモリセル群を選択する列方向選択回路CSと、前記行方向選択回路RSによって選択されたメモリセル群のそれぞれに接続されている分割ビット線のうち、前記列方向選択回路CSによって選択された列に対応する分割ビット線を対応する共通ビット線に接続し、それ以外の列の分割ビット線については接続しない断続回路S1〜Spと、を有し、前記断続回路S1〜Spは、前記分割ビット線BL11〜BLp1,BLX11〜BLXp1毎に配置されており、前記列方向選択回路CSの選択結果に応じて前記各断続回路S1〜Spを制御するための列方向選択信号線COL1〜COLpが前記共通ビット線GBL1〜GBLp,GBLX1〜GBLXpに平行して配置されていることを特徴とする半導体記憶装置が提供される。

【0033】

ここで、行方向選択回路RSは、行入力アドレス信号に応じて行方向の所定のメモリセル群を選択する。列方向選択回路CSは、列入力アドレス信号に応じて列方向の所定のメモリセル群を選択する。断続回路S1〜Spは、行方向選択回路RSによって選択されたメモリセル群のそれぞれに接続されている分割ビット線のうち、列方向選択回路CSによって選択された列に対応する分割ビット線を対応する共通ビット線に接続し、それ以外の列の分割ビット線については接続しない。

【0034】

【発明の実施の形態】

以下、本発明の実施の形態を図面を参照して説明する。

図1は、本発明の動作原理を説明する原理図である。この図に示すように、本発明の半導体記憶装置は、行方向選択回路RS、列方向選択回路CS、バンクB1〜Bnによって構成されている。また、各バンクは、バンクB1を例に挙げて説明すると、列方向を構成するm個のメモリセルがp列集まって構成されている。

【0035】

各列を構成するメモリセルは、第1列を例に挙げて説明すると、メモリセルC11〜C1mによって構成され、分割ビット線BL11および補分割ビット線BLX11に接続されている。また、分割ビット線BL11および補分割ビット線BLX11は、断続回路S1を介して共通ビット線GBL11および補共通ビット線GBLX1に接続されている。

【0036】

ここで、行方向選択回路RSは、行入力アドレス信号に応じて行方向の所定のメモリセル群を選択する。

列方向選択回路CSは、列入力アドレス信号に応じて列方向の所定のメモリセル群を選択する。

【0037】

断続回路S1〜Spは、行方向選択回路RSによって選択されたメモリセル群のそれぞれに接続されている分割ビット線BL11〜BLp1および補分割ビット線BLX11〜BLXp1のうち、列方向選択回路CSから出力される列方向選択信号COL1〜COLpによって選択された列に対応する分割ビット線および補分割ビット線を対応する共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpに接続し、それ以外の列の分割ビット線については接続しない。

【0038】

次に、以上の原理図の動作について説明する。例えば、読み出し動作を例に挙げて説明すると、先ず、行方向選択回路RSと、列方向選択回路CSに対して、行入力アドレス信号と、列入力アドレス信号がそれぞれ供給される。

【0039】

行方向選択回路RSは、行入力アドレス信号をデコードし、対応する行方向のメモリセル群を選択する。例えば、メモリセルC11が読み出しの対象となっている場合には、行方向選択回路RSは、メモリセルC11〜Cp1を選択する。

【0040】

その結果、メモリセルC11〜Cp1からデータが読み出され、正信号が分割ビット線BL11〜BLp1にそれぞれ出力され、また、補信号が補分割ビット線BLX1〜BLXp1にそれぞれ出力される。

【0041】

次に、列方向選択回路CSは、読み出し対象となるメモリセルが属する列を選択するための列方向選択信号をアクティブの状態にする。いまの例では、メモリセルC11が読み出し対象であるので、列方向選択回路CSは、列方向選択信号COL1をアクティブの状態にし、それ以外の列方向選択信号についてはインアクティブの状態にする。その結果、断続回路S1がONの状態になり、分割ビット線BL11が共通ビット線GBL1に接続され、また、補分割ビット線BLX11が補共通ビット線GBLX1に接続されるので、メモリセルC11から読み出されたデータは、列方向選択回路CSに供給されることになる。

【0042】

なお、このとき、他の断続回路S2〜Spは全てOFFの状態であるので、これらからはデータは出力されないので、共通ビット線GBL2〜GBLpおよび補共通ビット線GBLX2〜GBLXpの電位は変化しない。

【0043】

列方向選択回路CSは、断続回路S1から供給されたデータを図示せぬセンスアンプによって増幅した後、出力する。

なお、以上はメモリセルC11からデータを読み出す際の動作であるが、これ以外のメモリセルからデータを読み出す場合も前述の場合と同様の動作により実行される。

【0044】

また、書き込み動作についても、列方向選択回路CSから所望のメモリセルにデータが供給される以外は、データを読み出す場合と同様であるので、その説明は省略する。

【0045】

以上に説明したように本発明の半導体記憶装置によれば、断続回路S1〜Spにより、行方向選択回路RSによって選択されたメモリセル群のそれぞれに接続されている分割ビット線および補分割ビット線のうち、列方向選択回路CSによって選択された列に対応する分割ビット線および補分割ビット線を対応する共通ビット線および補共通ビット線にそれぞれ接続し、それ以外の列の分割ビット線および補分割ビット線については接続しないようにしたので、読み出し対象となる共通ビット線および補共通ビット線以外にはデータが出力されない構造となり、その結果、その充放電によって浪費される電力を削減することが可能になる。

【0046】

次に、本発明の実施の形態について説明する。

図2は、本発明の第1の実施の形態の構成例を示す図である。この図に示すように、本発明の第1の実施の形態は、タイミング制御回路1、ローデコーダ2、ワード線ドライバ3、バンクデコーダ4、カラムデコーダ5、バンクB1〜Bn、プリチャージ回路PC1〜PCp、カラムスイッチCS1〜CSp、および、I/O回路6によって構成されている。また、バンクB1〜Bnは、バンクB1を例に挙げて説明すると、列方向に配置されたm個のメモリセルC11〜C1mがp列集まって構成されている。各列を構成するメモリセルは、第1列目を例に挙げて説明すると、正信号が印加される分割ビット線BL11と、補信号が印加される補分割ビット線BLX11とに接続され、これらの分割ビット線BL11および補分割ビット線BLX11は、バンク制御回路BC1を介して共通ビット線GBL1および補共通ビット線GBLX1にそれぞれ接続される。

【0047】

ここで、タイミング制御回路1は、アドレス信号、クロック信号、および、制御信号を入力し、これらの信号に基づいて、ローデコーダ2、バンクデコーダ4、カラムデコーダ5、および、プリチャージ回路PC1〜PCpを制御する。

【0048】

ローデコーダ2は、タイミング制御回路1から供給された行入力アドレス信号をデコードし、その結果に応じてワード線ドライバ3を制御し、行方向の所定のメモリセル群を選択する。

【0049】

カラムデコーダ5は、タイミング制御回路1から供給された列入力アドレス信号をデコードし、その結果に応じてカラムスイッチCS1〜CSpを制御し、列方向の所定のメモリセル群を選択する。

【0050】

ワード線ドライバ3は、ローデコーダ2の制御に応じて、行方向の所定のメモリセル群を選択する。

バンクデコーダ4は、タイミング制御回路1の制御に応じて、バンクB1〜Bnを選択するために各バンクに具備されているバンク制御回路BC1〜BCpを制御する。

【0051】

バンクB1〜Bnは、前述したように、メモリセル群が列方向に所定の個数単位(この例ではm個単位)で分割されて構成されている。データを読み出す場合またはデータを書き込む場合には、ワード線ドライバ3によって所定のメモリセルが選択され、対応する分割ビット線BL11〜BLp1および補分割ビット線BLX11〜BLXp1と接続され、また、バンク制御回路BC1〜BCpによって所定のバンクが選択され、共通ビット線GBL1〜GBLp、および、補共通ビット線GBLX1〜GBLXpに接続される。

【0052】

メモリセル(MC)C11〜C1m,・・・,Cp1〜Cpmは、データを記憶する最小単位である。

バンク制御回路BC1〜BCpは、バンクデコーダ4およびカラムデコーダ5の制御に応じて、ONまたはOFFの状態となり、分割ビット線BL11〜BLp1および補分割ビット線BLX11〜BLXp1を、共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpにそれぞれ接続する。

【0053】

図3(A)および図3(B)は、バンク制御回路BC1の分割ビット線BL11および共通ビット線GBL1側の詳細な構成例を示す図である。

図3(A)に示すように、バンク制御回路BC1の分割ビット線BL11および共通ビット線GBL1側は、NチャネルトランジスタQ1およびQ2によって構成されており、バンクデコーダ4からの出力BSと、カラムデコーダ5からの列方向選択信号COL1との論理積に基づいて分割ビット線BL11と共通ビット線GBL1とを接続する構成となっている。なお、補分割ビット線BLX11および補共通ビット線GBLX1側も同様の構成とされており、また、その他のバンク制御回路もバンク制御回路BC1と同様の構成とされている。

【0054】

図3(B)もバンク制御回路BC1の分割ビット線BL11および共通ビット線GBL1側の詳細な構成例を示す図である。

この例では、バンク制御回路BC1の分割ビット線BL11および共通ビット線GBL1側は、トランスファーQ5,Q6およびインバータQ7,Q8によって構成されており、バンクデコーダ4からの出力BSが“H”の状態になるとトランスファーQ5がONの状態になり、また、カラムデコーダ5からの列方向選択信号COL1が“H”の状態になると、トランスファーQ6がONの状態になる。従って、バンクデコーダ4からの出力BSおよび列方向選択信号COL1の双方が“H”の状態になった場合には、トランスファーQ5,Q6の双方がONの状態になり、分割ビット線BL11と共通ビット線GBL1とが接続される。なお、補分割ビット線BLX11および補共通ビット線GBLX1側も同様の構成とされており、また、その他のバンク制御回路もバンク制御回路BC1と同様の構成とされている。

【0055】

図2に戻って、プリチャージ回路PC1〜PCpは、タイミング制御回路1の制御に応じて、読み出し動作の終了後、電荷を失った共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpに対して電荷を補充するプリチャージ動作を行う。

【0056】

カラムスイッチCS1〜CSpは、カラムデコーダ5の制御に応じて、何れかひとつがONの状態になり、他はOFFの状態になって、所定の列の共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpを、データバスDBおよび補データバスDBXに接続する。

【0057】

図4は、カラムスイッチCS1〜CSpの詳細な構成例を示す図である。カラムスイッチCS1を例に挙げて説明すると、カラムスイッチCS1は、インバータG1a,G1d,G1e、および、トランスファーG1b,G1cによって構成されている。トランスファーG1b,G1cは、カラムデコーダ5からの出力信号CD1が“H”の状態になった場合に双方ともにONの状態になり、共通ビット線GBL1とデータバスDB、および、補共通ビット線GBLX1と補データバスDBXとをそれぞれ接続する。また、列方向選択信号COL1は、出力信号CD1がインバータG1d,G1eによって二度反転された出力であるので、結局、カラムデコーダ5からの出力信号CD1と同一の論理の信号となる。

【0058】

なお、列方向選択信号線COL1〜COLpは、共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpと平行に敷設されているので、垂直に敷設した場合に比較してチップ面積が増大することを防止できる。

【0059】

I/O回路6は、センスアンプ、ライトアンプ、および、入出力回路から構成され、読み出されたデータをセンスアンプによって増幅して出力するとともに、入力されたデータをライトアンプで増幅してデータバスDBおよび補データバスDBXに出力する。

【0060】

次に、以上の第1の実施の形態の動作について説明する。

例えば、読み出し動作を例に挙げて説明すると、タイミング制御回路1に読み出し対象となるアドレスが入力されると、タイミング制御回路1は、このアドレスに基づいて、所定の制御信号をローデコーダ2、バンクデコーダ4、および、カラムデコーダ5に供給する。

【0061】

ローデコーダ2は、タイミング制御回路1から供給された行入力アドレス信号をデコードし、ワード線ドライバ3にどのワード線をドライブすべきかを通知する。

【0062】

ワード線ドライバ3は、ローデコーダ2の制御に応じて、所定のワード線をアクティブの状態にする。いまの例では、例えば、メモリセルC11が読み出しの対象になっているとすると、メモリセルC11〜Cp1に接続されているワード線がアクティブの状態にされ、その他はインアクティブの状態にされる。

【0063】

すると、メモリセルC11〜Cp1からデータが読み出され、分割ビット線BL11〜BLp1および補分割ビット線BLX11〜BLXp1に、読み出されたデータに対応する電圧が印加されることになる。

【0064】

カラムデコーダ5は、タイミング制御回路1から供給された列入力アドレス信号をデコードし、その結果に応じて該当するカラムスイッチCS1〜CSpをONの状態にする。いまの例では、メモリセルC11が選択されているので、図4に示す出力信号CD1が“H”の状態になる。その結果、トランスファーG1b,G1cがONの状態になり、共通ビット線GBL1とデータバスDBが接続され、また、補共通ビット線GBL1Xと補共通データバスDBXとが接続される。

【0065】

更に、出力信号COL1が“H”の状態になると、図3に示す、バンク制御回路BC1を構成するトランジスタQ2がONの状態になり、また、このとき、バンクデコーダ4からの信号は“H”の状態であるので、トランジスタQ1もONの状態になり、分割ビット線BL11が共通ビット線GBL1に接続されることになる。同様の動作は、補信号側でも実行されるので、補分割ビット線BLX11が補共通ビット線GBLX1に接続されることになる。

【0066】

なお、このとき、他の列のバンク制御回路BC2〜BCpについては、列方向選択信号COL2〜COLpが“L”の状態であるのでOFFの状態になる。その結果、分割ビット線BL21〜BLp1および補分割ビット線BLX21〜BLXp1は、共通ビット線GBL2〜GBLpおよび補共通ビット線GBLX2〜GBLXpには接続されないので、共通ビット線GBL2〜GBLpおよび補共通ビット線GBLX2〜GBLXpには電圧が出力されないことになる。その結果、これらの共通ビット線GBL2〜GBLpおよび補共通ビット線GBLX2〜GBLXpに対しては充放電電流が流れないので、その分の電力を削減することができる。

【0067】

メモリセルC11から読み出されたデータは、共通ビット線GBL1および補共通ビット線GBLX1を介してデータバスDBおよび補データバスDBXにそれぞれ出力される。

【0068】

I/O回路6は、このようにして読み出されたデータを内蔵されているセンスアンプで所定の電圧まで昇圧した後、出力する。

なお、その他のメモリセルからの読み出し動作も、前述の場合と同様であるのでその説明は省略する。また、書き込み動作については、I/O回路6側からデータが読み込まれてメモリセルに供給される以外は、前述の場合と同様であるのでその説明も省略する。

【0069】

以上に説明したように、本発明の実施の形態によれば、列方向選択信号によりアクセスの対象となっていないバンク制御回路についてはOFFの状態になるようにしたので、不要な共通ビット線および補共通ビット線に対して充放電電流が流れることを防止し、その結果、装置全体の消費電力を削減することができる。

【0070】

具体的には、本発明によれば、1/Ncの共通ビット線のみ電位振幅が得られるため、ビット線階層方式でのビット線の充放電電流は、以下の式で表される。

【0071】

【数6】

Ib=(Cb/Nb・Vb + Cg・Vg/Nc)・f・N ・・・(6)

例えば、メモリアレイを4分割(Nb=4)して、共通ビット線の容量がビット線の半分(Cg=Cb/2)になったとして、1/8(Nc=8)の列選択をすると、充放電電流は以下の式で表される。

【0072】

【数7】

Ib =(Cb/4・Vb + Cb/2・Vg/8)・f・N ・・・(7)

更に、分割ビット線と共通ビット線の電位振幅が同じ(Vb=Vg)であるとすると、充放電電流は以下のように表される。

【0073】

【数8】

Ib=5/16・Cb・Vb・f・N・5/16

=5/16・Io ・・・(8)

その結果、充電電流は11/16(68.75%)となり、大幅な電流削減となる。これは従来のビット線階層方式と比較して2.75倍(=68.75/25)の削減効果である。

【0074】

更に、共通ビット線の電圧振幅が大きいとき、例えば式(5)と同様の場合を計算すると、

【0075】

【数9】

Ib=(Cb/4・Vb+Cb/2・10・Vb/8)・f・N

=(1/4+5/8)・Cb・Vb・f・N

=7/8・Io ・・・(9)

となり、5倍以上の電流増加だったものを、7/8倍と大幅に抑えるとことができる。

【0076】

また、本発明によれば、列方向選択線を共通ビット線および補共通ビット線と並走させるとともに、列方向選択線をカラムスイッチを制御するための信号と共用にするようにしたので、チップ面積を増加させることなく共通ビット線の活性/非活性を制御することが可能になる。例えば、列方向選択信号をカラムスイッチ選択信号と独立に設け、列方向選択信号の信号線をワードラインと並走させる構成とすると、複数のカラムデコーダ線およびバッファリング回路をバンク毎に敷設する必要がある。従って、その分面積が増加するが、本発明ではそのような面積の増大を防止することができる。

【0077】

次に、本発明の第2の実施の形態について説明する。

図5は、本発明の第2の実施の形態の構成例を示す図である。なお、この図において図2の場合と対応する部分には同一の符号を付してあるのでその説明は省略する。

【0078】

図5に示す例では、図2に示す場合と比較して、カラムスイッチCS1〜CSpがそれぞれ書き込み専用のWカラムスイッチWCS1〜WCSpと、読み出し専用のRカラムスイッチRCS1〜RCSpに分割されている。

【0079】

また、この図では、図2の場合と比較して、INPUT回路40およびOUTPUT回路41が新たに設けられ、また、タイミング制御回路1からライトイネーブル信号WE,WEXが新たに設けられている。しかしながら、INPUT回路40およびOUTPUT回路41は、図2に示すI/O回路6を入力機能および出力機能にそれぞれ分割したものであり、また、ライトイネーブル信号WE,WEXは、図2において不図示であったものを説明の便宜に鑑みて新たに表示したものである。

【0080】

ここで、WカラムスイッチWCS1〜WCSpは、データを書き込む際に、カラムデコーダ5の制御に応じてONの状態になり、共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpを書き込み用データバスWDBおよび補書き込み用データバスWDBXにそれぞれ接続する。

【0081】

また、RカラムスイッチRCS1〜RCSpは、データを読み出す際に、カラムデコーダ5の制御に応じてONの状態になり、共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpを読み出し用データバスRDBおよび補読み出し用データバスRDBXにそれぞれ接続する。

【0082】

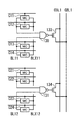

図6は、WカラムスイッチWCS1〜WCSpおよびRカラムスイッチRCS1〜RCSpの詳細な構成例を示す図である。

WカラムスイッチWCS1およびRカラムスイッチRCS1を例に挙げて説明すると、これらのスイッチは、AND素子60、NAND素子61、Nチャネルトランジスタ62,65、Pチャネルトランジスタ63,64、および、インバータ66,67によって構成されている。

【0083】

ここで、AND素子60およびNチャネルトランジスタ62,65がWカラムスイッチWCS1に対応し、また、NAND素子61、Pチャネルトランジスタ63,64、および、インバータ66,67がRカラムスイッチRCS1に対応している。なお、インバータ66,67は、WカラムスイッチWCS1またはRカラムスイッチRCS1の何れに具備してもよい。または、これらとは別個独立の構成とすることも可能である。

【0084】

次に、以上の実施の形態の動作について説明する。なお、第2の実施の形態の動作は、基本的には第1の実施の形態の動作と同様であるので、その差異点となる部分を中心にして以下に説明する。

【0085】

図6に示す、Nチャネルトランジスタ62,65は、AND素子60の出力が“H”の場合、即ち、カラムデコーダ5の出力信号CD1とライトイネーブル信号WEが“H”の状態(データ書き込み状態)の場合にONの状態になり、その結果、共通ビット線GBL1と書き込み用データバスWDBが接続され、また、補共通ビット線GBLX1と補書き込み用データバスWDBXが接続され、データの書き込みが可能になる。

【0086】

一方、Pチャネルトランジスタ63,64は、NAND素子61の出力が“L”の場合、即ち、カラムデコーダ5の出力信号CD1と補ライトイネーブル信号WEXが“H”の状態(データ読み出し状態)の場合にONの状態になり、その結果、共通ビット線GBL1と読み出し用データバスRDBが接続され、また、補共通ビット線GBLX1と補読み出し用データバスWDBXが接続され、データの読み出しが可能になる。

【0087】

ところで、Nチャネルトランジスタ62,65がONの状態である場合には、Pチャネルトランジスタ63,65はOFFの状態であり、また、Pチャネルトランジスタ63,64がONの状態である場合には、Nチャネルトランジスタ62,65はOFFの状態となる。その結果、共通ビット線GBL1および補共通ビット線GBLX1は、読み出し時には読み出し用データバスRDBおよび補読み出し用データバスRDBXのみに接続され、書き込み時には書き込み用データバスWDBおよび補書き込み用データバスWDBXのみに接続されるので、例えば、読み出し時に書き込み用データバスおよび補書き込み用データバスが負荷になることを防止することができる。

【0088】

以上に説明したように、本発明の第2の実施の形態によれば、カラムスイッチを書き込み用のWカラムスイッチWCS1〜WCSpと読み出し用のRカラムスイッチRCS1〜RCSpに分割し、読み出し動作中は書き込み用のWカラムスイッチWCS1〜WCSpをOFFの状態にし、また、書き込み中は読み出し用のRカラムスイッチRCS1〜RCSpをOFFの状態にするようにしたので、読み出し時および書き込み時の駆動負荷を減少させることが可能になり、その結果、装置全体の消費電力を削減することが可能になる。

【0089】

次に、本発明の第3の実施の形態について説明する。

図7は、本発明の第3の実施の形態の構成例を示す図である。なお、この図において、図2に示す場合と対応する部分には同一の符号を付してあるのでその説明は省略する。

【0090】

本発明の第3の実施の形態では、図2の場合に比較して、I/O回路6がINPUT回路40およびOUTPUT回路41に分割されているとともに、カラムスイッチCS1〜CSpがWカラムスイッチWCS1〜WCSpとマルチプレクサ回路80とに分割されている。なお、その他の構成は、図2の場合と同様である。

【0091】

ここで、マルチプレクサ回路80は、カラムデコーダ5からの出力に応じて、共通ビット線GBL1〜GBLpの出力を選択し、OUTPUT回路41に出力する。

【0092】

図8は、マルチプレクサ回路80の詳細な構成例を示す図である。この図に示すように、マルチプレクサ回路80は、クロックトインバータ80−1〜80−pによって構成されている。クロックトインバータ80−1〜80−pは、カラムデコーダ5の出力信号CD1〜CDpが“H”の状態である場合には、CDX1〜CDXp信号を反転して出力し、それ以外の場合にはハイインピーダンス状態になる。

【0093】

次に、本発明の第3の実施の形態の動作について説明する。

例えば、メモリセルC11が読み出し対象になった場合には、前述の第1の実施の形態の場合と同様に、バンク制御回路BC1がONの状態になるので、メモリセルC11から読み出されたデータは、共通ビット線GBL1を介してマルチプレクサ回路80のクロックトインバータ80−1に供給される。

【0094】

このとき、カラムデコーダ5からの出力信号CD1は“H”の状態であり、その他の信号は“L”の状態であるので、クロックトインバータ80−1は動作状態になり、その他のクロックトインバータ80−2〜80−pはハイインピーダンス状態になるので、共通ビット線GBL1に印加されている信号が反転されてOUTPUT回路41に供給される。

【0095】

ところで、クロックトインバータ80−1〜80−pの入力端子は、それを構成するトランジスタのゲートに接続されている。一方、図2に示す回路では、カラムスイッチCS1〜CSpの入力端子(共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXp)はそれを構成するトランジスタのドレインまたはソースに接続されている。ここで、ソース−ドレインを信号が通過する際には、そのON抵抗によって信号が劣化することがあるので、図2の方法ではメモリセルから読み出された信号がカラムスイッチを通過する際に劣化してしまう場合がある。しかしながら、本実施の形態のように、メモリセルから読み出されたデータをゲートに入力するようにすると、そのような信号の劣化を防止することが可能になる。

【0096】

マルチプレクサ回路80からの出力を受けたOUTPUT回路41は、供給された信号をセンスアンプで増幅した後、出力する。

なお、書き込み動作の場合には、INPUT回路40を介して入力されたデータがWカラムスイッチWCS1〜WCSpを介して所望のメモリセルに供給される。例えば、メモリセルC11が書き込み対象である場合には、WカラムスイッチWCS1がONの状態になり、INPUT回路40を介して入力されたデータが共通ビット線GBL1および補共通ビット線GBLX1に供給される。次に、バンク制御回路BC1がONの状態にされ、共通ビット線GBL1および補共通ビット線GBLX1と分割ビット線BL11および補分割ビット線BLX11がそれぞれ接続され、データが分割ビット線BL11および補分割ビット線BLX11に供給される。このとき、ワード線ドライバ3によってメモリセルC11がアクティブの状態にされているので、分割ビット線BL11および補分割ビット線BLX11からメモリセルC11にデータが書き込まれることになる。

【0097】

以上の実施の形態によれば、読み出したデータについては、クロックトインバータを有するマルチプレクサ回路80によって選択するようにしたので、信号の劣化を防止することが可能になる。

【0098】

図9は、マルチプレクサ回路80の他の構成例を示す図である。この図の例は、メモリセルが行方向に8個配置されている場合(p=8である場合)の構成例であり、マルチプレクサ回路80は、NAND素子80a〜80d,80gおよびNOR素子80e,80fによって構成されている。

【0099】

ここで、NAND素子80aは、共通ビット線GBL1とGBL2の論理積を求めた結果を反転して出力する。NAND素子80b〜80dは、共通ビット線GBL3とGBL4、GBL5とGBL6、GBL7とGBL8のそれぞれの論理積を求めた結果を反転して出力する。

【0100】

NOR素子80eは、NAND素子80aと80bの出力の論理和を求めた結果を反転して出力する。また、NOR素子80fは、NAND素子80cと80dの出力の論理和を求めた結果を反転して出力する。

【0101】

NAND素子80gは、NOR素子80eと80fの出力の論理積を反転した結果を出力する。

このような回路によれば、共通ビット線GBL1〜GBL8の全てが“H”の状態である場合には、NAND素子80gから“L”が出力され、また、これらの何れか一つが“L”の状態である場合には“H”が出力されるので、実質的に図8の構成例と同様の動作を実現することができる。

【0102】

また、この実施の形態の場合も、共通ビット線GBL1〜GBL8は、NAND素子80a〜80dに接続されており、一般的にNAND素子の入力端子はゲート端子に接続されているので、図8の場合と同様に、メモリセルから読み出された信号が劣化することを防止できる。

【0103】

次に、本発明の第4の実施の形態について説明する。

図10は、本発明の第4の実施の形態の構成例を示す図である。なお、この図において、図7の場合と対応する部分には同一の符号を付してあるのでその説明は省略する。

【0104】

この実施の形態では、図7に示す場合と比較して、プリチャージ回路PC1〜PCpがプリチャージ回路NPC1〜NPCpに置換されている。その他の構成は、図7の場合と同様である。

【0105】

図11は、プリチャージ回路NPC1〜NPCpおよびWカラムスイッチWCS1〜WCSpの詳細な構成例を示す図である。ここで、プリチャージ回路NPC1およびWカラムスイッチWCS1を例に挙げて説明すると、プリチャージ回路NPC1は、Pチャネルトランジスタ103,104によって構成されている。また、WカラムスイッチWCS1は、AND素子100、Nチャネルトランジスタ101,102、および、インバータ105,106によって構成されている。なお、マルチプレクサ回路80は、図9と同様の構成とされている。

【0106】

次に、以上の実施の形態の動作について説明する。

先ず、読み出し動作について説明する。例えば、メモリセルC11からデータを読み出す場合、前述の場合と同様に、ワード線ドライバ3によってメモリセルC11が選択されるとともに、バンク制御回路BC1がONの状態にされ、データが共通ビット線GBL1および補共通ビット線GBLX1に読み出される。

【0107】

このとき、図11に示すライトイネーブル信号WEは“L”の状態であるので、AND素子100の出力は“L”の状態になり、Nチャネルトランジスタ101,102はOFFの状態になる。その結果、メモリセルC11から読み出されたデータは、書き込み用データバスWDBおよび補書き込み用データバスWDBXには供給されず、マルチプレクサ回路80にのみ供給され、出力されることになる。

【0108】

このとき、カラムデコーダ5の出力信号CD1〜CDpは、CD1以外は全て“L”の状態である。従って、Pチャネルトランジスタ103,104はOFFの状態になり、その他の列に対応するPチャネルトランジスタは全てONの状態になる。ところで、Pチャネルトランジスタは、電源に接続されているので、共通ビット線GBL2〜GBLpおよび補共通ビット線GBLX2〜GBLXpは電源電圧によってプリチャージされることになる。なお、このとき、WカラムスイッチWCS2〜WCSpは全てOFFの状態になっているので、電源電圧が書き込み用データバスWDBおよび補書き込み用データバスWDBXに印加されることはない。

【0109】

続いて、書き込み動作について説明する。例えば、メモリセルC11にデータを書き込む場合、前述の場合と同様に、ワード線ドライバ3によってメモリセルC11が選択されるとともに、バンク制御回路BC1がONの状態にされ、共通ビット線GBL1および補共通ビット線GBLX1がメモリセルC11に接続される。

【0110】

このとき、図11に示すライトイネーブル信号WEは“H”の状態であり、また、カラムデコーダ5の出力信号CD1は“H”の状態であるので、AND素子100の出力は“H”の状態になり、Nチャネルトランジスタ101,102はONの状態になる。その結果、書き込み用データバスWDBおよび補書き込み用データバスWDBXがメモリセルC11に接続され、データの書き込みが可能になる。

【0111】

また、カラムデコーダ5の出力信号CD1〜CDpは、CD1以外は全て“L”の状態である。従って、Pチャネルトランジスタ103,104はOFFの状態になり、その他の列に対応するPチャネルトランジスタは全てONの状態になる。ところで、前述の場合と同様に、Pチャネルトランジスタは、電源に接続されているので、共通ビット線GBL2〜GBLpおよび補共通ビット線GBLX2〜GBLXpは電源電圧によってプリチャージされることになる。なお、このとき、WカラムスイッチWCS2〜WCSpは全てOFFの状態になっているので、電源電圧が書き込み用データバスWDBおよび補書き込み用データバスWDBXに印加されることはない。

【0112】

以上のように、読み出しまたは書き込みの対象となっている列以外は、プリチャージ回路PC1〜PCpによって共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpをプリチャージ状態にするようにしたので、共通ビット線GBL1〜GBLpおよび補共通ビット線GBLX1〜GBLXpがフローティング状態になることを回避することができ、その結果、外部ノイズに対する耐カップリング特性を向上させることが可能になる。

【0113】

次に、本発明の第5の実施の形態について説明する。

図12は、本発明の第5の実施の形態の構成例を示す図である。本発明の第5の実施の形態では、図12に示すように、共通ビット線と、列方向選択信号線との間に電源線が配置されている。即ち、図12の例では、第(N−1)列から第(N+1)列までの配線の配置状態が例示列挙されており、第N列が読み出しの対象となっている状態を示している。

【0114】

この例では、第N列を例に挙げて説明すると、共通ビット線GBLNと列方向選択信号線COLNとの間には、電源電圧線VDDが配置されており、これら3つの配線は全て同一の配線層に配置されている。

【0115】

このように、共通ビット線GBLNおよび列方向選択信号線COLNが同一の配線層に配置されている場合には、小信号が出力されるデータの読み出し時において、列方向選択信号線COLNから共通ビット線GBLNに対してノイズが漏洩する場合がある。

【0116】

そこで、共通ビット線GBLNと列方向選択信号線COLNとの間に、電圧が常に一定である電源電圧線VDDを配置することにより、共通ビット線GBLNをシールドし、ノイズの漏洩を防止することができる。

【0117】

なお、以上の実施の形態では、電源電圧線VDDを配置するようにしたが、接地線を配置することでも同等の効果を得ることが出来る。また、データの読み出し時には一定の電圧を保持する配線を配置することでも同等の効果を期待できる。

【0118】

また、以上の実施の形態では、共通ビット線GBL1〜GBLpのみを例に挙げて説明したが、補共通ビット線GBLX1〜GBLXpに対しても同様の方法によりこれらをシールドすることが可能である。

【0119】

更に、以上の実施の形態では、共通ビット線GBL1〜GBLpと列方向選択信号COL1〜COLpとを同一の階層に配置するようにしたが、これらを異なる階層に配置することも可能である。そのような構成によれば、電源電圧線等をその間に配置しないでも、ノイズの漏洩を防止することができる。

【0120】

次に、本発明の第6の実施の形態について説明する。

図13は、本発明の第6の実施の形態の構成例を示す図である。なお、この図では、発明の重要部分のみが記載されている。

【0121】

図13の例では、第1列目のバンクB1は、メモリセルC11〜C14によって構成され、メモリセルC11,C12の一方の出力は、NAND素子130の一方の端子に接続され、メモリセルC13,C14の一方の出力は、NAND素子130の他方の端子に接続されている。

【0122】

第1列目のバンクB2は、メモリセルC21〜C24によって構成され、メモリセルC21,C22の一方の出力は、NAND素子131の一方の端子に接続され、メモリセルC23,C24の一方の出力は、NAND素子131の他方の端子に接続されている。

【0123】

NAND素子130の出力は、Nチャネルトランジスタ133に入力されており、また、NAND素子131の出力は、Nチャネルトランジスタ134に入力されている。

【0124】

Nチャネルトランジスタ133は、列方向選択信号COL1と共通ビット線GBL1とに接続されている。また、Nチャネルトランジスタ134も同様に、列方向選択信号COL1と共通ビット線GBL1とに接続されている。

【0125】

次に、以上の実施の形態の動作について説明する。

例えば、メモリセルC11が読み出しの対象となっている場合を例に挙げて説明する。その場合、先ず、ワード線によってメモリセルC11が選択され、メモリセルC11に記憶されているデータが出力される。

【0126】

なお、NAND素子130,131の入力端子に接続されている側の分割ビット線は“H”レベルにプルアップされているので、選択されたメモリセルC11を含む分割ビット線は記憶されているデータに応じて“H”または“L”の状態になり、それ以外の分割ビット線については“H”の状態となる。

【0127】

従って、メモリセルC11の出力が“L”の状態である場合には、NAND素子130の上側の入力端子は“L”の状態になり、下側の入力端子は“H”の状態になる。その結果、NAND素子130の出力は“H”の状態になるので、Nチャネルトランジスタ133はONの状態になる。

【0128】

ここで、列方向選択信号COL1の選択された状態を“L”とすると、Nチャネルトランジスタ133がONの状態になり、GBL1は“L”になる。

なお、NAND素子131については、その入力が共に“H”の状態であるので、出力が“L”の状態になる。その結果、Nチャネルトランジスタ134はOFFの状態になり、共通ビット線GBL1の状態には影響しない。

【0129】

一方、メモリセルC11から読み出されたデータが“H”の状態である場合には、NAND素子130の出力は“L”の状態になり、また、NAND素子131の出力も前述のように“L”の状態になるので、Nチャネルトランジスタ133は、OFFの状態になり、GBL1は“H”の状態になる。

【0130】

また、第1列以外では、全てのNAND素子(図示せず)の出力が“L”の状態になるので、GBL2〜GBLpは全て“H”の状態になる。その結果、第1列のみからデータが出力されることになる。

【0131】

以上の説明は、読み出し対象がメモリセルC11である場合についてであるが、他のメモリセルが読み出し対象となった場合でも、前述の場合と同様の動作により、データが読み出されることになる。

【0132】

また、以上の説明では、第1列のメモリセルについての説明であるが、それ以外の列についても同様の動作により、データを読み出すことが可能になる。

以上の実施の形態によれば、図2の実施の形態に比較して、バンクデコーダが不要になるので、回路を簡素化することにより、チップ面積を削減することが可能になる。

【0133】

次に、本発明の第7の実施の形態について説明する。

図14は、本発明の第7の実施の形態の構成例を示す図である。なお、この図において図13と対応する部分には同一の符号を付してあるので、その説明は省略する。

【0134】

この図の例では、Nチャネルトランジスタ140〜143のソース(またはドレイン)端子は列方向選択信号COL1〜COL4にそれぞれ接続され、ドレイン(またはソース)端子は共通ビット線GBLCに全て接続されている。なお、Nチャネルトランジスタ140のゲートは、第1列目のバンクB1に対応するNAND素子130に接続され、Nチャネルトランジスタ141〜143のゲートは、第2列目〜第4列目のバンクB1に対応するNAND素子(不図示)にそれぞれ接続されている。

【0135】

また、Nチャネルトランジスタ150〜153のソース(またはドレイン)端子は列方向選択信号COL1〜COL4にそれぞれ接続され、ドレイン(またはソース)端子は共通ビット線GBLCに全て接続されている。なお、Nチャネルトランジスタ150のゲートは、第1列目のバンクB2に対応するNAND素子131に接続され、Nチャネルトランジスタ151〜153のゲートは、第2列目〜第4列目のバンクB2に対応するNAND素子(不図示)にそれぞれ接続されている。

【0136】

なお、その他の構成は、図13の場合と同様である。

次に、本発明の第7の実施の形態の動作について説明する。

前述のように、メモリセルC11が読み出しの対象となっているとすると、メモリセルC11に格納されているデータが“L”の場合には、NAND素子130の出力は“H”の状態になる。その結果、Nチャネルトランジスタ140がONの状態になり、列方向選択信号COL1に印加されている電圧が共通ビット線GBLCに供給されることになる。列方向選択信号COL1の選択された状態を“L”とすると、共通ビット線GBLCは、“L”の状態になる。

【0137】

また、Nチャネルトランジスタ150は、NAND素子131の出力が“L”の状態であるのでOFFの状態になる。また、その他のNチャネルトランジスタ141〜143およびNチャネルトランジスタ151〜153は全てOFFの状態になる。従って、Nチャネルトランジスタ141〜143およびNチャネルトランジスタ150〜153は、共通ビット線GBLCに対しては影響を与えない。

【0138】

一方、メモリセルC11に格納されているデータが“H”の場合には、NAND素子130の出力は“L”の状態になる。このとき、Nチャネルトランジスタ150は、NAND素子131の出力が“L状態であるのでOFFの状態になる。また、その他のNチャネルトランジスタ141〜143およびNチャネルトランジスタ151〜153は全てOFFの状態になるので、共通ビット線GBLCは、“H”の状態になる。

【0139】

従って、共通ビット線GBLCには、読み出し対象となっているメモリセルから出力されたデータと同相の論理で供給されることになる。なお、このような動作は、何れのメモリセルが選択された場合でも同様に実行されるので、メモリセルに格納されているデータを読み出すことが可能になる。

【0140】

従って、以上の実施によれば、図13の場合と比較して、共通ビット線がGBLCの一本のみでよいので、図13の場合に比較して配線の本数を減少させ、その結果として、チップ面積を更に削減とが可能になる。また、GBLの負荷を減少させることにより、半導体記憶装置の動作を高速化することが可能になる。

【0141】

最後に、第1乃至第7の実施の形態で示した回路は、ほんの一例であり、本発明がこのような場合にのみ限定されるものではないことはいうまでもない。

(付記1) メモリセルが接続されるビット線が列方向に複数に分割された分割ビット線と、分割ビット線に出力された電圧を列単位で取り出す共通ビット線とを有する半導体記憶装置において、

行入力アドレス信号に応じて行方向の所定のメモリセル群を選択する行方向選択回路と、

列入力アドレス信号に応じて列方向の所定のメモリセル群を選択する列方向選択回路と、

前記行方向選択回路によって選択されたメモリセル群のそれぞれに接続されている分割ビット線のうち、前記列方向選択回路によって選択された列に対応する分割ビット線を対応する共通ビット線に接続し、それ以外の列の分割ビット線については接続しない断続回路と、

を有することを特徴とする半導体記憶装置。

【0142】

(付記2) 前記分割ビット線および共通ビット線は、通常の信号用の通常信号線と、補信号用の補信号線の対になっていることを特徴とする付記1記載の半導体記憶装置。

【0143】

(付記3) 前記断続回路は、分割ビット線毎に配置されており、

前記列方向選択回路の選択結果に応じて各断続回路を制御するための列方向選択信号線が前記共通信号線に平行して配置されていることを特徴とする付記1記載の半導体記憶装置。

【0144】

(付記4) 前記共通ビット線と、前記列方向選択信号線とは同一の配線層に配置されており、同一列の前記共通ビット線と前記列方向選択信号線との間には、読み出し時において所定の電位を維持する信号線が配置されていることを特徴とする付記3記載の半導体記憶装置。

【0145】

(付記5) 前記所定の電位を維持する信号線は、電源電圧線、接地電圧線、または、書き込みに係る所定の信号線であることを特徴とする付記3記載の半導体記憶装置。

【0146】

(付記6) 前記共通ビット線と、前記列方向選択信号線とは異なる配線層に配置されていることを特徴とする付記3記載の半導体記憶装置。

(付記7) 前記共通ビット線は、前記列方向選択回路の選択結果に応じてONまたはOFFの状態となるカラムスイッチを介して共通データバスに接続されており、

前記列方向選択信号は、前記カラムスイッチの制御信号と共用されていることを特徴とする付記3記載の半導体記憶装置。

【0147】

(付記8) 前記カラムスイッチは、書き込み専用のカラムスイッチと、読み出し専用のカラムスイッチとを有し、

前記書き込み専用のカラムスイッチは、書き込み用共通データバスに接続され、前記読み出し専用のカラムスイッチは、読み出し用共通データバスに接続されていることを特徴とする付記7記載の半導体記憶装置。

【0148】

(付記9) 前記共通ビット線は、マルチプレクサを介して読み出し用共通データバスに接続されており、

前記マルチプレクサを構成するトランジスタのゲートに対して各共通ビット線が接続されていることを特徴とする付記1記載の半導体記憶装置。

【0149】

(付記10) 前記共通ビット線をプリチャージするプリチャージ回路と、

前記列選択回路によって選択された列に対応するプリチャージ回路については非動作状態とし、他のプリチャージ回路については動作状態に制御するプリチャージ回路制御回路と、

を更に有することを特徴とする付記1記載の半導体記憶装置。

【0150】

(付記11) 前記分割ビット線単位で設けられたトランジスタを有し、

前記トランジスタは、各列を構成する前記共通ビット線と、前記列選択信号線とを、前記分割ビット線の電圧に応じて接続または非接続の状態にすることを特徴とする付記1記載の半導体記憶装置。

【0151】

(付記12) 前記列毎の共通ビット線が1本に統合され、全ての列の出力が合成されて出力されることを特徴とする付記11記載の半導体記憶装置。

【0152】

【発明の効果】

以上説明したように本発明では、メモリセルが接続されるビット線が列方向に複数に分割された分割ビット線と、分割ビット線に出力された電圧を列単位で取り出す共通ビット線とを有する半導体記憶装置において、行入力アドレス信号に応じて行方向の所定のメモリセル群を選択する行方向選択回路と、列入力アドレス信号に応じて列方向の所定のメモリセル群を選択する列方向選択回路と、行方向選択回路によって選択されたメモリセル群のそれぞれに接続されている分割ビット線のうち、列方向選択回路によって選択された列に対応する分割ビット線を対応する共通ビット線に接続し、それ以外の列の分割ビット線については接続しない断続回路と、を設けるようにしたので、アクセス対象になっていない共通ビット線に対する充放電電流の発生を防止することにより、装置全体の消費電力を削減することが可能になる。

【図面の簡単な説明】

【図1】本発明の動作原理を説明する原理図である。

【図2】本発明の第1の実施の形態の構成例を示す回路図である。

【図3】図2に示すバンク制御回路の詳細な構成例を示す回路図である。

【図4】図2に示すカラムスイッチの詳細な構成例を示す回路図である。

【図5】本発明の第2の実施の形態の構成例を示す回路図である。

【図6】図5に示すWカラムスイッチおよびRカラムスイッチの詳細な構成例を示す回路図である。

【図7】本発明の第3の実施の形態の構成例を示す回路図である。

【図8】図7に示すマルチプレクサ回路の詳細な構成例を示す回路図である。

【図9】図7に示すマルチプレクサ回路の他の詳細な構成例を示す回路図である。

【図10】本発明の第4の実施の形態の構成例を示す回路図である。

【図11】図10に示すプリチャージ回路の詳細な構成例を示す回路図である。

【図12】本発明の第5の実施の形態の構成例を示す回路図である。

【図13】本発明の第6の実施の形態の構成例を示す回路図である。

【図14】本発明の第7の実施の形態の構成例を示す回路図である。

【図15】従来の半導体記憶装置の構成例を示す回路図である。

【符号の説明】

B1〜Bn バンク

CS 列方向選択回路

C11〜C1m,Cp1〜Cpm メモリセル

RS 行方向選択回路

S1〜Sp 断続回路

BL11〜BLp1 分割ビット線

BLX11〜BLXp1 補分割ビット線

GBL1〜GBLp 共通ビット線

GBLX1〜GBLXp 補共通ビット線

COL1〜COLp 列方向選択信号線

1 タイミング制御回路

2 ローデコーダ

3 ワード線ドライバ

4 バンクデコーダ

5 カラムデコーダ

6 I/O回路

BC1〜BCp バンク制御回路

PC1〜PCp プリチャージ回路

CS1〜CSp カラムスイッチ

WCS1〜WCSp Wカラムスイッチ

RCS1〜RCSp Rカラムスイッチ

40 INPUT回路

41 OUTPUT回路

80 マルチプレクサ回路

Claims (17)

- メモリセルが接続されるビット線が列方向に複数に分割された分割ビット線と、前記分割ビット線に出力された電圧を列単位で取り出す共通ビット線とを有する半導体記憶装置において、

行入力アドレス信号に応じて行方向の所定のメモリセル群を選択する行方向選択回路と、

列入力アドレス信号に応じて列方向の所定のメモリセル群を選択する列方向選択回路と、

前記行方向選択回路によって選択されたメモリセル群のそれぞれに接続されている前記分割ビット線のうち、前記列方向選択回路によって選択された列に対応する分割ビット線を対応する共通ビット線に接続し、それ以外の列の分割ビット線については接続しない断続回路と、を有し、

前記断続回路は、前記分割ビット線毎に配置されており、

前記列方向選択回路の選択結果に応じて前記各断続回路を制御するための列方向選択信号線が前記共通ビット線に平行して配置されていることを特徴とする半導体記憶装置。 - 前記分割ビット線および前記共通ビット線は、通常の信号用の通常信号線と、補信号用の補信号線の対になっていることを特徴とする請求項1記載の半導体記憶装置。

- 前記共通ビット線と、前記列方向選択信号線とは同一の配線層に配置されており、同一列の前記共通ビット線と前記列方向選択信号線との間には、読み出し時において所定の電位を維持する信号線が配置されていることを特徴とする請求項1記載の半導体記憶装置。

- 前記所定の電位を維持する信号線は、電源電圧線、接地電圧線、または、書き込みに係る所定の信号線であることを特徴とする請求項3記載の半導体記憶装置。

- 前記共通ビット線と、前記列方向選択信号線とは異なる配線層に配置されていることを特徴とする請求項1記載の半導体記憶装置。

- 前記共通ビット線は、前記列方向選択回路の選択結果に応じてONまたはOFFの状態となるカラムスイッチを介して共通データバスに接続されており、

列方向選択信号は、前記カラムスイッチの制御信号と共用されていることを特徴とする請求項1記載の半導体記憶装置。 - 前記カラムスイッチは、書き込み専用のカラムスイッチと、読み出し専用のカラムスイッチとを有し、

前記書き込み専用のカラムスイッチは、書き込み用共通データバスに接続され、前記読み出し専用のカラムスイッチは、読み出し用共通データバスに接続されていることを特徴とする請求項6記載の半導体記憶装置。 - 前記共通ビット線は、マルチプレクサを介して読み出し用共通データバスに接続されており、

前記マルチプレクサを構成するトランジスタのゲートに対して前記各共通ビット線が接続されていることを特徴とする請求項1記載の半導体記憶装置。 - 前記共通ビット線をプリチャージするプリチャージ回路と、

前記列方向選択回路によって選択された列に対応するプリチャージ回路については非動作状態とし、他のプリチャージ回路については動作状態に制御するプリチャージ回路制御回路と、

を更に有することを特徴とする請求項1記載の半導体記憶装置。 - 前記分割ビット線単位で設けられたトランジスタを有し、

前記トランジスタは、各列を構成する前記共通ビット線と、前記列方向選択信号線とを、前記分割ビット線の電圧に応じて接続または非接続の状態にすることを特徴とする請求項1記載の半導体記憶装置。 - 前記列毎の共通ビット線が1本に統合され、全ての列の出力が合成 されて出力されることを特徴とする請求項10記載の半導体記憶装置。

- 複数のメモリセルから成るメモリセルアレイを有する半導体記憶装置において、

前記メモリセルアレイを列方向に分割して形成され、列方向に配置された複数のバンクと、

前記メモリセルが列方向に接続されたビット線を分割して形成され、それぞれのバンクと列に対して設けられる複数の分割ビット線と、

それぞれの列に対して設けられて前記複数のバンクによって共用され、前記分割ビット線に出力される電圧が供給される複数の共通ビット線と、

前記複数の共通ビット線によって共用されるデータバスと、

行入力アドレス信号に応じて行方向の所定のメモリセル群を選択する行方向選択信号を生成する行方向選択回路と、

列入力アドレス信号に応じて列方向の所定のメモリセル群を選択する列方向選択信号を生成する列方向選択回路と、

前記列方向選択信号に応じて前記複数の共通ビット線のうち1本を選択し、選択した該共通ビット線を前記データバスに接続するカラムスイッチと、

それぞれの分割ビット線に対して設けられる断続回路とを有し、

前記断続回路は、前記列方向選択信号に応じて前記分割ビット線のうち1本を選択し、前記行方向選択信号に応じて選択されたメモリセル群に接続された、選択した該分割ビット線を、対応する共通ビット線に接続し、

前記断続回路は、選択した前記分割ビット線以外の分割ビット線を、対応する共通ビット線に接続しないことを特徴とする半導体記憶装置。 - 前記カラムスイッチは、書き込み専用のカラムスイッチと、読み出し専用のカラムスイッチとを有し、

前記書き込み専用のカラムスイッチは、書き込み用共通データバスに接続され、前記読み出し専用のカラムスイッチは、読み出し用共通データバスに接続されていることを特徴とする請求項12記載の半導体記憶装置。 - 前記共通ビット線は、マルチプレクサを介して読み出し用共通データバスに接続されており、

前記マルチプレクサを構成するトランジスタのゲートに対して前記各共通ビット線が接続されていることを特徴とする請求項12記載の半導体記憶装置。 - 前記共通ビット線をプリチャージするプリチャージ回路と、

前記列方向選択回路によって選択された列に対応するプリチャージ回路については非動作状態とし、他のプリチャージ回路については動作状態に制御するプリチャージ回路制御回路と、

を更に有することを特徴とする請求項12記載の半導体記憶装置。 - 前記分割ビット線単位で設けられたトランジスタを有し、

前記トランジスタは、各列を構成する前記共通ビット線と、列方向選択信号線とを、前記分割ビット線の電圧に応じて接続または非接続の状態にすることを特徴とする請求項12記載の半導体記憶装置。 - 前記列毎の共通ビット線が1本に統合され、全ての列の出力が合成されて出力されることを特徴とする請求項16記載の半導体記憶装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001344484A JP3784301B2 (ja) | 2001-11-09 | 2001-11-09 | 半導体記憶装置 |

| US10/202,855 US6741487B2 (en) | 2001-11-09 | 2002-07-26 | Semiconductor memory |

| TW091117067A TW564438B (en) | 2001-11-09 | 2002-07-30 | Semiconductor memory |

| KR1020020048379A KR100847279B1 (ko) | 2001-11-09 | 2002-08-16 | 반도체 기억 장치 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001344484A JP3784301B2 (ja) | 2001-11-09 | 2001-11-09 | 半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003151280A JP2003151280A (ja) | 2003-05-23 |

| JP2003151280A5 JP2003151280A5 (ja) | 2005-04-14 |

| JP3784301B2 true JP3784301B2 (ja) | 2006-06-07 |

Family

ID=19158002

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001344484A Expired - Fee Related JP3784301B2 (ja) | 2001-11-09 | 2001-11-09 | 半導体記憶装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6741487B2 (ja) |

| JP (1) | JP3784301B2 (ja) |

| KR (1) | KR100847279B1 (ja) |

| TW (1) | TW564438B (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004103116A (ja) * | 2002-09-10 | 2004-04-02 | Matsushita Electric Ind Co Ltd | 半導体装置 |

| JP2005063548A (ja) * | 2003-08-11 | 2005-03-10 | Semiconductor Energy Lab Co Ltd | メモリ及びその駆動方法 |

| US7319633B2 (en) * | 2003-12-19 | 2008-01-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US7242624B2 (en) * | 2005-06-14 | 2007-07-10 | Qualcomm Incorporated | Methods and apparatus for reading a full-swing memory array |

| US7286423B2 (en) * | 2006-02-27 | 2007-10-23 | Freescale Semiconductor, Inc. | Bit line precharge in embedded memory |

| US7440335B2 (en) * | 2006-05-23 | 2008-10-21 | Freescale Semiconductor, Inc. | Contention-free hierarchical bit line in embedded memory and method thereof |

| US7750403B2 (en) * | 2006-06-30 | 2010-07-06 | Semiconductor Energy Laboratory Co., Ltd | Semiconductor device and manufacturing method thereof |

| US7477551B2 (en) * | 2006-11-08 | 2009-01-13 | Texas Instruments Incorporated | Systems and methods for reading data from a memory array |

| US20080123437A1 (en) * | 2006-11-29 | 2008-05-29 | Vikas Agarwal | Apparatus for Floating Bitlines in Static Random Access Memory Arrays |

| KR101245298B1 (ko) * | 2007-10-11 | 2013-03-19 | 삼성전자주식회사 | 저항체를 이용한 비휘발성 메모리 장치 |

| JP5315739B2 (ja) * | 2008-03-21 | 2013-10-16 | 富士通株式会社 | メモリ装置、メモリ制御方法 |

| KR101044268B1 (ko) * | 2008-11-28 | 2011-06-28 | 김동철 | 스프링 고정금구 |

| JP5505274B2 (ja) | 2010-11-22 | 2014-05-28 | 富士通セミコンダクター株式会社 | スタティックram |

| JP5772058B2 (ja) * | 2011-02-24 | 2015-09-02 | 富士通セミコンダクター株式会社 | 半導体記憶装置 |

| JP5760829B2 (ja) | 2011-08-09 | 2015-08-12 | 富士通セミコンダクター株式会社 | スタティックram |

| JP5703200B2 (ja) * | 2011-12-01 | 2015-04-15 | 株式会社東芝 | 半導体記憶装置 |

| TWI503821B (zh) * | 2012-07-09 | 2015-10-11 | Faraday Tech Corp | 靜態隨機存取記憶裝置及其位元線電壓控制電路 |

| GB2525904B (en) * | 2014-05-08 | 2018-05-09 | Surecore Ltd | Memory unit |

| JP6620472B2 (ja) * | 2015-09-08 | 2019-12-18 | 凸版印刷株式会社 | 半導体記憶装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2618938B2 (ja) * | 1987-11-25 | 1997-06-11 | 株式会社東芝 | 半導体記憶装置 |

| US5995403A (en) * | 1996-03-29 | 1999-11-30 | Nec Corporation | DRAM having memory cells each using one transfer gate and one capacitor to store plural bit data |

| JP3579205B2 (ja) * | 1996-08-06 | 2004-10-20 | 株式会社ルネサステクノロジ | 半導体記憶装置、半導体装置、データ処理装置及びコンピュータシステム |

| JP2000011639A (ja) * | 1998-06-19 | 2000-01-14 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP2000207886A (ja) | 1999-01-08 | 2000-07-28 | Seiko Epson Corp | 半導体記憶装置 |

-

2001

- 2001-11-09 JP JP2001344484A patent/JP3784301B2/ja not_active Expired - Fee Related

-

2002

- 2002-07-26 US US10/202,855 patent/US6741487B2/en not_active Expired - Fee Related

- 2002-07-30 TW TW091117067A patent/TW564438B/zh not_active IP Right Cessation

- 2002-08-16 KR KR1020020048379A patent/KR100847279B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| US6741487B2 (en) | 2004-05-25 |

| JP2003151280A (ja) | 2003-05-23 |

| KR100847279B1 (ko) | 2008-07-21 |

| KR20030038341A (ko) | 2003-05-16 |

| TW564438B (en) | 2003-12-01 |

| US20030090951A1 (en) | 2003-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3784301B2 (ja) | 半導体記憶装置 | |

| US7248534B2 (en) | Semiconductor memory device | |

| US6862229B2 (en) | Physically alternating sense amplifier activation | |

| US5568428A (en) | Memory device and serial-parallel data transform circuit | |

| CN100385572C (zh) | 半导体装置和半导体存储装置 | |

| JP2000030457A (ja) | 半導体記憶装置 | |

| JPH0373080B2 (ja) | ||

| US20120063241A1 (en) | Semiconductor device and control method thereof | |

| US6768692B2 (en) | Multiple subarray DRAM having a single shared sense amplifier | |

| JPH0766666B2 (ja) | 半導体記憶装置 | |

| US5912853A (en) | Precision sense amplifiers and memories, systems and methods using the same | |

| US5369620A (en) | Dynamic random access memory device having column selector for selecting data lines connectable with bit lines | |

| EP0573046B1 (en) | Semiconductor memory device with single data line pair shared between memory cell arrays | |

| JP2002124086A (ja) | ダイナミックランダムアクセスメモリのための読出データ経路 | |

| US5715210A (en) | Low power semiconductor memory device | |

| EP0454162A2 (en) | Semiconductor memory device | |

| JP2000215668A (ja) | 半導体記憶装置 | |

| KR100378562B1 (ko) | 반도체집적회로장치 | |

| US6434079B2 (en) | Semiconductor memory device for distributing load of input and output lines | |

| US7095673B2 (en) | Semiconductor memory device capable of operating at high speed | |

| JP2740486B2 (ja) | 半導体記憶装置 | |

| JP4002418B2 (ja) | 半導体集積回路 | |

| JP3067060B2 (ja) | 半導体記憶装置 | |

| JPH04238193A (ja) | 半導体記憶装置 | |

| JPH113599A (ja) | 半導体記憶装置及びデータ処理装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040609 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040609 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060314 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060314 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090324 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100324 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100324 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110324 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110324 Year of fee payment: 5 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110324 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110324 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120324 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130324 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140324 Year of fee payment: 8 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |