JP2017216325A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2017216325A JP2017216325A JP2016108367A JP2016108367A JP2017216325A JP 2017216325 A JP2017216325 A JP 2017216325A JP 2016108367 A JP2016108367 A JP 2016108367A JP 2016108367 A JP2016108367 A JP 2016108367A JP 2017216325 A JP2017216325 A JP 2017216325A

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- channel mos

- mos transistor

- diode

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 24

- 230000015556 catabolic process Effects 0.000 claims abstract description 14

- 238000010586 diagram Methods 0.000 description 9

- 230000003068 static effect Effects 0.000 description 4

- 230000004913 activation Effects 0.000 description 3

- 230000005611 electricity Effects 0.000 description 3

- 238000000034 method Methods 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000006378 damage Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000037361 pathway Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H9/00—Emergency protective circuit arrangements for limiting excess current or voltage without disconnection

- H02H9/04—Emergency protective circuit arrangements for limiting excess current or voltage without disconnection responsive to excess voltage

- H02H9/045—Emergency protective circuit arrangements for limiting excess current or voltage without disconnection responsive to excess voltage adapted to a particular application and not provided for elsewhere

- H02H9/046—Emergency protective circuit arrangements for limiting excess current or voltage without disconnection responsive to excess voltage adapted to a particular application and not provided for elsewhere responsive to excess voltage appearing at terminals of integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0248—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection

- H01L27/0251—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0248—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection

- H01L27/0251—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices

- H01L27/0255—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices using diodes as protective elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0248—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection

- H01L27/0251—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices

- H01L27/0266—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices using field effect transistors as protective elements

- H01L27/0285—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices using field effect transistors as protective elements bias arrangements for gate electrode of field effect transistors, e.g. RC networks, voltage partitioning circuits

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

Description

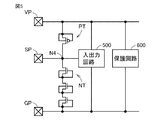

図1は、実施形態1に基づく半導体装置1の全体を説明する図である。

入出力回路520は、ドライバ504,508を駆動する出力論理521と、パッドSPからの抵抗510を介する入力信号を処理する入力回路522と、信号レベルを昇圧/降圧するレベルシフタ523とを含む。

定常状態において、インバータ603のノードN2は「L」レベルに設定されている。従って、NチャネルMOSトランジスタ604はオフしている。また、PチャネルMOSトランジスタ608はオンしている。ノードN2は「L」レベルであるためNチャネルMOSトランジスタ611はオフしており、カレントミラー回路は非活性化されている。

図3に示されるように、パッドSPに入力される電圧レベルが接地線GMよりも電圧レベルが低い場合には、ダイオードD2を介してESD電流がパッドSPに流れ込むことになる。

図4に示されるように、保護ダイオードD1の特性線LAと、保護ダイオードD2の特性線L2とが示されている。

図5に示されるように、保護ダイオードD1およびD2をMOSトランジスタとして構成することが可能である。当該構成とすることにより簡易な構成で保護ダイオードD1,D2の面積を縮小することが可能である。

上記の実施形態1においては、パッドSPに入力される電圧レベルが接地線GMよりも電圧レベルが低い場合にESD耐性を維持する構成について説明した。

図6を参照して、パッドSPに入力される電圧レベルが電源線VMよりも高い場合には、保護ダイオードD1を保護ダイオードD1#に置換するとともに、ノードN4と接地線GMとの間に保護ダイオードD1#を設ける。また、保護ダイオードD2を保護ダイオードD2#に置換するとともに、ノードN4と電源線VMとの間に複数段(3段)の保護ダイオードD2#を設ける点が異なる。その他の構成については同様であるのでその詳細な説明については繰り返さない。

Claims (5)

- 電源配線と、

接地配線と、

前記電源配線と前記接地配線との間に接続された入力回路と、

前記入力回路と接続され、前記接地配線に供給される電圧よりも低い負電圧の入力が可能な入力パッドと、

前記接地配線と、前記入力パッドとの間に設けられた複数の第1ダイオードと、

前記入力パッドと前記電源配線との間に設けられた第2ダイオードとを備え、

前記第2ダイオードの逆バイアス降伏電圧は、各前記第1ダイオードの逆バイアス降伏電圧よりも大きい、半導体装置。 - 電源配線と、

接地配線と、

前記電源配線と前記接地配線との間に接続された入力回路と、

前記入力回路と接続され、前記電源配線に供給される電圧よりも高い電圧の入力が可能な入力パッドと、

前記電源配線と、前記入力パッドとの間に設けられた複数の第1ダイオードと、

前記入力パッドと前記接地配線との間に設けられた第2ダイオードとを備え、

前記第2ダイオードの逆バイアス降伏電圧は、各前記第1ダイオードの逆バイアス降伏電圧よりも大きい、半導体装置。 - 前記電源配線と前記接地配線との間に設けられる静電気放電に対する保護回路とをさらに備える、請求項1または2記載の半導体装置。

- 前記複数の第1ダイオードのウェル濃度と前記第2ダイオードのウェル濃度とは異なる、請求項1〜3のいずれか一項に記載の半導体装置。

- 前記複数の第1ダイオードおよび前記第2ダイオードは、MOSトランジスタで構成される、請求項1〜4のいずれか一項に記載の半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016108367A JP2017216325A (ja) | 2016-05-31 | 2016-05-31 | 半導体装置 |

| US15/480,000 US10361557B2 (en) | 2016-05-31 | 2017-04-05 | Semiconductor device |

| CN201710330480.1A CN107452734A (zh) | 2016-05-31 | 2017-05-11 | 半导体器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016108367A JP2017216325A (ja) | 2016-05-31 | 2016-05-31 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017216325A true JP2017216325A (ja) | 2017-12-07 |

| JP2017216325A5 JP2017216325A5 (ja) | 2019-01-10 |

Family

ID=60420677

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016108367A Pending JP2017216325A (ja) | 2016-05-31 | 2016-05-31 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US10361557B2 (ja) |

| JP (1) | JP2017216325A (ja) |

| CN (1) | CN107452734A (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106449634B (zh) | 2016-09-23 | 2019-06-14 | 矽力杰半导体技术(杭州)有限公司 | 瞬态电压抑制器及其制造方法 |

| KR20190140216A (ko) * | 2018-06-11 | 2019-12-19 | 에스케이하이닉스 주식회사 | Esd 보호 회로를 포함하는 반도체 집적 회로 장치 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07176735A (ja) * | 1993-12-17 | 1995-07-14 | Nec Corp | 半導体回路の入力保護回路 |

| JP2001298157A (ja) * | 2000-04-14 | 2001-10-26 | Nec Corp | 保護回路及びこれを搭載した半導体集積回路 |

| JP2010153779A (ja) * | 2008-12-24 | 2010-07-08 | Magnachip Semiconductor Ltd | 静電気放電保護回路 |

| JP2013201164A (ja) * | 2012-03-23 | 2013-10-03 | Toshiba Corp | 半導体装置 |

| JP2016072349A (ja) * | 2014-09-29 | 2016-05-09 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4736271A (en) * | 1987-06-23 | 1988-04-05 | Signetics Corporation | Protection device utilizing one or more subsurface diodes and associated method of manufacture |

| GB2334633B (en) * | 1998-02-21 | 2002-09-25 | Mitel Corp | Low leakage electrostatic discharge protection system |

| JP2003023084A (ja) | 2001-07-05 | 2003-01-24 | Matsushita Electric Ind Co Ltd | Esd保護回路 |

| JP4942007B2 (ja) * | 2004-10-25 | 2012-05-30 | ルネサスエレクトロニクス株式会社 | 半導体集積回路 |

| JP5232444B2 (ja) * | 2007-11-12 | 2013-07-10 | ルネサスエレクトロニクス株式会社 | 半導体集積回路 |

| KR101145785B1 (ko) * | 2008-12-26 | 2012-05-16 | 에스케이하이닉스 주식회사 | 집적회로 |

| US20130003242A1 (en) * | 2010-07-15 | 2013-01-03 | Kun-Hsien Lin | Transient voltage suppressor for multiple pin assignments |

-

2016

- 2016-05-31 JP JP2016108367A patent/JP2017216325A/ja active Pending

-

2017

- 2017-04-05 US US15/480,000 patent/US10361557B2/en active Active

- 2017-05-11 CN CN201710330480.1A patent/CN107452734A/zh active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07176735A (ja) * | 1993-12-17 | 1995-07-14 | Nec Corp | 半導体回路の入力保護回路 |

| JP2001298157A (ja) * | 2000-04-14 | 2001-10-26 | Nec Corp | 保護回路及びこれを搭載した半導体集積回路 |

| JP2010153779A (ja) * | 2008-12-24 | 2010-07-08 | Magnachip Semiconductor Ltd | 静電気放電保護回路 |

| JP2013201164A (ja) * | 2012-03-23 | 2013-10-03 | Toshiba Corp | 半導体装置 |

| JP2016072349A (ja) * | 2014-09-29 | 2016-05-09 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US10361557B2 (en) | 2019-07-23 |

| US20170346281A1 (en) | 2017-11-30 |

| CN107452734A (zh) | 2017-12-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6503395B2 (ja) | 静電放電回路 | |

| US7589945B2 (en) | Distributed electrostatic discharge protection circuit with varying clamp size | |

| US7593201B2 (en) | Semiconductor integrated circuit | |

| KR101870995B1 (ko) | 반도체 집적회로의 esd 보호 회로 | |

| JP6308925B2 (ja) | 半導体装置 | |

| JP6623139B2 (ja) | Esd保護回路 | |

| JP2015002510A (ja) | 静電気保護回路 | |

| JP2007234718A (ja) | 半導体集積回路装置 | |

| US11411395B2 (en) | Electrostatic discharge protection circuit and operation method | |

| KR102462819B1 (ko) | 반도체 장치 | |

| US8427798B2 (en) | Semiconductor integrated circuit device | |

| JP2014026996A (ja) | Esd保護回路 | |

| JP2016167516A (ja) | 静電気保護回路 | |

| CN105575960B (zh) | 用于芯片上静电放电保护方案的方法及电路 | |

| US9812437B2 (en) | Semiconductor integrated circuit device, and electronic appliance using the same | |

| JP2009147040A (ja) | 半導体集積回路装置 | |

| US10361557B2 (en) | Semiconductor device | |

| JP6784820B2 (ja) | Esd保護回路 | |

| JP6461725B2 (ja) | 半導体装置および内部回路の制御方法 | |

| JP6480051B2 (ja) | 半導体装置 | |

| JP6595948B2 (ja) | 半導体装置 | |

| JP2011119415A (ja) | 半導体集積装置 | |

| KR101131568B1 (ko) | 반도체 장치의 보호 회로 | |

| JP5819489B2 (ja) | 半導体装置 | |

| JP6639631B2 (ja) | 半導体装置および制御装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181120 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20181120 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190913 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190924 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20200317 |