JP2014174131A5 - - Google Patents

Download PDFInfo

- Publication number

- JP2014174131A5 JP2014174131A5 JP2013049807A JP2013049807A JP2014174131A5 JP 2014174131 A5 JP2014174131 A5 JP 2014174131A5 JP 2013049807 A JP2013049807 A JP 2013049807A JP 2013049807 A JP2013049807 A JP 2013049807A JP 2014174131 A5 JP2014174131 A5 JP 2014174131A5

- Authority

- JP

- Japan

- Prior art keywords

- adder

- input

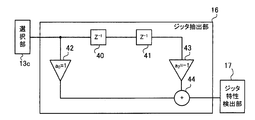

- jitter

- recovered clock

- multiplier

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000605 extraction Methods 0.000 description 3

- 230000003111 delayed effect Effects 0.000 description 2

- 238000012795 verification Methods 0.000 description 2

- 101150071746 Pbsn gene Proteins 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

Images

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013049807A JP2014174131A (ja) | 2013-03-13 | 2013-03-13 | 受信回路、半導体集積回路及び試験方法 |

| US14/176,901 US9255966B2 (en) | 2013-03-13 | 2014-02-10 | Receiver circuit, semiconductor integrated circuit, and test method |

| CN201410076418.0A CN104052439B (zh) | 2013-03-13 | 2014-03-04 | 接收器电路、半导体集成电路和测试方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013049807A JP2014174131A (ja) | 2013-03-13 | 2013-03-13 | 受信回路、半導体集積回路及び試験方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014174131A JP2014174131A (ja) | 2014-09-22 |

| JP2014174131A5 true JP2014174131A5 (enExample) | 2016-01-28 |

Family

ID=51504872

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013049807A Pending JP2014174131A (ja) | 2013-03-13 | 2013-03-13 | 受信回路、半導体集積回路及び試験方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9255966B2 (enExample) |

| JP (1) | JP2014174131A (enExample) |

| CN (1) | CN104052439B (enExample) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20170008077A (ko) * | 2015-07-13 | 2017-01-23 | 에스케이하이닉스 주식회사 | 고속 통신을 위한 인터페이스 회로 및 이를 포함하는 시스템 |

| US9922248B2 (en) * | 2015-09-25 | 2018-03-20 | Intel Corporation | Asynchronous on-die eye scope |

| KR102583236B1 (ko) | 2016-06-30 | 2023-09-27 | 삼성전자주식회사 | Prbs 패턴을 이용한 클럭 데이터 복원 회로, 그리고 그것의 동작 방법 |

| US10014899B2 (en) * | 2016-07-15 | 2018-07-03 | Texas Instruments Incorporated | System and method for built-in self-test of electronic circuits |

| WO2018165976A1 (en) * | 2017-03-17 | 2018-09-20 | Photonic Technologies (Shanghai) Co., Ltd. | Method and apparatus for built-in self-test |

| JP6839359B2 (ja) | 2017-04-28 | 2021-03-10 | 富士通株式会社 | ジッタ測定回路 |

| JP7009984B2 (ja) * | 2017-12-27 | 2022-01-26 | 学校法人東京理科大学 | ノイズ除去フィルタ装置及びノイズ除去方法 |

| US10373671B1 (en) * | 2018-04-09 | 2019-08-06 | Micron Technology, Inc. | Techniques for clock signal jitter generation |

| KR102833443B1 (ko) | 2021-09-13 | 2025-07-10 | 삼성전자주식회사 | 패턴 생성기 및 이를 포함하는 내장 자체 시험 장치 |

| TWI806539B (zh) * | 2022-04-08 | 2023-06-21 | 瑞昱半導體股份有限公司 | 測試系統以及測試方法 |

| CN116248542B (zh) * | 2023-05-12 | 2023-08-08 | 芯耀辉科技有限公司 | 一种用于数字通信中抖动容限测试的装置、方法及系统 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5835501A (en) * | 1996-03-04 | 1998-11-10 | Pmc-Sierra Ltd. | Built-in test scheme for a jitter tolerance test of a clock and data recovery unit |

| JP2002014164A (ja) * | 2000-06-30 | 2002-01-18 | Mitsubishi Electric Corp | レーダ装置 |

| JP2003207544A (ja) | 2002-01-15 | 2003-07-25 | Mitsubishi Electric Corp | Ic内蔵発振回路のテスト装置 |

| US7171601B2 (en) * | 2003-08-21 | 2007-01-30 | Credence Systems Corporation | Programmable jitter generator |

| JP2005098981A (ja) | 2003-08-27 | 2005-04-14 | Nec Corp | 半導体集積回路装置、測定結果管理システム、及び管理サーバ |

| JP3892847B2 (ja) | 2003-12-03 | 2007-03-14 | 株式会社東芝 | 半導体集積回路及び半導体集積回路のテスト方法 |

| US7135904B1 (en) * | 2004-01-12 | 2006-11-14 | Marvell Semiconductor Israel Ltd. | Jitter producing circuitry and methods |

| JP2005233933A (ja) * | 2004-01-19 | 2005-09-02 | Nec Electronics Corp | 組合せ試験方法及び試験装置 |

| JP2005311564A (ja) | 2004-04-20 | 2005-11-04 | Advantest Corp | ジッタ発生回路 |

| JP2008228083A (ja) * | 2007-03-14 | 2008-09-25 | Toshiba Corp | 半導体集積回路 |

| US8289032B2 (en) * | 2007-03-20 | 2012-10-16 | Rambus Inc. | Integrated circuit having receiver jitter tolerance (“JTOL”) measurement |

| JP2011254122A (ja) * | 2009-03-23 | 2011-12-15 | Nec Corp | 回路、制御システム、制御方法及びプログラム |

| JP5256094B2 (ja) * | 2009-03-30 | 2013-08-07 | アンリツ株式会社 | ジッタ測定装置 |

-

2013

- 2013-03-13 JP JP2013049807A patent/JP2014174131A/ja active Pending

-

2014

- 2014-02-10 US US14/176,901 patent/US9255966B2/en not_active Expired - Fee Related

- 2014-03-04 CN CN201410076418.0A patent/CN104052439B/zh not_active Expired - Fee Related

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2014174131A5 (enExample) | ||

| JP5955764B2 (ja) | 半導体装置のデータ出力タイミング制御回路 | |

| CN107836094B (zh) | 时钟恢复电路 | |

| TWI535213B (zh) | 時脈資料回復電路與方法 | |

| KR101518153B1 (ko) | 비트 생성 장치 및 비트 생성 방법 | |

| JP5286845B2 (ja) | データリカバリ回路 | |

| JPWO2011086688A1 (ja) | ビット列生成装置及びビット列生成方法 | |

| JP2016517680A5 (enExample) | ||

| WO2016130360A8 (en) | Circuits for and methods of filtering inter-symbol interference for serdes applications | |

| CN106936531B (zh) | 一种多片基于jesd204b协议adc的同步方法 | |

| JP2011044795A5 (enExample) | ||

| Schmitz et al. | Rössler-based chaotic communication system implemented on FPGA | |

| TWI672035B (zh) | 時脈資料回復裝置與相位控制方法 | |

| CN105577350B (zh) | 一种时钟数据恢复方法及装置 | |

| JP2018520585A5 (enExample) | ||

| TWI666878B (zh) | 時鐘及資料恢復電路及用於執行時鐘及資料恢復的方法 | |

| JP4509699B2 (ja) | 回路解析方法および回路解析装置 | |

| CN104348465B (zh) | 一种控制方法和控制电路 | |

| JP2012244537A (ja) | データリカバリ方法およびデータリカバリ装置 | |

| US9264051B2 (en) | Clock generation circuit and electronic apparatus | |

| CN104917497A (zh) | 一种基于逻辑延时锁定的抗干扰电路及方法 | |

| JP2013074351A5 (enExample) | ||

| CN105516631B (zh) | 一种抗震动的模拟分量视频信号解码电路 | |

| US9379720B1 (en) | Clock recovery circuit | |

| CN103516334B (zh) | 延迟线电路及其相位内插模块 |