JP2011524091A - 電気的に絶縁された支柱のダイオードのための共有ダイオード要素部を有するレール積層体を備えた不揮発性メモリアレイ - Google Patents

電気的に絶縁された支柱のダイオードのための共有ダイオード要素部を有するレール積層体を備えた不揮発性メモリアレイ Download PDFInfo

- Publication number

- JP2011524091A JP2011524091A JP2011513573A JP2011513573A JP2011524091A JP 2011524091 A JP2011524091 A JP 2011524091A JP 2011513573 A JP2011513573 A JP 2011513573A JP 2011513573 A JP2011513573 A JP 2011513573A JP 2011524091 A JP2011524091 A JP 2011524091A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- diode element

- conductor

- integrated circuit

- diode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004020 conductor Substances 0.000 claims abstract description 101

- 230000008859 change Effects 0.000 claims abstract description 40

- 238000004519 manufacturing process Methods 0.000 claims abstract description 19

- 238000000034 method Methods 0.000 claims description 44

- 229910052710 silicon Inorganic materials 0.000 claims description 31

- 239000010703 silicon Substances 0.000 claims description 31

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 30

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical group [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 29

- 229920005591 polysilicon Polymers 0.000 claims description 29

- 239000000758 substrate Substances 0.000 claims description 27

- 238000005530 etching Methods 0.000 claims description 24

- 239000004065 semiconductor Substances 0.000 claims description 9

- 238000003860 storage Methods 0.000 claims description 5

- 238000000059 patterning Methods 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 152

- 239000000463 material Substances 0.000 description 37

- 230000008569 process Effects 0.000 description 24

- 239000012790 adhesive layer Substances 0.000 description 11

- 229920002120 photoresistant polymer Polymers 0.000 description 11

- 239000003989 dielectric material Substances 0.000 description 8

- 230000005684 electric field Effects 0.000 description 7

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 6

- 229910017052 cobalt Inorganic materials 0.000 description 6

- 239000010941 cobalt Substances 0.000 description 6

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 6

- AIOWANYIHSOXQY-UHFFFAOYSA-N cobalt silicon Chemical compound [Si].[Co] AIOWANYIHSOXQY-UHFFFAOYSA-N 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- 239000011229 interlayer Substances 0.000 description 4

- 238000005240 physical vapour deposition Methods 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 238000013500 data storage Methods 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 230000003446 memory effect Effects 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- 238000000137 annealing Methods 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 239000012777 electrically insulating material Substances 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 230000008018 melting Effects 0.000 description 2

- 238000002844 melting Methods 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- ORQBXQOJMQIAOY-UHFFFAOYSA-N nobelium Chemical compound [No] ORQBXQOJMQIAOY-UHFFFAOYSA-N 0.000 description 2

- 229910000314 transition metal oxide Inorganic materials 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000005387 chalcogenide glass Substances 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 238000011065 in-situ storage Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000001465 metallisation Methods 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 230000007935 neutral effect Effects 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920006254 polymer film Polymers 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- MAKDTFFYCIMFQP-UHFFFAOYSA-N titanium tungsten Chemical compound [Ti].[W] MAKDTFFYCIMFQP-UHFFFAOYSA-N 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- -1 tungsten nitride Chemical class 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B20/00—Read-only memory [ROM] devices

- H10B20/10—ROM devices comprising bipolar components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/20—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having two electrodes, e.g. diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

Landscapes

- Semiconductor Memories (AREA)

Abstract

Description

Claims (15)

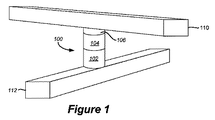

- 基板の上方を第1方向に伸びている第1導体と、

第2導体および第1ダイオード要素の第1部分を備える第1の一連の帯部と、

前記第1導体と前記第1の一連の帯部との間に形成されている支柱と、を備え、

前記第1の一連の帯部は前記基板の上方を第2方向に伸びており、

前記第2方向は前記第1方向に略直交しており、

前記支柱は、前記第1導体と前記第1の一連の帯部との間に直列に存在する、前記第1ダイオード要素の第2部分と、第2ダイオード要素と、状態変化素子とを含んでいる、集積回路装置。 - 前記第1ダイオード要素の前記第1部分は、ポリシリコンの真性層を備え、

前記第1ダイオード要素の前記第2部分は、ポリシリコンの真性層を備える、

請求項1に記載の集積回路装置。 - 前記第2ダイオード要素は、第1導電型の高濃度にドープされたシリコン領域を備える、

請求項1または2に記載の集積回路装置。 - 前記第1の一連の帯部は、

前記第2導体と前記第1ダイオード要素の前記第1部分との間に形成された、第2導電型の高濃度にドープされたポリシリコン領域をさらに備える、

請求項3に記載の集積回路装置。 - 前記第1ダイオード要素の前記第1部分は、第1導電型の低濃度にドープされたポリシリコンの層を備え、

前記第1ダイオード要素の前記第2部分は、第1導電型の低濃度にドープされたポリシリコンの層を備え、

前記第2ダイオード要素は、第2導電型の高濃度にドープされたポリシリコン領域を備え、

前記第2導電型は前記第1導電型と反対の型である、

請求項1に記載の集積回路装置。 - 前記状態変化素子はアンチヒューズである、

請求項1ないし5の何れか1項に記載の集積回路装置。 - 前記アンチヒューズは、前記第1要素の前記第2部分と前記第2ダイオード要素との間に形成されている、

請求項6に記載の集積回路装置。 - 前記支柱は、前記第1ダイオード要素、前記第2ダイオード要素および前記状態変化素子と直列なアンチヒューズをさらに備える、

請求項1ないし5の何れか1項に記載の集積回路装置。 - 前記第1導体、前記第2導体、前記第1ダイオード要素の前記第1部分、前記第1ダイオード要素の前記第2部分、および前記第2ダイオード要素は、少なくとも1つの不揮発性記憶素子を形成する、

請求項1ないし8の何れか1項に記載の集積回路装置。 - 前記集積回路は、モノリシックな3次元の不揮発性メモリアレイを備え、

前記少なくとも1つの不揮発性記憶素子は、前記モノリシックな3次元の不揮発性メモリアレイの第1メモリレベルで形成されており、

前記集積回路は、少なくとも1つの追加的なメモリレベルを備えている、

請求項9に記載の集積回路装置。 - 基板の上方の第1高さに、略平行および略同一平面内の複数の第1導体を形成するステップを備え、

前記第1導体は第1方向に伸びており、

基板の上方の第2高さに、略平行および略同一平面内の複数のレール積層体を形成するステップを備え、

前記レール積層体は前記第1方向と略直交する第2方向に伸びており、

レール積層体の各々は、第2導体と、前記レール積層体に関連する複数のダイオードについての第1ダイオード要素の第1部分を含んでおり、

複数の第1導体と複数のレール積層体との交差点の間に、複数の支柱を形成するステップを備え、

前記複数の支柱は、第1レール積層体と前記複数の第1導体との間に形成されている第1の支柱群を備え、

前記第1の支柱群の各々は、前記第1レール積層体に関連する前記複数のダイオードについての前記第1ダイオード要素の第2部分と、第2ダイオード要素と、状態変化素子を備える、

集積回路装置の製造方法。 - 前記第1支柱群内の各々の支柱の前記第2ダイオード要素は、第1導電型の高濃度にドープされたポリシリコン層であり、

各々のレール積層体の前記第1ダイオード要素の第1部分は、ポリシリコンの真性層であり、

前記第1支柱群内の各々の支柱の前記第1ダイオード要素の前記第2部分は、ポリシリコンの真性層である、

請求項11に記載の方法。 - 複数の第1導体、前記第2導体、前記第1ダイオード要素、前記第2ダイオード要素、および前記状態変化素子は、複数の不揮発性記憶素子を形成し、

前記不揮発性半導体メモリは、モノリシックな3次元の不揮発性メモリアレイを備え、

前記複数の不揮発性記憶素子は、前記モノリシックな3次元の不揮発性メモリアレイの第1メモリレベルで形成されており、

前記集積回路は、少なくとも1つの追加的なメモリレベルを備えている、

請求項11または12に記載の方法。 - 前記基板上方の前記第2高さは、前記基板上方の前記第1高さよりも高い、

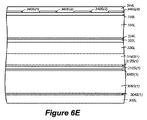

請求項11ないし13の何れか1項に記載の方法。 - 第1の導電層を基板上に形成するステップを備え、

高濃度にドープされたポリシリコン層を前記第1の導電層の表面に形成するステップを備え、

前記高濃度にドープされたポリシリコン層の表面にアンチヒューズ層を形成するステップを備え、

前記アンチヒューズ層の表面に第1の真性ポリシリコン層を形成するステップを備え、

前記第1の真性ポリシリコン層の表面に第1パターンを適用するステップを備え、

第1の導電層、高濃度にドープされたポリシリコン層、アンチヒューズ層、および第1の真性ポリシリコン層を、前記第1パターンに従ってエッチングするステップを備え、

パターニングおよびエッチングは、前記第1方向に伸びる各層の帯部を形成し、

前記帯部は、前記複数の第1導体を備え、

パターニングおよびエッチングの後に、前記第1の真性ポリシリコン層の表面に第2の真性ポリシリコン層を形成するステップを備え、

前記第2の真性ポリシリコン層の表面に第2の導電層を形成するステップを備え、

前記第2の導電層の表面に第2パターンを適用するステップを備え、

前記複数のレール積層体を形成するために、前記第2の導電層および前記第2の真性ポリシリコン層を前記第2パターンに従ってエッチングするステップを備え、

前記第2の真性ポリシリコン層は、各レール積層体の前記第1ダイオード要素の前記第1部分を形成しており、

前記第2導電層は、各レール積層体の前記第2導体を形成しており、

前記複数の支柱を形成するために、第1の真性ポリシリコン層、前記アンチヒューズ層、および前記高濃度にドープされたポリシリコン層を、前記第2パターンに従ってエッチングするステップを備える、

請求項19に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/139,435 US8154005B2 (en) | 2008-06-13 | 2008-06-13 | Non-volatile memory arrays comprising rail stacks with a shared diode component portion for diodes of electrically isolated pillars |

| US12/139,435 | 2008-06-13 | ||

| PCT/US2009/046001 WO2009152001A1 (en) | 2008-06-13 | 2009-06-02 | Non-volatile memory arrays comprising rail stacks with a shared diode component portion for diodes of electrically isolated pillars |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011524091A true JP2011524091A (ja) | 2011-08-25 |

| JP2011524091A5 JP2011524091A5 (ja) | 2012-05-24 |

Family

ID=40933694

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011513573A Pending JP2011524091A (ja) | 2008-06-13 | 2009-06-02 | 電気的に絶縁された支柱のダイオードのための共有ダイオード要素部を有するレール積層体を備えた不揮発性メモリアレイ |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US8154005B2 (ja) |

| EP (1) | EP2286453A1 (ja) |

| JP (1) | JP2011524091A (ja) |

| KR (1) | KR20110039260A (ja) |

| CN (1) | CN102067315B (ja) |

| TW (1) | TWI582907B (ja) |

| WO (1) | WO2009152001A1 (ja) |

Families Citing this family (57)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8154005B2 (en) | 2008-06-13 | 2012-04-10 | Sandisk 3D Llc | Non-volatile memory arrays comprising rail stacks with a shared diode component portion for diodes of electrically isolated pillars |

| US8105867B2 (en) * | 2008-11-18 | 2012-01-31 | Sandisk 3D Llc | Self-aligned three-dimensional non-volatile memory fabrication |

| US8120068B2 (en) * | 2008-12-24 | 2012-02-21 | Sandisk 3D Llc | Three-dimensional memory structures having shared pillar memory cells |

| US7978498B2 (en) * | 2009-04-03 | 2011-07-12 | Sandisk 3D, Llc | Programming non-volatile storage element using current from other element |

| US8270199B2 (en) * | 2009-04-03 | 2012-09-18 | Sandisk 3D Llc | Cross point non-volatile memory cell |

| US8139391B2 (en) * | 2009-04-03 | 2012-03-20 | Sandisk 3D Llc | Multi-bit resistance-switching memory cell |

| JP2011129737A (ja) * | 2009-12-18 | 2011-06-30 | Toshiba Corp | 半導体記憶装置の製造方法及び半導体記憶装置 |

| WO2011156787A2 (en) * | 2010-06-11 | 2011-12-15 | Crossbar, Inc. | Pillar structure for memory device and method |

| US9224496B2 (en) | 2010-08-11 | 2015-12-29 | Shine C. Chung | Circuit and system of aggregated area anti-fuse in CMOS processes |

| US9711237B2 (en) | 2010-08-20 | 2017-07-18 | Attopsemi Technology Co., Ltd. | Method and structure for reliable electrical fuse programming |

| US9496033B2 (en) | 2010-08-20 | 2016-11-15 | Attopsemi Technology Co., Ltd | Method and system of programmable resistive devices with read capability using a low supply voltage |

| US9070437B2 (en) | 2010-08-20 | 2015-06-30 | Shine C. Chung | Circuit and system of using junction diode as program selector for one-time programmable devices with heat sink |

| US9824768B2 (en) | 2015-03-22 | 2017-11-21 | Attopsemi Technology Co., Ltd | Integrated OTP memory for providing MTP memory |

| US10249379B2 (en) | 2010-08-20 | 2019-04-02 | Attopsemi Technology Co., Ltd | One-time programmable devices having program selector for electrical fuses with extended area |

| US8804398B2 (en) | 2010-08-20 | 2014-08-12 | Shine C. Chung | Reversible resistive memory using diodes formed in CMOS processes as program selectors |

| US8830720B2 (en) | 2010-08-20 | 2014-09-09 | Shine C. Chung | Circuit and system of using junction diode as program selector and MOS as read selector for one-time programmable devices |

| US9431127B2 (en) | 2010-08-20 | 2016-08-30 | Shine C. Chung | Circuit and system of using junction diode as program selector for metal fuses for one-time programmable devices |

| US9251893B2 (en) | 2010-08-20 | 2016-02-02 | Shine C. Chung | Multiple-bit programmable resistive memory using diode as program selector |

| US9042153B2 (en) | 2010-08-20 | 2015-05-26 | Shine C. Chung | Programmable resistive memory unit with multiple cells to improve yield and reliability |

| US9818478B2 (en) * | 2012-12-07 | 2017-11-14 | Attopsemi Technology Co., Ltd | Programmable resistive device and memory using diode as selector |

| US9025357B2 (en) | 2010-08-20 | 2015-05-05 | Shine C. Chung | Programmable resistive memory unit with data and reference cells |

| US10916317B2 (en) | 2010-08-20 | 2021-02-09 | Attopsemi Technology Co., Ltd | Programmable resistance memory on thin film transistor technology |

| US9236141B2 (en) | 2010-08-20 | 2016-01-12 | Shine C. Chung | Circuit and system of using junction diode of MOS as program selector for programmable resistive devices |

| US9460807B2 (en) | 2010-08-20 | 2016-10-04 | Shine C. Chung | One-time programmable memory devices using FinFET technology |

| US9349773B2 (en) | 2010-08-20 | 2016-05-24 | Shine C. Chung | Memory devices using a plurality of diodes as program selectors for memory cells |

| US10229746B2 (en) | 2010-08-20 | 2019-03-12 | Attopsemi Technology Co., Ltd | OTP memory with high data security |

| US10923204B2 (en) | 2010-08-20 | 2021-02-16 | Attopsemi Technology Co., Ltd | Fully testible OTP memory |

| US9019742B2 (en) | 2010-08-20 | 2015-04-28 | Shine C. Chung | Multiple-state one-time programmable (OTP) memory to function as multi-time programmable (MTP) memory |

| US8488359B2 (en) | 2010-08-20 | 2013-07-16 | Shine C. Chung | Circuit and system of using junction diode as program selector for one-time programmable devices |

| JP5422534B2 (ja) * | 2010-10-14 | 2014-02-19 | 株式会社東芝 | 不揮発性抵抗変化素子および不揮発性抵抗変化素子の製造方法 |

| US8913449B2 (en) | 2012-03-11 | 2014-12-16 | Shine C. Chung | System and method of in-system repairs or configurations for memories |

| US8923085B2 (en) | 2010-11-03 | 2014-12-30 | Shine C. Chung | Low-pin-count non-volatile memory embedded in a integrated circuit without any additional pins for access |

| US9019791B2 (en) | 2010-11-03 | 2015-04-28 | Shine C. Chung | Low-pin-count non-volatile memory interface for 3D IC |

| US8988965B2 (en) | 2010-11-03 | 2015-03-24 | Shine C. Chung | Low-pin-count non-volatile memory interface |

| CN102544011A (zh) * | 2010-12-08 | 2012-07-04 | 庄建祥 | 反熔丝存储器及电子系统 |

| US10192615B2 (en) | 2011-02-14 | 2019-01-29 | Attopsemi Technology Co., Ltd | One-time programmable devices having a semiconductor fin structure with a divided active region |

| US10586832B2 (en) | 2011-02-14 | 2020-03-10 | Attopsemi Technology Co., Ltd | One-time programmable devices using gate-all-around structures |

| US8848423B2 (en) | 2011-02-14 | 2014-09-30 | Shine C. Chung | Circuit and system of using FinFET for building programmable resistive devices |

| JP2013065772A (ja) * | 2011-09-20 | 2013-04-11 | Toshiba Corp | 半導体装置の製造方法 |

| US9324849B2 (en) | 2011-11-15 | 2016-04-26 | Shine C. Chung | Structures and techniques for using semiconductor body to construct SCR, DIAC, or TRIAC |

| US9136261B2 (en) | 2011-11-15 | 2015-09-15 | Shine C. Chung | Structures and techniques for using mesh-structure diodes for electro-static discharge (ESD) protection |

| US8912576B2 (en) | 2011-11-15 | 2014-12-16 | Shine C. Chung | Structures and techniques for using semiconductor body to construct bipolar junction transistors |

| US9007804B2 (en) | 2012-02-06 | 2015-04-14 | Shine C. Chung | Circuit and system of protective mechanisms for programmable resistive memories |

| US8861249B2 (en) | 2012-02-06 | 2014-10-14 | Shine C. Chung | Circuit and system of a low density one-time programmable memory |

| US8917533B2 (en) | 2012-02-06 | 2014-12-23 | Shine C. Chung | Circuit and system for testing a one-time programmable (OTP) memory |

| US9076526B2 (en) | 2012-09-10 | 2015-07-07 | Shine C. Chung | OTP memories functioning as an MTP memory |

| US9183897B2 (en) | 2012-09-30 | 2015-11-10 | Shine C. Chung | Circuits and methods of a self-timed high speed SRAM |

| US9324447B2 (en) | 2012-11-20 | 2016-04-26 | Shine C. Chung | Circuit and system for concurrently programming multiple bits of OTP memory devices |

| US9178143B2 (en) * | 2013-07-29 | 2015-11-03 | Industrial Technology Research Institute | Resistive memory structure |

| US9412473B2 (en) | 2014-06-16 | 2016-08-09 | Shine C. Chung | System and method of a novel redundancy scheme for OTP |

| KR102471608B1 (ko) * | 2016-06-03 | 2022-11-29 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그의 구동 방법 |

| US10726914B2 (en) | 2017-04-14 | 2020-07-28 | Attopsemi Technology Co. Ltd | Programmable resistive memories with low power read operation and novel sensing scheme |

| US11615859B2 (en) | 2017-04-14 | 2023-03-28 | Attopsemi Technology Co., Ltd | One-time programmable memories with ultra-low power read operation and novel sensing scheme |

| US11062786B2 (en) | 2017-04-14 | 2021-07-13 | Attopsemi Technology Co., Ltd | One-time programmable memories with low power read operation and novel sensing scheme |

| US10535413B2 (en) | 2017-04-14 | 2020-01-14 | Attopsemi Technology Co., Ltd | Low power read operation for programmable resistive memories |

| US10770160B2 (en) | 2017-11-30 | 2020-09-08 | Attopsemi Technology Co., Ltd | Programmable resistive memory formed by bit slices from a standard cell library |

| KR102682821B1 (ko) | 2019-01-25 | 2024-07-08 | 삼성전자주식회사 | 가변 저항 메모리 장치 |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6420215B1 (en) * | 2000-04-28 | 2002-07-16 | Matrix Semiconductor, Inc. | Three-dimensional memory array and method of fabrication |

| US6525953B1 (en) * | 2001-08-13 | 2003-02-25 | Matrix Semiconductor, Inc. | Vertically-stacked, field-programmable, nonvolatile memory and method of fabrication |

| JP2003204045A (ja) * | 2001-11-26 | 2003-07-18 | Hewlett Packard Co <Hp> | 4つの状態を取り得るメモリセルを有するメモリデバイス |

| US6642603B1 (en) * | 2002-06-27 | 2003-11-04 | Matrix Semiconductor, Inc. | Same conductivity type highly-doped regions for antifuse memory cell |

| US20040002186A1 (en) * | 2002-06-27 | 2004-01-01 | Vyvoda Michael A. | Electrically isolated pillars in active devices |

| JP2004228561A (ja) * | 2003-01-23 | 2004-08-12 | Sharp Corp | デュアルトレンチで隔離されたクロスポイントメモリアレイとその製造方法 |

| US6777773B2 (en) * | 2000-08-14 | 2004-08-17 | Matrix Semiconductor, Inc. | Memory cell with antifuse layer formed at diode junction |

| US20050242386A1 (en) * | 2004-04-29 | 2005-11-03 | Kern-Huat Ang | Memory cell and method of fabricating the same |

| JP2009283513A (ja) * | 2008-05-19 | 2009-12-03 | Toshiba Corp | 不揮発性記憶装置及びその製造方法 |

Family Cites Families (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| AU562641B2 (en) | 1983-01-18 | 1987-06-18 | Energy Conversion Devices Inc. | Electronic matrix array |

| US5835396A (en) | 1996-10-17 | 1998-11-10 | Zhang; Guobiao | Three-dimensional read-only memory |

| US7157314B2 (en) | 1998-11-16 | 2007-01-02 | Sandisk Corporation | Vertically stacked field programmable nonvolatile memory and method of fabrication |

| US6034882A (en) * | 1998-11-16 | 2000-03-07 | Matrix Semiconductor, Inc. | Vertically stacked field programmable nonvolatile memory and method of fabrication |

| CN1278645A (zh) * | 1999-06-22 | 2001-01-03 | 张世熹 | 高密度集成电路之存储器 |

| US8575719B2 (en) | 2000-04-28 | 2013-11-05 | Sandisk 3D Llc | Silicon nitride antifuse for use in diode-antifuse memory arrays |

| US6631085B2 (en) | 2000-04-28 | 2003-10-07 | Matrix Semiconductor, Inc. | Three-dimensional memory array incorporating serial chain diode stack |

| TW540086B (en) * | 2000-08-14 | 2003-07-01 | Matrix Semiconductor Inc | Dense arrays and charge storage devices, and methods for making same |

| US6515888B2 (en) | 2000-08-14 | 2003-02-04 | Matrix Semiconductor, Inc. | Low cost three-dimensional memory array |

| US6627530B2 (en) | 2000-12-22 | 2003-09-30 | Matrix Semiconductor, Inc. | Patterning three dimensional structures |

| US6356477B1 (en) | 2001-01-29 | 2002-03-12 | Hewlett Packard Company | Cross point memory array including shared devices for blocking sneak path currents |

| US6579760B1 (en) | 2002-03-28 | 2003-06-17 | Macronix International Co., Ltd. | Self-aligned, programmable phase change memory |

| US7623370B2 (en) | 2002-04-04 | 2009-11-24 | Kabushiki Kaisha Toshiba | Resistance change memory device |

| US7081377B2 (en) | 2002-06-27 | 2006-07-25 | Sandisk 3D Llc | Three-dimensional memory |

| JP2006511965A (ja) | 2002-12-19 | 2006-04-06 | マトリックス セミコンダクター インコーポレイテッド | 高密度不揮発性メモリを製作するための改良された方法 |

| US7285464B2 (en) | 2002-12-19 | 2007-10-23 | Sandisk 3D Llc | Nonvolatile memory cell comprising a reduced height vertical diode |

| US7005350B2 (en) | 2002-12-31 | 2006-02-28 | Matrix Semiconductor, Inc. | Method for fabricating programmable memory array structures incorporating series-connected transistor strings |

| US6822903B2 (en) | 2003-03-31 | 2004-11-23 | Matrix Semiconductor, Inc. | Apparatus and method for disturb-free programming of passive element memory cells |

| US6951780B1 (en) | 2003-12-18 | 2005-10-04 | Matrix Semiconductor, Inc. | Selective oxidation of silicon in diode, TFT, and monolithic three dimensional memory arrays |

| US7224013B2 (en) | 2004-09-29 | 2007-05-29 | Sandisk 3D Llc | Junction diode comprising varying semiconductor compositions |

| US7405465B2 (en) * | 2004-09-29 | 2008-07-29 | Sandisk 3D Llc | Deposited semiconductor structure to minimize n-type dopant diffusion and method of making |

| US20060250836A1 (en) | 2005-05-09 | 2006-11-09 | Matrix Semiconductor, Inc. | Rewriteable memory cell comprising a diode and a resistance-switching material |

| WO2008016833A2 (en) * | 2006-07-31 | 2008-02-07 | Sandisk 3D Llc | Increasing write voltage pulse operations in non-volatile memory |

| WO2008016420A2 (en) * | 2006-07-31 | 2008-02-07 | Sandisk 3D Llc | Multi-use memory cell and memory array and method for use therewith |

| KR100881292B1 (ko) | 2007-01-23 | 2009-02-04 | 삼성전자주식회사 | 3차원 적층구조를 가지는 저항성 반도체 메모리 장치 및그의 제어방법 |

| TW200847399A (en) | 2007-05-21 | 2008-12-01 | Ind Tech Res Inst | Phase change memory device and method of fabricating the same |

| US7989740B2 (en) | 2008-05-16 | 2011-08-02 | Thermon Manufacturing Company | Heating cable |

| US20090283739A1 (en) | 2008-05-19 | 2009-11-19 | Masahiro Kiyotoshi | Nonvolatile storage device and method for manufacturing same |

| US8154005B2 (en) | 2008-06-13 | 2012-04-10 | Sandisk 3D Llc | Non-volatile memory arrays comprising rail stacks with a shared diode component portion for diodes of electrically isolated pillars |

| US8105867B2 (en) | 2008-11-18 | 2012-01-31 | Sandisk 3D Llc | Self-aligned three-dimensional non-volatile memory fabrication |

| US8120068B2 (en) | 2008-12-24 | 2012-02-21 | Sandisk 3D Llc | Three-dimensional memory structures having shared pillar memory cells |

-

2008

- 2008-06-13 US US12/139,435 patent/US8154005B2/en not_active Expired - Fee Related

-

2009

- 2009-06-02 KR KR1020117000959A patent/KR20110039260A/ko not_active Application Discontinuation

- 2009-06-02 EP EP09763292A patent/EP2286453A1/en not_active Withdrawn

- 2009-06-02 CN CN2009801221973A patent/CN102067315B/zh active Active

- 2009-06-02 JP JP2011513573A patent/JP2011524091A/ja active Pending

- 2009-06-02 WO PCT/US2009/046001 patent/WO2009152001A1/en active Application Filing

- 2009-06-12 TW TW098119833A patent/TWI582907B/zh not_active IP Right Cessation

-

2012

- 2012-04-06 US US13/441,805 patent/US8748859B2/en active Active

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6420215B1 (en) * | 2000-04-28 | 2002-07-16 | Matrix Semiconductor, Inc. | Three-dimensional memory array and method of fabrication |

| US6777773B2 (en) * | 2000-08-14 | 2004-08-17 | Matrix Semiconductor, Inc. | Memory cell with antifuse layer formed at diode junction |

| US6525953B1 (en) * | 2001-08-13 | 2003-02-25 | Matrix Semiconductor, Inc. | Vertically-stacked, field-programmable, nonvolatile memory and method of fabrication |

| JP2003204045A (ja) * | 2001-11-26 | 2003-07-18 | Hewlett Packard Co <Hp> | 4つの状態を取り得るメモリセルを有するメモリデバイス |

| US6642603B1 (en) * | 2002-06-27 | 2003-11-04 | Matrix Semiconductor, Inc. | Same conductivity type highly-doped regions for antifuse memory cell |

| US20040002186A1 (en) * | 2002-06-27 | 2004-01-01 | Vyvoda Michael A. | Electrically isolated pillars in active devices |

| JP2004228561A (ja) * | 2003-01-23 | 2004-08-12 | Sharp Corp | デュアルトレンチで隔離されたクロスポイントメモリアレイとその製造方法 |

| US20050242386A1 (en) * | 2004-04-29 | 2005-11-03 | Kern-Huat Ang | Memory cell and method of fabricating the same |

| JP2009283513A (ja) * | 2008-05-19 | 2009-12-03 | Toshiba Corp | 不揮発性記憶装置及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2286453A1 (en) | 2011-02-23 |

| CN102067315A (zh) | 2011-05-18 |

| US8748859B2 (en) | 2014-06-10 |

| US20120187361A1 (en) | 2012-07-26 |

| KR20110039260A (ko) | 2011-04-15 |

| CN102067315B (zh) | 2013-04-24 |

| US8154005B2 (en) | 2012-04-10 |

| WO2009152001A1 (en) | 2009-12-17 |

| TW201007887A (en) | 2010-02-16 |

| US20090309089A1 (en) | 2009-12-17 |

| TWI582907B (zh) | 2017-05-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2011524091A (ja) | 電気的に絶縁された支柱のダイオードのための共有ダイオード要素部を有するレール積層体を備えた不揮発性メモリアレイ | |

| US7706177B2 (en) | Method of programming cross-point diode memory array | |

| US7800933B2 (en) | Method for using a memory cell comprising switchable semiconductor memory element with trimmable resistance | |

| US7800932B2 (en) | Memory cell comprising switchable semiconductor memory element with trimmable resistance | |

| US7660181B2 (en) | Method of making non-volatile memory cell with embedded antifuse | |

| JP5735271B2 (ja) | 大きくて一様な電流を有する上向きpinダイオードの大型アレイとそれを形成する方法 | |

| US7618850B2 (en) | Method of making a diode read/write memory cell in a programmed state | |

| US7800934B2 (en) | Programming methods to increase window for reverse write 3D cell | |

| US8072791B2 (en) | Method of making nonvolatile memory device containing carbon or nitrogen doped diode | |

| US8008700B2 (en) | Non-volatile memory cell with embedded antifuse | |

| US8102694B2 (en) | Nonvolatile memory device containing carbon or nitrogen doped diode | |

| US20080316809A1 (en) | High forward current diodes for reverse write 3D cell | |

| KR20100080899A (ko) | 다중 안티퓨즈 메모리 셀과 이를 형성, 프로그래밍 및 감지하는 방법 | |

| US20070164388A1 (en) | Memory cell comprising a diode fabricated in a low resistivity, programmed state | |

| US7800939B2 (en) | Method of making 3D R/W cell with reduced reverse leakage | |

| KR20100014547A (ko) | 탄소 나노튜브 직물 요소와 조종 요소를 포함하는 메모리 셀과 이를 형성하는 방법 | |

| US7759666B2 (en) | 3D R/W cell with reduced reverse leakage | |

| JP5695417B2 (ja) | 逆方向リークが減少した3次元の読み書きセルとそれを作る方法 | |

| TWI508307B (zh) | 含有碳或氮摻雜二極體之非揮發性記憶體及其製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110404 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110412 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120402 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120402 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131009 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131015 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140311 |