JP2010103424A - 半導体発光素子の製造方法 - Google Patents

半導体発光素子の製造方法 Download PDFInfo

- Publication number

- JP2010103424A JP2010103424A JP2008275683A JP2008275683A JP2010103424A JP 2010103424 A JP2010103424 A JP 2010103424A JP 2008275683 A JP2008275683 A JP 2008275683A JP 2008275683 A JP2008275683 A JP 2008275683A JP 2010103424 A JP2010103424 A JP 2010103424A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- light emitting

- semiconductor light

- layer

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/822—Materials of the light-emitting regions

- H10H20/824—Materials of the light-emitting regions comprising only Group III-V materials, e.g. GaP

- H10H20/825—Materials of the light-emitting regions comprising only Group III-V materials, e.g. GaP containing nitrogen, e.g. GaN

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/819—Bodies characterised by their shape, e.g. curved or truncated substrates

- H10H20/82—Roughened surfaces, e.g. at the interface between epitaxial layers

Landscapes

- Led Devices (AREA)

Abstract

【解決手段】基板11と基板11上に成膜されたIII族窒化物半導体の積層構造からなるIII族窒化物半導体層とを有するウェーハの基板11の被研削面103を研削する研削工程と、研削工程により研削された基板11の被研削面103の表面粗さRaを3nm〜25nmに調整する研磨工程と、研磨工程により表面粗さRaを調整した基板11の被研削面103側から、基板11を分割するための切断予定ラインに沿ってレーザL2を照射することにより、基板11の内部に加工変質部分41,42を設けるレーザ加工工程と、レーザ加工工程により加工変質部分41,42を設けた基板11を加工変質部分41,42及び切断予定ラインに沿って分割する分割工程と、を有することを特徴とする半導体発光素子の製造方法。

【選択図】図6

Description

このようなIII族窒化物半導体を用いた半導体発光素子の光取り出し効率を改善する方法として、発光素子とその外部の媒体との屈折率の違いによって生じる発光素子の内部への光の閉じ込めを低減させる方法が挙げられる。

また、特許文献2には、基板裏面に凹凸を設け、光を基板側面に向けて反射させることによって、基板側面からの光の取り出し効率を上げた透光性電極を有する窒化物系化合物半導体発光素子が記載されている。

さらに、特許文献4には、ウェーハを個々の素子に分割する方法として、半導体層が積層されたウェーハの基板内部に集光点を合わせてレーザ光を照射することにより改質領域を形成し、この改質領域によって切断起点領域を形成し、切断起点領域に沿ってウェーハを切断する方法が提案されている。この場合、基板内の所定の位置に改質領域を形成するために、レーザ光の焦光点を正確に合わせることが必要となる。

また、レーザ加工工程は、基板の内部の被研削面側から厚さ方向で(2/3)部の範囲に加工変質部分を設けることが好ましい。

さらに、レーザ加工工程は、基板に対してレーザをパルス照射することが好ましい。

また、基板上に成膜されたIII族窒化物半導体層側から切断予定ラインに沿ってレーザを照射することにより基板に割溝を形成する割溝形成工程をさらに有することが好ましい。

さらに、凸部を形成した基板の表面にIII族窒化物半導体からなるバッファ層をスパッタリングにより形成するバッファ層形成工程をさらに有することが好ましい。

さらに、ウェーハのIII族窒化物半導体層は、それぞれIII族窒化物化合物半導体を含むn型半導体層、発光層、p型半導体層が積層されることが好ましい。

また、本発明が適用される半導体発光素子の製造方法において、基板は最大径が約100mm以上であることが好ましい。

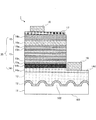

図1は、III族窒化物半導体層を有する半導体発光素子の一例を示した断面図である。図1に示すように、半導体発光素子Iは、表面に複数の凸部102が形成された基板11と、基板11の複数の凸部102が形成された面上に成膜されたバッファ層12と、複数の凸部102を埋めるようにバッファ層12上に成膜された下地層13と、下地層13上にLED構造20が形成された構造を有している。

LED構造20は、n型半導体層14、発光層15、p型半導体層16が順次積層されている。LED構造20を構成するn型半導体層14は、n型コンタクト層14a及びn型クラッド層14bを有する。発光層15は、障壁層15a及び井戸層15bが交互に積層された構造を有する。p型半導体層16は、p型クラッド層16a及びp型コンタクト層16bが積層されている。

さらに、p型半導体層16上に透明正極17が積層され、その上に正極ボンディングパッド18が形成されるとともに、n型半導体層14のn型コンタクト層14aに形成された露出領域14dに負極19が積層されている。

基板11は、III族窒化物化合物半導体とは異なる材料から構成される。基板11を構成する材料としては、例えば、サファイア、炭化ケイ素(シリコンカーバイド:SiC)、シリコン、酸化亜鉛、酸化マグネシウム、酸化マンガン、酸化ジルコニウム、酸化マンガン亜鉛鉄、酸化マグネシウムアルミニウム、ホウ化ジルコニウム、酸化ガリウム、酸化インジウム、酸化リチウムガリウム、酸化リチウムアルミニウム、酸化ネオジウムガリウム、酸化ランタンストロンチウムアルミニウムタンタル、酸化ストロンチウムチタン、酸化チタン、ハフニウム、タングステン、モリブデン等が挙げられる。これらの中でも、サファイア、炭化ケイ素(シリコンカーバイド:SiC)が好ましく、サファイアが特に好ましい。

さらに、本実施の形態では、基板11の裏面である被研削面103の表面粗さRaが、3nm〜25nm、好ましくは、5nm〜20nmになるように調整されている。

基板11の裏面を上述した範囲の表面粗さRaを有する粗面として調整することにより、基板11の反りが低減し、基板11の平坦性を保つことができる。

また、被研削面103における光の乱反射により、半導体発光素子Iの光取り出し効率が増大する。

さらに、後述するように、基板11内部に改質領域を形成するために、基板11の被研削面103側からレーザ光を照射する際に、レーザ光の焦光点を正確に合わせることが可能となる。

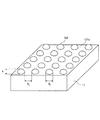

図2及び図3は、複数の凸部102が形成された基板11を説明する図である。図2に示すように、基板11に形成された複数の凸部102は、所定の最大径d1と高さhを有し、均一な大きさと均一な形状になるように形成されている。本実施の形態では、凸部102の形状は半球状である。尚、凸部102の形状は特に限定されない。

本実施の形態では、凸部102の最大径d1は、0.5μm〜2μmの範囲である。凸部102の高さhは、0.5μm〜2μmの範囲である。さらに、複数の凸部102は、基板11の表面に所定の間隔d2を設けて配置されている。本実施の形態では、複数の凸部102の間隔d2は、0.5μm〜2μmの範囲である。

また、図3に示すように、複数の凸部102は、基板11の表面101S上に碁盤目状に等間隔に配置されている。

本実施形態では、基板11上に均一な形状の複数の凸部102を形成することにより、基板11と下地層13との界面が凹凸形状となる。そのため、このような構造を有する基板11の上にLED構造20を設けた半導体発光素子Iは、界面における光の乱反射により、光取り出し効率がさらに増大する。

バッファ層12は、後述するように半導体発光素子のLED構造を有する化合物半導体層を有機金属化学気相成長法(MOCVD)により成膜する際に、バッファ機能を発揮する薄膜層として基板11上に設けられる。バッファ層12を設けることにより、バッファ層12上に成膜される下地層13とさらにこの上に成膜されるLED構造20を有する化合物半導体層は、良好な配向性及び結晶性を有する結晶膜となる。

本実施の形態では、バッファ層12の厚さは、0.01μm〜0.5μmである。バッファ層12の厚さが過度に薄いと、バッファ層12による基板11と下地層13との格子定数の違いを緩和する効果が十分に得られない場合がある。バッファ層12の厚さが過度に厚いと、成膜処理時間が長くなり、生産性が低下する傾向がある。

下地層13に用いる材料としては、Gaを含むIII族窒化物(GaN系化合物半導体)が用いられ、特に、AlGaN、又はGaNを好適に用いることができる。本実施の形態における下地層13は、LED構造20を有する化合物半導体層の下地層として機能するものである。

本実施の形態では、下地層13の厚さは、0.1μm以上、好ましく0.5μm以上、さらに好ましくは1μm以上である。但し、下地層13の厚さは、通常、10.0μm以下である。

前述したように、LED構造20を構成するn型半導体層14は、n型コンタクト層14a及びn型クラッド層14bを有する。発光層15は、障壁層15a及び井戸層15bが交互に積層された構造を有する。p型半導体層16は、p型クラッド層16a及びp型コンタクト層16bが積層されている。

n型半導体層14のn型コンタクト層14aとしては、下地層13と同様にGaN系化合物半導体が用いられる。また、下地層13及びn型コンタクト層14aを構成する窒化ガリウム系化合物半導体は同一組成であることが好ましく、これらの合計の膜厚を0.1μm〜20μm、好ましくは0.5μm〜15μm、さらに好ましくは1μm〜12μmの範囲に設定することが好ましい。

発光層15は、窒化ガリウム系化合物半導体からなる障壁層15aと、インジウムを含有する窒化ガリウム系化合物半導体からなる井戸層15bとが交互に繰り返して積層され、且つ、n型半導体層14側及びp型半導体層16側に障壁層15aが配される順で積層して形成される。本実施の形態では、発光層15は、6層の障壁層15aと5層の井戸層15bとが交互に繰り返して積層され、発光層15の最上層及び最下層に障壁層15aが配され、各障壁層15aの間に井戸層15bが配される構成とされている。

また、井戸層15bには、インジウムを含有する窒化ガリウム系化合物半導体として、例えば、Ga1−sInsN(0<s<0.4)等の窒化ガリウムインジウムを用いることができる。

p型半導体層16は、p型クラッド層16a及びp型コンタクト層16bから構成される。p型クラッド層16aとしては、好ましくは、AldGa1−dN(0<d≦0.4)のものが挙げられる。p型クラッド層16aの膜厚は、好ましくは1nm〜400nmであり、より好ましくは5nm〜100nmである。

p型コンタクト層16bとしては、少なくともAleGa1−eN(0≦e<0.5)を含んでなる窒化ガリウム系化合物半導体層が挙げられる。p型コンタクト層16bの膜厚は、特に限定されないが、10nm〜500nmが好ましく、より好ましくは50nm〜200nmである。

透明正極17を構成する材料としては、例えば、ITO(In2O3−SnO2)、AZO(ZnO−Al2O3)、IZO(In2O3−ZnO)、GZO(ZnO−Ga2O3)等の従来公知の材料が挙げられる。また、透明正極17の構造は特に限定されず、従来公知の構造を採用することができる。透明正極17は、p型半導体層16上のほぼ全面を覆うように形成しても良く、格子状や樹形状に形成しても良い。

透明正極17上に形成される電極としての正極ボンディングパッド18は、例えば、従来公知のAu、Al、Ni、Cu等の材料から構成される。正極ボンディングパッド18の構造は特に限定されず、従来公知の構造を採用することができる。

正極ボンディングパッド18の厚さは、100nm〜1000nmの範囲内であり、好ましくは300nm〜500nmの範囲内である。

図1に示すように、負極19は、基板11上に成膜されたバッファ層12及び下地層13の上にさらに成膜されたLED構造20(n型半導体層14、発光層15及びp型半導体層16)において、n型半導体層14のn型コンタクト層14aに接するように形成される。このため、負極19を形成する際は、p型半導体層16、発光層15及びn型半導体層14の一部を除去し、n型コンタクト層14aの露出領域14dを形成し、この上に負極19を形成する。

負極19の材料としては、各種組成および構造の負極が周知であり、これら周知の負極

を何ら制限無く用いることができ、この技術分野でよく知られた慣用の手段で設けること

ができる。

次に、本実施の形態が適用される半導体発光素子の製造方法について説明する。

図4、図5、図6は、半導体発光素子の製造工程を説明する図である。

図4(a)に示すように、先ず、サファイア板10を準備する。サファイア板10の最大径は、通常、約50mm以上、好ましくは約100mm以上の範囲であり、約50mm〜約200mmの範囲がより好ましい。厚さは、0.4mm〜2mmの範囲が好ましい。

本実施の形態では、(1)最大径約50mmと厚さ0.7mmを有するサファイア板10、(2)最大径約100mmと厚さ1mmを有するサファイア板10、(3)最大径約150mmと厚さ1.3mmを有するサファイア板10を使用する。

尚、LED構造20の内、下地層13をMOCVD法によって形成した後、n型コンタクト層14a及びn型クラッド層14bの各層をスパッタ法で形成し、その上の発光層15をMOCVD法で形成し、そして、p型半導体層16を構成するp型クラッド層16a及びp型コンタクト層16bの各層を反応性スパッタ法で形成してもよい。

ここで、本実施の形態では、研削工程及び研磨工程により、基板11の厚さを調整するとともに、基板11の裏面である被研削面103の表面粗さRaを、3nm〜25nm、好ましくは、5nm〜20nmになるように調整する。

また、加工変質部分41,42は、基板11に設けた割溝30と基板11の厚さ方向に略同一の直線上に形成している。

このとき、分割後の基板11の分割面(端面11a)には、加工変質部分41,42の少なくとも一部が残存する領域と、基板11を切断した際に分割面(端面11a)に生じる亀裂痕が不規則に残存する領域とが存在し、分割面(端面11a)のほぼ全体が粗面となる。

このように、基板11の分割面(端面11a)を粗面として形成することにより、分割面(端面11a)の表面積が増加し、入射した光を効率良く外部に出射できる基板11とすることができ、光取り出し効率に優れた半導体発光素子Iを製造することが可能となる。

しかしながら、本実施の形態が適用される半導体発光素子の製造方法によれば、研磨工程において、研削工程で研削された基板の被研削面の表面粗さRaを3nm〜25nmに調整することにより、レーザ加工工程における基板の平坦性を保つことができる。

このような効果は、基板、例えば、サファイア基板の最大径が、大きいものほど格別となる。本実施の形態では、最大径が、約50mm<約100mm<約150mmの順で、特に効果的であった。

Claims (11)

- III族窒化物半導体層を有する半導体発光素子の製造方法であって、

基板と当該基板上に成膜されたIII族窒化物半導体の積層構造からなるIII族窒化物半導体層とを有するウェーハの当該基板の被研削面を研削する研削工程と、

前記研削工程により研削された前記基板の前記被研削面の表面粗さRaを3nm〜25nmに調整する研磨工程と、

前記研磨工程により前記表面粗さRaを調整した前記基板の前記被研削面側から、当該基板を分割するための切断予定ラインに沿ってレーザを照射することにより、当該基板の内部に加工変質部分を設けるレーザ加工工程と、

前記レーザ加工工程により前記加工変質部分を設けた前記基板を当該加工変質部分及び前記切断予定ラインに沿って分割する分割工程と、

を有することを特徴とする半導体発光素子の製造方法。 - 前記レーザ加工工程は、前記基板の厚さ方向に断続的に複数の前記加工変質部分を設けることを特徴とする請求項1に記載の半導体発光素子の製造方法。

- 前記レーザ加工工程は、前記基板の内部の前記被研削面側から厚さ方向で(2/3)部の範囲に前記加工変質部分を設けることを特徴とする請求項1又は2に記載の半導体発光素子の製造方法。

- 前記レーザ加工工程は、前記基板に対して前記レーザをパルス照射することを特徴とする請求項1乃至3のいずれか1項に記載の半導体発光素子の製造方法。

- 前記分割工程において、前記基板を分割することにより当該基板の分割面を粗面とすることを特徴とする請求項1乃至4のいずれか1項に記載の半導体発光素子の製造方法。

- 前記基板上に成膜された前記III族窒化物半導体層側から前記切断予定ラインに沿ってレーザを照射することにより当該基板に割溝を形成する割溝形成工程をさらに有することを特徴とする請求項1乃至5のいずれか1項に記載の半導体発光素子の製造方法。

- 前記基板の表面に予め複数の凸部を形成する基板加工工程をさらに有することを特徴とする請求項1乃至6のいずれか1項に記載の半導体発光素子の製造方法。

- 前記凸部を形成した前記基板の前記表面にIII族窒化物半導体からなるバッファ層をスパッタリングにより形成するバッファ層形成工程をさらに有することを特徴とする請求項1乃至7のいずれか1項に記載の半導体発光素子の製造方法。

- 前記基板は、サファイア又はシリコンカーバイドから選ばれることを特徴とする請求項1乃至8のいずれか1項に記載の半導体発光素子の製造方法。

- 前記ウェーハの前記III族窒化物半導体層は、それぞれIII族窒化物化合物半導体を含むn型半導体層、発光層、p型半導体層が積層されることを特徴とする請求項1乃至9のいずれか1項に記載の半導体発光素子の製造方法。

- 前記基板は、最大径が約100mm以上であることを特徴とする請求項1乃至10のいずれか1項に記載の半導体発光素子の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008275683A JP2010103424A (ja) | 2008-10-27 | 2008-10-27 | 半導体発光素子の製造方法 |

| PCT/JP2009/068250 WO2010050410A1 (ja) | 2008-10-27 | 2009-10-23 | 半導体発光素子の製造方法 |

| US13/126,136 US20110204412A1 (en) | 2008-10-27 | 2009-10-23 | Method for manufacturing semiconductor light emitting element |

| TW098136325A TWI427827B (zh) | 2008-10-27 | 2009-10-27 | Manufacturing method of semiconductor light emitting element |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008275683A JP2010103424A (ja) | 2008-10-27 | 2008-10-27 | 半導体発光素子の製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010103424A true JP2010103424A (ja) | 2010-05-06 |

Family

ID=42128773

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008275683A Pending JP2010103424A (ja) | 2008-10-27 | 2008-10-27 | 半導体発光素子の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20110204412A1 (ja) |

| JP (1) | JP2010103424A (ja) |

| TW (1) | TWI427827B (ja) |

| WO (1) | WO2010050410A1 (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011176379A (ja) * | 2009-09-07 | 2011-09-08 | El-Seed Corp | 半導体発光素子 |

| WO2012023954A1 (en) * | 2010-08-20 | 2012-02-23 | Invenlux Corporation | Light-emitting devices with substrate coated with optically denser material |

| JP2012227187A (ja) * | 2011-04-15 | 2012-11-15 | Showa Denko Kk | 半導体発光チップの製造方法および半導体発光チップ |

| JP2013098298A (ja) * | 2011-10-31 | 2013-05-20 | Toyoda Gosei Co Ltd | Iii族窒化物半導体発光素子の製造方法 |

| JP2013168680A (ja) * | 2013-05-28 | 2013-08-29 | Toshiba Corp | 半導体発光素子及びその製造方法 |

| US9147599B2 (en) | 2011-10-18 | 2015-09-29 | Fuji Electric Co., Ltd. | Wafer support system and method for separating support substrate from solid-phase bonded wafer and method for manufacturing semiconductor device |

| JP2016184718A (ja) * | 2015-03-24 | 2016-10-20 | 日亜化学工業株式会社 | 発光素子の製造方法 |

| US9873170B2 (en) | 2015-03-24 | 2018-01-23 | Nichia Corporation | Method of manufacturing light emitting element |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5222916B2 (ja) * | 2010-09-17 | 2013-06-26 | シャープ株式会社 | 半導体基材の製造方法、半導体装置、および電気機器 |

| US8722516B2 (en) * | 2010-09-28 | 2014-05-13 | Hamamatsu Photonics K.K. | Laser processing method and method for manufacturing light-emitting device |

| DE102011012925A1 (de) * | 2011-03-03 | 2012-09-06 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Halbleiterchips |

| TWI430475B (zh) * | 2011-08-03 | 2014-03-11 | Lextar Electronics Corp | 發光二極體的製造方法 |

| CN102290505B (zh) * | 2011-09-09 | 2014-04-30 | 上海蓝光科技有限公司 | GaN基发光二极管芯片及其制造方法 |

| US20140361329A1 (en) * | 2012-02-02 | 2014-12-11 | Koninklijke Philips N.V. | Producing light emitting devices at variable flux levels |

| US20130234149A1 (en) * | 2012-03-09 | 2013-09-12 | Electro Scientific Industries, Inc. | Sidewall texturing of light emitting diode structures |

| KR101233062B1 (ko) * | 2012-04-18 | 2013-02-19 | (주)휴넷플러스 | 나노 급 패턴이 형성된 고효율 질화물계 발광다이오드용 기판의 제조방법 |

| US9040389B2 (en) | 2012-10-09 | 2015-05-26 | Infineon Technologies Ag | Singulation processes |

| CN103022284A (zh) * | 2013-01-08 | 2013-04-03 | 聚灿光电科技(苏州)有限公司 | Led芯片切割方法及其制备的led芯片 |

| US9548419B2 (en) * | 2014-05-20 | 2017-01-17 | Southern Taiwan University Of Science And Technology | Light emitting diode chip having multi microstructure substrate surface |

| TWI614914B (zh) * | 2014-07-11 | 2018-02-11 | 晶元光電股份有限公司 | 發光元件及其製造方法 |

| CN111430511A (zh) * | 2014-07-25 | 2020-07-17 | 晶元光电股份有限公司 | 发光元件及其制造方法 |

| WO2016202039A1 (zh) * | 2015-06-17 | 2016-12-22 | 厦门市三安光电科技有限公司 | 发光二极管及其制备方法 |

| US10505072B2 (en) * | 2016-12-16 | 2019-12-10 | Nichia Corporation | Method for manufacturing light emitting element |

| TWI846791B (zh) * | 2019-12-31 | 2024-07-01 | 晶元光電股份有限公司 | 發光元件及其製造方法 |

| CN113228310A (zh) * | 2020-12-30 | 2021-08-06 | 泉州三安半导体科技有限公司 | 一种半导体发光元件及其制备方法 |

| JP7534656B2 (ja) | 2022-03-15 | 2024-08-15 | 日亜化学工業株式会社 | 発光素子の製造方法及び発光素子 |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002053398A (ja) * | 2000-08-03 | 2002-02-19 | Hitachi Cable Ltd | 結晶基板 |

| JP2003218065A (ja) * | 2002-11-13 | 2003-07-31 | Nichia Chem Ind Ltd | 窒化物半導体素子の製造方法 |

| JP2003318441A (ja) * | 2001-07-24 | 2003-11-07 | Nichia Chem Ind Ltd | 半導体発光素子 |

| JP2005244198A (ja) * | 2004-01-26 | 2005-09-08 | Matsushita Electric Ind Co Ltd | 半導体装置の製造方法 |

| JP2006024914A (ja) * | 2004-06-11 | 2006-01-26 | Showa Denko Kk | 化合物半導体素子ウェハーの製造方法 |

| JP2006169104A (ja) * | 2000-09-18 | 2006-06-29 | Mitsubishi Cable Ind Ltd | 半導体基材及びその作製方法 |

| JP2006245380A (ja) * | 2005-03-04 | 2006-09-14 | Toshiba Corp | 半導体発光素子及び半導体発光素子の製造方法 |

| JP2008106316A (ja) * | 2006-10-26 | 2008-05-08 | Showa Denko Kk | Iii族窒化物化合物半導体発光素子の製造方法、及びiii族窒化物化合物半導体発光素子、並びにランプ |

| JP2008117799A (ja) * | 2006-10-31 | 2008-05-22 | Stanley Electric Co Ltd | 半導体基板の処理方法、半導体装置の製造方法、及びZnO基板 |

| JP2008251753A (ja) * | 2007-03-29 | 2008-10-16 | Mitsubishi Chemicals Corp | 窒化物led素子の製造方法 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6903385B2 (en) * | 2002-10-09 | 2005-06-07 | Sensor Electronic Technology, Inc. | Semiconductor structure having a textured nitride-based layer |

| US7008861B2 (en) * | 2003-12-11 | 2006-03-07 | Cree, Inc. | Semiconductor substrate assemblies and methods for preparing and dicing the same |

| JP2005268752A (ja) * | 2004-02-19 | 2005-09-29 | Canon Inc | レーザ割断方法、被割断部材および半導体素子チップ |

| US7772605B2 (en) * | 2004-03-19 | 2010-08-10 | Showa Denko K.K. | Compound semiconductor light-emitting device |

| US7875898B2 (en) * | 2005-01-24 | 2011-01-25 | Panasonic Corporation | Semiconductor device |

| US7829909B2 (en) * | 2005-11-15 | 2010-11-09 | Verticle, Inc. | Light emitting diodes and fabrication methods thereof |

| US7838331B2 (en) * | 2005-11-16 | 2010-11-23 | Denso Corporation | Method for dicing semiconductor substrate |

| JP4908381B2 (ja) * | 2006-12-22 | 2012-04-04 | 昭和電工株式会社 | Iii族窒化物半導体層の製造方法、及びiii族窒化物半導体発光素子、並びにランプ |

| WO2008083081A2 (en) * | 2006-12-28 | 2008-07-10 | Saint-Gobain Ceramics & Plastics, Inc. | Sapphire substrates and methods of making same |

| US8236591B2 (en) * | 2007-08-03 | 2012-08-07 | Nichia Corporation | Semiconductor light emitting element and method for manufacturing the same |

-

2008

- 2008-10-27 JP JP2008275683A patent/JP2010103424A/ja active Pending

-

2009

- 2009-10-23 WO PCT/JP2009/068250 patent/WO2010050410A1/ja not_active Ceased

- 2009-10-23 US US13/126,136 patent/US20110204412A1/en not_active Abandoned

- 2009-10-27 TW TW098136325A patent/TWI427827B/zh active

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002053398A (ja) * | 2000-08-03 | 2002-02-19 | Hitachi Cable Ltd | 結晶基板 |

| JP2006169104A (ja) * | 2000-09-18 | 2006-06-29 | Mitsubishi Cable Ind Ltd | 半導体基材及びその作製方法 |

| JP2003318441A (ja) * | 2001-07-24 | 2003-11-07 | Nichia Chem Ind Ltd | 半導体発光素子 |

| JP2003218065A (ja) * | 2002-11-13 | 2003-07-31 | Nichia Chem Ind Ltd | 窒化物半導体素子の製造方法 |

| JP2005244198A (ja) * | 2004-01-26 | 2005-09-08 | Matsushita Electric Ind Co Ltd | 半導体装置の製造方法 |

| JP2006024914A (ja) * | 2004-06-11 | 2006-01-26 | Showa Denko Kk | 化合物半導体素子ウェハーの製造方法 |

| JP2006245380A (ja) * | 2005-03-04 | 2006-09-14 | Toshiba Corp | 半導体発光素子及び半導体発光素子の製造方法 |

| JP2008106316A (ja) * | 2006-10-26 | 2008-05-08 | Showa Denko Kk | Iii族窒化物化合物半導体発光素子の製造方法、及びiii族窒化物化合物半導体発光素子、並びにランプ |

| JP2008117799A (ja) * | 2006-10-31 | 2008-05-22 | Stanley Electric Co Ltd | 半導体基板の処理方法、半導体装置の製造方法、及びZnO基板 |

| JP2008251753A (ja) * | 2007-03-29 | 2008-10-16 | Mitsubishi Chemicals Corp | 窒化物led素子の製造方法 |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011176379A (ja) * | 2009-09-07 | 2011-09-08 | El-Seed Corp | 半導体発光素子 |

| JPWO2011027679A1 (ja) * | 2009-09-07 | 2013-02-04 | エルシード株式会社 | 半導体発光素子 |

| WO2012023954A1 (en) * | 2010-08-20 | 2012-02-23 | Invenlux Corporation | Light-emitting devices with substrate coated with optically denser material |

| US8723201B2 (en) | 2010-08-20 | 2014-05-13 | Invenlux Corporation | Light-emitting devices with substrate coated with optically denser material |

| JP2012227187A (ja) * | 2011-04-15 | 2012-11-15 | Showa Denko Kk | 半導体発光チップの製造方法および半導体発光チップ |

| US9147599B2 (en) | 2011-10-18 | 2015-09-29 | Fuji Electric Co., Ltd. | Wafer support system and method for separating support substrate from solid-phase bonded wafer and method for manufacturing semiconductor device |

| JP2013098298A (ja) * | 2011-10-31 | 2013-05-20 | Toyoda Gosei Co Ltd | Iii族窒化物半導体発光素子の製造方法 |

| JP2013168680A (ja) * | 2013-05-28 | 2013-08-29 | Toshiba Corp | 半導体発光素子及びその製造方法 |

| JP2016184718A (ja) * | 2015-03-24 | 2016-10-20 | 日亜化学工業株式会社 | 発光素子の製造方法 |

| US9873170B2 (en) | 2015-03-24 | 2018-01-23 | Nichia Corporation | Method of manufacturing light emitting element |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2010050410A1 (ja) | 2010-05-06 |

| TW201025681A (en) | 2010-07-01 |

| US20110204412A1 (en) | 2011-08-25 |

| TWI427827B (zh) | 2014-02-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2010103424A (ja) | 半導体発光素子の製造方法 | |

| JP5556657B2 (ja) | Iii族窒化物半導体発光素子の製造方法及びiii族窒化物半導体発光素子、並びにランプ | |

| JP5179068B2 (ja) | 化合物半導体素子の製造方法 | |

| CN101467272B (zh) | 氮化镓系化合物半导体发光元件 | |

| JP3904585B2 (ja) | 半導体素子の製造方法 | |

| JP5281545B2 (ja) | 半導体発光素子の製造方法 | |

| KR101454821B1 (ko) | 결정성막, 디바이스, 및, 결정성막 또는 디바이스의 제조방법 | |

| TW200524180A (en) | Light-emitting semiconductor device, manufacturing method thereof, and electrode forming method | |

| TW201236071A (en) | Semiconductor light emitting chip and substrate processing method | |

| JP2011129765A (ja) | 半導体発光素子の製造方法 | |

| JP2005166728A (ja) | 窒化物系半導体素子の製造方法 | |

| US20100102341A1 (en) | Semiconductor light emitting device and method for manufacturing the same | |

| JP2007214500A (ja) | 半導体部材及びその製造方法 | |

| TWI327340B (en) | Production method for semiconductor device | |

| JP2008124254A (ja) | 窒化ガリウム系化合物半導体発光素子 | |

| JP4540514B2 (ja) | 化合物半導体発光素子およびその製造方法 | |

| US8866186B2 (en) | Group III nitride semiconductor light-emitting device | |

| JP2004228290A (ja) | 半導体発光素子及びその製造方法 | |

| JP2013098298A (ja) | Iii族窒化物半導体発光素子の製造方法 | |

| JP2005302804A (ja) | 発光ダイオード及びその製造方法 | |

| US20100038656A1 (en) | Nitride LEDs based on thick templates | |

| JP2005252245A (ja) | 窒化ガリウム系化合物半導体ウェハー | |

| JP2006203251A (ja) | 半導体素子の製造方法 | |

| JP4282743B2 (ja) | 窒化ガリウム系化合物半導体発光素子 | |

| JP2008306225A (ja) | 窒化ガリウム系化合物半導体発光素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110701 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121211 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20121212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130208 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130827 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131023 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140107 |