JP4540514B2 - 化合物半導体発光素子およびその製造方法 - Google Patents

化合物半導体発光素子およびその製造方法 Download PDFInfo

- Publication number

- JP4540514B2 JP4540514B2 JP2005077638A JP2005077638A JP4540514B2 JP 4540514 B2 JP4540514 B2 JP 4540514B2 JP 2005077638 A JP2005077638 A JP 2005077638A JP 2005077638 A JP2005077638 A JP 2005077638A JP 4540514 B2 JP4540514 B2 JP 4540514B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- compound semiconductor

- light emitting

- light

- laser

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

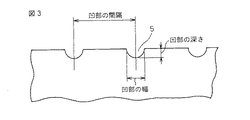

(1)基板上に発光層を備えた化合物半導体発光素子に於いて、素子側面の少なくとも基板部の一部が辺方向に凹部を有することを特徴とする化合物半導体発光素子。

(10)小孔の開口径が1〜20μmであることを特徴とする上記8または9項に記載の製造方法。

(19)上記18項に記載のランプを備えていることを特徴とする光源。

パルスレーザーの場合、周波数および加工スピードによってピッチを調整できる。

また、レーザー光の焦点位置を基板内部に結ばれるように調整することにより、基板内部に小空隙(または変質部)を形成することができる。このように、基板の表面(背面)に小孔を形成する替わりに、基板内部に小空隙を形成させてもよい。

窒化ガリウム系化合物半導体からなる青色発光素子を以下のとおり作製した。

サファイア基板ウェハー上にAlNからなるバッファ層を介してアンドープGaNからなる厚さ2μmの下地層、Siドープ(濃度1×1019/cm3)GaNからなる厚さ2μmのnコンタクト層、Siドープ(濃度1×1018/cm3)In0.1Ga0.9Nからなるnクラッド層、GaNからなる厚さ16nmの障壁層とIn0.2Ga0.8Nからなる厚さ2.5nmの井戸層を交互に5回積層させた後最後に障壁層を設けた多重量子井戸構造の発光層、Mgドープ(濃度1×1020/cm3)Al0.07Ga0.93Nからなる厚さ2.5nmのpクラッド層およびMgドープ(濃度8×1019/cm3)GaNからなる厚さ0.15μmのpコンタクト層を順次積層して化合物半導体積層物とした。

ベアチップマウントした状態の積分球測定において、この発光素子は電流20mAで10mWの発光出力を示した。

サファイア基板背面に分離帯域に対応してレーザー照射により小孔を形成する替わりに、幅が10μm、深さが20μmの従来の裁断ラインをレーザー照射により形成したことを除いて、実施例1と同様に発光素子を作製した。得られた発光素子の側面は、レーザー照射部分には微小な凹凸が形成されていたが、側面全体では非常に平坦であった。

この発光素子は電流20mAで9.5mWの発光出力を示し、実施例1に比較して約5%低かった。

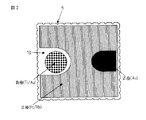

本実施例では、基板の背面側に小孔を形成する替わりに、基板表面側のエッチングされた分離帯域上に小孔を形成したことを除いて、実施例1と同様に発光素子を作製した。但し、レーザーで小孔を形成する前にレジスト保護膜を半導体表面に塗布し、小孔形成後を保護膜上のデブリと共に保護膜を洗浄で除去した。

この発光素子は電流20mAで10.2mWの発光出力を示した。

基板表面側から形成する小孔の深さを約3.5μmとし、基板背面側に比較例1と同様の裁断ラインを設けたことを除いて、実施例2と同様に発光素子を作製した。

得られた発光素子の側面には、半導体層のみに凹凸が形成されていた。この発光素子は電流20mAで9.7mWの発光出力を示し、実施例2に比較して約5%低かった。

本実施例では、基板表面側から小孔を形成するまでは実施例2と全く同様の操作で行ない、その後、その小孔に対応する位置に基板背面にも小孔を形成した。但し、小孔の深さは、表面側が10μmであり、背面側が15μmであった。

この発光素子は電流20mAで10.2mWの発光出力を示した。

本実施例では、基板背面に小孔を形成するまでは実施例1と全く同様の操作で行ない、その後、その小孔を半円状に2分割するように、ダイヤモンド針で従来のスクライブラインを幅2μmおよび深さ10μmで形成した。スクライブラインを形成後、基板表面側から押し割って分離することにより、5cmφのウェハーから350μm角のチップを多数得た。不良率は実施例1よりも改良された。

この発光素子は電流20mAで10mWの発光出力を示した。

本実施例では、レーザー光の焦点位置を基板背面から20μm内部に設定して、スポット径を1μmとし、5μm間隔でレーザー光を照射したことを除いて、実施例1と同様に発光素子を作製した。

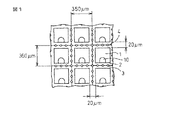

2 分離帯域

3 小孔

4 分離帯域中心線

5 凹部

10 負極形成面

Claims (6)

- 基板となるウェハー上に、n型またはp型の化合物半導体からなる発光層を含む化合物半導体層を積層し、該発光層に駆動電流を流通させるための負極および正極が所定の位置に配置し、個々の発光素子に分離するための分離帯域を形成し、該基板となるウェハー内部に焦点位置を設定したレーザー光を、該基板の該分離帯域に沿って直線状に走査しつつ間歇的に照射し、その後、該分離帯域に沿って個々の発光素子に分割することにより、発光素子の基板側面に、平面形状で波浪型にうねった辺方向に周期的な凹凸を形成することを特徴とする化合物半導体発光素子の製造方法。

- レーザー光を間歇的に照射する際の間隔を4μm以上40μm以下とすることを特徴とする請求項1に記載の化合物半導体発光素子の製造方法。

- レーザー光の焦点位置の深さを、基板厚さの1/10〜3/4とすることを特徴とする請求項1または2のいずれかに記載の化合物半導体発光素子の製造方法。

- レーザー光を、該基板の該分離帯域に沿って直線上に走査しつつ間歇的に照射した後、レーザーにより該基板の該分離帯域に沿ってスクライブラインをさらに設けることを特徴とする請求項1〜3のいずれか一項に記載の化合物半導体発光素子の製造方法。

- レーザー光を、基板背面から照射することを特徴とする請求項1〜4のいずれか一項に記載の化合物半導体発光素子の製造方法。

- 基板がサファイアからなることを特徴とする請求項1〜5のいずれか一項に記載の化合物半導体発光素子の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005077638A JP4540514B2 (ja) | 2004-03-19 | 2005-03-17 | 化合物半導体発光素子およびその製造方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004081286 | 2004-03-19 | ||

| JP2005077638A JP4540514B2 (ja) | 2004-03-19 | 2005-03-17 | 化合物半導体発光素子およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005303286A JP2005303286A (ja) | 2005-10-27 |

| JP2005303286A5 JP2005303286A5 (ja) | 2010-06-17 |

| JP4540514B2 true JP4540514B2 (ja) | 2010-09-08 |

Family

ID=35334378

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005077638A Active JP4540514B2 (ja) | 2004-03-19 | 2005-03-17 | 化合物半導体発光素子およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4540514B2 (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4986445B2 (ja) * | 2005-12-13 | 2012-07-25 | 昭和電工株式会社 | 窒化ガリウム系化合物半導体発光素子 |

| JP2009059969A (ja) * | 2007-08-31 | 2009-03-19 | Seiwa Electric Mfg Co Ltd | 半導体発光素子、発光装置、照明装置、表示装置及び半導体発光素子の製造方法 |

| KR101123010B1 (ko) * | 2008-12-09 | 2012-06-15 | 삼성엘이디 주식회사 | 반도체 발광소자 및 그 제조방법 |

| TWI470823B (zh) | 2009-02-11 | 2015-01-21 | Epistar Corp | 發光元件及其製造方法 |

| JP2010278145A (ja) * | 2009-05-27 | 2010-12-09 | Shogen Koden Kofun Yugenkoshi | 発光素子及びその製造方法 |

| WO2011007816A1 (ja) * | 2009-07-15 | 2011-01-20 | 三菱化学株式会社 | 半導体発光素子、半導体発光装置、半導体発光素子の製造方法、および半導体発光装置の製造方法 |

| JP2012025068A (ja) * | 2010-07-26 | 2012-02-09 | Kitaoka Tekkosho:Kk | 脆性材料の割断装置および割断方法 |

| KR20120100193A (ko) * | 2011-03-03 | 2012-09-12 | 서울옵토디바이스주식회사 | 발광 다이오드 칩 |

| JP5644745B2 (ja) | 2011-12-05 | 2014-12-24 | 豊田合成株式会社 | 半導体発光素子および発光装置 |

| EP2605295A3 (en) * | 2011-12-13 | 2015-11-11 | LG Innotek Co., Ltd. | Ultraviolet light emitting device |

| TWI514622B (zh) * | 2013-02-19 | 2015-12-21 | Lextar Electronics Corp | 發光二極體晶粒及其製造方法 |

| JP6151557B2 (ja) * | 2013-05-13 | 2017-06-21 | 株式会社ディスコ | レーザー加工方法 |

Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5650586A (en) * | 1979-10-01 | 1981-05-07 | Mitsubishi Electric Corp | Light emitting diode |

| JPH03129882A (ja) * | 1989-10-16 | 1991-06-03 | Mitsubishi Monsanto Chem Co | 発光ダイオードチップ |

| JPH04116848A (ja) * | 1990-09-06 | 1992-04-17 | Seiko Instr Inc | 半導体装置の製造方法 |

| JPH07273069A (ja) * | 1994-03-31 | 1995-10-20 | Nichia Chem Ind Ltd | 窒化ガリウム系化合物半導体チップの製造方法 |

| JPH0992878A (ja) * | 1995-09-25 | 1997-04-04 | Shin Etsu Handotai Co Ltd | 半導体発光素子及びその製造方法 |

| JPH09270528A (ja) * | 1996-03-29 | 1997-10-14 | Sanyo Electric Co Ltd | 発光ダイオード素子及びその製造方法 |

| JP2002205180A (ja) * | 2000-09-13 | 2002-07-23 | Hamamatsu Photonics Kk | レーザ加工方法 |

| JP2003110136A (ja) * | 2001-09-28 | 2003-04-11 | Toyoda Gosei Co Ltd | 発光素子 |

| JP2003151921A (ja) * | 2001-11-09 | 2003-05-23 | Sanyo Electric Co Ltd | 化合物半導体とその製造方法 |

| JP2003298107A (ja) * | 2002-01-29 | 2003-10-17 | Toshiba Corp | 半導体発光素子及びその製造方法 |

| JP2003338468A (ja) * | 2002-03-12 | 2003-11-28 | Hamamatsu Photonics Kk | 発光素子の製造方法、発光ダイオード、及び半導体レーザ素子 |

| JP2004165227A (ja) * | 2002-11-08 | 2004-06-10 | Toyoda Gosei Co Ltd | Iii族窒化物系化合物半導体素子の製造方法 |

-

2005

- 2005-03-17 JP JP2005077638A patent/JP4540514B2/ja active Active

Patent Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5650586A (en) * | 1979-10-01 | 1981-05-07 | Mitsubishi Electric Corp | Light emitting diode |

| JPH03129882A (ja) * | 1989-10-16 | 1991-06-03 | Mitsubishi Monsanto Chem Co | 発光ダイオードチップ |

| JPH04116848A (ja) * | 1990-09-06 | 1992-04-17 | Seiko Instr Inc | 半導体装置の製造方法 |

| JPH07273069A (ja) * | 1994-03-31 | 1995-10-20 | Nichia Chem Ind Ltd | 窒化ガリウム系化合物半導体チップの製造方法 |

| JPH0992878A (ja) * | 1995-09-25 | 1997-04-04 | Shin Etsu Handotai Co Ltd | 半導体発光素子及びその製造方法 |

| JPH09270528A (ja) * | 1996-03-29 | 1997-10-14 | Sanyo Electric Co Ltd | 発光ダイオード素子及びその製造方法 |

| JP2002205180A (ja) * | 2000-09-13 | 2002-07-23 | Hamamatsu Photonics Kk | レーザ加工方法 |

| JP2003110136A (ja) * | 2001-09-28 | 2003-04-11 | Toyoda Gosei Co Ltd | 発光素子 |

| JP2003151921A (ja) * | 2001-11-09 | 2003-05-23 | Sanyo Electric Co Ltd | 化合物半導体とその製造方法 |

| JP2003298107A (ja) * | 2002-01-29 | 2003-10-17 | Toshiba Corp | 半導体発光素子及びその製造方法 |

| JP2003338468A (ja) * | 2002-03-12 | 2003-11-28 | Hamamatsu Photonics Kk | 発光素子の製造方法、発光ダイオード、及び半導体レーザ素子 |

| JP2004165227A (ja) * | 2002-11-08 | 2004-06-10 | Toyoda Gosei Co Ltd | Iii族窒化物系化合物半導体素子の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005303286A (ja) | 2005-10-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4540514B2 (ja) | 化合物半導体発光素子およびその製造方法 | |

| US7008861B2 (en) | Semiconductor substrate assemblies and methods for preparing and dicing the same | |

| TWI254468B (en) | Compound semiconductor light-emitting device and production method thereof | |

| TWI442462B (zh) | Semiconductor light - emitting chip and substrate processing methods | |

| US7183136B2 (en) | Semiconductor element and method for producing the same | |

| JP5267462B2 (ja) | 半導体発光素子及びその製造方法 | |

| JP4753628B2 (ja) | 化合物半導体素子ウェハーの製造方法 | |

| JP3904585B2 (ja) | 半導体素子の製造方法 | |

| JP5179068B2 (ja) | 化合物半導体素子の製造方法 | |

| WO2010050410A1 (ja) | 半導体発光素子の製造方法 | |

| JP2007087973A (ja) | 窒化物半導体素子の製法およびその方法により得られる窒化物半導体発光素子 | |

| US8866186B2 (en) | Group III nitride semiconductor light-emitting device | |

| JP2009081428A (ja) | 半導体発光素子およびその製造方法 | |

| JP2011129765A (ja) | 半導体発光素子の製造方法 | |

| JP4937599B2 (ja) | 窒化物半導体発光素子及びその製造方法 | |

| JP2013239471A (ja) | 発光ダイオード素子の製造方法 | |

| JP2004228290A (ja) | 半導体発光素子及びその製造方法 | |

| JP5025199B2 (ja) | Iii族窒化物半導体発光素子 | |

| JP2006203251A (ja) | 半導体素子の製造方法 | |

| JP2009033205A (ja) | 窒化物半導体発光素子の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080218 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100427 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20100427 |

|

| TRDD | Decision of grant or rejection written | ||

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20100521 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100525 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100622 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4540514 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130702 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130702 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130702 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |