JP2010056111A - 電子部品およびその製造方法 - Google Patents

電子部品およびその製造方法 Download PDFInfo

- Publication number

- JP2010056111A JP2010056111A JP2008216321A JP2008216321A JP2010056111A JP 2010056111 A JP2010056111 A JP 2010056111A JP 2008216321 A JP2008216321 A JP 2008216321A JP 2008216321 A JP2008216321 A JP 2008216321A JP 2010056111 A JP2010056111 A JP 2010056111A

- Authority

- JP

- Japan

- Prior art keywords

- conductor layer

- inductor

- main body

- firing

- electronic component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 39

- 239000004020 conductor Substances 0.000 claims abstract description 439

- 239000000919 ceramic Substances 0.000 claims abstract description 35

- 238000010304 firing Methods 0.000 claims description 120

- 239000003989 dielectric material Substances 0.000 claims description 7

- 230000001105 regulatory effect Effects 0.000 claims description 5

- 238000000034 method Methods 0.000 description 52

- 239000003990 capacitor Substances 0.000 description 30

- 239000002184 metal Substances 0.000 description 14

- 229910052751 metal Inorganic materials 0.000 description 14

- 230000001965 increasing effect Effects 0.000 description 11

- 239000000758 substrate Substances 0.000 description 11

- 238000004891 communication Methods 0.000 description 9

- 230000000052 comparative effect Effects 0.000 description 8

- 230000000694 effects Effects 0.000 description 8

- 230000008569 process Effects 0.000 description 8

- 239000011521 glass Substances 0.000 description 7

- 238000007650 screen-printing Methods 0.000 description 7

- 239000000843 powder Substances 0.000 description 5

- 239000000463 material Substances 0.000 description 3

- 238000007639 printing Methods 0.000 description 3

- 238000009751 slip forming Methods 0.000 description 3

- 239000007787 solid Substances 0.000 description 3

- 230000008602 contraction Effects 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 230000007480 spreading Effects 0.000 description 2

- 238000003892 spreading Methods 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000010344 co-firing Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

Images

Landscapes

- Manufacturing Cores, Coils, And Magnets (AREA)

- Coils Or Transformers For Communication (AREA)

- Filters And Equalizers (AREA)

Abstract

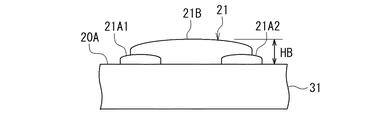

【解決手段】電子部品1は、セラミックよりなり、上面20Aを形成する誘電体層を含む本体20と、本体20の上面20Aに配置されたインダクタ用導体層21とを備えている。インダクタ用導体層21は、第1の導体層21Aと第2の導体層21Bとを有している。第1の導体層21Aは、インダクタ用導体層21の長手方向に沿って延び、互いの間に間隙を形成し、インダクタ用導体層21の長手方向に沿った2つの端縁を画定する2つの端縁画定部21A1,21A2を含んでいる。第2の導体層21Bは、2つの端縁画定部21A1,21A2における外側の端縁よりはみ出すことなく、2つの端縁画定部21A1,21A2の間の間隙を埋めるように配置されている。

【選択図】図1

Description

後に本体となる焼成前本体と、焼成前本体と一体化され、後に第1の導体層となる第1の焼成前導体層とを形成する工程と、

焼成前本体と第1の焼成前導体層とを同時に焼成して、本体と第1の導体層とを形成する工程と、

本体の端面に対して、後に第2の導体層となる第2の焼成前導体層を形成する工程と、

第2の焼成前導体層を焼成して、第2の導体層を形成する工程とを備えている。

後に本体となる焼成前本体と、焼成前本体と一体化され、後に2つの規制部となる2つの焼成前規制部とを形成する工程と、

焼成前本体と2つの焼成前規制部とを同時に焼成して、本体と2つの規制部とを形成する工程と、

本体の端面に対して、後にインダクタ用導体層となる焼成前インダクタ用導体層を形成する工程と、

焼成前インダクタ用導体層を焼成して、インダクタ用導体層を形成する工程とを備えている。

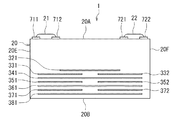

以下、本発明の実施の形態について図面を参照して詳細に説明する。始めに、図5を参照して、本発明の第1の実施の形態に係る電子部品の回路構成について説明する。本実施の形態に係る電子部品1は、バンドパスフィルタの機能を有している。図5に示したように、電子部品1は、信号の入力のために用いられる入力端子2と、信号の出力のために用いられる出力端子3と、入力端子2に電気的に接続された第1の共振器4と、出力端子3に電気的に接続された第2の共振器5と、キャパシタ15とを備えている。

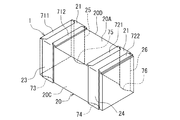

次に、図14および図15を参照して、本発明の第2の実施の形態について説明する。図14は、本実施の形態に係る電子部品1の外観を示す斜視図である。図15は、側面20C側から見た電子部品1の主要部分を示す説明図である。

次に、図16ないし図19を参照して、本発明の第3の実施の形態について説明する。図16は、本実施の形態に係る電子部品1の外観を示す斜視図である。図17は、本実施の形態における本体および第1の導体層を示す斜視図である。図18は、本実施の形態に係る電子部品1の製造方法における第2の焼成前導体層と焼成前側面端子とを形成する工程を示す斜視図である。図19は、本実施の形態に係る電子部品1の製造方法において第2の焼成前導体層と焼成前側面端子とが形成された後の状態を示す斜視図である。

次に、図20を参照して、本発明の第4の実施の形態について説明する。図20は、本実施の形態に係る電子部品1の外観を示す斜視図である。図20に示したように、本実施の形態に係る電子部品1は、第2の実施の形態と同様に、インダクタ用導体層21,22は、それぞれ1つの導体層によって構成されている。電子部品1は、誘電体よりなり、インダクタ用導体層21の長手方向に沿って延び、且つ互いの間に間隙を形成するように本体20の上面20Aに配置され、インダクタ用導体層21の位置を規制する2つの規制部711,712と、誘電体よりなり、インダクタ用導体層22の長手方向に沿って延び、且つ互いの間に間隙を形成するように本体20の上面20Aに配置され、インダクタ用導体層22の位置を規制する2つの規制部721,722とを備えている。規制部711,712,721,722を構成する誘電体は、セラミックであることが好ましい。

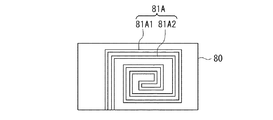

次に、図21および図22を参照して、本発明の第5の実施の形態について説明する。本実施の形態に係る電子部品は、平面渦巻き形状のインダクタ用導体層を備えたものである。図21は、インダクタ用導体層の第1の導体層を示す平面図である。図22は、インダクタ用導体層を示す平面図である。図22に示したように、本実施の形態に係る電子部品は、本体と、本体の端面としての上面80に配置された平面渦巻き形状のインダクタ用導体層81とを備えている。インダクタ用導体層81は、共に上面80に接する第1の導体層81Aと第2の導体層81Bとを有している。第1の導体層81Aと第2の導体層81Bは、いずれも、主に金属によって構成されている。図21に示したように、第1の導体層81Aは、インダクタ用導体層81の長手方向に沿って延び、互いの間に間隙を形成し、インダクタ用導体層81の長手方向に沿った2つの端縁を画定する2つの端縁画定部81A1,81A2を含んでいる。端縁画定部81A1,81A2の平面形状は、いずれも、平面渦巻き形状である。端縁画定部81A1,81A2の中心側の端部同士は連結されている。図22に示したように、第2の導体層81Bは、2つの端縁画定部81A1,81A2における外側の端縁よりはみ出すことなく、2つの端縁画定部81A1,81A2の間の間隙を埋めるように配置されている。

次に、図23および図24を参照して、本発明の第6の実施の形態について説明する。本実施の形態に係る電子部品は、ミアンダ形状のインダクタ用導体層を備えたものである。図23は、インダクタ用導体層の第1の導体層を示す平面図である。図24は、インダクタ用導体層を示す平面図である。図24に示したように、本実施の形態に係る電子部品は、本体と、本体の端面としての上面90に配置されたミアンダ形状のインダクタ用導体層91とを備えている。インダクタ用導体層91は、共に上面90に接する第1の導体層91Aと第2の導体層91Bとを有している。第1の導体層91Aと第2の導体層91Bは、いずれも、主に金属によって構成されている。図23に示したように、第1の導体層91Aは、インダクタ用導体層91の長手方向に沿って延び、互いの間に間隙を形成し、インダクタ用導体層91の長手方向に沿った2つの端縁を画定する2つの端縁画定部91A1,91A2を含んでいる。端縁画定部91A1,91A2の平面形状は、いずれも、ミアンダ形状である。図24に示したように、第2の導体層91Bは、2つの端縁画定部91A1,91A2における外側の端縁よりはみ出すことなく、2つの端縁画定部91A1,91A2の間の間隙を埋めるように配置されている。

Claims (12)

- 端面を有する本体と、

前記本体の前記端面に配置され、インダクタを構成するインダクタ用導体層とを備え、

前記本体と前記インダクタ用導体層は共に焼成により形成された電子部品であって、

前記本体は、セラミックよりなり、前記端面を形成する端面形成用誘電体層を含み、

前記インダクタ用導体層は、共に前記端面に接する第1の導体層と第2の導体層とを有し、

前記第1の導体層は、前記インダクタ用導体層の長手方向に沿って延び、互いの間に間隙を形成し、前記インダクタ用導体層の長手方向に沿った2つの端縁を画定する2つの端縁画定部を含み、

前記第2の導体層は、前記2つの端縁画定部における外側の端縁よりはみ出すことなく、前記2つの端縁画定部の間の間隙を埋めるように配置されていることを特徴とする電子部品。 - 前記電子部品は、前記インダクタ用導体層によって構成されたインダクタを有する共振器を備えていることを特徴とする請求項1記載の電子部品。

- 端面を有する本体と、

前記本体の前記端面に配置され、インダクタを構成するインダクタ用導体層とを備え、

前記本体と前記インダクタ用導体層は共に焼成により形成され、

前記本体は、セラミックよりなり、前記端面を形成する端面形成用誘電体層を含み、

前記インダクタ用導体層は、共に前記端面に接する第1の導体層と第2の導体層とを有し、

前記第1の導体層は、前記インダクタ用導体層の長手方向に沿って延び、互いの間に間隙を形成し、前記インダクタ用導体層の長手方向に沿った2つの端縁を画定する2つの端縁画定部を含み、

前記第2の導体層は、前記2つの端縁画定部における外側の端縁よりはみ出すことなく、前記2つの端縁画定部の間の間隙を埋めるように配置されている電子部品を製造する方法であって、

後に前記本体となる焼成前本体と、前記焼成前本体と一体化され、後に前記第1の導体層となる第1の焼成前導体層とを形成する工程と、

前記焼成前本体と前記第1の焼成前導体層とを同時に焼成して、前記本体と前記第1の導体層とを形成する工程と、

前記本体の前記端面に対して、後に前記第2の導体層となる第2の焼成前導体層を形成する工程と、

前記第2の焼成前導体層を焼成して、前記第2の導体層を形成する工程とを備えたことを特徴とする電子部品の製造方法。 - 前記電子部品は、前記インダクタ用導体層によって構成されたインダクタを有する共振器を備えていることを特徴とする請求項3記載の電子部品の製造方法。

- 前記本体は、更に、前記端面に対して垂直な側面を有し、

前記電子部品は、更に、前記本体の側面に配置され、且つ前記インダクタ用導体層に接続された側面端子を備え、

前記第2の焼成前導体層を形成する工程では、導体ペーストによって、前記第2の焼成前導体層と、後に前記側面端子となる焼成前側面端子とを、連続するように形成し、

前記第2の導体層を形成する工程では、前記第2の焼成前導体層と前記焼成前側面端子とを同時に焼成して、前記第2の導体層と前記側面端子とを形成することを特徴とする請求項3または4記載の電子部品の製造方法。 - 前記本体は、前記側面に形成され、前記焼成前側面端子を形成するために前記導体ペーストを導く溝部を有することを特徴とする請求項5記載の電子部品の製造方法。

- 端面を有する本体と、

前記本体の前記端面に配置され、インダクタを構成するインダクタ用導体層とを備え、

前記本体と前記インダクタ用導体層は共に焼成により形成された電子部品であって、

前記本体は、セラミックよりなり、前記端面を形成する端面形成用誘電体層を含み、

電子部品は、更に、誘電体よりなり、前記インダクタ用導体層の長手方向に沿って延び、且つ互いの間に間隙を形成するように前記本体の前記端面に配置され、前記インダクタ用導体層の位置を規制する2つの規制部を備え、

前記インダクタ用導体層は、前記2つの規制部における外側の端縁よりはみ出すことなく、前記2つの規制部の間の間隙を埋めるように配置されていることを特徴とする電子部品。 - 前記電子部品は、前記インダクタ用導体層によって構成されたインダクタを有する共振器を備えていることを特徴とする請求項7記載の電子部品。

- 端面を有する本体と、

前記本体の前記端面に配置され、インダクタを構成するインダクタ用導体層とを備え、

前記本体と前記インダクタ用導体層は共に焼成により形成され、

前記本体は、セラミックよりなり、前記端面を形成する端面形成用誘電体層を含み、

更に、誘電体よりなり、前記インダクタ用導体層の長手方向に沿って延び、且つ互いの間に間隙を形成するように前記本体の前記端面に配置され、前記インダクタ用導体層の位置を規制する2つの規制部を備え、

前記インダクタ用導体層は、前記2つの規制部における外側の端縁よりはみ出すことなく、前記2つの規制部の間の間隙を埋めるように配置されている電子部品を製造する方法であって、

後に前記本体となる焼成前本体と、前記焼成前本体と一体化され、後に前記2つの規制部となる2つの焼成前規制部とを形成する工程と、

前記焼成前本体と前記2つの焼成前規制部とを同時に焼成して、前記本体と前記2つの規制部とを形成する工程と、

前記本体の前記端面に対して、後に前記インダクタ用導体層となる焼成前インダクタ用導体層を形成する工程と、

前記焼成前インダクタ用導体層を焼成して、前記インダクタ用導体層を形成する工程とを備えたことを特徴とする電子部品の製造方法。 - 前記電子部品は、前記インダクタ用導体層によって構成されたインダクタを有する共振器を備えていることを特徴とする請求項9記載の電子部品の製造方法。

- 前記本体は、更に、前記端面に対して垂直な側面を有し、

前記電子部品は、更に、前記本体の側面に配置され、且つ前記インダクタ用導体層に接続された側面端子を備え、

前記焼成前インダクタ用導体層を形成する工程では、導体ペーストによって、前記焼成前インダクタ用導体層と、後に前記側面端子となる焼成前側面端子とを、連続するように形成し、

前記インダクタ用導体層を形成する工程では、前記焼成前インダクタ用導体層と前記焼成前側面端子とを同時に焼成して、前記インダクタ用導体層と前記側面端子とを形成することを特徴とする請求項9または10記載の電子部品の製造方法。 - 前記本体は、前記側面に形成され、前記焼成前側面端子を形成するために前記導体ペーストを導く溝部を有することを特徴とする請求項11記載の電子部品の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008216321A JP5262432B2 (ja) | 2008-08-26 | 2008-08-26 | 電子部品およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008216321A JP5262432B2 (ja) | 2008-08-26 | 2008-08-26 | 電子部品およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010056111A true JP2010056111A (ja) | 2010-03-11 |

| JP5262432B2 JP5262432B2 (ja) | 2013-08-14 |

Family

ID=42071751

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008216321A Expired - Fee Related JP5262432B2 (ja) | 2008-08-26 | 2008-08-26 | 電子部品およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5262432B2 (ja) |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03219605A (ja) * | 1990-01-24 | 1991-09-27 | Murata Mfg Co Ltd | 積層型インダクタンス素子 |

| JPH08265083A (ja) * | 1995-03-24 | 1996-10-11 | Mitsubishi Materials Corp | チップ型低域フィルタ |

| JPH09307389A (ja) * | 1996-05-10 | 1997-11-28 | Murata Mfg Co Ltd | 積層型lcフィルタ |

| JPH104015A (ja) * | 1996-06-17 | 1998-01-06 | Matsushita Electric Ind Co Ltd | 電子部品 |

| JPH11135351A (ja) * | 1997-10-27 | 1999-05-21 | Fuji Elelctrochem Co Ltd | 積層インダクタおよびその製造方法 |

| JP2002076704A (ja) * | 2000-08-31 | 2002-03-15 | Murata Mfg Co Ltd | 積層型lc複合部品 |

| JP2010041266A (ja) * | 2008-08-04 | 2010-02-18 | Tdk Corp | 積層型電子部品 |

-

2008

- 2008-08-26 JP JP2008216321A patent/JP5262432B2/ja not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03219605A (ja) * | 1990-01-24 | 1991-09-27 | Murata Mfg Co Ltd | 積層型インダクタンス素子 |

| JPH08265083A (ja) * | 1995-03-24 | 1996-10-11 | Mitsubishi Materials Corp | チップ型低域フィルタ |

| JPH09307389A (ja) * | 1996-05-10 | 1997-11-28 | Murata Mfg Co Ltd | 積層型lcフィルタ |

| JPH104015A (ja) * | 1996-06-17 | 1998-01-06 | Matsushita Electric Ind Co Ltd | 電子部品 |

| JPH11135351A (ja) * | 1997-10-27 | 1999-05-21 | Fuji Elelctrochem Co Ltd | 積層インダクタおよびその製造方法 |

| JP2002076704A (ja) * | 2000-08-31 | 2002-03-15 | Murata Mfg Co Ltd | 積層型lc複合部品 |

| JP2010041266A (ja) * | 2008-08-04 | 2010-02-18 | Tdk Corp | 積層型電子部品 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5262432B2 (ja) | 2013-08-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6538531B2 (en) | Multilayered LC composite component and method for adjusting frequency of the same | |

| JP4458296B2 (ja) | 誘電体共振器、誘電体フィルタ及びその特性調整方法 | |

| US8169288B2 (en) | Electronic component and method for making the same | |

| JP4682890B2 (ja) | 積層型ノイズフィルタ | |

| US20140132385A1 (en) | Multilayer chip inductor and production method for same | |

| JP6460328B2 (ja) | Lc複合部品 | |

| JPWO2013058144A1 (ja) | 複合電子部品 | |

| JP2004180032A (ja) | 誘電体フィルタ | |

| JP2008017243A (ja) | 電子部品 | |

| JP5601334B2 (ja) | 電子部品 | |

| JP5262432B2 (ja) | 電子部品およびその製造方法 | |

| JP4926031B2 (ja) | フィルタ装置 | |

| JP2009246889A (ja) | 積層型電子部品 | |

| JP4900728B2 (ja) | 積層型電子部品 | |

| JP4354943B2 (ja) | 積層型誘電体共振器およびバンドパスフィルタ | |

| JP4415279B2 (ja) | 電子部品 | |

| JP4986882B2 (ja) | フィルタ装置 | |

| JP4873274B2 (ja) | 積層型電子部品 | |

| JP2010123649A (ja) | 積層デバイス | |

| JP5293633B2 (ja) | 積層型電子部品 | |

| JP2007274283A (ja) | 積層型誘電体共振器およびその製造方法 | |

| JP4873273B2 (ja) | 積層型電子部品 | |

| JP4821814B2 (ja) | 積層型電子部品 | |

| JP4457362B2 (ja) | 電子部品 | |

| JP2007235465A (ja) | 積層型誘電体共振器およびバンドパスフィルタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110506 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120426 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120531 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120723 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130307 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130415 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5262432 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |