JP2010040635A - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP2010040635A JP2010040635A JP2008199487A JP2008199487A JP2010040635A JP 2010040635 A JP2010040635 A JP 2010040635A JP 2008199487 A JP2008199487 A JP 2008199487A JP 2008199487 A JP2008199487 A JP 2008199487A JP 2010040635 A JP2010040635 A JP 2010040635A

- Authority

- JP

- Japan

- Prior art keywords

- film

- region

- semiconductor device

- insulating film

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 186

- 238000004519 manufacturing process Methods 0.000 title claims description 72

- 238000003860 storage Methods 0.000 claims abstract description 125

- 239000000758 substrate Substances 0.000 claims abstract description 119

- 229910052731 fluorine Inorganic materials 0.000 claims abstract description 100

- 239000011737 fluorine Substances 0.000 claims abstract description 100

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 claims abstract 5

- 238000005468 ion implantation Methods 0.000 claims description 153

- 238000000034 method Methods 0.000 claims description 99

- 238000010438 heat treatment Methods 0.000 claims description 83

- 239000012535 impurity Substances 0.000 claims description 49

- 230000008569 process Effects 0.000 claims description 44

- 239000004020 conductor Substances 0.000 claims description 43

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 37

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 37

- 230000003647 oxidation Effects 0.000 claims description 19

- 238000007254 oxidation reaction Methods 0.000 claims description 19

- 230000006870 function Effects 0.000 claims description 18

- 230000003213 activating effect Effects 0.000 claims description 17

- 238000012545 processing Methods 0.000 claims description 2

- 230000001590 oxidative effect Effects 0.000 claims 2

- 150000002500 ions Chemical class 0.000 claims 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 abstract description 90

- 229910052710 silicon Inorganic materials 0.000 abstract description 90

- 239000010703 silicon Substances 0.000 abstract description 90

- 230000002093 peripheral effect Effects 0.000 description 101

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 93

- 229920002120 photoresistant polymer Polymers 0.000 description 40

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 35

- 230000000694 effects Effects 0.000 description 25

- 230000004888 barrier function Effects 0.000 description 23

- 230000014759 maintenance of location Effects 0.000 description 21

- 229910052581 Si3N4 Inorganic materials 0.000 description 19

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 19

- 125000006850 spacer group Chemical group 0.000 description 18

- LPQOADBMXVRBNX-UHFFFAOYSA-N ac1ldcw0 Chemical compound Cl.C1CN(C)CCN1C1=C(F)C=C2C(=O)C(C(O)=O)=CN3CCSC1=C32 LPQOADBMXVRBNX-UHFFFAOYSA-N 0.000 description 17

- 238000005530 etching Methods 0.000 description 17

- 230000007547 defect Effects 0.000 description 13

- 238000009792 diffusion process Methods 0.000 description 10

- 238000012795 verification Methods 0.000 description 9

- 230000008859 change Effects 0.000 description 8

- 239000000969 carrier Substances 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 150000004767 nitrides Chemical class 0.000 description 7

- 238000000206 photolithography Methods 0.000 description 6

- 230000001133 acceleration Effects 0.000 description 5

- 238000009826 distribution Methods 0.000 description 5

- 238000002955 isolation Methods 0.000 description 5

- 230000005669 field effect Effects 0.000 description 4

- -1 fluorine ions Chemical class 0.000 description 4

- 229910052735 hafnium Inorganic materials 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 230000005641 tunneling Effects 0.000 description 4

- 230000004913 activation Effects 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 2

- 238000009825 accumulation Methods 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 230000000415 inactivating effect Effects 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 229910003855 HfAlO Inorganic materials 0.000 description 1

- 229910004129 HfSiO Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000002800 charge carrier Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000011982 device technology Methods 0.000 description 1

- 230000005685 electric field effect Effects 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 230000010365 information processing Effects 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 238000011282 treatment Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40117—Multistep manufacturing processes for data storage electrodes the electrodes comprising a charge-trapping insulator

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/4234—Gate electrodes for transistors with charge trapping gate insulator

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/30—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/40—EEPROM devices comprising charge-trapping gate insulators characterised by the peripheral circuit region

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

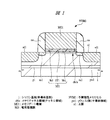

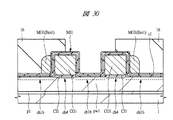

【解決手段】電荷蓄積膜MI1に対して電荷を授受することで記憶動作を行う不揮発性メモリセルNVM1を有する半導体装置であって、不揮発性メモリセルNVM1は、シリコン基板1の主面s1に形成されたpウェルpw1と、主面s1上に電荷蓄積膜MI1を隔てて形成されたメモリゲート電極MG1とを有し、更に、シリコン基板1の主面s1のうち、電荷蓄積膜MI1下に位置するメモリチャネル領域ch1aにフッ素を含んでいる。

【選択図】図1

Description

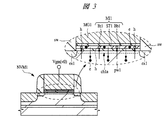

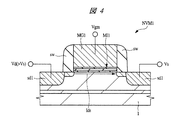

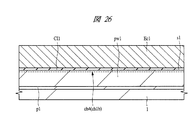

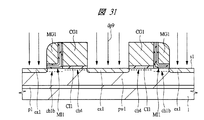

本実施の形態1の半導体装置が有する不揮発性メモリセルの構造を、図1を用いて詳しく説明する。図1は、本実施の形態1の不揮発性メモリセルNVM1の要部断面図である。本実施の形態1の半導体装置は、シリコン基板(半導体基板)1に形成された複数の不揮発性メモリセルNVM1を有する。

本実施の形態2では、上記実施の形態1の半導体装置が有する不揮発性メモリセルNVM1において、メモリチャネル領域ch1aにフッ素を導入する方法に関して、種々の方法を説明する。以下では、不揮発性メモリセルNVM1を形成する工程の途中の工程として、本実施の形態2の製造方法を説明するが、それ以外の工程は、上記実施の形態1で説明したものと同様であり、重複した説明は省略する。

本実施の形態3の半導体装置が有する不揮発性メモリセルの構造を、図23を用いて詳しく説明する。図23は、本実施の形態3の不揮発性メモリセルNVM2の要部断面図である。本実施の形態3の不揮発性メモリセルNVM2は、上記実施の形態1の不揮発性メモリセルNVM1と比較して、以下の異なる構成を有する。

2 分離部

3〜5,8〜16 フォトレジスト膜

6 酸化シリコン膜

7 多結晶シリコン膜

7n n型多結晶シリコン膜

7p p型多結晶シリコン膜

Bb1 下部バリア膜(第1絶縁膜)

Bt1 上部バリア膜(第3絶縁膜)

CG1 制御ゲート電極

ch1a,ch1b メモリチャネル領域(チャネル領域)

ch2,ch3 周辺チャネル領域

ch4 制御チャネル領域

CI1 制御ゲート絶縁膜

dp1a〜dp1e 第1イオン注入

dp2〜dp9 イオン注入

e 電子

Ec1 制御ゲート導体膜

Em1 メモリゲート導体膜

er1 消去特性

ex1 メモリエクステンション領域(第2半導体領域)

ex2 n型周辺エクステンション領域

ex3 p型周辺エクステンション領域

Gn n型周辺ゲート電極

Gp p型周辺ゲート電極

h 正孔(ホール)

Ids ソース・ドレイン電流

IG 周辺ゲート絶縁膜

MG1 メモリゲート電極

MI1 電荷蓄積膜

NVM1,NVM2 不揮発性メモリセル

nw1 周辺nウェル

p1 半導体領域

pw1 pウェル(第1半導体領域)

pw2 周辺pウェル

Qn n型MISトランジスタ

Qp p型MISトランジスタ

Rm メモリ領域

Rp 周辺領域

Rpn n型周辺領域

Rpp p型周辺領域

s1 主面

sd1 メモリソース・ドレイン領域(第3半導体領域)

sd2 n型周辺ソース・ドレイン領域

sd3 p型周辺ソース・ドレイン領域

ST1 電荷ストレージ膜(第2絶縁膜)

sw サイドウォールスペーサ

Vgm メモリゲート電圧

wr1,wr2 書き込み特性

Claims (16)

- 半導体基板の主面に複数の不揮発性メモリセルを形成する工程を有する半導体装置の製造方法であって、

前記不揮発性メモリセルを形成する工程は、

(a)前記半導体基板の主面に、第1導電型の第1半導体領域を形成する工程と、

(b)前記半導体基板の主面上のうち、前記第1半導体領域に平面的に含まれる位置に、電荷蓄積膜を隔ててメモリゲート電極を形成する工程と、

(c)前記半導体基板の主面のうちチャネル領域に、第1イオン注入によってフッ素を注入した後、第1熱処理によって前記フッ素を活性化する工程とを有し、

前記チャネル領域は、前記半導体基板の主面のうち、前記(b)工程で形成する前記電荷蓄積膜下に位置する領域であり、

前記(c)工程は、少なくとも前記(a)工程を終えた後に施し、

前記不揮発性メモリセルは、前記電荷蓄積膜に対して電荷を授受して記憶動作を行うことを特徴とする半導体装置の製造方法。 - 請求項1記載の半導体装置の製造方法において、

前記(c)工程の前記第1イオン注入では、前記チャネル領域に対し、1×1013〜1×1015cm−2のドーズ量でフッ素を注入することを特徴とする半導体装置の製造方法。 - 請求項2記載の半導体装置の製造方法において、

前記(b)工程では、前記電荷蓄積膜として、第1絶縁膜、第2絶縁膜、および、第3絶縁膜を順に形成し、

前記第2絶縁膜は、電荷を捕獲する機能を有する絶縁膜であり、

前記第2絶縁膜を挟む前記第1および第3絶縁膜は、前記第2絶縁膜に捕獲された電荷の外部への漏出を防ぐ機能を有する絶縁膜であり、

前記第1および第3絶縁膜として、酸化シリコンを主体とする絶縁膜を形成することを特徴とする半導体装置の製造方法。 - 請求項3記載の半導体装置の製造方法において、

前記(c)工程の前記第1イオン注入は、前記(a)工程を終えた後、前記(b)工程の前に施すことを特徴とする半導体装置の製造方法。 - 請求項4記載の半導体装置の製造方法において、

前記(b)工程では、前記半導体基板を熱酸化することで前記第1絶縁膜を形成し、

前記(c)工程の前記第1熱処理は、前記(b)工程で前記第1絶縁膜を形成するための熱酸化と同一の工程で施すことを特徴とする半導体装置の製造方法。 - 請求項3記載の半導体装置の製造方法において、

前記(b)工程は、

(b1)前記半導体基板の主面上に、前記電荷蓄積膜を隔ててメモリゲート導体膜を形成する工程と、

(b2)前記メモリゲート導体膜を加工して、前記メモリゲート電極を形成する工程とを有し、

前記(c)工程の第1イオン注入は、前記(b1)工程の後、前記(b2)工程の前に施すことを特徴とする半導体装置の製造方法。 - 請求項3記載の半導体装置の製造方法において、

前記不揮発性メモリセルを形成する工程は、更に、

(d)前記メモリゲート電極の側方下部のうち、前記第1半導体領域内の前記半導体基板の主面に、前記第1導電型と逆導電型である第2導電型の第2半導体領域を形成する工程を有し、

前記(d)工程では、該当の前記半導体基板の主面に第2導電型となる不純物をイオン注入し、熱処理を施すことで前記第2半導体領域を形成し、

前記(c)工程の第1イオン注入は、前記(d)工程における前記第2半導体領域を形成するためのイオン注入の直前または直後に施すことを特徴とする半導体装置の製造方法。 - 請求項7記載の半導体装置の製造方法において、

前記(c)工程の前記第1熱処理は、前記(d)工程における前記第2半導体領域を形成するための熱処理と同一の工程で施すことを特徴とする半導体装置の製造方法。 - 請求項3記載の半導体装置の製造方法において、

前記不揮発性メモリセルを形成する工程は、更に、

(d)前記メモリゲート電極の側方下部のうち、前記第1半導体領域内の前記半導体基板の主面に、前記第1導電型と逆導電型である第2導電型の第2半導体領域を形成する工程と、

(e)前記メモリゲート電極の側方下部のうち、前記第1半導体領域内の前記半導体基板の主面であって、かつ、平面的に見て、前記第2半導体領域の外側に、第2導電型の第3半導体領域を形成する工程とを有し、

前記(d)および(e)工程では、前記第3半導体領域の第2導電型不純物濃度は前記第2半導体領域の第2導電型不純物濃度よりも高くなるようにして、それぞれ、前記第2および第3半導体領域を形成し、

前記(e)工程では、該当の前記半導体基板の主面に第2導電型となる不純物イオンを注入し、熱処理を施すことで前記第3半導体領域を形成し、

前記(c)工程の第1イオン注入は、前記(e)工程における前記第2半導体領域を形成するためのイオン注入の直前または直後に施すことを特徴とする半導体装置の製造方法。 - 請求項9記載の半導体装置の製造方法において、

前記(c)工程の前記第1熱処理は、前記(e)工程における前記第3半導体領域を形成するための熱処理と同一の工程で施すことを特徴とする半導体装置の製造方法。 - 請求項3記載の半導体装置の製造方法において、

前記不揮発性メモリセルを形成する工程は、前記(a)工程の後、前記(b)工程の前に、更に、

(d)前記半導体基板の主面上のうち、前記第1半導体領域に平面的に含まれる位置に、制御ゲート絶縁膜を隔てて制御ゲート電極を形成する工程を有し、

前記(d)工程では、前記制御ゲート絶縁膜として、酸化シリコンを主体とする絶縁膜を形成し、

前記(b)工程では、前記(d)工程で形成した前記制御ゲート電極に隣り合うようにして、前記電荷蓄積膜を隔てて前記メモリゲート電極を形成することを特徴とする半導体装置の製造方法。 - 請求項11記載の半導体装置の製造方法において、

前記(c)工程の前記第1イオン注入は、前記(a)工程を終えた後、前記(d)工程の前に施すことを特徴とする半導体装置の製造方法。 - 請求項12記載の半導体装置の製造方法において、

前記(d)工程では、前記半導体基板を熱酸化することで前記制御ゲート絶縁膜を形成し、

前記(c)工程の前記第1熱処理は、前記(d)工程で前記制御ゲート絶縁膜を形成するための熱酸化と同一の工程で施すことを特徴とする半導体装置の製造方法。 - 半導体基板に形成された複数の不揮発性メモリセルを有する半導体装置であって、

前記不揮発性メモリセルは、

(a)前記半導体基板の主面に形成された、第1導電型の第1半導体領域と、

(b)前記半導体基板の主面上のうち、前記第1半導体領域に平面的に含まれる位置に、電荷蓄積膜を隔てて配置されたメモリゲート電極とを有し、

前記半導体基板の主面のうち、前記電荷蓄積膜下に位置するチャネル領域はフッ素を含み、

前記不揮発性メモリセルは、前記電荷蓄積膜に対して電荷を授受して記憶動作を行うことを特徴とする半導体装置。 - 請求項14記載の半導体装置において、

前記電荷蓄積膜は、前記半導体基板に近い方から順に配置された、第1絶縁膜、第2絶縁膜、および、第3絶縁膜を有し、

前記第2絶縁膜は、電荷を捕獲する機能を有する絶縁膜であり、

前記第2絶縁膜を挟む前記第1および第3絶縁膜は、前記第2絶縁膜に捕獲された電荷の外部への漏出を防ぐ機能を有する絶縁膜であり、

前記第1および第3絶縁膜は、酸化シリコンを主体とする絶縁膜であることを特徴とする半導体装置。 - 請求項15記載の半導体装置において、

前記不揮発性メモリセルは、更に、

(c)前記半導体基板の主面上のうち、前記第1半導体領域に平面的に含まれる位置に、制御ゲート絶縁膜を隔てて配置された制御ゲート電極を有し、

前記メモリゲート電極は、前記電荷蓄積膜を隔てて、前記制御ゲート電極に隣り合うようにして配置されていることを特徴とする半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008199487A JP5406479B2 (ja) | 2008-08-01 | 2008-08-01 | 半導体装置の製造方法 |

| US12/495,957 US7994012B2 (en) | 2008-08-01 | 2009-07-01 | Semiconductor device and a method of manufacturing the same |

| US13/186,466 US20110272757A1 (en) | 2008-08-01 | 2011-07-19 | Semiconductor device and a method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008199487A JP5406479B2 (ja) | 2008-08-01 | 2008-08-01 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010040635A true JP2010040635A (ja) | 2010-02-18 |

| JP5406479B2 JP5406479B2 (ja) | 2014-02-05 |

Family

ID=41607437

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008199487A Expired - Fee Related JP5406479B2 (ja) | 2008-08-01 | 2008-08-01 | 半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7994012B2 (ja) |

| JP (1) | JP5406479B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8329545B1 (en) * | 2008-12-30 | 2012-12-11 | Micron Technology, Inc. | Method of fabricating a charge trap NAND flash memory |

| KR20150028189A (ko) | 2013-09-05 | 2015-03-13 | 르네사스 일렉트로닉스 가부시키가이샤 | 반도체 장치 및 그 제조 방법 |

| CN105449003A (zh) * | 2014-08-28 | 2016-03-30 | 中芯国际集成电路制造(上海)有限公司 | 一种半导体器件及其制造方法和电子装置 |

| JP6407644B2 (ja) * | 2014-09-24 | 2018-10-17 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| CN106409838A (zh) * | 2016-10-31 | 2017-02-15 | 上海华虹宏力半导体制造有限公司 | Sonos存储器的工艺方法 |

| US11233148B2 (en) * | 2017-11-06 | 2022-01-25 | Intel Corporation | Reducing band-to-band tunneling in semiconductor devices |

| JP7089967B2 (ja) * | 2018-07-17 | 2022-06-23 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000012802A (ja) * | 1998-06-17 | 2000-01-14 | Hitachi Ltd | 半導体集積回路装置の製造方法および半導体集積回路装置 |

| JP2002190535A (ja) * | 2000-12-21 | 2002-07-05 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| JP2004247633A (ja) * | 2003-02-17 | 2004-09-02 | Renesas Technology Corp | 半導体装置 |

| US6949433B1 (en) * | 2003-02-07 | 2005-09-27 | Fasl Llc | Method of formation of semiconductor resistant to hot carrier injection stress |

| JP2007281092A (ja) * | 2006-04-04 | 2007-10-25 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| WO2008059768A1 (fr) * | 2006-11-14 | 2008-05-22 | Nec Corporation | Dispositif à semi-conducteur |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6191463B1 (en) * | 1997-07-15 | 2001-02-20 | Kabushiki Kaisha Toshiba | Apparatus and method of improving an insulating film on a semiconductor device |

| JP2000236074A (ja) | 1998-12-17 | 2000-08-29 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP2000269492A (ja) * | 1999-03-16 | 2000-09-29 | Nec Corp | 半導体装置の製造方法 |

| US6670664B1 (en) * | 2002-10-22 | 2003-12-30 | Taiwan Semiconductor Manufacturing Co., Ltd. | Single transistor random access memory (1T-RAM) cell with dual threshold voltages |

| JP2005197547A (ja) | 2004-01-09 | 2005-07-21 | Elpida Memory Inc | 半導体装置の製造方法 |

| KR20060076011A (ko) * | 2004-12-29 | 2006-07-04 | 삼성전자주식회사 | 반도체 소자 및 그 형성 방법 |

| JP2007048882A (ja) | 2005-08-09 | 2007-02-22 | Toyohashi Univ Of Technology | 半導体装置およびその製造方法 |

| US20070202645A1 (en) * | 2006-02-28 | 2007-08-30 | Tien Ying Luo | Method for forming a deposited oxide layer |

| US7449753B2 (en) * | 2006-04-10 | 2008-11-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Write margin improvement for SRAM cells with SiGe stressors |

| CN100590853C (zh) * | 2006-12-15 | 2010-02-17 | 中芯国际集成电路制造(上海)有限公司 | 半导体存储器及其形成方法 |

-

2008

- 2008-08-01 JP JP2008199487A patent/JP5406479B2/ja not_active Expired - Fee Related

-

2009

- 2009-07-01 US US12/495,957 patent/US7994012B2/en active Active

-

2011

- 2011-07-19 US US13/186,466 patent/US20110272757A1/en not_active Abandoned

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000012802A (ja) * | 1998-06-17 | 2000-01-14 | Hitachi Ltd | 半導体集積回路装置の製造方法および半導体集積回路装置 |

| JP2002190535A (ja) * | 2000-12-21 | 2002-07-05 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| US6949433B1 (en) * | 2003-02-07 | 2005-09-27 | Fasl Llc | Method of formation of semiconductor resistant to hot carrier injection stress |

| JP2004247633A (ja) * | 2003-02-17 | 2004-09-02 | Renesas Technology Corp | 半導体装置 |

| JP2007281092A (ja) * | 2006-04-04 | 2007-10-25 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| WO2008059768A1 (fr) * | 2006-11-14 | 2008-05-22 | Nec Corporation | Dispositif à semi-conducteur |

Also Published As

| Publication number | Publication date |

|---|---|

| US20110272757A1 (en) | 2011-11-10 |

| JP5406479B2 (ja) | 2014-02-05 |

| US20100025754A1 (en) | 2010-02-04 |

| US7994012B2 (en) | 2011-08-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5142494B2 (ja) | 半導体装置の製造方法 | |

| US9673339B2 (en) | Semiconductor storage device and manufacturing method thereof | |

| JP5007017B2 (ja) | 半導体装置の製造方法 | |

| US7709315B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP5406479B2 (ja) | 半導体装置の製造方法 | |

| KR101038873B1 (ko) | 플래시 메모리 소자의 제조 방법 | |

| JP2008288503A (ja) | 半導体装置 | |

| TWI731066B (zh) | 半導體裝置之製造方法 | |

| KR20040093404A (ko) | 반도체장치 및 그 제조방법 | |

| US20070269972A1 (en) | Method of manufacturing a semiconductor device | |

| JP2008277530A (ja) | 不揮発性半導体記憶装置 | |

| US8546862B2 (en) | Memory cell, an array, and a method for manufacturing a memory cell | |

| KR20030086823A (ko) | 평탄하지 않은 게이트 절연막을 구비하는 비휘발성 메모리장치 및 그 제조 방법 | |

| JP5161494B2 (ja) | 半導体記憶装置 | |

| US8044455B2 (en) | Semiconductor device and method of manufacturing the same | |

| US20160064226A1 (en) | Method of manufacturing semiconductor device | |

| EP2074649A2 (en) | A multi-transistor based non-volatile memory cell with dual threshold voltage | |

| JP2006332143A (ja) | 半導体装置及びその製造方法 | |

| JP2011096772A (ja) | 半導体装置およびその製造方法 | |

| US20150008507A1 (en) | Semiconductor device and manufacturing method thereof | |

| JP2010062359A (ja) | 半導体装置の製造方法 | |

| JP2006080567A (ja) | 半導体集積回路装置およびその製造方法 | |

| JP2009283731A (ja) | 半導体装置およびその製造方法 | |

| JP5091546B2 (ja) | 半導体装置の製造方法 | |

| JP2014103345A (ja) | 半導体装置および半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110801 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130723 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130920 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131008 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131101 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5406479 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |