JP2010040611A - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2010040611A JP2010040611A JP2008199073A JP2008199073A JP2010040611A JP 2010040611 A JP2010040611 A JP 2010040611A JP 2008199073 A JP2008199073 A JP 2008199073A JP 2008199073 A JP2008199073 A JP 2008199073A JP 2010040611 A JP2010040611 A JP 2010040611A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- manufacturing

- semiconductor substrate

- buried diffusion

- impurity

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Thyristors (AREA)

Abstract

【解決手段】半導体基板102に不純物イオンを注入する不純物イオン注入工程S112と、半導体基板102に注入された不純物イオンを活性化するアニール工程S114と、アニール工程で活性化された不純物原子の埋め込み拡散を行う埋め込み拡散工程S116とをこの順序で含む半導体装置の製造方法において、不純物イオン注入工程S112においては、下地酸化膜を介することなく半導体基板102に直接不純物イオンを注入し、アニール工程S114と埋め込み拡散工程S116とを同一の熱処理炉で行うとともに、アニール工程S114終了後、熱処理炉中に酸素ガスを導入した状態でアニール温度T1から埋め込み拡散温度T2に昇温することを特徴とする半導体装置の製造方法。

【選択図】図1

Description

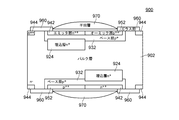

2端子型双方向性サイリスタ800は、図8に示すように、例えば、n−型半導体基板802の一方の表面及び他方の表面それぞれにベース層832、エミッタ層842及びオーミック層852が形成され、さらに、ガラス層860及び半田層870が形成された構成を有し、このような2端子型双方向性サイリスタ800は、サージ電圧やサージ電流から電子機器を防護するサージ防護素子として好適に用いることができる。

従来の2端子型双方向性サイリスタ900は、図9に示すように、ベース層932よりも深い位置にn+型埋め込み拡散領域924が形成されている。

このため、従来の2端子型双方向性サイリスタ900は、2端子型双方向性サイリスタ800よりも高耐圧で高性能(高速応答性能、サージ印加時電圧上昇抑制性能)な2端子型双方向性サイリスタとなる。

これに対して、半導体装置が2端子型双方向性サイリスタである場合には、ベース領域、エミッタ領域及びオーミック領域ともに比較的深い位置まで不純物が導入された構造を有するため、上記のような問題は発生しにくいものとなる。

実施形態1に係る2端子型双方向性サイリスタの製造方法は、埋め込み拡散領域形成工程S110、ベース層形成工程S120、エミッタ層形成工程S130、オーミック層形成工程S140をこの順序で含むものである。以下、これら各工程を順次説明する。

図1は、実施形態1に係る半導体装置の製造方法のうち埋め込み拡散領域形成工程S110を説明するために示す図である。図1(a)〜図1(d)は埋め込み拡散領域形成工程S110における各工程を示す図である。

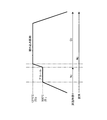

図2は、実施形態1に係る半導体装置の製造方法のうちアニール工程S114〜埋め込み拡散工程S116における、処理温度と導入ガスの種類を説明するために示す図である。

図4は、実施形態1に係る半導体装置の製造方法のうちのエミッタ層形成工程S130を説明するために示す図である。

図5は、実施形態1に係る半導体装置の製造方法のうちのオーミック層形成工程S140を説明するために示す図である。

図6は、実施形態1に係る半導体装置の製造方法によって製造された半導体装置(2端子型双方向性サイリスタ)の構成を示す図である。

ベース層を形成するための不純物イオン注入用マスクM2(例えば、フォトレジスト又はシリコン酸化膜。)を半導体基板102の一方の表面及び他方の表面にそれぞれ形成し、当該不純物イオン注入用マスクM2の開口部からp型不純物イオン(例えばボロンイオン)をそれぞれ注入する(図3(a)参照。)。その後、不純物イオン注入用マスクM2を除去してアニール工程を行い、p型不純物を活性化して(図3(b)参照。)、半導体基板102の一方の表面及び他方の表面それぞれにベース層132を形成する。なお、ベース層132の深さは例えば25μmであり、p型不純物の不純物濃度は例えば5×1018cm−3である。

エミッタ層を形成するための不純物イオン注入用マスクM3(例えば、フォトレジスト又はシリコン酸化膜。)を半導体基板102の一方の表面及び他方の表面にそれぞれ形成し、当該不純物イオン注入用マスクM3の開口部からn型不純物イオン(例えばリンイオン)をそれぞれ注入する(図4(a)参照。)。その後、不純物イオン注入用マスクM3を除去してアニール工程を行い、n型不純物を活性化して(図4(b)参照。)、半導体基板102の一方の表面及び他方の表面それぞれにエミッタ層142及びチャネルストッパ144を形成する。なお、エミッタ層142の深さは例えば10μmであり、n型不純物の不純物濃度は例えば1×1019cm−3である。

オーミック層を形成するための不純物イオン注入用マスクM4(例えば、フォトレジスト又はシリコン酸化膜。)を半導体基板102の一方の表面及び他方の表面にそれぞれ形成し、当該不純物イオン注入用マスクM4の開口部からp型不純物イオン(例えばボロンイオン)をそれぞれ注入する(図5(a)参照。)。その後、不純物イオン注入用マスクM4を除去してアニール工程を行い、p型不純物を活性化して(図5(b)参照。)、半導体基板102の一方の表面及び他方の表面それぞれにオーミック層152を形成する。なお、オーミック層152の深さは例えば10μmであり、p型不純物の不純物濃度は例えば1×1019cm−3である。

図7は、実施形態2及び3に係る半導体装置の製造方法のうちアニール工程S114〜埋め込み拡散工程S116における、処理温度と導入ガスの種類を説明するために示す図である。

Claims (4)

- 半導体基板の表面に不純物イオン注入用マスクを形成し、当該不純物イオン注入用マスクの開口部から前記半導体基板に不純物イオンを注入する不純物イオン注入工程と、

前記半導体基板を所定のアニール温度に加熱して前記半導体基板に注入された不純物イオンを活性化するアニール工程と、

前記半導体基板を前記アニール温度よりも高い所定の埋め込み拡散温度に加熱して前記アニール工程で活性化された不純物原子の埋め込み拡散を行う埋め込み拡散工程とをこの順序で含む半導体装置の製造方法において、

前記不純物イオン注入工程においては、下地酸化膜を介することなく前記半導体基板に直接前記不純物イオンを注入し、

前記アニール工程と前記埋め込み拡散工程とを同一の熱処理炉で行うとともに、前記アニール工程終了後、前記熱処理炉中に酸素ガスを導入した状態で前記アニール温度から前記埋め込み拡散温度に昇温することを特徴とする半導体装置の製造方法。 - 請求項1に記載の半導体装置の製造方法において、

前記熱処理炉中に酸素ガスを導入した状態のまま前記埋め込み拡散工程を開始することを特徴とする半導体装置の製造方法。 - 請求項2に記載の半導体装置の製造方法において、

前記埋め込み拡散工程の途中から、前記熱処理炉中に酸素ガスの代わりに不活性ガスを導入することを特徴とする半導体装置の製造方法。 - 請求項1〜3のいずれかに記載の半導体装置の製造方法において、

前記半導体装置は、2端子型双方向性サイリスタであることを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008199073A JP5255942B2 (ja) | 2008-07-31 | 2008-07-31 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008199073A JP5255942B2 (ja) | 2008-07-31 | 2008-07-31 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010040611A true JP2010040611A (ja) | 2010-02-18 |

| JP5255942B2 JP5255942B2 (ja) | 2013-08-07 |

Family

ID=42012875

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008199073A Expired - Fee Related JP5255942B2 (ja) | 2008-07-31 | 2008-07-31 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5255942B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113161237A (zh) * | 2021-04-20 | 2021-07-23 | 江苏韦达半导体有限公司 | 内沟槽台面工艺触发二极管芯片的制作工艺 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108538722A (zh) * | 2018-04-03 | 2018-09-14 | 苏州德森瑞芯半导体科技有限公司 | 放电管生产方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0462840A (ja) * | 1990-06-25 | 1992-02-27 | Kawasaki Steel Corp | 半導体基板の熱処理方法 |

| JPH04170022A (ja) * | 1990-11-01 | 1992-06-17 | Mitsubishi Materials Corp | 埋め込み層の形成方法 |

| JPH05275687A (ja) * | 1991-05-21 | 1993-10-22 | Shindengen Electric Mfg Co Ltd | プレ−ナ型二端子双方向性サイリスタ |

| JP2002043325A (ja) * | 2000-07-27 | 2002-02-08 | Sanyo Electric Co Ltd | 高耐圧半導体装置の製造方法 |

| JP2002324846A (ja) * | 2001-04-25 | 2002-11-08 | Sanken Electric Co Ltd | 半導体装置及びその製造方法 |

-

2008

- 2008-07-31 JP JP2008199073A patent/JP5255942B2/ja not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0462840A (ja) * | 1990-06-25 | 1992-02-27 | Kawasaki Steel Corp | 半導体基板の熱処理方法 |

| JPH04170022A (ja) * | 1990-11-01 | 1992-06-17 | Mitsubishi Materials Corp | 埋め込み層の形成方法 |

| JPH05275687A (ja) * | 1991-05-21 | 1993-10-22 | Shindengen Electric Mfg Co Ltd | プレ−ナ型二端子双方向性サイリスタ |

| JP2002043325A (ja) * | 2000-07-27 | 2002-02-08 | Sanyo Electric Co Ltd | 高耐圧半導体装置の製造方法 |

| JP2002324846A (ja) * | 2001-04-25 | 2002-11-08 | Sanken Electric Co Ltd | 半導体装置及びその製造方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113161237A (zh) * | 2021-04-20 | 2021-07-23 | 江苏韦达半导体有限公司 | 内沟槽台面工艺触发二极管芯片的制作工艺 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5255942B2 (ja) | 2013-08-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101340002B1 (ko) | Soi웨이퍼의 제조방법 | |

| JPH10209168A (ja) | 半導体装置の製造方法 | |

| WO2016063630A1 (ja) | 炭化珪素半導体装置 | |

| CN101180709A (zh) | 非对称双向瞬态电压抑制器及其形成方法 | |

| WO2013145022A1 (ja) | 炭化珪素半導体装置の製造方法 | |

| CN111727506B (zh) | 半导体装置以及半导体装置的制造方法 | |

| JP5255942B2 (ja) | 半導体装置の製造方法 | |

| JP2006179864A (ja) | 半導体デバイス | |

| JPH06112146A (ja) | 拡散型シリコン素子基板の製造方法 | |

| JP2009218381A (ja) | SOI(Silicononinsulator)基板の製造方法 | |

| CN107316863A (zh) | 瞬态电压抑制器及其制作方法 | |

| JP2016042570A (ja) | 半導体用の最適化層 | |

| JP2010040786A (ja) | 半導体装置の製造方法 | |

| CN108010840B (zh) | 掺杂半导体器件的制备方法和半导体器件 | |

| JPWO2007072624A1 (ja) | Soi基板の製造方法およびsoi基板 | |

| TW200410317A (en) | Semiconductor device and method of manufacturing the same | |

| JP4539098B2 (ja) | 貼り合わせ基板の製造方法 | |

| JP2005135979A (ja) | 絶縁ゲート型バイポーラトランジスタ及びその製造方法 | |

| JP3550621B2 (ja) | Simox法によるsoi基板の製造方法 | |

| JP2003347560A (ja) | 双方向性ツェナーダイオードの製造方法 | |

| JP4483775B2 (ja) | 半導体装置の製造方法 | |

| JP5292984B2 (ja) | 半導体装置の製造方法 | |

| JP2016100566A (ja) | Soiウエハの製造方法及びsoiウエハ | |

| WO2022054429A1 (ja) | Soiウェーハの製造方法及びsoiウェーハ | |

| JPS5895868A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110516 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130122 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130319 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130409 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130422 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5255942 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160426 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |