JP2009206268A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2009206268A JP2009206268A JP2008046370A JP2008046370A JP2009206268A JP 2009206268 A JP2009206268 A JP 2009206268A JP 2008046370 A JP2008046370 A JP 2008046370A JP 2008046370 A JP2008046370 A JP 2008046370A JP 2009206268 A JP2009206268 A JP 2009206268A

- Authority

- JP

- Japan

- Prior art keywords

- conductivity type

- region

- trench regions

- semiconductor device

- semiconductor substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 56

- 238000004519 manufacturing process Methods 0.000 title claims description 15

- 239000000758 substrate Substances 0.000 claims abstract description 33

- 238000009792 diffusion process Methods 0.000 claims description 11

- 239000011229 interlayer Substances 0.000 claims description 11

- 238000000151 deposition Methods 0.000 claims description 9

- 238000005530 etching Methods 0.000 claims description 7

- 239000002184 metal Substances 0.000 claims description 6

- 238000000034 method Methods 0.000 claims description 6

- 239000000969 carrier Substances 0.000 abstract description 2

- 230000015556 catabolic process Effects 0.000 description 7

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 235000004522 Pentaglottis sempervirens Nutrition 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 240000004050 Pentaglottis sempervirens Species 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41766—Source or drain electrodes for field effect devices with at least part of the source or drain electrode having contact below the semiconductor surface, e.g. the source or drain electrode formed at least partially in a groove or with inclusions of conductor inside the semiconductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41758—Source or drain electrodes for field effect devices for lateral devices with structured layout for source or drain region, i.e. the source or drain region having cellular, interdigitated or ring structure or being curved or angular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42356—Disposition, e.g. buried gate electrode

- H01L29/4236—Disposition, e.g. buried gate electrode within a trench, e.g. trench gate electrode, groove gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66613—Lateral single gate silicon transistors with a gate recessing step, e.g. using local oxidation

- H01L29/66621—Lateral single gate silicon transistors with a gate recessing step, e.g. using local oxidation using etching to form a recess at the gate location

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7816—Lateral DMOS transistors, i.e. LDMOS transistors

- H01L29/7825—Lateral DMOS transistors, i.e. LDMOS transistors with trench gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

- H01L29/0852—Source or drain regions of field-effect devices of field-effect transistors with insulated gate of DMOS transistors

- H01L29/0873—Drain regions

- H01L29/0882—Disposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7827—Vertical transistors

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

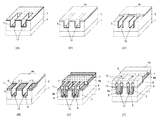

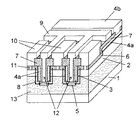

【解決手段】 半導体基板1に設けられた第1導電型ウェル領域2に、トレンチ領域12を複数本設けられており、ソース電極10は、前記トレンチ領域12の間の基板表面に設けられた第2導電型ソース領域6とオーミック接合されている。また、第2導電型ソース領域6と隣接して第1導電型高濃度領域11が設けられており、第2導電型ソース領域6と共にソース電極10にバッティングコンタクトされ、基板電位が固定されるようになっている。第2導電型ドレイン領域5はトレンチ領域12の底部に設けられており、トレンチ領域12の内部に埋め込まれたドレイン電極9によって基板表面に取り出されている。ゲート電極4a、4b及びドレイン電極9に任意の電圧を印加することにより、第2導電型ソース領域6から第2導電型ドレイン領域5にキャリアが矢印8の方向流れ、半導体装置がオン状態となる。

【選択図】 図1

Description

(2)(1)に記載の半導体装置において、前記半導体基板と前記第1導電型ウェル領域の間に第2導電型ドレイン領域を囲むように第2導電型低濃度拡散領域が形成された半導体装置とした。

(3)半導体基板に第1導電型ウェル領域形成する工程と、前記第1導電型ウェル領域より浅く複数本のトレンチ領域を形成する工程と、ゲート酸化膜を堆積させる工程と、ゲート電極膜を堆積させる工程と、前記複数本のトレンチ領域の底部上に堆積した前記ゲート酸化膜および前記ゲート電極膜及び前記複数本のトレンチ領域間の前記半導体基板表面上に堆積した前記ゲート酸化膜および前記ゲート電極膜の一部を異方性エッチングにより除去する工程と、層間絶縁膜を堆積させる工程と、前記ゲート電極膜上に堆積した前記層間絶縁膜の一部及び前記複数本のトレンチ領域の底部上に堆積した前記層間絶縁膜一部及び前記複数本のトレンチ領域間の前記半導体基板表面上に堆積した前記層間絶縁膜一部をエッチングにより除去する工程と、金属膜を堆積させる工程と、前記金属膜の一部をエッチングする工程を有する半導体装置の製造方法とした。

(4)(3)に記載の半導体装置の製造方法において、第2導電型低濃度拡散領域を形成する工程を有する半導体装置の製造方法とした。

(5)(3)に記載の半導体装置の製造方法において、エピタキシャル成長工程を有する半導体装置の製造方法とした。

図1に、本発明の実施形態の半導体装置構成を示す。(a)は上面図、(b)は(a)の点線部で切断した場合の鳥瞰図である。

(変形例)

本変形例では、ドレイン領域に電界緩和領域を設けることにより半導体装置の耐圧を向上させる。

2 第1導電型ウェル領域

3 ゲート絶縁膜

4 ゲート電極

5 第2導電型ドレイン領域

6 第2導電型ソース領域

7 層間絶縁膜

8 キャリア経路

9 ドレイン電極

10 ソース電極

11 第1導電型高濃度領域

12 トレンチ領域

13 第2導電型低濃度拡散領域

Claims (5)

- 半導体基板の表面から定められた深さまで設けられた第1導電型ウェル領域と、

前記第1導電型ウェル領域の深さより浅く形成された複数本のトレンチ領域と、

前記トレンチ領域の側面にゲート絶縁膜を介し接触して配置されたゲート電極と、

前記複数本のトレンチ領域の各底部に設けられた第2導電型ドレイン領域と、

前記複数本のトレンチ領域を挟む前記半導体基板表面に前記ゲート絶縁膜に沿って設けられた第2導電型ソース領域と、

前記複数本のトレンチ領域を挟む前記半導体基板表面に前記ソース領域に接して設けられた第1導電型高濃度領域と、

を有する半導体装置。 - 前記半導体基板と前記第1導電型ウェル領域の間に第2導電型ドレイン領域を囲むように第2導電型低濃度拡散領域が形成された請求項1に記載の半導体装置。

- 半導体基板に第1導電型ウェル領域を形成する工程と、

前記第1導電型ウェル領域より浅く複数本のトレンチ領域を形成する工程と、

ゲート絶縁膜を堆積させる工程と、

ゲート電極膜を堆積させる工程と、

前記複数本のトレンチ領域の底部上に堆積した前記ゲート酸化膜および前記ゲート電極膜及び前記複数本のトレンチ領域間の前記半導体基板表面上に堆積した前記ゲート絶縁膜および前記ゲート電極膜の一部を異方性エッチングにより除去する工程と、

層間絶縁膜を堆積させる工程と、

前記ゲート電極膜上に堆積した前記層間絶縁膜の一部及び前記複数本のトレンチ領域の底部上に堆積した前記層間絶縁膜一部及び前記複数本のトレンチ領域間の前記半導体基板表面上に堆積した前記層間絶縁膜一部をエッチングにより除去する工程と、

金属膜を堆積させる工程と、

前記金属膜の一部をエッチングする工程と、

を有する半導体装置の製造方法。 - 前記第1導電型ウェル領域を形成する工程の前に第2導電型低濃度拡散領域をトランジスタが形成される領域全面に形成する工程をさらに有する請求項3に記載の半導体装置の製造方法。

- 前記第2導電型低濃度拡散領域をトランジスタが形成される領域全面に形成する工程はエピタキシャル成長を含む工程である請求項4に記載の半導体装置の製造方法。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008046370A JP2009206268A (ja) | 2008-02-27 | 2008-02-27 | 半導体装置及びその製造方法 |

| TW098105809A TWI462291B (zh) | 2008-02-27 | 2009-02-24 | 半導體裝置及其製造方法 |

| US12/392,491 US7859049B2 (en) | 2008-02-27 | 2009-02-25 | Semiconductor device |

| KR1020090016201A KR20090092718A (ko) | 2008-02-27 | 2009-02-26 | 반도체 장치 및 그 제조 방법 |

| EP09153700A EP2096677A3 (en) | 2008-02-27 | 2009-02-26 | Semiconductor device and method of manufacturing the same |

| CN2009101184317A CN101552292B (zh) | 2008-02-27 | 2009-02-27 | 半导体器件及其制造方法 |

| US12/949,434 US8193060B2 (en) | 2008-02-27 | 2010-11-18 | Method of manufacturing a semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008046370A JP2009206268A (ja) | 2008-02-27 | 2008-02-27 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009206268A true JP2009206268A (ja) | 2009-09-10 |

| JP2009206268A5 JP2009206268A5 (ja) | 2011-02-03 |

Family

ID=40600263

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008046370A Withdrawn JP2009206268A (ja) | 2008-02-27 | 2008-02-27 | 半導体装置及びその製造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US7859049B2 (ja) |

| EP (1) | EP2096677A3 (ja) |

| JP (1) | JP2009206268A (ja) |

| KR (1) | KR20090092718A (ja) |

| CN (1) | CN101552292B (ja) |

| TW (1) | TWI462291B (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100861213B1 (ko) * | 2007-04-17 | 2008-09-30 | 동부일렉트로닉스 주식회사 | 반도체 소자 및 그 제조방법 |

| US9224860B2 (en) | 2010-12-10 | 2015-12-29 | Mitsubishi Electric Corporation | Trench-gate type semiconductor device and manufacturing method therefor |

| US8679919B2 (en) | 2011-12-15 | 2014-03-25 | Semiconductor Components Industries, Llc | Electronic device comprising a conductive structure and an insulating layer within a trench and a process of forming the same |

| US8647970B2 (en) * | 2011-12-15 | 2014-02-11 | Semiconductor Components Industries, Llc | Electronic device comprising conductive structures and an insulating layer between the conductive structures and within a trench |

| US8878287B1 (en) * | 2012-04-12 | 2014-11-04 | Micrel, Inc. | Split slot FET with embedded drain |

| US10326013B2 (en) * | 2016-11-23 | 2019-06-18 | Microchip Technology Incorporated | Method of forming a field-effect transistor (FET) or other semiconductor device with front-side source and drain contacts |

| US20180145171A1 (en) * | 2016-11-23 | 2018-05-24 | Microchip Technology Incorporated | Field Effect Transistor (FET) or Other Semiconductor Device with Front-Side Source and Drain Contacts |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08181313A (ja) * | 1994-10-25 | 1996-07-12 | Fuji Electric Co Ltd | 横型トレンチmisfetおよびその製造方法 |

| JP2002141505A (ja) * | 2000-10-31 | 2002-05-17 | Shindengen Electric Mfg Co Ltd | 電界効果トランジスタ |

| JP2003249650A (ja) * | 2001-12-18 | 2003-09-05 | Fuji Electric Co Ltd | 半導体装置および半導体装置の製造方法 |

| JP2004193535A (ja) * | 2002-01-16 | 2004-07-08 | Fuji Electric Device Technology Co Ltd | 半導体装置およびその製造方法 |

| JP2005322874A (ja) * | 2004-04-06 | 2005-11-17 | Fuji Electric Holdings Co Ltd | 半導体装置およびその製造方法 |

| JP2006108514A (ja) * | 2004-10-07 | 2006-04-20 | Fuji Electric Holdings Co Ltd | 半導体装置およびその製造方法 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0783118B2 (ja) | 1988-06-08 | 1995-09-06 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

| KR0165398B1 (ko) * | 1995-05-26 | 1998-12-15 | 윤종용 | 버티칼 트랜지스터의 제조방법 |

| JP3252804B2 (ja) * | 1998-07-31 | 2002-02-04 | 日本電気株式会社 | 固体撮像素子の駆動方法 |

| WO2000044041A1 (en) * | 1999-01-22 | 2000-07-27 | Hitachi, Ltd. | Semiconductor integrated circuit and manufacture thereof |

| EP1858085A3 (en) * | 1999-10-27 | 2008-01-23 | The Kansai Electric Power Co., Inc. | Semiconductor device |

| US6624470B2 (en) * | 2001-05-30 | 2003-09-23 | Fuji Electric Co., Ltd. | Semiconductor device and a method for manufacturing same |

| US7372088B2 (en) * | 2004-01-27 | 2008-05-13 | Matsushita Electric Industrial Co., Ltd. | Vertical gate semiconductor device and method for fabricating the same |

| CN100539184C (zh) * | 2004-02-16 | 2009-09-09 | 富士电机电子技术株式会社 | 双方向元件及其制造方法、半导体装置 |

| US20070032029A1 (en) * | 2005-04-19 | 2007-02-08 | Rensselaer Polytechnic Institute | Lateral trench power MOSFET with reduced gate-to-drain capacitance |

| JP2008177335A (ja) * | 2007-01-18 | 2008-07-31 | Fuji Electric Device Technology Co Ltd | 炭化珪素絶縁ゲート型半導体装置。 |

-

2008

- 2008-02-27 JP JP2008046370A patent/JP2009206268A/ja not_active Withdrawn

-

2009

- 2009-02-24 TW TW098105809A patent/TWI462291B/zh not_active IP Right Cessation

- 2009-02-25 US US12/392,491 patent/US7859049B2/en not_active Expired - Fee Related

- 2009-02-26 EP EP09153700A patent/EP2096677A3/en not_active Withdrawn

- 2009-02-26 KR KR1020090016201A patent/KR20090092718A/ko not_active Application Discontinuation

- 2009-02-27 CN CN2009101184317A patent/CN101552292B/zh not_active Expired - Fee Related

-

2010

- 2010-11-18 US US12/949,434 patent/US8193060B2/en not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08181313A (ja) * | 1994-10-25 | 1996-07-12 | Fuji Electric Co Ltd | 横型トレンチmisfetおよびその製造方法 |

| JP2002141505A (ja) * | 2000-10-31 | 2002-05-17 | Shindengen Electric Mfg Co Ltd | 電界効果トランジスタ |

| JP2003249650A (ja) * | 2001-12-18 | 2003-09-05 | Fuji Electric Co Ltd | 半導体装置および半導体装置の製造方法 |

| JP2004193535A (ja) * | 2002-01-16 | 2004-07-08 | Fuji Electric Device Technology Co Ltd | 半導体装置およびその製造方法 |

| JP2005322874A (ja) * | 2004-04-06 | 2005-11-17 | Fuji Electric Holdings Co Ltd | 半導体装置およびその製造方法 |

| JP2006108514A (ja) * | 2004-10-07 | 2006-04-20 | Fuji Electric Holdings Co Ltd | 半導体装置およびその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8193060B2 (en) | 2012-06-05 |

| CN101552292B (zh) | 2013-03-27 |

| EP2096677A2 (en) | 2009-09-02 |

| KR20090092718A (ko) | 2009-09-01 |

| CN101552292A (zh) | 2009-10-07 |

| US7859049B2 (en) | 2010-12-28 |

| EP2096677A3 (en) | 2009-10-14 |

| TW200945587A (en) | 2009-11-01 |

| TWI462291B (zh) | 2014-11-21 |

| US20090212357A1 (en) | 2009-08-27 |

| US20110065247A1 (en) | 2011-03-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI438898B (zh) | 自我對準之互補雙擴散金氧半導體 | |

| JP4976658B2 (ja) | 半導体装置の製造方法 | |

| EP2755237A2 (en) | Trench MOS gate semiconductor device and method of fabricating the same | |

| JP5110776B2 (ja) | 半導体装置の製造方法 | |

| JP2009206268A (ja) | 半導体装置及びその製造方法 | |

| JP2008192985A (ja) | 半導体装置、及び半導体装置の製造方法 | |

| JP2019519938A (ja) | 短チャネルトレンチ型パワーmosfet | |

| JP2009021456A (ja) | フィン型トランジスタおよびその形成方法 | |

| JP5420225B2 (ja) | 半導体装置およびその製造方法 | |

| JP2009081397A (ja) | 半導体装置および半導体装置の製造方法 | |

| KR101371495B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| JP4997694B2 (ja) | 半導体装置およびその製造方法 | |

| JP5486654B2 (ja) | 半導体装置 | |

| JP2015146390A (ja) | 半導体メモリ装置およびその製造方法 | |

| JP2009016480A (ja) | 半導体装置、及び半導体装置の製造方法 | |

| US20120126312A1 (en) | Vertical dmos-field effect transistor | |

| KR101747615B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| JP2008103378A (ja) | 半導体装置とその製造方法 | |

| KR101682420B1 (ko) | 선택적 게르마늄 응축과 측벽공정을 이용한 자기정렬된 이종접합 터널링 전계효과 트랜지스터의 제조방법 | |

| JP4191025B2 (ja) | 縦型misfet | |

| JP2005322723A (ja) | 半導体装置およびその製造方法 | |

| JP2009259968A (ja) | 半導体装置及びその製造方法 | |

| JP5486673B2 (ja) | 半導体装置 | |

| JP2007115734A (ja) | 半導体装置の製造方法 | |

| JP2005093874A (ja) | 半導体装置および半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091108 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091113 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101208 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101208 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121220 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121225 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20130221 |