JP2008122635A - 表示方法及びこの方法を用いた表示装置 - Google Patents

表示方法及びこの方法を用いた表示装置 Download PDFInfo

- Publication number

- JP2008122635A JP2008122635A JP2006306164A JP2006306164A JP2008122635A JP 2008122635 A JP2008122635 A JP 2008122635A JP 2006306164 A JP2006306164 A JP 2006306164A JP 2006306164 A JP2006306164 A JP 2006306164A JP 2008122635 A JP2008122635 A JP 2008122635A

- Authority

- JP

- Japan

- Prior art keywords

- gradation

- pseudo

- gradations

- display

- frames

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2018—Display of intermediate tones by time modulation using two or more time intervals

- G09G3/2022—Display of intermediate tones by time modulation using two or more time intervals using sub-frames

- G09G3/2025—Display of intermediate tones by time modulation using two or more time intervals using sub-frames the sub-frames having all the same time duration

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/02—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators characterised by the way in which colour is displayed

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0247—Flicker reduction other than flicker reduction circuits used for single beam cathode-ray tubes

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

- Transforming Electric Information Into Light Information (AREA)

Abstract

【解決手段】本発明は、表示装置を駆動するドライバ回路2に入力される画像信号の第1ビット数が、出力される階調データの第2ビット数のより多い場合に、表示装置に第1ビット数の階調を表示させる表示方法である。そして、本発明に係る表示方法は、各階調間に、第1フレーム数を1組としてフレームレートコントロールを行い擬似階調を追加する第1擬似階調表示ステップと、第1フレーム数と異なる第2フレーム数を1組としてフレームレートコントロールを行い、第1擬似階調表示ステップを行った階調間の少なくとも1つに擬似階調を追加する第2擬似階調表示ステップとを備える。

【選択図】図3

Description

本実施の形態に係るマトリクス型の画像表示装置(以下、単に表示装置ともいう)の回路構成を示すブロック図を図1に示す。図1に示す表示装置では、jビットの入力画像信号(以下、単に画像信号ともいう)が入力される信号処理回路1では、画像信号をレベルに対応したデジタル信号に変換する。さらに、信号処理回路1では、当該デジタル信号に対し、タイミング調整やレベル調整などを行い、表示データとしてデータドライバIC2に出力する。

図4に、本実施の形態に係る表示方法のフローチャートを示す。図4に示すフローチャートでは、iビットの階調データを出力可能なデータドライバIC2を用いて、jビット(i<j)の画像信号の階調を表示させる。まず、図4に示すフローチャートでは、2フレーム及び3フレームを1組としてFRCを行い作成した擬似階調を、iビットの各階調間に追加する(ステップS1)。例えば、階調Gkと階調Gk+1との間には、2フレームを1組としてFRCを行い作成した擬似階調{Gk×1/2+(Gk+1)×1/2}及び、3フレームを1組としてFRCを行い作成した擬似階調{Gk×2/3+(Gk+1)×1/3},{Gk×1/3+(Gk+1)×2/3}が追加される。

図5に、本実施の形態に係る表示方法のフローチャートを示す。図5に示すフローチャートでは、iビットの階調データを出力可能なデータドライバIC2を用いて、jビット(i<j)の画像信号の階調を表示させる場合に、まず、2^(j−i)フレームを1組としてFRCを行い作成された擬似階調を、iビットの各階調間に作成する(ステップS7)。なお、ステップS7により、FRCによらない階調数2^i個に、FRCによる階調数{2^j−2^i−2^(j−i)+1}個を追加した階調数を表示することができるようになる。

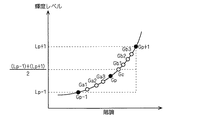

図7に、本実施の形態に係る表示方法のフローチャートを示す。図7に示すフローチャートでは、iビットの階調データを出力可能なデータドライバIC2を用いて、jビット(i<j)の画像信号の階調を表示させる場合の表示方法である。まず、2フレームを1組としてFRCを行い作成した擬似階調を、iビットの各階調間に作成する(ステップS10)。例えば、階調Gpと階調Gp+1との間には、2フレームを1組としてFRCを行い作成した擬似階調{Gp×1/2+(Gp+1)×1/2}を追加する。なお、ステップS10により追加される階調数は[2^i−1]個となる。

Claims (11)

- 表示装置を駆動するドライバ回路に入力される画像信号の第1ビット数が、出力される階調データの第2ビット数のより多い場合に、前記表示装置に前記第1ビット数の階調を表示させる表示方法であって、

各階調間に、第1フレーム数を1組としてフレームレートコントロールを行い擬似階調を追加する第1擬似階調表示ステップと、

前記第1フレーム数と異なる第2フレーム数を1組としてフレームレートコントロールを行い、前記第1擬似階調表示ステップを行った階調間の少なくとも1つに擬似階調を追加する第2擬似階調表示ステップとを備える表示方法。 - 請求項1に記載の表示方法であって、

前記第1擬似階調表示ステップ及び前記第2擬似階調表示ステップで追加する擬似階調数では、前記第1ビット数の階調を表示できない場合に、前記第1フレーム数及び前記第2フレーム数と異なる第3フレーム数を1組としてフレームレートコントロールを行う擬似階調を、前記第1ビット数の階調に至るまで順次追加する擬似階調追加ステップをさらに備える表示方法。 - 請求項1又は請求項2に記載の表示方法であって、

前記第1フレーム数は、前記第1ビット数と前記第2ビット数との差で2をべき乗した値であることを特徴とする表示方法。 - 請求項1乃至請求項3のいずれか1つに記載の表示方法であって、

前記第2フレーム数は、前記第1ビット数と前記第2ビット数との差で2をべき乗した値より小さい自然数であることを特徴とする表示方法。 - 請求項1又は請求項2に記載の表示方法であって、

前記第1フレーム数を2とし、前記第2フレーム数を3とすることを特徴とする表示方法。 - 請求項2に記載の表示方法であって、

前記第1フレーム数を2とし、前記第2フレーム数を3とし、前記第3フレーム数を4以上の自然数として前記第1ビット数の階調に至るまで当該前記第3フレーム数を順次繰り上げることを特徴とする表示方法。 - 表示装置を駆動するドライバ回路に入力される画像信号の第1ビット数が、出力される階調データの第2ビット数のより多い場合に、前記表示装置に前記第1ビット数の階調を表示させる表示方法であって、

隣接する階調間において、所定のフレーム数を1組としてフレームレートコントロールを行い擬似階調を追加する第1擬似階調表示ステップと、

連続する2階調間において、所定のフレーム数を1組としてフレームレートコントロールを行い擬似階調を追加する第2擬似階調表示ステップとを備える表示方法。 - 請求項7に記載の表示方法であって、

前記第1擬似階調表示ステップの所定のフレーム数と、前記第2擬似階調表示ステップの所定のフレーム数とが異なることを特徴とする表示方法。 - 請求項7に記載の表示方法であって、

前記第1擬似階調表示ステップ及び前記第2擬似階調表示ステップで追加する擬似階調数では、前記第1ビット数の階調を表示できない場合に、前記所定のフレーム数を順次繰り上げて前記第1擬似階調表示ステップ及び前記第2擬似階調表示ステップを繰り返し実行し、前記第1ビット数の階調に至るまで擬似階調を順次追加する擬似階調追加ステップをさらに備える表示方法。 - 請求項7乃至請求項9のいずれか1つに記載の表示方法であって、

前記第2擬似階調表示ステップは、階調−輝度特性曲線が非線形となる階調領域に適用することを特徴とする表示方法。 - 請求項1乃至請求項10のいずれか1つに記載の表示方法を用いて、第1ビット数の階調データを表示することを特徴とする表示装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006306164A JP2008122635A (ja) | 2006-11-13 | 2006-11-13 | 表示方法及びこの方法を用いた表示装置 |

| TW096127729A TW200823859A (en) | 2006-11-13 | 2007-07-30 | Display method and display apparatus using this method |

| US11/831,155 US8009181B2 (en) | 2006-11-13 | 2007-07-31 | Display method and display apparatus using this method |

| KR1020070111314A KR20080043225A (ko) | 2006-11-13 | 2007-11-02 | 표시 방법 및 이 방법을 사용한 표시 장치 |

| CN2007101869226A CN101183520B (zh) | 2006-11-13 | 2007-11-13 | 显示方法和使用了该方法的显示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006306164A JP2008122635A (ja) | 2006-11-13 | 2006-11-13 | 表示方法及びこの方法を用いた表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014030400A Division JP5778809B2 (ja) | 2014-02-20 | 2014-02-20 | 擬似階調の設定方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008122635A true JP2008122635A (ja) | 2008-05-29 |

| JP2008122635A5 JP2008122635A5 (ja) | 2010-05-13 |

Family

ID=39368786

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006306164A Pending JP2008122635A (ja) | 2006-11-13 | 2006-11-13 | 表示方法及びこの方法を用いた表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8009181B2 (ja) |

| JP (1) | JP2008122635A (ja) |

| KR (1) | KR20080043225A (ja) |

| CN (1) | CN101183520B (ja) |

| TW (1) | TW200823859A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012118105A (ja) * | 2010-11-29 | 2012-06-21 | Lapis Semiconductor Co Ltd | 表示装置、中間階調処理回路及び中間階調処理方法 |

| JP2014130370A (ja) * | 2014-02-20 | 2014-07-10 | Mitsubishi Electric Corp | 表示方法及びこの方法を用いた表示装置 |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101393726B (zh) * | 2007-09-21 | 2011-02-02 | 北京京东方光电科技有限公司 | 像素灰度扩展方法、像素电容充电时间驱动方法及装置 |

| CN102473387B (zh) * | 2009-08-28 | 2014-07-09 | 夏普株式会社 | 液晶显示装置及其电位设定方法 |

| JP5963942B2 (ja) * | 2013-03-05 | 2016-08-03 | 三菱電機株式会社 | 表示装置の映像信号制御方法および映像信号制御装置 |

| KR102345091B1 (ko) * | 2014-12-26 | 2021-12-31 | 엘지디스플레이 주식회사 | 표시장치와 이의 구동방법 |

| CN107564485A (zh) * | 2017-09-19 | 2018-01-09 | 惠科股份有限公司 | 显示器的驱动系统及驱动方法 |

| CN111312159A (zh) * | 2020-03-11 | 2020-06-19 | 深圳市德普微电子有限公司 | 一种灰度显示驱动方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02993A (ja) * | 1988-06-06 | 1990-01-05 | Ascii Corp | Lcd階調表示制御装置 |

| JPH03125188A (ja) * | 1989-10-09 | 1991-05-28 | Hitachi Ltd | 液晶表示装置 |

| JPH1049108A (ja) * | 1996-07-30 | 1998-02-20 | Nec Corp | 液晶表示装置の階調表示方法 |

| JP2002328665A (ja) * | 2001-02-07 | 2002-11-15 | Seiko Epson Corp | 表示駆動回路、半導体集積回路、表示パネル及び表示駆動方法 |

| JP2003162267A (ja) * | 2001-11-29 | 2003-06-06 | Seiko Epson Corp | 表示駆動回路、電気光学装置、電子機器及び表示駆動方法 |

| JP2004126626A (ja) * | 1993-10-08 | 2004-04-22 | Toshiba Corp | 多階調表示装置 |

| JP2004333911A (ja) * | 2003-05-08 | 2004-11-25 | Seiko Epson Corp | 電気光学装置の駆動方法、電気光学装置および電子機器 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0572991A (ja) | 1991-09-12 | 1993-03-26 | Hitachi Ltd | 表示パネルの駆動方式 |

| JPH06161391A (ja) | 1992-11-18 | 1994-06-07 | Hitachi Ltd | 液晶駆動回路 |

| TW544650B (en) * | 2000-12-27 | 2003-08-01 | Matsushita Electric Ind Co Ltd | Matrix-type display device and driving method thereof |

| JP2002196728A (ja) * | 2000-12-27 | 2002-07-12 | Matsushita Electric Ind Co Ltd | 単純マトリクス型液晶表示パネルの駆動方法及び液晶表示装置 |

| JP3631727B2 (ja) | 2002-03-28 | 2005-03-23 | Nec液晶テクノロジー株式会社 | 画像表示方法および画像表示装置 |

| EP1365384A1 (en) * | 2002-05-23 | 2003-11-26 | STMicroelectronics S.r.l. | Driving method for flat panel display devices |

| JP4390483B2 (ja) * | 2003-06-19 | 2009-12-24 | シャープ株式会社 | 液晶中間調表示方法及びその方法を用いた液晶表示装置 |

| KR20050061799A (ko) * | 2003-12-18 | 2005-06-23 | 삼성전자주식회사 | 액정 표시 장치 및 그 구동 방법 |

| KR101182307B1 (ko) * | 2005-12-07 | 2012-09-20 | 엘지디스플레이 주식회사 | 평판표시장치와 그 화질 제어장치 및 화질 제어방법 |

-

2006

- 2006-11-13 JP JP2006306164A patent/JP2008122635A/ja active Pending

-

2007

- 2007-07-30 TW TW096127729A patent/TW200823859A/zh unknown

- 2007-07-31 US US11/831,155 patent/US8009181B2/en active Active

- 2007-11-02 KR KR1020070111314A patent/KR20080043225A/ko not_active Application Discontinuation

- 2007-11-13 CN CN2007101869226A patent/CN101183520B/zh not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02993A (ja) * | 1988-06-06 | 1990-01-05 | Ascii Corp | Lcd階調表示制御装置 |

| JPH03125188A (ja) * | 1989-10-09 | 1991-05-28 | Hitachi Ltd | 液晶表示装置 |

| JP2004126626A (ja) * | 1993-10-08 | 2004-04-22 | Toshiba Corp | 多階調表示装置 |

| JPH1049108A (ja) * | 1996-07-30 | 1998-02-20 | Nec Corp | 液晶表示装置の階調表示方法 |

| JP2002328665A (ja) * | 2001-02-07 | 2002-11-15 | Seiko Epson Corp | 表示駆動回路、半導体集積回路、表示パネル及び表示駆動方法 |

| JP2003162267A (ja) * | 2001-11-29 | 2003-06-06 | Seiko Epson Corp | 表示駆動回路、電気光学装置、電子機器及び表示駆動方法 |

| JP2004333911A (ja) * | 2003-05-08 | 2004-11-25 | Seiko Epson Corp | 電気光学装置の駆動方法、電気光学装置および電子機器 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012118105A (ja) * | 2010-11-29 | 2012-06-21 | Lapis Semiconductor Co Ltd | 表示装置、中間階調処理回路及び中間階調処理方法 |

| JP2014130370A (ja) * | 2014-02-20 | 2014-07-10 | Mitsubishi Electric Corp | 表示方法及びこの方法を用いた表示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101183520B (zh) | 2010-06-23 |

| US20080111838A1 (en) | 2008-05-15 |

| TW200823859A (en) | 2008-06-01 |

| CN101183520A (zh) | 2008-05-21 |

| KR20080043225A (ko) | 2008-05-16 |

| US8009181B2 (en) | 2011-08-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5373372B2 (ja) | 液晶表示装置の駆動装置及びその駆動方法 | |

| EP1137266B1 (en) | Image processing apparatus with ROM storing a noise signal and image display apparatus using same | |

| JP2008122635A (ja) | 表示方法及びこの方法を用いた表示装置 | |

| JP2007033864A (ja) | 画像処理回路及び画像処理方法 | |

| JP2003302955A (ja) | フレームレート制御方法及びそのための液晶表示装置 | |

| JPH08286634A (ja) | 中間調表示方法 | |

| WO2006009106A1 (ja) | 画像表示装置および画像表示方法 | |

| WO2009081602A1 (ja) | 表示装置 | |

| JP2011028278A (ja) | 画像表示装置、画像表示モニター、およびテレビジョン受像機 | |

| US20080117198A1 (en) | Display device and controller driver for improved FRC technique | |

| JP2007140217A (ja) | 表示装置 | |

| JP2001154631A (ja) | Pdpにおける階調制御方法及び装置 | |

| JP2008145493A (ja) | 画像表示方法、およびこの方法を用いた画像表示装置 | |

| JP2003050566A (ja) | 液晶表示装置 | |

| JP2004133400A (ja) | 要求されるよりも少ない映像レベルを表示してディザリングノイズを改善させるプラズマディスプレイパネル(pdp) | |

| JP4874931B2 (ja) | 表示装置 | |

| KR20020014766A (ko) | 플라즈마 디스플레이 패널의 표시계조 처리방법 | |

| JP5685065B2 (ja) | 表示装置、中間階調処理回路及び中間階調処理方法 | |

| JP2013088745A (ja) | 液晶表示装置 | |

| JP5778809B2 (ja) | 擬似階調の設定方法 | |

| KR100692094B1 (ko) | 디스플레이 장치 및 디스플레이 방법 | |

| JP2011227374A (ja) | 表示装置 | |

| JP2004088405A (ja) | 画像処理装置 | |

| JP2005043725A (ja) | 表示装置及び中間階調表示方法 | |

| KR100363169B1 (ko) | 영상 처리 시스템에 있어서 의사윤곽 보상장치 및 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091014 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20091014 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100317 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120119 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120131 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120323 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120501 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120627 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120724 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121010 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20121017 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20121228 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140220 |