JP2007096036A - 昇圧回路 - Google Patents

昇圧回路 Download PDFInfo

- Publication number

- JP2007096036A JP2007096036A JP2005284153A JP2005284153A JP2007096036A JP 2007096036 A JP2007096036 A JP 2007096036A JP 2005284153 A JP2005284153 A JP 2005284153A JP 2005284153 A JP2005284153 A JP 2005284153A JP 2007096036 A JP2007096036 A JP 2007096036A

- Authority

- JP

- Japan

- Prior art keywords

- booster circuit

- capacitor

- stage

- mos transistor

- drain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000003990 capacitor Substances 0.000 claims abstract description 97

- 239000000758 substrate Substances 0.000 claims abstract description 24

- 238000000034 method Methods 0.000 claims abstract description 15

- 230000000694 effects Effects 0.000 abstract description 12

- 230000006866 deterioration Effects 0.000 abstract description 7

- 238000010586 diagram Methods 0.000 description 15

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 230000015556 catabolic process Effects 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 238000002955 isolation Methods 0.000 description 6

- 101000805729 Homo sapiens V-type proton ATPase 116 kDa subunit a 1 Proteins 0.000 description 4

- 102100037979 V-type proton ATPase 116 kDa subunit a 1 Human genes 0.000 description 4

- 238000009792 diffusion process Methods 0.000 description 4

- 238000007796 conventional method Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 230000036962 time dependent Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/06—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider

- H02M3/07—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider using capacitors charged and discharged alternately by semiconductor devices with control electrode, e.g. charge pumps

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Semiconductor Integrated Circuits (AREA)

- Dc-Dc Converters (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Manipulation Of Pulses (AREA)

Abstract

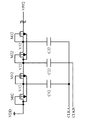

【解決手段】各段がMOSトランジスタ(M04、M14、M24、M34)と、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタ(C14、C24a、C24b、C34a、C34b、C34c)とからなり、前記MOSトランジスタが縦列接続されることによって各段が接続され、各段における前記MOSトランジスタのゲートとドレイン又はソースの一方とが互いに電気的に接続されるとともに、少なくとも1組の隣接するMOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続される。バックバイアス効果が抑制され、かつレイアウト面積を縮小することができる。また、後段の昇圧キャパシタを複数の直列キャパシタで構成することにより、各キャパシタの耐圧劣化を抑制することができる。

【選択図】図8

Description

J. F. Dickson, "On-Chip High-Voltage Generation in MNOS Integrated Circuits Using an Improved Voltage Multiplier Technique," IEEE J. Solid-State Circuits, Vol. SC-11, No. 3, pp. 374-378, June 1976.

VPP1=(VDD−Vt0)+VDD×3−(Vt1+Vt2+Vt3)

の電位まで昇圧される。

VPP1=(VDD−Vt0)+VDD×n

−(Vt1+Vt2+Vt3+・・・+Vtn)

の電位まで昇圧される。

5、6、19、21、25 N型ウェル領域

7、22、26 P型シリコン基板

11、30 ウェルコンタクト領域

12、31 キャパシタ領域

13、32 MOSトランジスタ

18、20 P型ウェル領域

23 N型DMOSキャパシタのゲート端子

24 N型DMOSキャパシタのN型ウェル(拡散層)端子

C11、C21、C31 キャパシタ

C12、C22、C32 キャパシタ

C13、C23a、C23b、C33a、C33b、C33c キャパシタ

C14、C24a、C24b、C34a、C34b、C34c キャパシタ

C15、C25a、C25b、C35a、C35b、C35c キャパシタ

CLKA、CLKB クロック信号

M01、M11、M21、M31 駆動PMOSトランジスタ

M02、M12、M22、M32 駆動NMOSトランジスタ

M03、M13、M23、M33 駆動PMOSトランジスタ

M04、M14、M24、M34 駆動PMOSトランジスタ

M05、M15、M25、M35 駆動PMOSトランジスタ

V11、V21、V31 ノード

V12、V22、V32 ノード

V13、V23、V33 ノード

V14、V24、V34 ノード

V15、V25、V35 ノード

VDD 電源電圧

VPP1〜VPP5 昇圧回路の出力電圧

Claims (9)

- 各段がMOSトランジスタと、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタとからなり、前記MOSトランジスタが縦列接続されることによって各段が接続されており、

各段における前記MOSトランジスタのゲートとドレイン又はソースの一方とが互いに電気的に接続されるとともに、少なくとも1組の隣接するMOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続されていることを特徴とする昇圧回路。 - 請求項1記載の昇圧回路において、

連続する2段の前記キャパシタの他端に逆位相の1対のクロック信号が入力されることを特徴とする昇圧回路。 - 請求項1記載の昇圧回路において、

前記MOSトランジスタがN型ウェル領域に形成されたPMOSトランジスタであることを特徴とする昇圧回路。 - 請求項1記載の昇圧回路において、

前記MOSトランジスタがP型ウェル領域に形成されたNMOSトランジスタであることを特徴とする昇圧回路。 - 請求項1記載の昇圧回路において、

少なくとも1つの段のキャパシタは複数の直列接続されたキャパシタからなることを特徴とする昇圧回路。 - 各段がMOSトランジスタと、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタとからなり、少なくとも1つの段のキャパシタは複数の直列接続されたキャパシタからなることを特徴とする昇圧回路。

- 請求項6記載の昇圧回路において、

前記キャパシタがN型のデプレッションMOSトランジスタで構成されたことを特徴とする昇圧回路。 - 請求項6記載の昇圧回路において、

前記キャパシタがPMOSトランジスタで構成されたことを特徴とする昇圧回路。 - 請求項1又は6に記載の昇圧回路において、

各段がLSIの入出力回路を形成するMOSトランジスタと同一のプロセスで製造するMOSトランジスタで構成されたことを特徴とする昇圧回路。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005284153A JP2007096036A (ja) | 2005-09-29 | 2005-09-29 | 昇圧回路 |

| CN200610154013XA CN1941579B (zh) | 2005-09-29 | 2006-09-19 | 升压电路 |

| US11/526,060 US7602231B2 (en) | 2005-09-29 | 2006-09-25 | Charge-pump circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005284153A JP2007096036A (ja) | 2005-09-29 | 2005-09-29 | 昇圧回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007096036A true JP2007096036A (ja) | 2007-04-12 |

| JP2007096036A5 JP2007096036A5 (ja) | 2008-10-09 |

Family

ID=37893106

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005284153A Pending JP2007096036A (ja) | 2005-09-29 | 2005-09-29 | 昇圧回路 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7602231B2 (ja) |

| JP (1) | JP2007096036A (ja) |

| CN (1) | CN1941579B (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017131069A (ja) * | 2016-01-21 | 2017-07-27 | 凸版印刷株式会社 | チャージポンプ |

| JP6962493B1 (ja) * | 2020-07-10 | 2021-11-05 | ソニーグループ株式会社 | 表示装置及び電子機器 |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4867657B2 (ja) * | 2006-12-28 | 2012-02-01 | ソニー株式会社 | 電圧供給回路、表示装置、および電子機器、並びに電圧供給方法 |

| WO2011108367A1 (en) * | 2010-03-02 | 2011-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Boosting circuit and rfid tag including boosting circuit |

| US8581658B2 (en) * | 2011-04-08 | 2013-11-12 | Taiwan Semiconductor Manufacturing Company, Ltd. | Charge pump |

| US8947158B2 (en) | 2012-09-03 | 2015-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

| TWI643435B (zh) | 2013-08-21 | 2018-12-01 | 日商半導體能源研究所股份有限公司 | 電荷泵電路以及具備電荷泵電路的半導體裝置 |

| KR102267237B1 (ko) | 2014-03-07 | 2021-06-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 전자 기기 |

| US9312280B2 (en) | 2014-07-25 | 2016-04-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9678523B2 (en) | 2015-10-15 | 2017-06-13 | Microsoft Technology Licensing, Llc | Self biasing driver circuit for voltage boosting |

| CN107453601B (zh) * | 2017-08-22 | 2023-09-19 | 合肥博雅半导体有限公司 | 电荷泵和存储器 |

| CN111371313B (zh) * | 2020-04-20 | 2021-03-26 | 上海传泰电子科技有限公司 | 一种高压电荷泵电路 |

| CN116137493A (zh) * | 2021-11-17 | 2023-05-19 | 科奇芯有限公司 | 电荷泵电路 |

| US11810626B2 (en) * | 2022-02-11 | 2023-11-07 | Sandisk Technologies Llc | Generating boosted voltages with a hybrid charge pump |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61119072A (ja) * | 1984-11-15 | 1986-06-06 | Toshiba Corp | 半導体容量装置 |

| JPH08306870A (ja) * | 1995-04-28 | 1996-11-22 | Fuji Xerox Co Ltd | 半導体集積昇圧回路装置 |

| JPH09331671A (ja) * | 1996-06-12 | 1997-12-22 | Oki Electric Ind Co Ltd | 昇圧回路 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4581546A (en) * | 1983-11-02 | 1986-04-08 | Inmos Corporation | CMOS substrate bias generator having only P channel transistors in the charge pump |

| US5237193A (en) * | 1988-06-24 | 1993-08-17 | Siliconix Incorporated | Lightly doped drain MOSFET with reduced on-resistance |

| US5059815A (en) * | 1990-04-05 | 1991-10-22 | Advanced Micro Devices, Inc. | High voltage charge pumps with series capacitors |

| TW271011B (ja) * | 1994-04-20 | 1996-02-21 | Nippon Steel Corp | |

| US6028473A (en) * | 1995-03-09 | 2000-02-22 | Macronix International Co., Ltd. | Series capacitor charge pump with dynamic biasing |

| US5962887A (en) * | 1996-06-18 | 1999-10-05 | Micron Technology, Inc. | Metal-oxide-semiconductor capacitor |

| EP0822601B1 (en) * | 1996-07-30 | 2006-05-24 | STMicroelectronics S.r.l. | MOS capacitor with wide voltage and frequency operating ranges |

| JP3323119B2 (ja) * | 1997-11-28 | 2002-09-09 | 株式会社東芝 | 半導体集積回路装置 |

| JP3223504B2 (ja) * | 1998-03-31 | 2001-10-29 | 日本電気株式会社 | 昇圧回路 |

| US5978283A (en) * | 1998-07-02 | 1999-11-02 | Aplus Flash Technology, Inc. | Charge pump circuits |

| JP3850580B2 (ja) * | 1999-03-30 | 2006-11-29 | 株式会社東芝 | 半導体装置 |

| US6320796B1 (en) * | 2000-11-10 | 2001-11-20 | Marvell International, Ltd. | Variable slope charge pump control |

-

2005

- 2005-09-29 JP JP2005284153A patent/JP2007096036A/ja active Pending

-

2006

- 2006-09-19 CN CN200610154013XA patent/CN1941579B/zh active Active

- 2006-09-25 US US11/526,060 patent/US7602231B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61119072A (ja) * | 1984-11-15 | 1986-06-06 | Toshiba Corp | 半導体容量装置 |

| JPH08306870A (ja) * | 1995-04-28 | 1996-11-22 | Fuji Xerox Co Ltd | 半導体集積昇圧回路装置 |

| JPH09331671A (ja) * | 1996-06-12 | 1997-12-22 | Oki Electric Ind Co Ltd | 昇圧回路 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017131069A (ja) * | 2016-01-21 | 2017-07-27 | 凸版印刷株式会社 | チャージポンプ |

| JP6962493B1 (ja) * | 2020-07-10 | 2021-11-05 | ソニーグループ株式会社 | 表示装置及び電子機器 |

| WO2022009731A1 (ja) * | 2020-07-10 | 2022-01-13 | ソニーグループ株式会社 | 駆動回路アレイ基板、表示装置および電子機器 |

| JP2022016421A (ja) * | 2020-07-10 | 2022-01-21 | ソニーグループ株式会社 | 表示装置及び電子機器 |

| JP7414183B1 (ja) | 2020-07-10 | 2024-01-16 | ソニーグループ株式会社 | 表示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7602231B2 (en) | 2009-10-13 |

| CN1941579B (zh) | 2012-05-09 |

| CN1941579A (zh) | 2007-04-04 |

| US20070069803A1 (en) | 2007-03-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2007096036A (ja) | 昇圧回路 | |

| EP0836268B1 (en) | Improved positive charge pump | |

| US5892267A (en) | Multi-stage voltage-boosting circuit with boosted back-gate bias | |

| TWI517541B (zh) | 四相電荷泵電路 | |

| US6888399B2 (en) | Semiconductor device equipped with a voltage step-up circuit | |

| US20080042731A1 (en) | High efficiency bi-directional charge pump circuit | |

| JP4113170B2 (ja) | 半導体装置 | |

| US20080290930A1 (en) | Low voltage charge pump | |

| JP2007221890A (ja) | 半導体集積回路 | |

| US20060273843A1 (en) | High efficiency bi-directional charge pump circuit | |

| US9484344B2 (en) | Semiconductor apparatus | |

| JP2022125281A (ja) | 半導体装置 | |

| Lin et al. | New four-phase generation circuits for low-voltage charge pumps | |

| RU2159472C2 (ru) | Устройство для умножения напряжения | |

| JP2008198985A (ja) | 昇圧回路 | |

| CN110677036A (zh) | 电荷泵电路及其形成方法 | |

| JP3354709B2 (ja) | 半導体昇圧回路 | |

| KR100573780B1 (ko) | 전하펌프 | |

| JPH11308856A (ja) | チャージポンプ回路装置 | |

| JP4730638B2 (ja) | 半導体装置 | |

| Lin et al. | A new 4-phase charge pump without body effects for low supply voltages | |

| US20080211569A1 (en) | Higher voltage switch based on a standard process | |

| JP3354713B2 (ja) | 半導体昇圧回路 | |

| KR200326693Y1 (ko) | 반도체 메모리 장치의 차아지 펌프회로 | |

| JP3569354B2 (ja) | 半導体昇圧回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080822 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080822 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111028 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111108 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120410 |