JP2005294637A - 積層コイルアレイ - Google Patents

積層コイルアレイ Download PDFInfo

- Publication number

- JP2005294637A JP2005294637A JP2004109188A JP2004109188A JP2005294637A JP 2005294637 A JP2005294637 A JP 2005294637A JP 2004109188 A JP2004109188 A JP 2004109188A JP 2004109188 A JP2004109188 A JP 2004109188A JP 2005294637 A JP2005294637 A JP 2005294637A

- Authority

- JP

- Japan

- Prior art keywords

- coil

- conductor

- laminated

- laminate

- adjustment

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004020 conductor Substances 0.000 claims abstract description 288

- 239000000919 ceramic Substances 0.000 claims description 92

- 239000003302 ferromagnetic material Substances 0.000 claims description 6

- 238000003475 lamination Methods 0.000 claims description 6

- 239000000463 material Substances 0.000 claims description 4

- 230000003247 decreasing effect Effects 0.000 abstract 1

- 230000005291 magnetic effect Effects 0.000 description 29

- 230000004907 flux Effects 0.000 description 12

- 239000000843 powder Substances 0.000 description 9

- 230000007423 decrease Effects 0.000 description 8

- 229910000859 α-Fe Inorganic materials 0.000 description 8

- 238000000034 method Methods 0.000 description 7

- 229910017518 Cu Zn Inorganic materials 0.000 description 6

- 229910017752 Cu-Zn Inorganic materials 0.000 description 6

- 229910017943 Cu—Zn Inorganic materials 0.000 description 6

- 229910010293 ceramic material Inorganic materials 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 238000007747 plating Methods 0.000 description 5

- 238000010030 laminating Methods 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 230000000694 effects Effects 0.000 description 2

- 238000010304 firing Methods 0.000 description 2

- 239000000696 magnetic material Substances 0.000 description 2

- 238000007650 screen-printing Methods 0.000 description 2

- -1 Fe 2 O 3 Chemical class 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 238000007606 doctor blade method Methods 0.000 description 1

- 230000005294 ferromagnetic effect Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 238000004898 kneading Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 239000004014 plasticizer Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

Images

Landscapes

- Filters And Equalizers (AREA)

- Coils Or Transformers For Communication (AREA)

Abstract

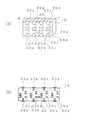

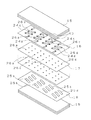

【解決手段】 内側のコイル導体20b,20cの近傍に、内部電極層と重ならないように調整用導体40を設ける。

【選択図】 図1

Description

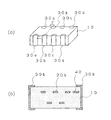

11,12,13,15,16,17,18 セラミックグリーンシート

14 セラミック層

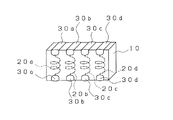

20a〜20d コイル導体

21,23,26a〜26d ビアホール

22 内部導体層

24a〜24d 上部帯状導体

25a〜25d 下部帯状導体

30a〜30d 外部電極

40 調整用導体

Claims (8)

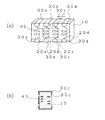

- 複数のセラミック層と内部導体層が交互に積層されてなる積層体を備え、複数の前記内部導体層が直列に接続されてなりコイル軸方向が前記積層体の積層方向に平行であるコイル導体が前記積層体の内部に3個以上配置されている積層コイルアレイであって、

前記積層体の前記コイル導体の配列方向の両端部に位置していないコイル導体の近傍に、前記コイル導体と前記積層体の積層方向で重ならないように前記積層体の積層面に平行な調整用導体を設けたことを特徴とする積層コイルアレイ。 - 前記調整用導体は、前記積層体の両端部に位置していないコイル導体が周回する内側の領域に設けられていることを特徴とする請求項1に記載の積層コイルアレイ。

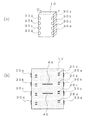

- 複数のセラミック層と内部導体層が交互に積層されてなる積層体を備え、複数の前記内部導体層が直列に接続されてなりコイル軸方向が前記積層体の積層方向に平行であるコイル導体が前記積層体の内部に3個以上配置されている積層コイルアレイであって、

前記積層体の積層面に垂直な端面であって、前記積層体の両端部に位置していないコイル導体の近傍に、調整用導体を設けたことを特徴とする積層コイルアレイ。 - 複数のセラミック層が積層されてなる積層体と、前記積層体の内部に積層面に平行に配置された複数の帯状導体からなる内部導体層と、前記積層体の内部に配置されたバイアホールと、を備え、所定の帯状導体の端部と異なる積層面に配置された帯状導体の端部とをバイアホールによって接続してなりコイル軸方向が前記積層体の積層方向と直交する方向であるコイル導体が、前記積層体の内部に3個以上配置されている積層コイルアレイであって、

前記積層体のコイル導体の配列方向の両端部に位置していないコイル導体の近傍に、前記コイル導体と前記積層体の積層方向で重ならないように前記積層体の積層面に平行な調整用導体を設けたことを特徴とする積層コイルアレイ。 - 前記コイル導体は、前記コイル軸方向に直交する方向に沿って3個以上配列されていることを特徴とする請求項1ないし請求項4のうちいずれか一項に記載の積層コイルアレイ。

- 前記コイル導体は、前記コイル軸方向に沿って3個以上配列されていることを特徴とする請求項1ないし請求項4のうちいずれか一項に記載の積層コイルアレイ。

- 前記調整用導体は強磁性体を含んでなることを特徴とする請求項1ないし請求項6のうちいずれか一項に記載の積層コイルアレイ。

- 前記調整用導体は前記内部導体層と同一の材料からなることを特徴とする請求項1ないし請求項7のうちいずれか一項に記載の積層コイルアレイ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109188A JP2005294637A (ja) | 2004-04-01 | 2004-04-01 | 積層コイルアレイ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109188A JP2005294637A (ja) | 2004-04-01 | 2004-04-01 | 積層コイルアレイ |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294637A true JP2005294637A (ja) | 2005-10-20 |

Family

ID=35327211

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004109188A Pending JP2005294637A (ja) | 2004-04-01 | 2004-04-01 | 積層コイルアレイ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294637A (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2008013071A1 (en) * | 2006-07-27 | 2008-01-31 | Murata Manufacturing Co., Ltd. | Noise filter array |

| WO2008069022A1 (ja) * | 2006-12-08 | 2008-06-12 | Murata Manufacturing Co., Ltd. | 電子部品 |

| JP2010245134A (ja) * | 2009-04-02 | 2010-10-28 | Murata Mfg Co Ltd | 電子部品及びその製造方法 |

| CN111986875A (zh) * | 2019-05-24 | 2020-11-24 | 株式会社村田制作所 | 层叠型线圈部件 |

| JPWO2021106477A1 (ja) * | 2019-11-26 | 2021-06-03 |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0463108U (ja) * | 1990-10-04 | 1992-05-29 | ||

| JPH04130409U (ja) * | 1991-05-17 | 1992-11-30 | 太陽誘電株式会社 | インダクタンス素子 |

| JPH0766037A (ja) * | 1993-08-25 | 1995-03-10 | Tdk Corp | 積層電子部品 |

| JPH07201568A (ja) * | 1993-12-28 | 1995-08-04 | Taiyo Yuden Co Ltd | 積層チップインダクタ |

| JPH09186017A (ja) * | 1995-12-28 | 1997-07-15 | Tokin Corp | 積層インダクタおよびその製造方法 |

| JPH11224817A (ja) * | 1998-02-06 | 1999-08-17 | Murata Mfg Co Ltd | 積層型インダクタアレイ |

| JP2001110641A (ja) * | 1999-10-06 | 2001-04-20 | Tokin Corp | 積層インピーダンス素子 |

| JP2003217935A (ja) * | 2002-01-24 | 2003-07-31 | Murata Mfg Co Ltd | 積層インダクタアレイ |

| JP2003272925A (ja) * | 2002-03-18 | 2003-09-26 | Mitsubishi Materials Corp | 電子部品 |

-

2004

- 2004-04-01 JP JP2004109188A patent/JP2005294637A/ja active Pending

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0463108U (ja) * | 1990-10-04 | 1992-05-29 | ||

| JPH04130409U (ja) * | 1991-05-17 | 1992-11-30 | 太陽誘電株式会社 | インダクタンス素子 |

| JPH0766037A (ja) * | 1993-08-25 | 1995-03-10 | Tdk Corp | 積層電子部品 |

| JPH07201568A (ja) * | 1993-12-28 | 1995-08-04 | Taiyo Yuden Co Ltd | 積層チップインダクタ |

| JPH09186017A (ja) * | 1995-12-28 | 1997-07-15 | Tokin Corp | 積層インダクタおよびその製造方法 |

| JPH11224817A (ja) * | 1998-02-06 | 1999-08-17 | Murata Mfg Co Ltd | 積層型インダクタアレイ |

| JP2001110641A (ja) * | 1999-10-06 | 2001-04-20 | Tokin Corp | 積層インピーダンス素子 |

| JP2003217935A (ja) * | 2002-01-24 | 2003-07-31 | Murata Mfg Co Ltd | 積層インダクタアレイ |

| JP2003272925A (ja) * | 2002-03-18 | 2003-09-26 | Mitsubishi Materials Corp | 電子部品 |

Cited By (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2008013071A1 (en) * | 2006-07-27 | 2008-01-31 | Murata Manufacturing Co., Ltd. | Noise filter array |

| US7880564B2 (en) | 2006-07-27 | 2011-02-01 | Murata Manufacturing Co., Ltd. | Noise filter array |

| WO2008069022A1 (ja) * | 2006-12-08 | 2008-06-12 | Murata Manufacturing Co., Ltd. | 電子部品 |

| JP2010245134A (ja) * | 2009-04-02 | 2010-10-28 | Murata Mfg Co Ltd | 電子部品及びその製造方法 |

| US8193894B2 (en) | 2009-04-02 | 2012-06-05 | Murata Manufacturing Co., Ltd. | Electronic component and method of manufacturing same |

| CN111986875A (zh) * | 2019-05-24 | 2020-11-24 | 株式会社村田制作所 | 层叠型线圈部件 |

| JPWO2021106477A1 (ja) * | 2019-11-26 | 2021-06-03 | ||

| WO2021106477A1 (ja) * | 2019-11-26 | 2021-06-03 | 株式会社村田製作所 | 積層型コイル部品 |

| CN114730655A (zh) * | 2019-11-26 | 2022-07-08 | 株式会社村田制作所 | 层叠型线圈部件 |

| JP7327506B2 (ja) | 2019-11-26 | 2023-08-16 | 株式会社村田製作所 | 積層型コイル部品 |

| CN114730655B (zh) * | 2019-11-26 | 2025-03-25 | 株式会社村田制作所 | 层叠型线圈部件 |

| US12406800B2 (en) | 2019-11-26 | 2025-09-02 | Murata Manufacturing Co., Ltd. | Multilayer coil component |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8334746B2 (en) | Electronic component | |

| EP1739695B1 (en) | Multilayer coil | |

| US7453344B2 (en) | Multilayer coil component | |

| JP3621300B2 (ja) | 電源回路用積層インダクタ | |

| US9251943B2 (en) | Multilayer type inductor and method of manufacturing the same | |

| US11087914B2 (en) | Common mode choke coil | |

| CN109585122B (zh) | 磁耦合型线圈部件 | |

| US6590486B2 (en) | Multilayer inductor | |

| JP2001044037A (ja) | 積層インダクタ | |

| US8395471B2 (en) | Electronic component | |

| WO2011132626A1 (ja) | 積層インダクタ | |

| WO2006073092A1 (ja) | 積層コイル | |

| CN100382207C (zh) | 层叠线圈及其生产方法 | |

| JP3545701B2 (ja) | コモンモードチョーク | |

| KR20130140410A (ko) | 적층 칩 전자부품 | |

| JP2000182834A (ja) | 積層型インダクタンス素子及びその製造方法 | |

| JP2005294637A (ja) | 積層コイルアレイ | |

| JP2003217935A (ja) | 積層インダクタアレイ | |

| JP2009088329A (ja) | コイル部品 | |

| JP4479353B2 (ja) | 積層型電子部品 | |

| WO2011048873A1 (ja) | 積層インダクタ | |

| JP2005259774A (ja) | 開磁路型積層コイル部品 | |

| JP4400430B2 (ja) | 積層型インダクタ | |

| JP2006351954A (ja) | 積層型コモンモードフィルタ | |

| JP2007324554A (ja) | 積層インダクタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070122 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090908 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091006 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091203 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100824 |