JP2005294571A - 電界効果型トランジスタ - Google Patents

電界効果型トランジスタ Download PDFInfo

- Publication number

- JP2005294571A JP2005294571A JP2004108140A JP2004108140A JP2005294571A JP 2005294571 A JP2005294571 A JP 2005294571A JP 2004108140 A JP2004108140 A JP 2004108140A JP 2004108140 A JP2004108140 A JP 2004108140A JP 2005294571 A JP2005294571 A JP 2005294571A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- field effect

- effect transistor

- semiconductor layer

- transistor element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Electroluminescent Light Sources (AREA)

- Thin Film Transistor (AREA)

Abstract

【課題】本発明は、新たな素子構造によってチャネル長を短くして短チャネル化するとともに、実行的電界移動度を向上させた半導体素子を、低コスト製造プロセスで製造することのできるトランジスタ素子を提供することを目的としている。

【課題手段】本発明に係る電界効果型トランジスタ素子は、基板1に、第1電極5、半導体層6、及び、第2電極4が順次積層され、この多層部位の周囲を取り囲むように電気絶縁層3が形成され、該電気絶縁層3の上面に、ゲート電極2が形成されていることを特徴とする。

【選択図】図1

【課題手段】本発明に係る電界効果型トランジスタ素子は、基板1に、第1電極5、半導体層6、及び、第2電極4が順次積層され、この多層部位の周囲を取り囲むように電気絶縁層3が形成され、該電気絶縁層3の上面に、ゲート電極2が形成されていることを特徴とする。

【選択図】図1

Description

本発明は、電界効果型トランジスタに関し、更に詳しくは、ドレイン電極、半導体層、ソース電極、ゲート絶縁層及びゲート電極が積層され、ゲート電極の電気信号によって電流値を制御する電界効果型トランジスタに関し、特に、シートディスプレイ等のコンピュータ用駆動演算回路として用いられる電界効果型トランジスタに適したものである。

半導体層にアモルファスシリコン(a−Si)或いはポリシリコン(p−Si)を用いた電界効果型トランジスタは、既にアクティブマトリクス型液晶ディスプレイ用、或いは有機EL表示装置用として実用化されている。図4はa−Si或いはp−Siを用いた電界効果型トランジスタの構造の一例である。図4に示す電界効果型トランジスタは基板11に対してソース電極15及びドレイン14が横方向に配置されている。つまり、ソース電極15及びドレイン電極14は、電気的に中性であるシリコン半導体層(チャネル層領域)16により分離されて設けられている。ゲート電極12は、ゲート絶縁層13によりシリコン半導体層16と電気的に分離されて、基板11の上に配置している。

近年、印刷法のような低コスト製造プロセスへの関心の高まりから、半導体層の形成に有機材料を用いた電界効果トランジスタが注目されている。図5及び図6は、有機半導体材料を用いた電界効果トランジスタの素子構造例である。図5に示すように、有機材料を用いた場合でも、前記シリコン材料を用いたトランジスタと同様に、ソース電極105及びドレイン電極104は、ドープしたシリコン基板101に対し横方向に配置されている構造が一般的である。ゲート電極(図示省略)は、ゲート絶縁層103により有機半導体層106と電気的に絶縁されて、基板101の上に配置している。

一方、特許文献1所載のトランジスタ構造が存在し、この特許文献1のトランジスタ構造は、図6に示すように、ドレイン電極114、半導体層116、ソース電極115が、基板111上に縦に順次積層されたものである。ここで、ゲート電極112及びゲート絶縁層113は、共に基板111上に形成されており、具体的には、ドレイン電極114、半導体層116及びソース電極115の三層の横方向に隣接してゲート絶縁層113が配置され、該ゲート絶縁層113の横方向に隣接してゲート電極112が配置されている。このような積層型の素子構造を用いることにより、チャネル長を横型素子に比べ短くできるので、有機半導体材料のような比較的高抵抗半導体材料を用いても、充分なドレイン電流が得られる。なお、このような有機半導体層を構成する半導体材料としては、π電子共役系の高分子化合物、芳香族化合物等の有機材料が一般に用いられる。

特開2003−110110号公報

既述の電界効果トランジスタは、それぞれゲート絶縁層を介してゲート電極より印加された電界が半導体層(チャネル部)に作用して、ソース電極とドレイン電極との間に流れる電流を制御することによりトランジスタ動作を実現している。

半導体層に有機材料を用いた電界効果トランジスタは、半導体層にa−Si或いはp−Siを用いた電界効果型トランジスタと比べて、化学気相蒸着法(CVD)のような真空プロセスを必要とせず、印刷法のような簡便なプロセスのみで素子を作製できるため、製造方法が簡便になり、製造コストを低減できるという利点を持っている。しかしながら、半導体層に有機材料を用いた電界効果トランジスタは、半導体層にa−Si或いはp−Siを用いた電界効果型トランジスタと比べて、キャリア移動度が低く、大電流を流すことができない。従って高速動作ができないという問題があった。

従来、このような問題を解決するために、一つとしては有機材料の改善が試みられている。

つまり、有機材料面からの改善として、例えば、π共役系高分子の共役状態を制御する技術、分子電気伝導異方性を用いる技術等の分子設計面に関わる技術、及び、蒸着法にて有機高分子膜を得る際に高い結晶性を実現させる技術が提案されている。

一方、素子構造の改善により上記問題を解決することも提案されている。つまり、図4及び図5に示される電界効果型トランジスタは、ソース電極とドレイン電極との間に電圧を印加した状態でゲート電極に電圧を印加して、ゲート絶縁層と半導体層との界面にチャネルを誘起させることにより、ソース電極とドレイン電極との間に電流を流すものであるが、このときのソース電極とドレイン電極との間の電流(Id)は、一般に次式で表すことができる。

Id=〔W・Cox・?・?Vg−Vth〕2〕/(2・L) (1)式

なお、数式中におけるCox、?、Vg及びVthは次の通りである。

Cox:ゲート容量(F/m2)

?:キャリア移動度(cm2/Vs)

Vg:ゲート電圧(V)

Vth:しきい値電圧(V)

Id=〔W・Cox・?・?Vg−Vth〕2〕/(2・L) (1)式

なお、数式中におけるCox、?、Vg及びVthは次の通りである。

Cox:ゲート容量(F/m2)

?:キャリア移動度(cm2/Vs)

Vg:ゲート電圧(V)

Vth:しきい値電圧(V)

上記式(1)を参照すると、限られたトランジスタ寸法(L:チャネル長、W:チャネル幅)内でトランジスタ性能を向上させるには、より高いId値を実現させなければならない。また、Id値を向上させるための他の因子(チャネル長Lやチャネル幅W以外の因子)として、Cox、??の増加が考えられる。従来においては比誘電率の高い材料を用いて実効的なCoxを向上させたもの(特許文献2)、π共役系高分子材料の開発により?を向上させたもの(特許文献3)等が提案されているが、これらは材料開発が行われて初めて実現され得る。また、チャネル長Lを減少させることにより高いIdを得るためには、素子構造の改善が課題となる。ここでチャネル長Lは、リソグラフィー加工の限界に依存しており、前記図4及び図5に示される電界効果トランジスタでは、チャネル長Lの値は5〜10?m程度が限界であった。一方、図6のような、積層型の素子構造にすることにより、L値を数百nmレベルまで小さくすることができ、式(1)より、数百倍にもおよぶId値を得られるようになった。しかしながら、有機材料の移動度の平均値が10-3〜10-4(cm2/Vs)(ベストデータ:10-2(cm2/Vs))であり、a−Siの場合0.5〜2(cm2/Vs)、p−Siの場合10〜100(cm2/Vs)であることから、有機材料の移動度はa−Siに比べ数十倍から数百倍小さく、p−Siと比べれば数千倍以上小さくなり、図6のような、縦型素子構造でも、まだ不充分である。

特開平10−270712号公報

特開平10−190001号公報

さらに、液晶表示装置においては、前述のようなトランジスタ素子が、前記ソース電極が画素透明電極に接続され、各画素ごとの液晶駆動を行っている。ここで、各画素においては、画素透明電極の占める領域が視認者に視認される透過領域として使用され、ゲート電極やドレイン電極等の存在領域は不透過領域となっている。このため、図4及び図5に示すような横型にソース電極及びドレイン電極が横方向に配置されたトランジスタ素子を用いた場合には液晶表示装置の透過領域の占める割合(開口率)が低くなり、また、特許文献1所載のものにあっても、ドレイン電極114、半導体層116及びソース電極115の三層と、ゲート絶縁層113と、該ゲート絶縁層113とが横方向に配置されているため、開口率が低いという問題を有している。

本発明は、かかる問題を鑑みてなされてものであり、新たな素子構造によってチャネル長を短くして短チャネル化するとともに、実行的電界移動度を向上させた半導体素子を、低コスト製造プロセスで製造することのできるトランジスタ素子を提供することを目的としている。さらには、TFT液晶表示装置等のアクティブマトリクス型ディスプレイに用いた際に、その開口率を高めることのできるトランジスタ素子を提供することを目的ともする。

本発明は、上記目的を解決すべく、本発明に係る電界効果型トランジスタ素子は、基板に、第1電極、半導体層、及び、第2電極が順次積層され、この多層部位の周囲を取り囲むように電気絶縁層が形成され、該電気絶縁層の上面に、ゲート電極が形成されていることを特徴とする。

上記構成を採用することにより、有機半導体材料のように電界移動度がa−Si或いはp−Siより低い材料を用いても、TFT液晶表示装置或いは有機EL表示装置を駆動するのに充分なドレイン電流(Id)が得られるようになった。すなわち、第一電極、半導体層、第二電極、ゲート絶縁膜、ゲート電極を基板に順次積層した構造により、チャネル長をナノメーターのオーダーにまで下げることができる。なお、前記絶縁層は、ゲート電極と他の電極とが短絡することを防ぐ範囲に形成されていれば足り、必ずしも多層部位の周囲全面を覆うことは必須ではない。

また、上記構造により、半導体層のチャネル領域を、半導体層積層方向に沿って左右2箇所に存在するように形成することができ、このため、実行的ドレイン電流を向上させることができる。

また、第一電極、半導体層、第二電極、ゲート絶縁膜、ゲート電極を基板に順次積層した構造であるため、表示装置に用いた場合にあっては、不透過領域を少なくすることができ、十分な開口率を得ることができる。このように表示装置に用いた場合には、第1電極または第2電極の何れか一方が、表面表示装置の画素電極に接続されていることが好ましい。特に、ゲート電極およびゲート絶縁膜にはピンホールが形成され、該ピンホールを介して前記第1電極または第2電極と画素電極とが電気的に接続されている構成を採用することが好ましい。

なお、前記電気絶縁層はゲート絶縁層とすることが可能である。さらに、前記半導体層を、無機材料や、低分子及び高分子有機材料より形成することが可能である。また、前記電気絶縁層を、無機材料や、低分子及び高分子有機材料より形成することも可能である。

また、前記第1電極、第2電極、及び、ドレイン電極は、無機材料や、低分子及び高分子有機材料と適切なドーパンドとなる添加剤より形成することが可能である。なお、各電極は同一の材料から構成されても良いし、異なる材料、つまりは、一つの電極が無機材料で構成され、他の材料が上記低分子及び高分子有機材料と適切なドーパンドとなる添加剤で構成されていることも可能である。

また、第1電極および第2電極は、それぞれ、ソース電極およびドレイン電極から構成することが可能である。

ここで、前記ソース電極は、従来のCVD法で成膜し、フォトリソグラフィーにより加工して形成する方法と、インクジェット法のような印刷法によって形成する方法がある。ここで、ソース電極は、複数本が平行に基板上に形成することが好ましい。

また、前記半導体層は、前記ソース電極と同様にCVD法とフォトリソグラフィーを用いても良いが、印刷法を用いた方が低コストである。ここで、半導体層の厚みは、チャネル長に相当するため、特に目的のチャネル長に応じて、正確な制御が必要となる。ドレイン電流値を大きくするためには、膜圧を小さくする程良いが、あまり小さくし過ぎると、ソース電極とドレイン電極が接触する可能性があるので、注意が必要である。なお、半導体層は、一つのソース電極層に複数積層され、つまり、各画素ごとに該半導体層が設けられることが好ましい。

また、前記ドレイン電極は、前記ソース電極と同様の方法により形成することができる。なお、ドレイン電極は、各半導体層ごとにそれぞれ設けられ、つまり、各画素ごとに該ドレイン電極層が設けられていることが好ましい。また、該ドレイン電極層は、各画素の画素電極(透明電極)に電気的に接続されることが好ましい。

また、前記ゲート絶縁膜は、CVD法とフォトリソグラフィー法の組み合わせで形成することができるが、印刷法によっても形成することができる。ここで、ゲート絶縁膜は、前記ソース電極、半導体層、及び、ドレイン電極が積層されてなる三層の周囲を取り囲むように形成されている。該ゲート絶縁膜は、前記半導体層及びドレイン電極層と同様に各画素ごとに設けられ、つまり、該ゲート絶縁膜は、ゲート電極層を他の電極層と電気的に接続しないように設けられていることが好ましい。

また、ゲート電極も、CVD法による成膜とフォトリソグラフィーによる加工で形成する方法と、印刷法のような溶液プロセスにより形成する方法との二通りによって形成することができる。また、CVD及びフォトリソグラフィーを用いたプロセスと、溶液プロセスの両方が含まれる工程を用いて、デュアル・サイド・ゲート電界効果型トランジスタを作製してもよい。なお、該ゲート電極は、前記ゲート絶縁膜が存在する位置において、前記ソース電極と平面視交差するように複数形成されることが好ましい。

なお、上述しているトランジスタ素子は縦型構造であり、半導体層中に形成されるチャネルは、基板面に対して上下方向である。したがって、半導体層として、芳香族化合物系有機材料のπ電子雲が上下方向に形成される環状化合物を採用すると、かかる環状化合物にとって特に有効な素子構造である

また、本発明に係る電界効果型トランジスタ素子の製造方法は、基板に、第1電極、半導体層、及び、第2電極を順次積層し、この三層の周囲を取り囲むように電気絶縁層を形成し、該電気絶縁層の上面に、ゲート電極が形成することを特徴とする。これにより、既述の利点を有する電界効果型トランジスタ素子を製造することができる。

なお、液晶表示装置等の表示装置の基板に上記電界効果型トランジスタ素子を形成する場合には、前記ゲート電極及び電気絶縁膜にピンホールを形成し、該ピンホールを介して前記第1電極または第二電極と画素電極とを電気的に接続する構成を採用することが好ましい。

以上のような本発明にあっては、基板に対して垂直方向にチャネル領域が形成される縦型の電界効果型トランジスタであるため、チャネル長が、従来の横型素子に比べてオーダーで小さくなるため、移動度の低い半導体材料を用いても、充分大きいドレイン電流が得られる。また、本発明のデュアル・サイド・ゲート電界効果トランジスタは、半導体層一層中に、二箇所チャネル領域が形成されるため、より効果的にドレイン電流が得られる。また、素子構造が容易であるため、従来の製造技術と精度でもって、トランジスタを製造することができる。

以下、本発明を実施する最良の形態について図面に基づいて説明する。

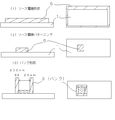

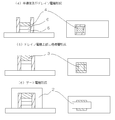

なお、図1は、本発明の一実施の形態の素子構造の模式的断面図を示す。図2は、本発明の一実施の形態の製造工程に関して、CVD法及びフォトリソグラフィー法を用いた場合の様子を説明する図である。図3は、本発明の一実施の形態の製造工程に関して、インクジェット法或いはマイクロコンタクトプリンティング法等の溶液プロセスを用いて製造する工程図である。

なお、図1は、本発明の一実施の形態の素子構造の模式的断面図を示す。図2は、本発明の一実施の形態の製造工程に関して、CVD法及びフォトリソグラフィー法を用いた場合の様子を説明する図である。図3は、本発明の一実施の形態の製造工程に関して、インクジェット法或いはマイクロコンタクトプリンティング法等の溶液プロセスを用いて製造する工程図である。

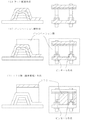

本発明の実施形態のトランジスタ素子は、デュアル・サイド・ゲートトランジスタとして有効に活用されるTFT素子であり、該TFT素子は、図1に示すように、基板上に、ソース電極5(第1電極)、半導体層6(半導体領域)、ドレイン電極(第2電極)、ゲート絶縁膜、及び、ゲート電極2を順次積層してなるものである。

前記ソース電極5は、複数本が平行に同一ピッチで基板1に形成されており、この複数本のソース電極5は、各画素領域の間に配置されている。また、前記ゲート電極層2は、前記ソース電極5と平面視直交するように複数本が平行に同一ピッチで形成されており、この複数本のゲート電極層2も、各画素領域の間に配置されている。そして、前記ソース電極5、半導体層6、ドレイン電極4及びゲート絶縁膜3は、平面視において前記ゲート電極層2と前記ソース電極5とが直交する箇所で、且つ、ゲート電極層2とソース電極5との間に形成されている。

上記構成からなる本実施形態のTFT素子は、ドレイン電流Idを基板1の面に直交する方向に流し、活性領域(ソース電極5、半導体層6及びドレイン電極4)の周囲に設けられたゲート電極2からゲート絶縁層3を介して半導体層6に電界が印加する構造となっている。ここで、ソース電極5に積層される半導体層6の膜厚Lは薄くすることができるので、従来のようにフォトリソグラフィーの加工精度に依存するものに比して、チャネル長Lを飛躍的に短くした構造を実現できる。その結果、トランジスタ性能、すなわち、実効的なドレイン電流値を向上させることができる。また、半導体素子の構造がシンプルであるので、製造工程を簡略化することができ、そのために、半導体素子の製造コストを低減することができる。

また、本実施形態のTFT素子は、前記第一電極(ソース電極5)、半導体層6及び第二電極(ドレイン電極4)の活性領域の周囲にゲート絶縁層3が形成され、更にゲート絶縁層3の周囲に第三電極(ゲート電極2)が設けられている。つまり、半導体層6のチャネル領域が半導体層積層方向に沿って左右2箇所に存在している。このように、半導体層6のチャネル領域は、半導体層6の左右両方に形成されているため、チャネル長Lを短くできる効果に加え、チャネル領域も二箇所形成されるため、より効果的にドレイン電流を流すことができる。

また、平面位置においてソース電極5とゲート電極2とが交差する位置に、前記ソース電極5、半導体層6及びドレイン電極4が配置されることにより、画素電極を大きくとることができ、このため、表示装置の開口率を向上することができる。

なお、本発明の半導体素子は、特許文献1で開示されているように、第一電極5と半導体層6との間、又は、半導体層6と第二電極7との間にバッファー層を設けることも適宜設計変更可能な事項である。このようにバッファー層を設けることにより、第一電極5と半導体層6と第二電極7との間に良好な電気的コンタクトを得ることができる。なお、このバッファー層は、例えば、印刷法、インクジェット法等の溶液プロセスで形成可能な導電性高分子材料で形成され、また、ポリチオフェンやポリフェニレン等の他、有機EL用途でよく用いられる低分子系導電性材料を真空蒸着法にて形成してもよい。このように、バッファー層を挿入した素子においては、キャリアは、半導体層とバッファー層の界面に形成された僅かな電位差障壁を越えて伝道するので、特にオフ電流の低減に効果的である。

前記半導体としては、好ましくは、ナフタレン、アントラセン、テトラセン、ペンタセン、及びそれらの誘導体よりなるアセン分子材料や、フタロシアニン系化合物、アゾ系化合物、ぺリレン系化合物よりなる顔料及びその誘導体や、ヒドラゾン化合物、ジフェニルメタン化合物、トリフェニルメタン化合物、スチルベン化合物、アリールビニル化合物、ピラゾリン化合物、トリフェニルアミン化合物、フェニレン誘導体及びトリアリールアミン化合物よりなる低分子化合物並びにそれらの誘導体や、ポリ−N−ビニルカルバゾール、ポリチオフェン、ポリフェニレン、ポリフェニレンビニレン、ポリアルキルフルオレン、ポリチオナフテン、ポリアニリン、ポリピロール等の高分子化合物等からなる有機半導体材料で構成することができる。このように、半導体を構成する材料が有機半導体材料とすることにより、高分子有機半導体材料を採用した場合には、その溶液をインクジェット法、マイクロコンタクトプリンティング法のような印刷法により成膜することができる。また、低分子有機半導体材料を採用した場合には、これを真空蒸着法等の手段により成膜することができるので、極めて薄い有機半導体層を低コストで形成することができる。

また、前記半導体層は、a−Si、p−Si等のシリコン、酸化亜鉛、酸化スズ等の金属酸化物のような無機半導体材料で構成されてもかまわない。このように、無機半導体材料を真空蒸着法等の手段により成膜できるので、極めて薄い無機半導体層を製造することができる。

前記ゲート絶縁層の材料としては、ポリビニルアルコール、ポリビニルブチラール、フェノール樹脂、ノボラック樹脂等のヒドロキシル基を有するポリマー、ポリアクリロニトリル等のシアノ基を有するポリマー、さらには、ポリクロロピレンポリエチレンテレフタレート、ポリオキシメチレン、ポリビニルクロライド、ポリ弗化ビニリデン、ポリメチルメタクリレート、ポリカーボネート、ポリイミド、ポリサルフォン、ポリオルガノシロキサン等のポリマー材料が挙げられる。また、ポリマーだけでなく、SiO2、SiN、Al2O3、等の無機材料を用いても良い。また、ゲート絶縁膜として二層以上の膜を積層することも可能である。また蒸着法やスパッタリング法、塗布法、印刷法またはインクジェット法等材料に応じた公知の成膜方法を用いて膜を堆積した後、フォトリソグラフィー工程及びエッチング工程によって所望の配置のゲート絶縁膜を形成することが可能である。

前記第一電極(ソース電極)、第二電極(ドレイン電極)及びゲート電極は、Cr、Al、Ta、Mo、Nb、Cu、Ag、Au、Pt、Pd、In、Ni、Ndおよびこれらの合金や、ポリシリコン、非晶質シリコン、錫酸化物、酸化インジウム、インジウム錫酸化物(ITO;Indium Tin Oxide)等の無機材料や、ドープされた導電性高分子(例えば、ポリエチレンジオキシチオフェン(PEDOT)とポリスチレンスルホン酸ナトリウムとの混合物等)等の有機材料から構成することができる。また二層以上の層から前記電極を形成することも可能である。電極もまた、蒸着法やスパッタリング法、塗布法、印刷法またはインクジェット法等材料に応じた公知の成膜方法を用いて膜を堆積した後、フォトリソグラフィー工程及びエッチング工程によって所望の配置に形成することができる。

なお、本発明のトランジスタ素子の製造方法の一実施態様を説明すると、まず基板1に第1電極5となる電極膜、半導体層6となる半導体膜及び第2電極4となる電極膜を例えば蒸着法等により順次積層する(図2(1)参照)。そして、エッチング処理により所望の形状の第1電極5、半導体層6及び第2電極4を得る(図2(2)参照)。次に、該第1電極5、半導体層6及び第2電極4の周囲にゲート絶縁膜3を例えば印刷法等により形成する(図2(3)参照)。そして、このゲート絶縁膜3の上面にゲート電極2を、例えば蒸着により成膜した後に、フォトリソグラフィー工程及びエッチング工程によって所望の形状に形成する(図2(4)参照)。

また、本発明のトランジスタ素子の製造方法の他の実施態様を説明すると、まず基板1にレジストからなるバンクを筒状に形成する(図3(1)参照)。そして、この筒状のバンク内に、第1電極5、半導体層6及び第2電極4を順次積層する(図3(2)参照)。次に、第2電極4の上面に、前記バンクと同様の材料によってゲート絶縁膜3を形成する(図3(3)参照)。そして、このゲート絶縁膜3の上面にゲート電極2を形成する(図3(4)参照)。

(実施例1)

次に、本発明の具体的な実施例として、以下のデュアル・サイド・ゲートトランジスタをその製造手順とともに図7及び図8を参酌しつつ以下説明する。

次に、本発明の具体的な実施例として、以下のデュアル・サイド・ゲートトランジスタをその製造手順とともに図7及び図8を参酌しつつ以下説明する。

まず、本実施例においては、ガラス基板1上にCr層5を膜厚50nmで成膜し(図7(1)参照)、該Cr層5の上面にAu層を膜厚150nmの厚みで成膜する。

次に、前記Au膜上にフォトレジストをスピンコートにより塗布し、続いて所定のパターンのマスクを用いて露光、現像する。続いて、Au層及びCr層5を剥離し、最後にNaOH溶液に浸してレジストを剥離し、所望形状のソース電極5を形成する(図7(2)参照)。

そして、ソース電極5の全てのサイドに、バンク形成を行った(図7(3)参照)。ここではボラック樹脂を含有するフォトレジストを前記基板1上にスピンコート法により成膜して、このレジスト膜を所望のパターンに露光、現像することにより、前記ソース電極5のサイドにレジストによるゲート絶縁層となるバンク3を形成している。バンク3の幅方向の厚みは200nmとしている。

次にソース電極5の上部に、インクジェット法により、ポリヘキシルチオフェン膜を作成し、半導体層6を形成する。半導体層6の厚みは200nmになるようにした。また、チャネル幅は20μmとした。さらに、半導体層6の上部に、PEDOT/PSS(ポリエチレンジオキシチオフェン/ポリスチレンスルホン酸塩)による膜をインクジェット法により作成して、ドレイン電極4を形成する(図8(1)参照)。

そして、ドレイン電極4の上部に、ドレイン電極4とゲート電極2の接触を避けるための絶縁層として、ノボラック樹脂を含有するフォトレジストをインクジェット法により塗布し、ゲート絶縁層3を形成する(図8(2)参照)。

ゲート絶縁層の周囲に、ゲート電極2としてTa膜を形成する。Ta膜形成はCVD法とドライエッチング法により形成した(図8(3)参照)。

以上の工程で作製したデュアル・サイド・ゲートトランジスタの特性評価を行った。ソース/ドレイン電圧を−20Vから0Vの範囲で変化させ、ゲート電圧を−20Vから0Vの範囲で変化させた。この場合のドレイン電流は150μAだった。ここから既述の式(1)式を用いて得られる移動度は1×10-2cm2/Vsである。またオン/オフ比は106であり、従来のa−Siを用いたトランジスタと同レベルだった。

(比較例1)

実施例1の比較例として、図6で示される、従来構造のいわゆる横型電界効果型トランジスタの製造に関する比較例1を以下に示す。

高濃度にリンをドープしたSiウエハよりなる基板を1100度で熱酸化処理して、200nmの熱酸化膜を形成する。そして、ソース/ドレイン電極としてAu/Cr膜を積層し、これらの膜にフォトリソグラフィ・エッチングにより、パターンを形成した。チャネル長を5μm、チャネル幅を20μmとした。最後にポリヘキシルチオフェン溶液をスピンコート法により成膜して、横型電界効果トランジスタを作製した。

実施例1の比較例として、図6で示される、従来構造のいわゆる横型電界効果型トランジスタの製造に関する比較例1を以下に示す。

高濃度にリンをドープしたSiウエハよりなる基板を1100度で熱酸化処理して、200nmの熱酸化膜を形成する。そして、ソース/ドレイン電極としてAu/Cr膜を積層し、これらの膜にフォトリソグラフィ・エッチングにより、パターンを形成した。チャネル長を5μm、チャネル幅を20μmとした。最後にポリヘキシルチオフェン溶液をスピンコート法により成膜して、横型電界効果トランジスタを作製した。

以上の工程で作製した横型電界効果トランジスタの特性評価を行った。ソース/ドレイン電圧を−20Vから0Vの範囲で変化させ、ゲート電圧を−20Vから0Vの範囲で変化させた。この場合のドレイン電流は6μAだった。ここから既述の式(1)を用いて得られる移動度は2×10-2cm2/Vsである。またオン/オフ比は106であり、従来のa−Siを用いたトランジスタと同レベルだった。

以上の実施例1及び比較例1の結果を比較したところ、キャリア移動度は、同じポリヘキシルチオフェンを用いているにも関わらず、異なった値を示した。これについては、実施例1では、ドレイン電極にPEDOT/PSSを用いており、一方、比較例1では、ソース/ドレイン電極ともAu/Crを用いていること、及び、ゲート絶縁膜に関して実施例1では、有機系高分子材料を用いており、比較例1ではシリコン熱酸化膜を用いているためである。このような要因から、実施例1では、移動度が比較例1に比べて約半分の値であるにも関わらず、ドレイン電流値は、実施例1は、比較例1に比べて25倍ある。一方、オン/オフ比に関して、実施例1と比較例1で違いは見られなかった。

これらの結果より、実施例1のデュアル・サイド・ゲート電界効果トランジスタを用いることにより、移動度の遅い半導体材料を用いても、充分大きいドレイン電流を得ることができ、特に、高分子系有機半導体用素子として有効であることが、確認された。

(実施例2)

次に、本発明の具体的な実施例として、以下のLCDパネルに用いられるTFT素子をその製造手順とともに図9及び図10を参酌しつつ以下説明する。

次に、本発明の具体的な実施例として、以下のLCDパネルに用いられるTFT素子をその製造手順とともに図9及び図10を参酌しつつ以下説明する。

まず、実施例2にあっては、基板1上にソース電極5を形成する(図9(1)参照)。ソース電極5はCr及びAuをCVD法により成膜し、フォトリソグラフィー及びドライエッチングにより形成している。ここで、ソース電極5は複数本形成されている。

次に、半導体層6を、ポリチオフェンをインクジェット法により成膜して形成する(図9(2)参照)。ここでは、半導体層6は、前記ソース電極5の上に複数形成している。

そして、前記半導体層6の上面に、ドレイン電極4を形成する(図9(3)参照)。ここで、ソース電極5と同様に、AuをCVD法により成膜し、フォトリソグラフィー及びドライエッチングにより形成した。

次に、前記積層された三層の周囲にゲート絶縁膜3を形成する(図9(4)参照)。ここでは、ポリビニルフェノールを用い、インクジェット法により成膜してゲート絶縁膜3を形成した(図8(4)参照)。

そして、前記三層の上面を通るようなゲート電極2を形成する(図10(1)参照)。ここでは、AlをCVD法により成膜形成して、前記ゲート電極2を形成した。

次に、パッシベーション膜形成を行う。窒化シリコンをCVD法により成膜する(図10(2)参照)。この際、マスク蒸着をおこなうことにより、ドレイン電極上にドレイン電極4まで貫通するピンホールを形成した。

そして、前記パッシベーション膜の上面に、画素電極として、ITO膜を形成する(図10(3)参照)。ここでは、透明電極は、CVD法により成膜し、フォトリソグラフィーおよびウエットエッチングにより形成した。

1、11、101、111…絶縁性基板、ガラス基板,透明性基板

2、12、102、112…ゲート電極

3、13、103、113…ゲート絶縁層

4、14、104,114…ドレイン電極

5、15、105、115…ソース電極

6、16、106,116…半導体層

2、12、102、112…ゲート電極

3、13、103、113…ゲート絶縁層

4、14、104,114…ドレイン電極

5、15、105、115…ソース電極

6、16、106,116…半導体層

Claims (12)

- 基板には、第1電極、半導体層、及び、第2電極が順次積層されており、

この多層部位の周囲を取り囲むように電気絶縁層が形成され、

該電気絶縁層の上面には、ゲート電極が形成されていることを特徴とする

電界効果型トランジスタ素子。 - 請求項1記載の電界効果型トランジスタ素子であって、

半導体層のチャネル領域が半導体層積層方向に沿って左右2箇所に存在するように形成されていることを特徴とする

電界効果型トランジスタ素子。 - 請求項1又は2記載の電界効果型トランジスタ素子であって、

前記第1電極または第2電極の何れか一方が、表面表示装置の画素電極に接続されていることを特徴する

電界効果型トランジスタ素子。 - 請求項1乃至3の何れかに記載の電界効果型トランジスタ素子であって、

前記電気絶縁層が、ゲート絶縁層であることを特徴する

電界効果型トランジスタ素子。 - 請求項1乃至4の何れかに記載の電界効果型トランジスタ素子であって、

前記半導体層が、無機材料より形成されていることを特徴とする

電界効果型トランジスタ素子。 - 請求項1乃至4の何れかに記載の電界効果型トランジスタ素子であって、

前記半導体層が、低分子及び高分子有機材料より形成されていることを特徴とする

電界効果型トランジスタ素子。 - 請求項1乃至6の何れかに記載の電界効果型トランジスタ素子であって、

前記電気絶縁層が、無機材料より形成されていることを特徴とする

電界効果型トランジスタ素子。 - 請求項1乃至6の何れかに記載の電界効果型トランジスタ素子であって、

前記電気絶縁層が、低分子及び高分子有機材料より形成されていることを特徴とする

電界効果型トランジスタ素子。 - 請求項1乃至8の何れかに記載の電界効果型トランジスタ素子であって、

前記第1電極、第2電極、及び、ドレイン電極の少なくとも一つが、無機材料より形成されていることを特徴とする

電界効果型トランジスタ素子。 - 請求項1乃至8の何れかに記載の電界効果型トランジスタ素子であって、

前記第1電極、第2電極、及び、ドレイン電極の少なくとも一つが、低分子及び高分子有機材料と、適切なドーパンドとなる添加剤より形成されていることを特徴とする

電界効果型トランジスタ素子。 - 請求項1乃至11の何れかに記載のトランジスタ素子を備えることを特徴とするアクティブマトリクス型ディスプレイ。

- 基板に、第1電極、半導体層、及び、第2電極を順次積層し、

この三層の周囲を取り囲むように電気絶縁層を形成し、

該電気絶縁層の上面に、ゲート電極が形成することを特徴とする

電界効果型トランジスタ素子の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108140A JP2005294571A (ja) | 2004-03-31 | 2004-03-31 | 電界効果型トランジスタ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108140A JP2005294571A (ja) | 2004-03-31 | 2004-03-31 | 電界効果型トランジスタ |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294571A true JP2005294571A (ja) | 2005-10-20 |

Family

ID=35327158

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004108140A Pending JP2005294571A (ja) | 2004-03-31 | 2004-03-31 | 電界効果型トランジスタ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294571A (ja) |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2007142238A1 (ja) * | 2006-06-07 | 2007-12-13 | Panasonic Corporation | 半導体素子およびその製造方法ならびに電子デバイスおよびその製造方法 |

| US7932142B2 (en) | 2007-11-14 | 2011-04-26 | Elpida Memory, Inc. | Transistor in a wiring interlayer insulating film |

| WO2011052410A1 (en) * | 2009-10-30 | 2011-05-05 | Semiconductor Energy Laboratory Co., Ltd. | Power diode, rectifier, and semiconductor device including the same |

| WO2011052413A1 (en) * | 2009-10-30 | 2011-05-05 | Semiconductor Energy Laboratory Co., Ltd. | Non-linear element, display device, and electronic device |

| WO2011065209A1 (en) * | 2009-11-27 | 2011-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Non-linear element, display device including non-linear element, and electronic device including display device |

| JP2011119691A (ja) * | 2009-10-30 | 2011-06-16 | Semiconductor Energy Lab Co Ltd | 電界効果型トランジスタ |

| JP2011119690A (ja) * | 2009-10-30 | 2011-06-16 | Semiconductor Energy Lab Co Ltd | 電界効果型トランジスタ |

| JP2011124562A (ja) * | 2009-11-13 | 2011-06-23 | Semiconductor Energy Lab Co Ltd | 非線形素子、該非線形素子を有する表示装置および該表示装置を有する電子機器 |

| JP2011129898A (ja) * | 2009-11-20 | 2011-06-30 | Semiconductor Energy Lab Co Ltd | トランジスタ |

| JP2011129899A (ja) * | 2009-11-20 | 2011-06-30 | Semiconductor Energy Lab Co Ltd | トランジスタ |

| US8492806B2 (en) | 2009-10-30 | 2013-07-23 | Semiconductor Energy Laboratory Co., Ltd. | Non-linear element, display device including non-linear element, and electronic device including display device |

| JP2015062248A (ja) * | 2009-11-28 | 2015-04-02 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2018203181A1 (ja) * | 2017-05-01 | 2018-11-08 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN117059626A (zh) * | 2023-08-11 | 2023-11-14 | 上海大学 | 一种薄膜晶体管及其制备方法和应用 |

-

2004

- 2004-03-31 JP JP2004108140A patent/JP2005294571A/ja active Pending

Cited By (47)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2007142238A1 (ja) * | 2006-06-07 | 2007-12-13 | Panasonic Corporation | 半導体素子およびその製造方法ならびに電子デバイスおよびその製造方法 |

| US7749921B2 (en) | 2006-06-07 | 2010-07-06 | Panasonic Corporation | Semiconductor element, method for manufacturing the semiconductor element, electronic device and method for manufacturing the electronic device |

| US7932142B2 (en) | 2007-11-14 | 2011-04-26 | Elpida Memory, Inc. | Transistor in a wiring interlayer insulating film |

| JP2015084428A (ja) * | 2009-10-30 | 2015-04-30 | 株式会社半導体エネルギー研究所 | 電界効果型トランジスタ |

| WO2011052413A1 (en) * | 2009-10-30 | 2011-05-05 | Semiconductor Energy Laboratory Co., Ltd. | Non-linear element, display device, and electronic device |

| KR101796909B1 (ko) * | 2009-10-30 | 2017-12-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 비선형 소자, 표시 장치, 및 전자 기기 |

| JP2011119691A (ja) * | 2009-10-30 | 2011-06-16 | Semiconductor Energy Lab Co Ltd | 電界効果型トランジスタ |

| JP2011119690A (ja) * | 2009-10-30 | 2011-06-16 | Semiconductor Energy Lab Co Ltd | 電界効果型トランジスタ |

| JP2017108193A (ja) * | 2009-10-30 | 2017-06-15 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2016154254A (ja) * | 2009-10-30 | 2016-08-25 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN102668095B (zh) * | 2009-10-30 | 2016-08-03 | 株式会社半导体能源研究所 | 晶体管 |

| CN102668095A (zh) * | 2009-10-30 | 2012-09-12 | 株式会社半导体能源研究所 | 晶体管 |

| US9385114B2 (en) | 2009-10-30 | 2016-07-05 | Semiconductor Energy Laboratory Co., Ltd. | Non-linear element, display device including non-linear element, and electronic device including display device |

| TWI500167B (zh) * | 2009-10-30 | 2015-09-11 | Semiconductor Energy Lab | 功率二極體、整流器、及包含該功率二極體或該整流器之半導體裝置 |

| US8492806B2 (en) | 2009-10-30 | 2013-07-23 | Semiconductor Energy Laboratory Co., Ltd. | Non-linear element, display device including non-linear element, and electronic device including display device |

| US8598635B2 (en) | 2009-10-30 | 2013-12-03 | Semiconductor Energy Laboratory Co., Ltd. | Transistor |

| US8643004B2 (en) | 2009-10-30 | 2014-02-04 | Semiconductor Energy Laboratory Co., Ltd. | Power diode including oxide semiconductor |

| US8704218B2 (en) | 2009-10-30 | 2014-04-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having an oxide semiconductor film |

| US8791456B2 (en) | 2009-10-30 | 2014-07-29 | Semiconductor Energy Laboratory Co. Ltd. | Non-linear element, display device including non- linear element, and electronic device including display device |

| US8941107B2 (en) | 2009-10-30 | 2015-01-27 | Semiconductor Energy Laboratory Co., Ltd. | Power diode, rectifier, and semiconductor device including the same |

| US9112041B2 (en) | 2009-10-30 | 2015-08-18 | Semiconductor Energy Laboratory Co., Ltd. | Transistor having an oxide semiconductor film |

| JP2015065466A (ja) * | 2009-10-30 | 2015-04-09 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2011052410A1 (en) * | 2009-10-30 | 2011-05-05 | Semiconductor Energy Laboratory Co., Ltd. | Power diode, rectifier, and semiconductor device including the same |

| US9105609B2 (en) | 2009-10-30 | 2015-08-11 | Semiconductor Energy Laboratory Co., Ltd. | Oxide-based semiconductor non-linear element having gate electrode electrically connected to source or drain electrode |

| JP2015092590A (ja) * | 2009-10-30 | 2015-05-14 | 株式会社半導体エネルギー研究所 | トランジスタ |

| TWI496288B (zh) * | 2009-10-30 | 2015-08-11 | Semiconductor Energy Lab | 非線性元件,顯示裝置及電子裝置 |

| JP2011124562A (ja) * | 2009-11-13 | 2011-06-23 | Semiconductor Energy Lab Co Ltd | 非線形素子、該非線形素子を有する表示装置および該表示装置を有する電子機器 |

| JP2015092603A (ja) * | 2009-11-20 | 2015-05-14 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR101800852B1 (ko) * | 2009-11-20 | 2017-12-20 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP2016184767A (ja) * | 2009-11-20 | 2016-10-20 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2011129899A (ja) * | 2009-11-20 | 2011-06-30 | Semiconductor Energy Lab Co Ltd | トランジスタ |

| JP2015097275A (ja) * | 2009-11-20 | 2015-05-21 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2016201562A (ja) * | 2009-11-20 | 2016-12-01 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2011129898A (ja) * | 2009-11-20 | 2011-06-30 | Semiconductor Energy Lab Co Ltd | トランジスタ |

| WO2011065209A1 (en) * | 2009-11-27 | 2011-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Non-linear element, display device including non-linear element, and electronic device including display device |

| JP2015097277A (ja) * | 2009-11-27 | 2015-05-21 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2013062533A (ja) * | 2009-11-27 | 2013-04-04 | Semiconductor Energy Lab Co Ltd | 非線形素子 |

| US8390044B2 (en) | 2009-11-27 | 2013-03-05 | Semiconductor Energy Laboratory Co., Ltd. | Non-linear element, display device including non-linear element, and electronic device including display device |

| US9368640B2 (en) | 2009-11-28 | 2016-06-14 | Semiconductor Energy Laboratory Co., Ltd. | Transistor with stacked oxide semiconductor films |

| JP2015062248A (ja) * | 2009-11-28 | 2015-04-02 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2018203181A1 (ja) * | 2017-05-01 | 2018-11-08 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JPWO2018203181A1 (ja) * | 2017-05-01 | 2020-03-12 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP7128809B2 (ja) | 2017-05-01 | 2022-08-31 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2022159517A (ja) * | 2017-05-01 | 2022-10-17 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP7441282B2 (ja) | 2017-05-01 | 2024-02-29 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2024050930A (ja) * | 2017-05-01 | 2024-04-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN117059626A (zh) * | 2023-08-11 | 2023-11-14 | 上海大学 | 一种薄膜晶体管及其制备方法和应用 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5638944B2 (ja) | 有機薄膜トランジスタ | |

| JP5599190B2 (ja) | 有機薄膜トランジスタの製造方法 | |

| US8089065B2 (en) | Organic thin film transistors | |

| US7919778B2 (en) | Making organic thin film transistor array panels | |

| JP4815765B2 (ja) | 有機半導体装置の製造方法 | |

| US8963141B2 (en) | Thin-film transistor, fabrication method thereof, and image display device | |

| CN102017209A (zh) | 有机薄膜晶体管 | |

| JP2005294571A (ja) | 電界効果型トランジスタ | |

| US7915074B2 (en) | Thin film transistor array panel and manufacturing method thereof | |

| JP4408903B2 (ja) | トランジスタ、トランジスタ回路、電気光学装置および電子機器 | |

| US7777220B2 (en) | Organic thin film transistor array panel | |

| CN102017211A (zh) | 有机薄膜晶体管 | |

| JP2005167164A (ja) | トランジスタ及びその作製方法 | |

| JP5148086B2 (ja) | 有機薄膜トランジスタ表示板 | |

| JP2004111872A (ja) | 縦型電界効果トランジスタ及びその製造方法並びにそれを有する演算素子 | |

| CN108428795B (zh) | 薄膜晶体管、其制造方法和包括其的电子设备 | |

| KR102277814B1 (ko) | 박막 트랜지스터 및 그 제조 방법과 상기 박막 트랜지스터를 포함하는 전자 소자 | |

| JP2005223049A (ja) | 半導体装置、半導体装置の製造方法、および表示装置 | |

| JP5884306B2 (ja) | 薄膜トランジスタおよびその製造方法、ならびに電子機器 | |

| JP6331644B2 (ja) | 薄膜トランジスタアレイおよびその製造方法 | |

| JP2016163029A (ja) | 薄膜トランジスタ、薄膜トランジスタアレイの製造方法及び画素表示装置 | |

| KR101240653B1 (ko) | 박막 트랜지스터 표시판 및 그 제조 방법 | |

| KR101363255B1 (ko) | 유기 박막 트랜지스터 및 이의 제조방법 | |

| JP5277532B2 (ja) | 電子素子 | |

| US20080073648A1 (en) | Thin film transistor array panel and manufacturing method thereof |