上記目的を達成するために、この発明の一の局面による半導体素子の製造方法は、基板上の第1素子形成領域に、第1の方向に延びる第1能動素子領域の端部が第1の方向と交差する第2の方向に延びる第1分割線上に配置されるように、第1能動素子領域を含む第1半導体素子層を形成するとともに、基板上の第1分割線に沿って第1素子形成領域に接する第2素子形成領域に、第1の方向に延びる第2能動素子領域の端部が第1分割線上に配置されるように、かつ、第1能動素子領域と第2能動素子領域とが第1の方向に連続しないように、第2能動素子領域を含む第2半導体素子層を形成する工程と、第1分割線に沿って、第1半導体素子層および第2半導体素子層が形成された基板を分割する工程とを備えている。なお、本発明の能動素子領域は、たとえば、半導体レーザ素子のリッジ部を意味する。

上記一の局面による半導体素子の製造方法では、上記のように、基板上の第1素子形成領域に、第1の方向に延びる第1能動素子領域を含む第1半導体素子層を形成するとともに、基板上の第1分割線に沿って第1素子形成領域に接する第2素子形成領域に、第1能動素子領域と第2能動素子領域とが第1の方向に連続しないように、第2能動素子領域を含む第2半導体素子層を形成することによって、基板上の第1素子形成領域および第2素子形成領域に第1の方向に連続するように延びる能動素子領域を形成する場合に比べて、素子分割前における能動素子領域の第1の方向の長さを小さくすることができる。これにより、第1素子形成領域および第2素子形成領域にそれぞれ形成される第1能動素子領域および第2能動素子領域の歪みが緩和されるので、第1能動素子領域および第2能動素子領域にクラックが発生するのを抑制することができる。この場合、第1の方向に延びる第1能動素子領域の端部および第1の方向に延びる第2能動素子領域の端部が、共に第1分割線上に配置されるように、第1能動素子領域を含む第1半導体素子層および第2能動素子領域を含む第2半導体素子層を形成することによって、第1分割線に沿って、第1半導体素子層および第2半導体素子層が形成された基板を分割すれば、分割面を共振器端面として用いる場合、1回の分割(劈開)で、第1能動素子領域および第2能動素子領域のそれぞれの一方の端部に共振器端面を形成することができる。これにより、第1能動素子領域と第2能動素子領域とが第1の方向に連続しないように第1半導体素子層および第2半導体素子層を形成したとしても、製造工程が増加することがない。また、第1素子形成領域と第2素子形成領域とを第1分割線に沿って第1の方向に互いに接するように構成することにより、第1素子形成領域と第2素子形成領域との間に無駄な領域が存在しないので、基板を効率的に利用することができる。

上記一の局面による半導体素子の製造方法において、好ましくは、第1半導体素子層および第2半導体素子層を形成する工程は、第1半導体素子層に対して第2の方向にずれるように、第2半導体素子層を形成する工程を含む。このように構成すれば、容易に、第1の方向に延びる第1能動素子領域および第2能動素子領域が第1の方向に連続しないように、第1半導体素子層と第2半導体素子層とを形成することができる。

上記一の局面による半導体素子の製造方法において、好ましくは、第1半導体素子層および第2半導体素子層を形成する工程に先立って、基板上に、第1半導体素子層および第2半導体素子層を形成する領域に開口部を有する選択成長マスクを形成する工程をさらに備える。このように構成すれば、選択成長マスク上には半導体素子層が形成されないので、容易に、第1能動素子領域と第2能動素子領域とが第1の方向に連続しないように、第1半導体素子層と第2半導体素子層とを基板上に形成することができる。

上記一の局面による半導体素子の製造方法において、好ましくは、基板上の第1の方向に延びる第2分割線に沿って第1素子形成領域に接する第3素子形成領域に、第1半導体素子層と第2の方向に連続しないように、第1の方向に延びる第3能動素子領域を含む第3半導体素子層を形成する工程を含む。このように構成すれば、基板上の第1素子形成領域および第3素子形成領域に、第2の方向に連続するように半導体素子層を形成する場合に比べて、素子分割前における半導体素子層の第2の方向の長さを小さくすることができる。これにより、第1素子形成領域および第3素子形成領域にそれぞれ形成される第1能動素子領域および第3能動素子領域の歪みが緩和されるので、第1能動素子領域および第3能動素子領域にクラックが発生するのを抑制することができる。

上記一の局面による半導体素子の製造方法において、好ましくは、基板の第1半導体素子層および第2半導体素子層を形成する領域以外の領域を所定の深さまでエッチングすることにより、基板に段差部を形成する工程をさらに備える。このように構成すれば、基板上に第1半導体素子層および第2半導体素子層を形成する際に、基板の段差部に位置する第1半導体素子層および第2半導体素子層が連続しないかまたは厚みが薄くなるので、段差部に位置する第1半導体素子層および第2半導体素子層に歪みを集中させることができる。これにより、第1半導体素子層および第2半導体素子層の段差部にクラックが発生しやすくなる一方、第1半導体素子層および第2半導体素子層の段差部以外の領域には、クラックが発生しにくくなるので、第1能動素子領域および第2能動素子領域にクラックが発生するのをより抑制することができる。

この場合、好ましくは、第1半導体素子層および第2半導体素子層を形成する工程は、段差部の側面上に、段差部の上部および下部に形成される第1半導体素子層および第2半導体素子層の厚みよりも小さい厚みを有する第1半導体素子層および第2半導体素子層を形成する工程を含む。このように構成すれば、基板上に第1半導体素子層および第2半導体素子層を形成する際に、基板の段差部に位置する厚みの小さい第1半導体素子層および第2半導体素子層に容易に歪みを集中させることができる。

上記一の局面による半導体素子の製造方法において、好ましくは、第1能動素子領域および第2能動素子領域は、半導体レーザ素子のリッジ部を含む。このように構成すれば、半導体レーザ素子において、製造工程が増加するのを抑制しながら、リッジ部にクラックが発生するのを抑制することができる。

なお、上記一の局面による半導体素子の製造方法において、第1半導体素子層および第2半導体素子層を形成する工程は、第1能動素子領域の第1の方向への延長線上に位置する第2素子形成領域上の部分において、第1半導体素子層が形成されていないかまたは第1半導体素子層の厚みが小さくなるように、第1半導体素子層を結晶成長する工程を含んでいてもよい。このように構成すれば、容易に、第1の方向に延びる第1能動素子領域が第1の方向に連続しないように、第1半導体素子層を形成することができる。

また、上記一の局面による半導体素子の製造方法において、第1半導体素子層および第2半導体素子層を形成する工程は、第1半導体素子層および第2半導体素子層が不連続となるように結晶成長する工程を含んでいてもよい。このように構成すれば、容易に、第1の方向に延びる第1能動素子領域が第1の方向に連続しないように、第1半導体素子層を形成することができる。

以下、本発明の実施形態を図面に基づいて説明する。

(第1実施形態)

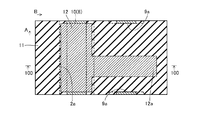

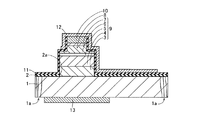

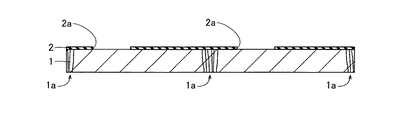

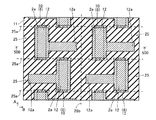

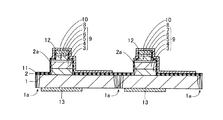

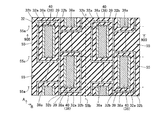

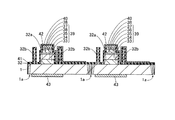

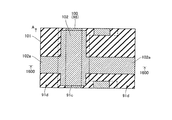

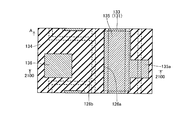

図1は、本発明の第1実施形態による窒化物系半導体レーザ素子の構造を示した平面図である。図2は、図1の100−100線に沿った断面図である。図3は、図2に示した第1実施形態による窒化物系半導体レーザ素子の発光層の詳細を示した拡大断面図である。まず、図1〜図3を参照して、第1実施形態による窒化物系半導体レーザ素子の構造について説明する。

第1実施形態による窒化物系半導体レーザ素子では、図2に示すように、約100μmの厚みを有するとともに、約5×1018cm−3のキャリア濃度を有する酸素がドープされたn型GaN基板1上に、開口部2aを有するとともに、約200nmの厚みを有するSiN膜からなる選択成長マスク2が形成されている。このn型GaN基板1は、ウルツ鉱型構造を有するとともに、(0001)面の表面を有する。また、n型GaN基板1の両端部の近傍の選択成長マスク2によって覆われた領域には、転位の集中している領域1aが形成されている。

また、n型GaN基板1上の開口部2aに対応する領域には、約100nmの厚みを有するとともに、約5×1018cm−3のドーピング量を有するSiがドープされたn型GaNからなるn型層3が形成されている。n型層3上には、約400nmの厚みを有するとともに、約5×1018cm−3のドーピング量および約5×1018cm−3のキャリア濃度を有するSiがドープされたn型Al0.05Ga0.95Nからなるn型クラッド層4が形成されている。

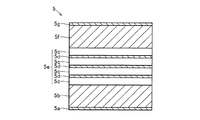

n型クラッド層4上には、発光層5が形成されている。この発光層5は、図3に示すように、n型クラッド層4に近い側から順に、n型キャリアブロック層5aと、n型光ガイド層5bと、多重量子井戸(MQW:Multiple Quantum Well)活性層5eと、p型光ガイド層5fと、p型キャップ層5gとから構成されている。n型キャリアブロック層5aは、約5nmの厚みを有するとともに、約5×1018cm−3のドーピング量および約5×1018cm−3のキャリア濃度を有するSiがドープされたn型Al0.1Ga0.9Nからなる。n型光ガイド層5bは、約100nmの厚みを有するとともに、約5×1018cm−3のドーピング量および約5×1018cm−3のキャリア濃度を有するSiがドープされたn型GaNからなる。また、MQW活性層5eは、約20nmの厚みを有するアンドープIn0.05Ga0.95Nからなる4層の障壁層5cと、約3nmの厚みを有するアンドープIn0.15Ga0.85Nからなる3層の井戸層5dとが交互に積層されている。また、p型光ガイド層5fは、約100nmの厚みを有するとともに、約4×1019cm−3のドーピング量および約5×1017cm−3のキャリア濃度を有するMgがドープされたp型GaNからなる。p型キャップ層5gは、約20nmの厚みを有するとともに、約4×1019cm−3のドーピング量および約5×1017cm−3のキャリア濃度を有するMgがドープされたp型Al0.1Ga0.9Nからなる。

また、図2に示すように、発光層5上には、平坦部とその平坦部から上方に突出するように形成された凸部とを有するとともに、約4×1019cm−3のドーピング量および約5×1017cm−3のキャリア濃度を有するMgがドープされたp型Al0.05Ga0.95Nからなるp型クラッド層6が形成されている。このp型クラッド層6の凸部は、約1.5μmの幅と約300nmの高さとを有する。また、p型クラッド層6の凸部以外の平坦部は、約100nmの厚みを有する。p型クラッド層6の凸部上には、約10nmの厚みを有するとともに、約4×1019cm−3のドーピング量および約5×1017cm−3のキャリア濃度を有するMgがドープされたp型GaNからなるp型コンタクト層7が形成されている。このp型コンタクト層7とp型クラッド層6の凸部とによって、共振器方向(図1のA方向)に延びるストライプ状(細長状)のリッジ部8が構成されている。

ここで、第1実施形態では、n型層3、n型クラッド層4、発光層5、p型クラッド層6およびp型コンタクト層7によって、半導体素子層9が構成されている。

リッジ部8を構成するp型コンタクト層7上には、下層から上層に向かって、約5nmの厚みを有するPt層と、約100nmの厚みを有するPd層と、約150nmの厚みを有するAu層とからなるp側オーミック電極10が形成されている。また、p側オーミック電極10の上面以外の領域を覆うように、約250nmの厚みを有するSiN膜からなる絶縁膜11が形成されている。絶縁膜11上の所定領域には、p側オーミック電極10の上面に接触するように、下層から上層に向かって、約100nmの厚みを有するTi層と、約100nmの厚みを有するPd層と、約3μmの厚みを有するAu層とからなるp側パッド電極12が形成されている。このp側パッド電極12は、図1に示すように、平面的に見て、矩形状に突出した端部12aを有する。

また、図2に示すように、n型GaN基板1の裏面上には、n型GaN基板1の裏面の転位の集中している領域1a以外の領域に接触するように、n側電極13が形成されている。このn側電極13は、n型GaN基板1の裏面に近い方から順に、約10nmの厚みを有するAl層と、約20nmの厚みを有するPt層と、約300nmの厚みを有するAu層とからなる。

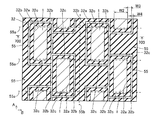

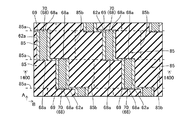

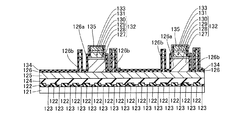

図4〜図19は、図1および図2に示した第1実施形態による窒化物系半導体レーザ素子の製造プロセスを説明するための断面図および平面図である。次に、図1〜図19を参照して、第1実施形態による窒化物系半導体レーザ素子の製造プロセスについて説明する。

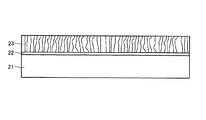

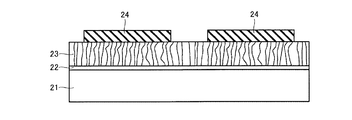

まず、図4〜図7を参照して、n型GaN基板1の形成プロセスについて説明する。具体的には、図4に示すように、MOCVD法を用いて、基板温度を約600℃に保持した状態で、サファイア基板21上に、約20nmの厚みを有するAlGaN層22を成長させる。その後、基板温度を約1100℃に変えて、AlGaN層22上に、約1μmの厚みを有するGaN層23を成長させる。この際、GaN層23の全領域に、縦方向に伝播された転位が、約5×108cm−2以上(たとえば、約5×109cm−2)の密度で形成される。

次に、図5に示すように、プラズマCVD法を用いて、GaN層23上に、約10μmの間隔を隔てて、約390μmの幅と約200nmの厚みとを有するSiNまたはSiO2からなるマスク層24を、約400μmの周期(中心間距離)で形成する。

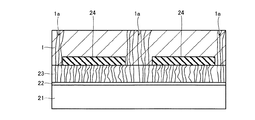

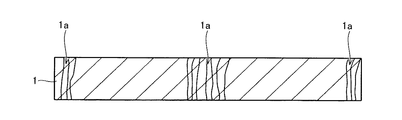

次に、図6に示すように、HVPE(Halide Vapor Phase Epitaxy:ハライド気相成長)法を用いて、基板温度を約1100℃に保持した状態で、マスク層24を選択成長マスクとして、GaN層23上に、約150μmの厚みを有するとともに、約5×1018cm−3のキャリア濃度を有する酸素がドープされたn型GaN基板1を選択横方向成長させる。この際、n型GaN基板1は、マスク層24が形成されていないGaN層23上に選択的に縦方向に成長した後、徐々に横方向に成長する。このため、マスク層24が形成されていないGaN層23上に位置するn型GaN基板1には、約5×108cm−2以上(たとえば、約5×109cm−2)の密度で縦方向に伝播された転位の集中している領域1aが約10μmの幅で形成される。その一方、マスク層24上に位置するn型GaN基板1には、n型GaN基板1が横方向に成長することにより転位が横方向へ曲げられるので、縦方向に伝播された転位が形成されにくく、転位密度は、約5×107cm−2以下(たとえば、約1×106cm−2)である。この後、n型GaN基板1下に位置するサファイア基板21、AlGaN層22、GaN層23およびマスク層24を除去する。このようにして、図7に示すように、約5×1018cm−3のキャリア濃度を有する酸素がドープされたn型GaN基板1を形成する。このn型GaN基板1は、ウルツ鉱型構造を有するとともに、(0001)面の表面を有する。なお、n型GaN基板1は、本発明の「基板」の一例である。

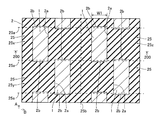

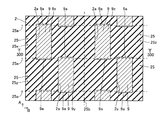

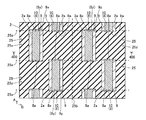

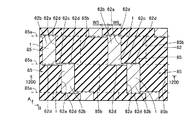

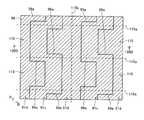

次に、図8および図9に示すように、プラズマCVD法を用いて、n型GaN基板1上に、開口部2aを有するとともに、約200nmの厚みを有するSiN膜からなる選択成長マスク2を形成する。この際、開口部2aを、素子形成領域(劈開線25aと素子分離線25bとに囲まれた領域)25の半導体素子層9(図2参照)を成長させる領域に配置する。なお、素子形成領域25は、本発明の「第1素子形成領域」、「第2素子形成領域」および「第3素子形成領域」の一例である。ここで、各素子形成領域25の位置関係は、仮に素子形成領域25xを「第1素子形成領域」とすれば、素子形成領域25yが「第2素子形成領域」であり、素子形成領域25zが「第3素子形成領域」である。

ここで、第1実施形態では、共振器方向(A方向)に隣接する素子形成領域25の各開口部2aがA方向に連続しないように、選択成長マスク2を形成する。具体的には、A方向に隣接する開口部2aを、一つ置きに共振器方向と直交する方向(B方向)にずらすことにより互い違いに配置する。また、開口部2aのA方向の端部2bが劈開線25aを跨いでA方向に隣接する素子形成領域25に達するように、選択成長マスク2を形成する。また、第1実施形態では、B方向に隣接する素子形成領域25の各開口部2aがB方向に連続しないように、選択成長マスク2を形成する。また、開口部2aのB方向の幅W1(図8参照)は、約10μmに設定する。なお、隣接する劈開線25a間の距離(共振器の長さ)は、約700μmであり、隣接する素子分離線25b間の距離(素子の幅)は、約400μmである。なお、劈開線25aおよび素子分離線25bは、それぞれ、本発明の「第1分割線」および「第2分割線」の一例である。

次に、図10および図11に示すように、MOCVD法を用いて、n型GaN基板1上の開口部2aに対応する領域に、n型層3、n型クラッド層4、発光層5、p型クラッド層6およびp型コンタクト層7を順次成長させる。

具体的には、基板温度を約1100℃の成長温度に保持した状態で、H2およびN2からなるキャリアガスと、NH3およびTMGaからなる原料ガスと、SiH4からなるドーパントガスとを用いて、n型GaN基板1上の開口部2aに対応する領域に、約100nmの厚みを有するとともに、約5×1018cm−3のドーピング量を有するSiがドープされたn型GaNからなるn型層3を成長させる。この後、原料ガスにTMAlをさらに加えて、n型層3上に、約400nmの厚みを有するとともに、約5×1018cm−3のドーピング量および約5×1018cm−3のキャリア濃度を有するSiがドープされたn型Al0.05Ga0.95Nからなるn型クラッド層4を成長させる。

続いて、図3に示したように、n型クラッド層4(図11参照)上に、約5nmの厚みを有するとともに、約5×1018cm−3のドーピング量および約5×1018cm−3のキャリア濃度を有するSiがドープされたn型Al0.1Ga0.9Nからなるn型キャリアブロック層5aを成長させる。

次に、基板温度を約800℃の成長温度に保持した状態で、H2およびN2からなるキャリアガスと、NH3およびTMGaからなる原料ガスと、SiH4からなるドーパントガスとを用いて、n型キャリアブロック層5a上に、約5×1018cm−3のドーピング量および約5×1018cm−3のキャリア濃度を有するSiがドープされたn型GaNからなるn型光ガイド層5bを成長させる。

この後、原料ガスにTMInをさらに加えるとともに、ドーパントガスを用いないで、n型光ガイド層5b上に、約20nmの厚みを有するアンドープIn0.05Ga0.95Nからなる4層の障壁層5cと、約3nmの厚みを有するアンドープIn0.15Ga0.85Nからなる3層の井戸層5dとを交互に成長させることによりMQW活性層5eを形成する。

そして、原料ガスをNH3およびTMGaに変えるとともに、Cp2Mgからなるドーパントガスを用いて、MQW活性層5e上に、約100nmの厚みを有するとともに、約4×1019cm−3のドーピング量および約5×1017cm−3のキャリア濃度を有するMgがドープされたp型GaNからなるp型光ガイド層5fを成長させる。この後、原料ガスにTMAlをさらに加えて、p型光ガイド層5f上に、約20nmの厚みを有するとともに、約4×1019cm−3のドーピング量および約5×1017cm−3のキャリア濃度を有するMgがドープされたp型Al0.1Ga0.9Nからなるp型キャップ層5gを成長させる。これにより、n型キャリアブロック層5a、n型光ガイド層5b、MQW活性層5e、p型光ガイド層5fおよびp型キャップ層5gからなる発光層5が形成される。

次に、図11に示すように、基板温度を約1100℃の成長温度に保持した状態で、H2およびN2からなるキャリアガスと、NH3、TMGaおよびTMAlからなる原料ガスと、Cp2Mgからなるドーパントガスとを用いて、発光層5上に、約400nmの厚みを有するとともに、約4×1019cm−3のドーピング量および約5×1017cm−3のキャリア濃度を有するMgがドープされたp型Al0.05Ga0.95Nからなるp型クラッド層6を成長させる。この後、原料ガスをNH3およびTMGaに変えて、p型クラッド層6上に、約10nmの厚みを有するとともに、約4×1019cm−3のドーピング量および約5×1017cm−3のキャリア濃度を有するMgがドープされたp型GaNからなるp型コンタクト層7を成長させる。これにより、n型層3、n型クラッド層4、発光層5、p型クラッド層6およびp型コンタクト層7からなる半導体素子層9が形成される。なお、半導体素子層9は、本発明の「第1半導体素子層」、「第2半導体素子層」および「第3半導体素子層」の一例である。ここで、各半導体素子層9の位置関係は、仮に半導体素子層9xを「第1半導体素子層」とすれば、半導体素子層9yが「第2半導体素子層」であり、半導体素子層9zが「第3半導体素子層」である。

この際、第1実施形態では、図10に示すように、半導体素子層9は、選択成長マスク2上には形成されない。すなわち、半導体素子層9xと9yとがA方向に連続しないように形成される。同時に、半導体素子層9xのA方向の端部9aが劈開線25aを跨いでA方向に隣接する素子形成領域25yに達するように形成されるとともに、半導体素子層9xのA方向への延長線上に位置する素子形成領域25yに半導体素子層の形成されない部分ができる。また、共振器方向と直交する方向(B方向)に隣接する素子形成領域25xと25zとに形成される半導体素子層9xと9zとがB方向に連続しないように形成されるとともに、半導体素子層9xと9zとの間に半導体素子層の形成されない部分ができる。

この後、窒素ガス雰囲気中で、約800℃の温度条件下でアニール処理する。

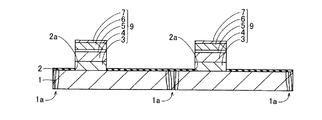

次に、図12に示すように、真空蒸着法を用いて、p型コンタクト層7上に、下層から上層に向かって、約5nmの厚みを有するPt層と、約100nmの厚みを有するPd層と、約150nmの厚みを有するAu層とからなるp側オーミック電極10を形成した後、p側オーミック電極10上の所定領域に、約250nmの厚みを有するとともに、約1.5μmの幅を有するストライプ状(細長状)のNi層26を形成する。

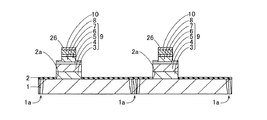

次に、図13に示すように、ドライエッチング技術を用いて、Ni層26をマスクとして、p側オーミック電極10をエッチングした後、p型コンタクト層7およびp型クラッド層6の上面から約300nmの厚み分をエッチングする。これにより、p型コンタクト層7とp型クラッド層6の凸部とから構成されるとともに、共振器方向に延びるストライプ状(細長状)のリッジ部8が形成される。なお、リッジ部8は、本発明の「第1能動素子領域」、「第2能動素子領域」および「第3能動素子領域」の一例である。ここで、リッジ部8は、仮にリッジ部8xを「第1能動素子領域」とすれば、リッジ部8yが「第2能動素子領域」であり、リッジ部8zが「第3能動素子領域」である。この後、Ni層26を除去することによって、図14および図15に示す状態にする。

ここで、第1実施形態では、図14および図15に示すように、A方向に隣接する素子形成領域25の各半導体素子層9のリッジ部8は、A方向に連続しないように形成される。また、各半導体素子層9のリッジ部8の端部8aは、劈開線25aを跨いでA方向に隣接する素子形成領域25に達するように形成される。

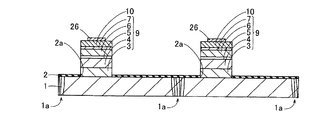

次に、図16に示すように、プラズマCVD法を用いて、全面を覆うように、約250nmの厚みを有するSiN膜(図示せず)を形成した後、p側オーミック電極10の上面上に位置するSiN膜を除去することによって、SiN膜からなる絶縁膜11を形成する。

次に、図17および図18に示すように、真空蒸着法を用いて、絶縁膜11上の所定領域に、p側オーミック電極10の上面に接触するように、下層から上層に向かって、約100nmの厚みを有するTi層と、約100nmの厚みを有するPd層と、約3μmの厚みを有するAu層とからなるp側パッド電極12を形成する。この際、図17に示すように、平面的に見て矩形状に突出した端部12aを有するように、p側パッド電極12を形成する。この後、図18に示すように、n型GaN基板1の厚みが約100μmになるように、n型GaN基板1の裏面を研磨した後、真空蒸着法を用いて、n型GaN基板1の裏面上に、n型GaN基板1の裏面の転位の集中している領域1a以外の領域に接触するように、n側電極13を形成する。なお、n側電極13を形成する際には、n型GaN基板1に近い方から順に、約10nmの厚みを有するAl層と、約20nmの厚みを有するPt層と、約300nmの厚みを有するAu層とを形成する。

次に、図17に示した劈開線25aに沿って、共振器方向(A方向)に隣接する素子形成領域25を分割する。これにより、図19に示すように、分割された隣接する素子形成領域25のそれぞれの劈開面に、共振器端面9bが形成される。この後、素子分離線25bに沿って素子を分離することによって、図1および図2に示した第1実施形態による窒化物系半導体レーザ素子が形成される。ここで、半導体レーザ素子には、A方向に隣接している素子形成領域25から劈開線25a(図10参照)を跨いで形成された半導体素子層9の端部9aが、リッジ部8に対してB方向にずれるように形成されている。

第1実施形態の製造プロセスでは、上記のように、素子分割前の共振器方向(A方向)に隣接する素子形成領域25に、各々のリッジ部8がA方向に連続しないように半導体素子層9を形成することによって、A方向に隣接する素子形成領域25にA方向に連続するリッジ部8を含む半導体素子層9を形成する場合に比べて、素子分割前におけるリッジ部8を含む半導体素子層9のA方向の長さを小さくすることができる。これにより、A方向に隣接する素子形成領域25にそれぞれ形成される半導体素子層9のリッジ部8の歪みが緩和されるので、リッジ部8にクラックが発生するのを抑制することができる。この場合、共振器方向(A方向)に隣接する素子形成領域25に形成される各半導体素子層9の端部9aを、共に劈開線25aを跨いでA方向に隣接する素子形成領域25に達するように配置することによって、劈開線25aに沿ってA方向に隣接する素子形成領域25を劈開すれば、1回の劈開で、A方向に隣接する素子形成領域25のそれぞれの半導体素子層9に一方の共振器端面を形成することができる。これにより、A方向に隣接する素子形成領域25に形成される半導体素子層9がA方向に連続していなかったとしても、製造工程が増加することがない。また、A方向に隣接する素子形成領域25を劈開線25aに沿って互いに接するように構成することにより、素子形成領域25間に無駄な領域が存在しないので、n型GaN基板1を効率的に利用することができる。

また、第1実施形態の製造プロセスでは、素子分割前の共振器方向と直交する方向(B方向)に隣接する素子形成領域25に、B方向に連続しないように半導体素子層9を形成することによって、B方向に隣接する素子形成領域25にB方向に連続するように半導体素子層9を形成する場合に比べて、素子分割前における半導体素子層9のB方向の長さを小さくすることができる。これにより、B方向に隣接する素子形成領域25にそれぞれ形成される半導体素子層9の歪みが緩和されるので、これによっても、半導体素子層9のリッジ部8にクラックが発生するのを抑制することができる。

また、第1実施形態の製造プロセスでは、n型GaN基板1上に、半導体素子層9を成長させる領域に開口部2aを有する選択成長マスク2を形成するとともに、共振器方向(A方向)に隣接する開口部2aを、一つ置きに共振器方向と直交する方向(B方向)にずらすことにより互い違いに配置することによって、選択成長マスク2上には半導体素子層9が形成されないので、容易に、A方向に隣接する素子形成領域25に形成される半導体素子層9のリッジ部8がA方向に連続しないように、半導体素子層9を形成することができる。

(第2実施形態)

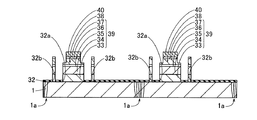

図20は、本発明の第2実施形態による窒化物系半導体レーザ素子の構造を示した平面図であり、図21は、図20の600−600線に沿った断面図である。次に、図20および図21を参照して、第2実施形態による窒化物系半導体レーザ素子の構造について説明する。

第2実施形態による窒化物系半導体レーザ素子では、図21に示すように、上記第1実施形態と同様のn型GaN基板1上に、開口部32aおよび32bを有するとともに、約200nmの厚みを有するSiN膜からなる選択成長マスク32が形成されている。この選択成長マスク32によって、n型GaN基板1の転位の集中している領域1aが覆われている。

また、n型GaN基板1上の開口部32aおよび32bに対応する領域には、n型層33、n型クラッド層34および発光層35が順次形成されている。発光層35上には、平坦部とその平坦部から上方に突出するように形成された凸部とを有するp型クラッド層36が形成されているとともに、p型クラッド層36の凸部上には、p型コンタクト層37が形成されている。このp型コンタクト層37とp型クラッド層36の凸部とによって、共振器方向(図20のA方向)に延びるストライプ状(細長状)のリッジ部38が構成されている。なお、n型層33、n型クラッド層34、発光層35、p型クラッド層36およびp型コンタクト層37は、それぞれ、上記第1実施形態のn型層3、n型クラッド層4、発光層5、p型クラッド層6およびp型コンタクト層7と同様の組成および厚みを有する。

ここで、第2実施形態では、n型層33、n型クラッド層34、発光層35、p型クラッド層36およびp型コンタクト層37によって、半導体素子層39が構成されている。

リッジ部38を構成するp型コンタクト層37上には、上記第1実施形態のp側オーミック電極10と同様の組成および厚みを有するp側オーミック電極40が形成されている。また、p側オーミック電極40の上面以外の領域を覆うように、上記第1実施形態の絶縁膜11と同様の組成および厚みを有する絶縁膜41が形成されている。絶縁膜41上の所定領域には、p側オーミック電極40の上面に接触するように、上記第1実施形態のp側パッド電極12と同様の組成および厚みを有するp側パッド電極42が形成されている。このp側パッド電極42は、図20に示すように、平面的に見て、矩形状に突出した端部42aを有する。

また、図21に示すように、n型GaN基板1の裏面上には、n型GaN基板1の裏面の転位の集中している領域1a以外の領域に接触するように、上記第1実施形態のn側電極13と同様の組成および厚みを有するn側電極43が形成されている。

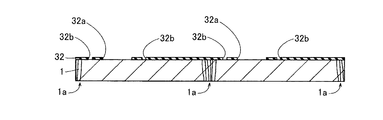

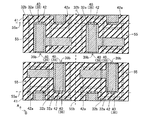

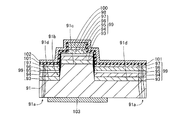

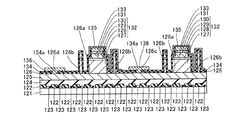

図22〜図31は、図20および図21に示した第2実施形態による窒化物系半導体レーザ素子の製造プロセスを説明するための平面図および断面図である。図20〜図31を参照して、この第2実施形態の製造プロセスでは、上記第1実施形態と異なり、n型GaN基板上に形成する選択成長マスクにおいて、半導体素子層を成長させる領域に形成された開口部を囲むように、さらに別の開口部を形成する場合について説明する。

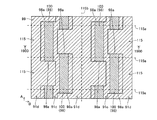

この第2実施形態の製造プロセスでは、まず、図22および図23に示すように、プラズマCVD法を用いて、n型GaN基板1上に、開口部32aおよび32bを有するとともに、約200nmの厚みを有するSiN膜からなる選択成長マスク32を形成する。この際、開口部32aを、素子形成領域(劈開線55aと素子分離線55bとに囲まれた領域)55の半導体素子層39(図21参照)を成長させる領域に配置する。なお、素子形成領域55は、本発明の「第1素子形成領域」、「第2素子形成領域」および「第3素子形成領域」の一例である。

ここで、第2実施形態では、共振器方向(A方向)に隣接する素子形成領域55の各開口部32aがA方向に連続しないように、選択成長マスク32を形成する。具体的には、A方向に隣接する開口部32aを、一つ置きに共振器方向と直交する方向(B方向)にずらすことにより互い違いに配置する。また、開口部32aのA方向の端部32cが劈開線55aを跨いでA方向に隣接する素子形成領域55に達するように、選択成長マスク32を形成する。また、第2実施形態では、B方向に隣接する素子形成領域55の各開口部32aがB方向に連続しないように、選択成長マスク32を形成する。また、開口部32aのB方向の幅W2(図22参照)は、約10μmに設定する。また、開口部32bを、開口部32aから約2μmの間隔W3(図22参照)を隔てて開口部32aを囲むように配置する。また、開口部32bのA方向およびB方向の幅W4(図22参照)は、約5μmに設定する。なお、隣接する劈開線55a間の距離(共振器の長さ)は、約700μmであり、隣接する素子分離線55b間の距離(素子の幅)は、約400μmである。なお、劈開線55aおよび素子分離線55bは、それぞれ、本発明の「第1分割線」および「第2分割線」の一例である。

次に、図24および図25に示すように、MOCVD法を用いて、n型GaN基板1上の開口部32aおよび32bに対応する領域に、上記第1実施形態のn型層3、n型クラッド層4、発光層5、p型クラッド層6およびp型コンタクト層7と同様の組成および厚みをそれぞれ有するn型層33、n型クラッド層34、発光層35、p型クラッド層36およびp型コンタクト層37を順次成長させる。これにより、n型層33、n型クラッド層34、発光層35、p型クラッド層36およびp型コンタクト層37からなる半導体素子層39が形成される。なお、半導体素子層39は、本発明の「第1半導体素子層」、「第2半導体素子層」および「第3半導体素子層」の一例である。

この際、第2実施形態では、図24に示すように、半導体素子層39は、選択成長マスク32上には形成されない。すなわち、共振器方向(A方向)に隣接する素子形成領域55に形成される各半導体素子層39がA方向に連続しないように形成されるとともに、共振器方向と直交する方向(B方向)に隣接する素子形成領域55に形成される各半導体素子層39がB方向に連続しないように形成される。また、半導体素子層39のA方向の端部39aが劈開線55aを跨いでA方向に隣接する素子形成領域55に達するように形成される。

この後、窒素ガス雰囲気中で、約800℃の温度条件下でアニール処理する。

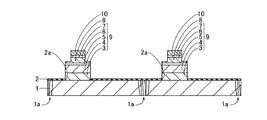

次に、図26および図27に示すように、図12〜図15に示した第1実施形態と同様のプロセスを用いて、p側オーミック電極40を形成した後、共振器方向(A方向)に延びるストライプ状(細長状)のリッジ部38を形成する。なお、リッジ部38は、本発明の「第1能動素子領域」、「第2能動素子領域」および「第3能動素子領域」の一例である。

ここで、第2実施形態では、A方向に隣接する素子形成領域55の各半導体素子層39のリッジ部38は、A方向に連続しないように形成される。また、各半導体素子層39のリッジ部38の端部38aは、劈開線55aを跨いでA方向に隣接する素子形成領域55に達するように形成される。

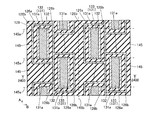

次に、図28に示すように、図16に示した第1実施形態と同様のプロセスを用いて、p側オーミック電極40の上面以外の領域を覆うように、上記第1実施形態の絶縁膜11と同様の組成および厚みを有する絶縁膜41を形成する。

次に、図29および図30に示すように、真空蒸着法を用いて、絶縁膜41上の所定領域に、p側オーミック電極40の上面に接触するように、上記第1実施形態のp側パッド電極12と同様の組成および厚みを有するp側パッド電極42を形成する。この際、図29に示すように、平面的に見て矩形状に突出した端部42aを有するように、p側パッド電極42を形成する。この後、図30に示すように、真空蒸着法を用いて、n型GaN基板1の裏面上に、n型GaN基板1の裏面の転位の集中している領域1a以外の領域に接触するように、上記第1実施形態のn側電極13と同様の組成および厚みを有するn側電極43を形成する。

次に、図29に示した劈開線55aに沿って、共振器方向(A方向)に隣接する素子形成領域55を分割する。これにより、図31に示すように、分割された隣接する素子形成領域55のそれぞれの劈開面に、共振器端面39bが形成される。この後、素子分離線55bに沿って素子を分離することによって、図20および図21に示した第2実施形態による窒化物系半導体レーザ素子が形成される。

第2実施形態の製造プロセスでは、上記のように、素子分割前の共振器方向(A方向)に隣接する素子形成領域55に、各々のリッジ部38がA方向に連続しないように半導体素子層39を形成することによって、上記第1実施形態と同様、素子分割前におけるリッジ部38を含む半導体素子層39のA方向の長さが小さくなることにより半導体素子層39のリッジ部38の歪みが緩和されるので、リッジ部38にクラックが発生するのを抑制することができる。また、共振器方向(A方向)に隣接する素子形成領域55に形成される各半導体素子層39の端部39aを、共に劈開線55aを跨いでA方向に隣接する素子形成領域55に達するように配置することによって、上記第1実施形態と同様、1回の劈開で、A方向に隣接する素子形成領域55のそれぞれの半導体素子層39に一方の共振器端面を形成することができるので、製造工程が増加することがない。

また、第2実施形態の製造プロセスでは、選択成長マスク32を形成する際に、リッジ部38を含む半導体素子層39を成長させる領域に配置する開口部32aを囲むように、さらに別の開口部32bを設けることによって、半導体素子層39に隣接する選択成長マスク32の表面積が小さくなるので、半導体素子層39を成長させる際に、半導体素子層39に隣接する選択成長マスク32の表面全体に達する原料ガスの総量が少なくなる。これにより、半導体素子層39に隣接する選択成長マスク32の表面から成長中の半導体素子層39の表面へ表面拡散する原料ガスやその分解物の量が少なくなる。これにより、選択成長マスク32の近傍に位置する成長中の半導体素子層39の表面に供給される原料ガスやその分解物の量の増加を低減できるので、選択成長マスク32の近傍に位置する半導体素子層39の厚みが大きくなるのを抑制することができる。その結果、半導体素子層39の厚みが、選択成長マスク32の近傍の位置と選択成長マスク32から遠い位置とで不均一になるのを抑制することができる。

なお、第2実施形態のその他の効果は、上記第1実施形態と同様である。

(第3実施形態)

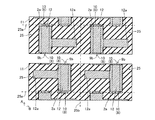

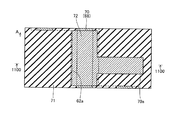

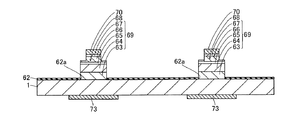

図32は,本発明の第3実施形態による窒化物系半導体レーザ素子の構造を示した平面図であり、図33は、図32の1100−1100線に沿った断面図である。次に、図32および図33を参照して、第3実施形態による窒化物系半導体レーザ素子の構造について説明する。

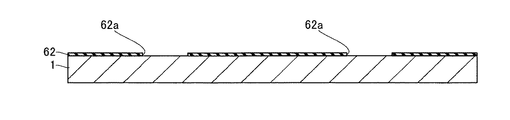

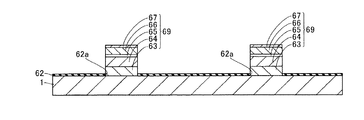

第3実施形態による窒化物系半導体レーザ素子では、図33に示すように、上記第1実施形態と同様のn型GaN基板1上に、開口部62aを有するとともに、約200nmの厚みを有するSiN膜からなる選択成長マスク62が形成されている。

また、n型GaN基板1上の開口部62aに対応する領域には、n型層63、n型クラッド層64および発光層65が順次形成されている。発光層65上には、平坦部とその平坦部から上方に突出するように形成された凸部とを有するp型クラッド層66が形成されているとともに、p型クラッド層66の凸部上には、p型コンタクト層67が形成されている。このp型コンタクト層67とp型クラッド層66の凸部とによって、共振器方向(図32のA方向)に延びるストライプ状(細長状)のリッジ部68が構成されている。なお、n型層63、n型クラッド層64、発光層65、p型クラッド層66およびp型コンタクト層67は、それぞれ、上記第1実施形態のn型層3、n型クラッド層4、発光層5、p型クラッド層6およびp型コンタクト層7と同様の組成および厚みを有する。

ここで、第3実施形態では、n型層63、n型クラッド層64、発光層65、p型クラッド層66およびp型コンタクト層67によって、半導体素子層69が構成されている。

リッジ部68を構成するp型コンタクト層67上には、上記第1実施形態のp側オーミック電極10と同様の組成および厚みを有するp側オーミック電極70が形成されている。また、p側オーミック電極70の上面以外の領域を覆うように、上記第1実施形態の絶縁膜11と同様の組成および厚みを有する絶縁膜71が形成されている。絶縁膜71上の所定領域には、p側オーミック電極70の上面に接触するように、上記第1実施形態のp側パッド電極12と同様の組成および厚みを有するp側パッド電極72が形成されている。このp側パッド電極72は、図32に示すように、平面的に見て、矩形状に突出した端部72aを有する。

また、図33に示すように、n型GaN基板1の裏面上には、上記第1実施形態のn側電極13と同様の組成および厚みを有するn側電極73が形成されている。

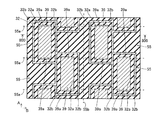

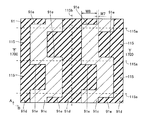

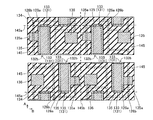

図34〜図43は、図32および図33に示した第3実施形態による窒化物系半導体レーザ素子の製造プロセスを説明するための平面図および断面図である。図32〜図43を参照して、この第3実施形態による製造プロセスでは、上記第1および第2実施形態と異なり、n型GaN基板上に形成する選択成長マスクにおいて、共振器方向(A方向)に隣接する素子形成領域に形成された各開口部が、共振器方向と直交する方向(B方向)にずらされた状態で、かつ、連続するように配置される場合について説明する。

この第3実施形態の製造プロセスでは、まず、図34および図35に示すように、プラズマCVD法を用いて、n型GaN基板1上に、開口部62aを有するとともに、約200nmの厚みを有するSiN膜からなる選択成長マスク62を形成する。この際、開口部62aを、素子形成領域(劈開線85aと素子分離線85bとに囲まれた領域)85の半導体素子層69(図33参照)を成長させる領域に配置する。また、開口部62aが、リッジ部形成領域62bとリッジ部不形成領域62cとを含むように、選択成長マスク62を形成する。なお、素子形成領域85は、本発明の「第1素子形成領域」、「第2素子形成領域」および「第3素子形成領域」の一例である。

ここで、第3実施形態では、共振器方向(A方向)に隣接する素子形成領域85の開口部62aの各リッジ部形成領域62bがA方向に連続しないように、選択成長マスク62を形成する。具体的には、A方向に隣接する開口部62aのリッジ部形成領域62bを、共振器方向と直交する方向(B方向)にずらすように配置する。また、開口部62aのリッジ部形成領域62bのA方向の端部62dが劈開線85aを跨いでA方向に隣接する素子形成領域85に達するように、選択成長マスク62を形成する。また、A方向に隣接する素子形成領域85にそれぞれ配置された開口部62aのリッジ部形成領域62bが、劈開線85a上においてA方向の小さい開口幅を有するリッジ部不形成領域62cにより接続されるように、選択成長マスク62を形成する。なお、この開口部62aのリッジ部不形成領域62cのB方向の幅W5(図34参照)は、約5μmに設定する。また、第3実施形態では、B方向に隣接する素子形成領域85の開口部62aの各リッジ部形成領域62bがB方向に連続しないように、選択成長マスク62を形成する。また、開口部62aのリッジ部形成領域62bのB方向の幅W6(図34参照)は、約100μmに設定する。なお、隣接する劈開線85a間の距離(共振器の長さ)は、約600μmであり、隣接する素子分離線85b間の距離(素子の幅)は、約400μmである。なお、劈開線85aおよび素子分離線85bは、それぞれ、本発明の「第1分割線」および「第2分割線」の一例である。

次に、図36および図37に示すように、MOCVD法を用いて、n型GaN基板1上の開口部62aに対応する領域に、上記第1実施形態のn型層3、n型クラッド層4、発光層5、p型クラッド層6およびp型コンタクト層7と同様の組成および厚みをそれぞれ有するn型層63、n型クラッド層64、発光層65、p型クラッド層66およびp型コンタクト層67を順次成長させる。これにより、n型層63、n型クラッド層64、発光層65、p型クラッド層66およびp型コンタクト層67からなる半導体素子層69が形成される。なお、半導体素子層69は、本発明の「第1半導体素子層」、「第2半導体素子層」および「第3半導体素子層」の一例である。

この際、第3実施形態では、図36に示すように、半導体素子層69は、選択成長マスク62上には形成されない。すなわち、この第3実施形態では、選択成長マスク62の開口部62aのリッジ部形成領域62bおよびリッジ部不形成領域62cに、半導体素子層69が形成される。この場合、リッジ部不形成領域62cに形成された半導体素子層69により、共振器方向(A方向)に隣接する素子形成領域85に形成された各半導体素子層69が接続されている。ただし、この第3実施形態では、半導体素子層69は、共振器方向(A方向)に隣接する素子形成領域85の各リッジ部68(図33参照)となる領域がA方向に連続しないように形成される。また、共振器方向と直交する方向(B方向)に隣接する素子形成領域85に形成される半導体素子層69がB方向に連続しないように形成される。また、半導体素子層69のリッジ部68となる領域のA方向の端部69aが、劈開線85aを跨いでA方向に隣接する素子形成領域85に達するように形成される。

この後、窒素ガス雰囲気中で、約800℃の温度条件下でアニール処理する。

次に、図38および図39に示すように、図12〜図15に示した第1実施形態と同様のプロセスを用いて、p側オーミック電極70を形成した後、共振器方向(A方向)に延びるストライプ状(細長状)のリッジ部68を形成する。なお、リッジ部68は、本発明の「第1能動素子領域」、「第2能動素子領域」および「第3能動素子領域」の一例である。

ここで、第3実施形態では、A方向に隣接する素子形成領域85の各半導体素子層69のリッジ部68は、A方向に連続しないように形成される。すなわち、この第3実施形態では、リッジ部不形成領域62cにはリッジ部68は形成されないので、A方向に隣接する素子形成領域85の各半導体素子層69のリッジ部68同士が連続することはない。また、各半導体素子層69のリッジ部68の端部68aは、劈開線85aを跨いでA方向に隣接する素子形成領域85に達するように形成される。

次に、図40に示すように、図16に示した第1実施形態と同様のプロセスを用いて、p側オーミック電極70の上面以外の領域を覆うように、上記第1実施形態の絶縁膜11と同様の組成および厚みを有する絶縁膜71を形成する。

次に、図41および図42に示すように、真空蒸着法を用いて、絶縁膜71上の所定領域に、p側オーミック電極70の上面に接触するように、上記第1実施形態のp側パッド電極12と同様の組成および厚みを有するp側パッド電極72を形成する。この際、図41に示すように、平面的に見て矩形状に突出した端部72aを有するように、p側パッド電極72を形成する。この後、図42に示すように、真空蒸着法を用いて、n型GaN基板1の裏面上に、上記第1実施形態のn側電極13と同様の組成および厚みを有するn側電極73を形成する。

次に、図41に示した劈開線85aに沿って、共振器方向(A方向)に隣接する素子形成領域85を分割する。これにより、図43に示すように、分割された隣接する素子形成領域85のそれぞれの劈開面に、共振器端面69bが形成される。この後、素子分離線85bに沿って素子を分離することによって、図32および図33に示した第3実施形態による窒化物系半導体レーザ素子が形成される。

第3実施形態の製造プロセスでは、上記のように、リッジ部形成領域62bとリッジ部不形成領域62cとを含む開口部62aを有する選択成長マスク62を素子形成領域85に形成するとともに、共振器方向(A方向)に隣接する素子形成領域85の開口部62aの各リッジ部形成領域62bがA方向に連続しないように、選択成長マスク62の開口部62aを形成することによって、A方向に隣接する素子形成領域85の各リッジ部形成領域62bに、各々のリッジ部68がA方向に連続しないように半導体素子層69を形成することができる。これにより、上記第1実施形態と同様、素子分割前における半導体素子層69のリッジ部68のA方向の長さが小さくなることにより半導体素子層69のリッジ部68の歪みが緩和されるので、リッジ部68にクラックが発生するのを抑制することができる。また、開口部62aのリッジ部形成領域62bのA方向の端部62dを、劈開線85aを跨いでA方向に隣接する素子形成領域85に達するように配置することによって、A方向に隣接する素子形成領域85に形成される各半導体素子層69の端部69aが、共に劈開線85aを跨いでA方向に隣接する素子形成領域85に達するように配置される。これにより、上記第1実施形態と同様、1回の劈開で、A方向に隣接する素子形成領域85のそれぞれの半導体素子層69に一方の共振器端面を形成することができるので、製造工程が増加することがない。

なお、第3実施形態のその他の効果は、上記第1実施形態と同様である。

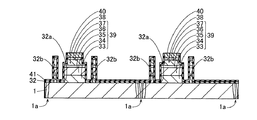

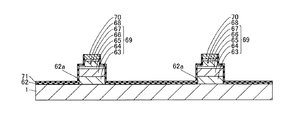

(第4実施形態)

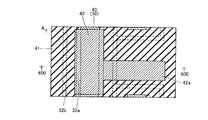

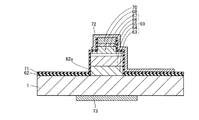

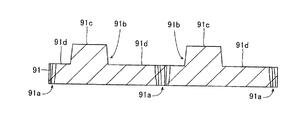

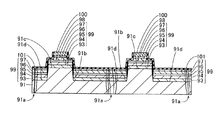

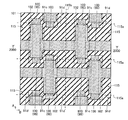

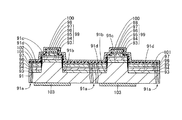

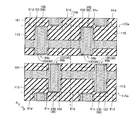

図44は、本発明の第4実施形態による窒化物系半導体レーザ素子の構造を示した平面図であり、図45は、図44の1600−1600線に沿った断面図である。次に、図44および図45を参照して、第4実施形態による窒化物系半導体レーザ素子の構造について説明する。

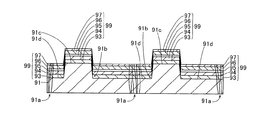

第4実施形態による窒化物系半導体レーザ素子では、図45に示すように、所定の角度傾斜した段差部91bを有するn型GaN基板91上に、n型層93、n型クラッド層94および発光層95が順次形成されている。発光層95上には、平坦部とその平坦部から上方に突出するように形成された凸部とを有するp型クラッド層96が形成されているとともに、p型クラッド層96の凸部上には、p型コンタクト層97が形成されている。このp型コンタクト層97とp型クラッド層96の凸部とによって、共振器方向(図44参照)に延びるストライプ状(細長状)のリッジ部98が構成されている。なお、n型層93、n型クラッド層94、発光層95、p型クラッド層96およびp型コンタクト層97は、それぞれ、上記第1実施形態のn型層3、n型クラッド層4、発光層5、p型クラッド層6およびp型コンタクト層7と同様の組成および厚みを有する。なお、n型GaN基板91の段差部91bの側面上に位置する半導体素子層99は、段差部91bの上部91cおよび下部91d上に位置する半導体素子層99の厚みよりも小さい厚みを有する。また、n型GaN基板91の段差部91bの下部91dと、段差部91bの下部91d上に位置する半導体素子層99とには、転位の集中している領域91aが形成されている。

ここで、第4実施形態では、n型層93、n型クラッド層94、発光層95、p型クラッド層96およびp型コンタクト層97によって、半導体素子層99が構成されている。

リッジ部98を構成するp型コンタクト層97上には、上記第1実施形態のp側オーミック電極10と同様の組成および厚みを有するp側オーミック電極100が形成されている。また、p側オーミック電極100の上面以外の領域を覆うように、上記第1実施形態の絶縁膜11と同様の組成および厚みを有する絶縁膜101が形成されている。絶縁膜101上には、p側オーミック電極100の上面に接触するように、上記第1実施形態のp側パッド電極12と同様の組成および厚みを有するp側パッド電極102が形成されている。このp側パッド電極102は、図44に示すように、平面的に見て、矩形状に突出した端部102aを有する。

また、図45に示すように、n型GaN基板91の裏面上には、n型GaN基板91の裏面の転位の集中している領域91a以外の領域に接触するように、上記第1実施形態のn側電極13と同様の組成および厚みを有するn側電極103が形成されている。

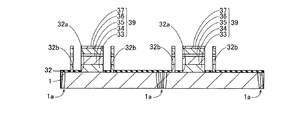

図46〜図55は、図44および図45に示した第4実施形態による窒化物系半導体レーザ素子の製造プロセスを説明するための平面図および断面図である。図44〜図55を参照して、この第4実施形態による製造プロセスでは、上記第1〜第3実施形態と異なり、n型GaN基板に段差部を設けるとともに、その段差部の上部上に、リッジ部を含む半導体素子層を形成する場合について説明する。

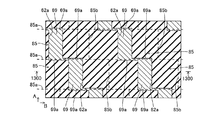

この第4実施形態の製造プロセスでは、まず、図46および図47に示すように、エッチング技術を用いて、n型GaN基板91の所定領域を約2μmの深さまでエッチングする。これにより、n型GaN基板91に、所定の角度傾斜した段差部91bを形成する。なお、図46では、太い斜線部分がエッチングされた領域である。この際、段差部91bの上部91cを、各素子形成領域(劈開線115aと素子分離線115bとに囲まれた領域)115の半導体素子層99(図45参照)を成長させる領域に配置する。なお、n型GaN基板91は、本発明の「基板」の一例であり、素子形成領域115は、本発明の「第1素子形成領域」、「第2素子形成領域」および「第3素子形成領域」の一例である。

ここで、第4実施形態では、共振器方向(A方向)に隣接する素子形成領域115の段差部91bの上部91cを、一つ置きに共振器方向と直交する方向(B方向)にずらすことにより互い違いに配置する。また、段差部91bの上部91cのA方向の端部91eが劈開線115aを跨いでA方向に隣接する素子形成領域115に達するように、n型GaN基板91をエッチングする。また、A方向に隣接する素子形成領域115にそれぞれ配置された段差部91bの上部91cが、劈開線115a上において接続されるように、n型GaN基板91をエッチングする。なお、この段差部91bの上部91cが接続されている領域のB方向の幅W7(図46参照)は、約6μmに設定する。また、第4実施形態では、B方向に隣接する素子形成領域115の段差部91bの各上部91cがB方向に連続しないように、n型GaN基板91をエッチングする。また、段差部91bの上部91cのB方向の幅W8(図46参照)は、約27μmに設定する。なお、隣接する劈開線115a間の距離(共振器の長さ)は、約800μmであり、隣接する素子分離線115b間の距離(素子の幅)は、約400μmである。なお、劈開線115aおよび素子分離線115bは、それぞれ、本発明の「第1分割線」および「第2分割線」の一例である。

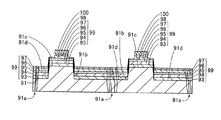

次に、図48および図49に示すように、MOCVD法を用いて、段差部91bを有するn型GaN基板91上に、上記第1実施形態のn型層3、n型クラッド層4、発光層5、p型クラッド層6およびp型コンタクト層7と同様の組成および厚みをそれぞれ有するn型層93、n型クラッド層94、発光層95、p型クラッド層96およびp型コンタクト層97を順次成長させる。これにより、n型層93、n型クラッド層94、発光層95、p型クラッド層96およびp型コンタクト層97からなる半導体素子層99が形成される。なお、半導体素子層99は、本発明の「第1半導体素子層」、「第2半導体素子層」および「第3半導体素子層」の一例である。

この際、第4実施形態では、図49に示すように、n型GaN基板91の段差部91bに位置する半導体素子層99は、段差部91bの上部91cおよび下部91dの上面上に位置する半導体素子層99の厚みよりも小さい厚みを有するように形成される。そして、この第4実施形態では、段差部91bの上部91cおよび下部91dに位置する半導体素子層99が、段差部91bに位置する半導体素子層99により接続されている。また、図48に示すように、段差部91bの上部91cに位置する半導体素子層99のリッジ部98となる領域のA方向の端部99aが、劈開線115aを跨いでA方向に隣接する素子形成領域115に達するように形成される。

この後、窒素ガス雰囲気中で、約800℃の温度条件下でアニール処理する。

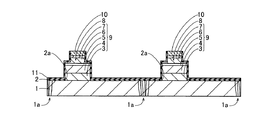

次に、図50および図51に示すように、図12〜図15に示した第1実施形態と同様のプロセスを用いて、p側オーミック電極100を形成した後、共振器方向(A方向)に延びるストライプ状(細長状)のリッジ部98を形成する。なお、リッジ部98は、本発明の「第1能動素子領域」、「第2能動素子領域」および「第3能動素子領域」の一例である。

この際、第4実施形態では、図50に示すように、段差部91bの上部91cに位置する半導体素子層99にのみリッジ部98を形成するとともに、そのリッジ部98がA方向に隣接する段差部91bの上部91cの各半導体素子層99が互いに接続している領域に配置されないようにする。これにより、A方向に隣接する素子形成領域115の各半導体素子層99のリッジ部98は、A方向に連続しないように形成される。また、各半導体素子層99のリッジ部98の端部98aは、劈開線115aを跨いでA方向に隣接する素子形成領域115に達するように形成される。

次に、図52に示すように、図16に示した第1実施形態と同様のプロセスを用いて、p側オーミック電極100の上面以外の領域を覆うように、上記第1実施形態の絶縁膜11と同様の組成および厚みを有する絶縁膜101を形成する。

次に、図53および図54に示すように、真空蒸着法を用いて、絶縁膜101上に、p側オーミック電極100の上面に接触するように、上記第1実施形態のp側パッド電極12と同様の組成および厚みを有するp側パッド電極102を形成する。この際、図53に示すように、p側パッド電極102の一部が共振器方向と直交する方向(B方向)に、平面的に見て矩形状に突出するように形成する。この後、図54に示すように、真空蒸着法を用いて、n型GaN基板91の裏面上に、n型GaN基板91の裏面の転位の集中している領域91a以外の領域に接触するように、上記第1実施形態のn側電極13と同様の組成および厚みを有するn側電極103を形成する。

次に、図53に示した劈開線115aに沿って、共振器方向(A方向)に隣接する素子形成領域115を分割する。これにより、図55に示すように、分割された隣接する素子形成領域115のそれぞれの劈開面に、共振器端面99bが形成される。この後、素子分離線115bに沿って素子を分離することによって、図44および図45に示した第4実施形態による窒化物系半導体レーザ素子が形成される。

第4実施形態の製造プロセスでは、上記のように、共振器方向(A方向)に隣接するn型GaN基板91の段差部91bの上部91cを共振器方向と直交する方向(B方向)にずらすことにより互い違いに配置することによって、n型GaN基板91上に半導体素子層99を形成すれば、A方向に隣接する素子形成領域115の段差部91bの上部91c上に位置する各半導体素子層99は、互い違いに配置される。この場合、段差部91bの上部91cに位置する半導体素子層99にのみリッジ部98を形成するとともに、そのリッジ部98がA方向に隣接する段差部91bの上部91cの各半導体素子層99が互いに接続している領域に配置されないようにすることによって、A方向に隣接する素子形成領域115の各リッジ部98をA方向に連続しないように形成することができる。これにより、上記第1実施形態と同様、素子分割前におけるリッジ部98を含む半導体素子層99のA方向の長さが小さくなることにより半導体素子層99のリッジ部98の歪みが緩和されるので、リッジ部98にクラックが発生するのを抑制することができる。また、段差部91bの上部91cのA方向の端部91eを、劈開線115aを跨いでA方向に隣接する素子形成領域115に達するように配置することによって、A方向に隣接する素子形成領域115に形成される各半導体素子層99の端部99aが、共に劈開線115aを跨いでA方向に隣接する素子形成領域115に達するように配置される。これにより、上記第1実施形態と同様、1回の劈開で、A方向に隣接する素子形成領域115のそれぞれの半導体素子層99に一方の共振器端面を形成することができるので、製造工程が増加することがない。

また、第4実施形態では、段差部91bを有するn型GaN基板91上に半導体素子層99を形成することによって、半導体素子層99を形成する際に、段差部91bに位置する半導体素子層99の厚みが薄くなるので、段差部91bに位置する半導体素子層99に歪みを集中させることができる。これにより、半導体素子層99の段差部91bに位置する半導体素子層99にクラックが発生しやすくなる一方、半導体素子層99の段差部91b以外の領域には、クラックが発生しにくくなるので、段差部91bの上部91c上に位置するリッジ部98にクラックが発生するのをより抑制することができる。

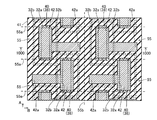

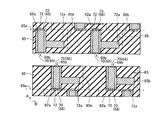

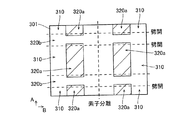

(第5実施形態)

図56は、本発明の第5実施形態による窒化物系半導体レーザ素子の構造を示した平面図であり、図57は、図56の2100−2100線に沿った断面図である。次に、図56および図57を参照して、第5実施形態による窒化物系半導体レーザ素子の構造について説明する。

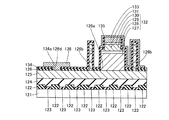

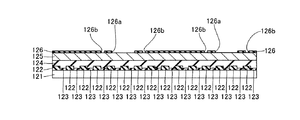

第5実施形態による窒化物系半導体レーザ素子では、図57に示すように、サファイア基板121上に、約200nmの厚みを有するSiN膜からなる選択成長マスク122が所定の間隔を隔てて形成されている。選択成長マスク122間に露出されたサファイア基板121の上面上には、約20nmの厚みを有するアンドープのAlGaNからなる低温バッファ層123が形成されている。選択成長マスク122および低温バッファ層123上には、約2μmの厚みを有するアンドープのGaNからなるバッファ層124が形成されている。バッファ層124上には、上記第1実施形態のn型層3と同様の組成および厚みを有するn型層125が形成されている。n型層125上には、開口部126a、126bおよび126dを有するとともに、約200nmの厚みを有するSiN膜からなる選択成長マスク126が形成されている。

また、n型層125上の開口部126aおよび126bに対応する領域には、n型コンタクト層127および発光層128が順次形成されている。発光層128上には、平坦部とその平坦部から上方に突出するように形成された凸部とを有するp型クラッド層129が形成されているとともに、p型クラッド層129の凸部上には、p型コンタクト層130が形成されている。このp型コンタクト層130とp型クラッド層129の凸部とによって、共振器方向(図56のA方向)に延びるストライプ状(細長状)のリッジ部131が構成されている。なお、n型コンタクト層127は、約2μmの厚みを有するSiがドープされたn型GaNからなる。また、発光層128、p型クラッド層129およびp型コンタクト層130は、それぞれ、上記第1実施形態の発光層5、p型クラッド層6およびp型コンタクト層7と同様の組成および厚みを有する。

ここで、第5実施形態では、n型コンタクト層127、発光層128、p型クラッド層129およびp型コンタクト層130によって、半導体素子層132が構成されている。

リッジ部131を構成するp型コンタクト層130上には、上記第1実施形態のp側オーミック電極10と同様の組成および厚みを有するp側オーミック電極133が形成されている。また、p側オーミック電極133の上面以外の領域を覆うように、上記第1実施形態の絶縁膜11と同様の組成および厚みを有する絶縁膜134が形成されている。この絶縁膜134の選択成長マスク126の開口部126dに対応する領域には、開口部134aが形成されている。絶縁膜134上の所定領域には、p側オーミック電極133の上面に接触するように、上記第1実施形態のp側パッド電極12と同様の組成および厚みを有するp側パッド電極135が形成されている。このp側パッド電極135は、図56に示すように、矩形状に突出した端部135aを有する。

また、図57に示すように、絶縁膜134上の開口部134aに対応する領域には、開口部134aおよび126dを介してn型層125に接触するように、上記第1実施形態のn側電極13と同様の組成および厚みを有するn側電極136が形成されている。このn側電極136は、図56に示すように、平面的に見て、四角形状に形成されている。

図58〜図68は、図56および図57に示した第5実施形態による窒化物系半導体レーザ素子の製造プロセスを説明するための断面図および平面図である。図56〜図68を参照して、この第5実施形態の製造プロセスでは、上記第1〜第4実施形態と異なり、n型GaN基板に代えてサファイア基板を用いる場合について説明する。

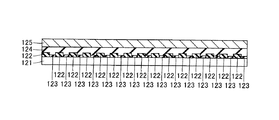

まず、図58に示すように、プラズマCVD法を用いて、サファイア基板121上に、約200nmの厚みを有するSiN膜からなる選択成長マスク122を所定の間隔を隔てて形成する。この後、MOCVD法を用いて、選択成長マスク122間に露出されたサファイア基板121の上面上に、約20nmの厚みを有するアンドープのAlGaNからなる低温バッファ層123を成長させる。

続いて、選択成長マスク122および低温バッファ層123上に、約2μmの厚みを有するアンドープのGaNからなるバッファ層124を選択横方向成長させる。この際、バッファ層124は、低温バッファ層123上に選択的に縦方向に成長した後、徐々に横方向に成長することにより表面が平坦となる。このため、バッファ層124に形成される転位が横方向に曲げられるので、縦方向に伝播された転位が形成されにくくなる。これにより、バッファ層124の転位密度を低減することができる。この後、バッファ層124上に、上記第1実施形態のn型層3と同様の組成および厚みを有するn型層125を成長させる。

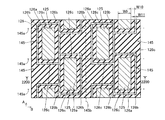

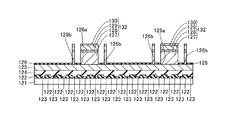

次に、図59および図60に示すように、プラズマCVD法を用いて、n型層125上に、開口部126aおよび126bを有するとともに、約200nmの厚みを有するSiN膜からなる選択成長マスク126を形成する。この際、開口部126aを、各素子形成領域(劈開線145aと素子分離線145bとに囲まれた領域)145の半導体素子層132(図57参照)を成長させる領域に配置する。なお、素子形成領域145は、本発明の「第1素子形成領域」、「第2素子形成領域」および「第3素子形成領域」の一例である。

ここで、第5実施形態では、共振器方向(A方向)に隣接する素子形成領域145の開口部126aがA方向に連続しないように、選択成長マスク126を形成する。具体的には、A方向に隣接する開口部126aを、一つ置きに共振器方向と直交する方向(B方向)にずらすことにより互い違いに配置する。また、開口部126aのA方向の端部126cが劈開線145aを跨いでA方向に隣接する素子形成領域145に達するように、選択成長マスク126を形成する。また、第5実施形態では、B方向に隣接する素子形成領域145の各開口部126aがB方向に連続しないように、選択成長マスク126を形成する。また、開口部126aのB方向の幅W9(図59参照)は、約10μmに設定する。また、開口部126bを、開口部126aから約2μmの間隔W10(図59参照)を隔てて開口部126aを囲むように配置する。また、開口部126bのA方向およびB方向の幅W11(図59参照)は、約5μmに設定する。なお、隣接する劈開線145a間の距離(共振器の長さ)は、約700μmであり、隣接する素子分離線145b間の距離(素子の幅)は、約400μmである。なお、劈開線145aおよび素子分離線145bは、それぞれ、本発明の「第1分割線」および「第2分割線」の一例である。

次に、図61および図62に示すように、MOCVD法を用いて、n型層125上の開口部126aおよび126bに対応する領域に、約2μmの厚みを有するSiがドープされたn型GaNからなるn型コンタクト層127を成長させる。続いて、上記第1実施形態の発光層5、p型クラッド層6およびp型コンタクト層7と同様の組成および厚みをそれぞれ有する発光層128、p型クラッド層129およびp型コンタクト層130を順次成長させる。これにより、n型コンタクト層127、発光層128、p型クラッド層129およびp型コンタクト層130からなる半導体素子層132が形成される。なお、半導体素子層132は、本発明の「第1半導体素子層」、「第2半導体素子層」および「第3半導体素子層」の一例である。

この際、第5実施形態では、図61に示すように、半導体素子層132は、選択成長マスク126上には形成されない。すなわち、共振器方向(A方向)に隣接する素子形成領域145に形成される半導体素子層132がA方向に連続しないように形成されるとともに、共振器方向と直交する方向(B方向)に隣接する素子形成領域145に形成される半導体素子層132がB方向に連続しないように形成される。また、半導体素子層132のA方向の端部132aが劈開線145aを跨いでA方向に隣接する素子形成領域145に達するように形成される。

この後、窒素ガス雰囲気中で、約800℃の温度条件下でアニール処理する。

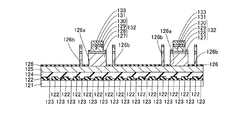

次に、図63および図64に示すように、図12〜図15に示した第1実施形態と同様のプロセスを用いて、p側オーミック電極133を形成した後、共振器方向(A方向)に延びるストライプ状(細長状)のリッジ部131を形成する。なお、リッジ部131は、本発明の「第1能動素子領域」、「第2能動素子領域」および「第3能動素子領域」の一例である。

ここで、第5実施形態では、A方向に隣接する素子形成領域145の各半導体素子層132のリッジ部131は、A方向に連続しないように形成される。また、各半導体素子層132のリッジ部131の端部131aは、劈開線145aを跨いでA方向に隣接する素子形成領域145に達するように形成される。

次に、図65に示すように、図16に示した第1実施形態と同様のプロセスを用いて、p側オーミック電極133の上面以外の領域を覆うように、上記第1実施形態の絶縁膜11と同様の組成および厚みを有する絶縁膜134を形成する。

次に、図66および図67に示すように、エッチング技術を用いて、絶縁膜134および選択成長マスク126の所定領域に、それぞれ、開口部134aおよび126dを形成する。この後、真空蒸着法を用いて、絶縁膜134上の所定領域に、p側オーミック電極133の上面に接触するように、上記第1実施形態のp側パッド電極12と同様の組成および厚みを有するp側パッド電極135を形成する。この際、図66に示すように、平面的に見て矩形状に突出した端部135aを有するように、p側パッド電極135を形成する。この後、図67に示すように、真空蒸着法を用いて、絶縁膜134上の開口部134aに対応する領域に、開口部134aおよび126cを介してn型層125に接触するように、上記第1実施形態のn側電極13と同様の組成および厚みを有するn側電極136を形成する。この際、図66に示すように、平面的に見て四角形状を有するように、n側電極136を形成する。

次に、図66に示した劈開線145aに沿って、共振器方向(A方向)に隣接する素子形成領域145を分割する。これにより、図68に示すように、分割された隣接する素子形成領域145のそれぞれの劈開面に、共振器端面132bが形成される。この後、素子分離線145bに沿って素子を分離することによって、図56および図57に示した第5実施形態による窒化物系半導体レーザ素子が形成される。

第5実施形態の製造プロセスでは、基板としてサファイア基板121を用いる場合において、半導体素子層132のリッジ部131にクラックが発生するのを抑制することができるなどの第2実施形態と同様の効果を得ることができる。

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれる。

たとえば、上記第1〜第5実施形態では、本発明を半導体レーザ素子に適用する場合について説明したが、本発明はこれに限らず、半導体レーザ素子以外の半導体素子にも適用可能である。

また、上記第1〜第5実施形態では、基板上に、n型半導体層、発光層およびp型半導体層を順次形成したが、本発明はこれに限らず、基板上に、p型半導体層、発光層およびn型半導体層を順次形成する場合にも、同様の効果を得ることができる。

また、上記第1〜第5実施形態では、ウルツ鉱型構造の窒化物系半導体各層を形成したが、本発明はこれに限らず、閃亜鉛鉱型構造の半導体各層を形成してもよい。

また、上記第1〜第5実施形態では、MOCVD法を用いて、窒化物系半導体各層を結晶成長させたが、本発明はこれに限らず、HVPE法やガスソースMBE法(Molecular Beam Epitaxy:分子線エピタキシャル成長法)などを用いて、半導体各層を結晶成長させてもよい。

また、上記第1〜第5実施形態では、共振器方向(A方向)の両側に隣接する素子形成領域において能動素子領域を不連続に形成したが、本発明はこれに限らず、A方向の一方の片側に隣接する素子形成領域において能動素子領域を不連続に形成するとともに、A方向の他方の片側に隣接する素子形成領域において能動素子領域を連続に形成する場合においても、同様の効果を得ることができる。