JP2002164781A5 - - Google Patents

Download PDFInfo

- Publication number

- JP2002164781A5 JP2002164781A5 JP2000361557A JP2000361557A JP2002164781A5 JP 2002164781 A5 JP2002164781 A5 JP 2002164781A5 JP 2000361557 A JP2000361557 A JP 2000361557A JP 2000361557 A JP2000361557 A JP 2000361557A JP 2002164781 A5 JP2002164781 A5 JP 2002164781A5

- Authority

- JP

- Japan

- Prior art keywords

- clock signal

- controlled oscillator

- voltage controlled

- output

- oscillation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Description

【0009】

【課題を解決するための手段】

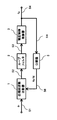

本発明の発振回路は、従来の回路構成に加えて、電圧制御発振器3の出力と分周器5の入力との間に遅延回路を挿入することによって、上述の課題を解決した。遅延回路に設定される遅延量は、電圧制御発振器の構成によって異なり、帰還クロック信号S6の立ち上がりエッジおよび立ち下がりエッジが、電圧制御発振器3の内部に存在するすべてのクロック信号の立ち上がりエッジ、立ち下がりエッジから最も乖離した位置となるように設定される。すなわち、電圧制御発振器3が電気的あるいは機械的な共振現象を利用したものである場合は、帰還クロック信号S6の立ち上がりエッジ、立ち下がりエッジのいずれかと、電圧制御発振器3の出力クロック信号S4の立ち上がりエッジまたは立ち下がりエッジとの時間差が、電圧制御発振器3の出力クロック信号S4の発振周期に対して1/4またはその奇数倍に概ね等しく設定される。一方、電圧制御発振器3がK個のインバータ回路を環状に接続してなるリングオシレータ形式のものである場合は、帰還クロック信号S6の立ち上がりエッジ、立ち下がりエッジのいずれかと、電圧制御発振器3の出力クロック信号S4の立ち上がりエッジまたは立ち下がりエッジとの時間差が、電圧制御発振器3の出力クロック信号S4の発振周期に対し1/(4K)またはその奇数倍に概ね等しく設定される。このように構成することにより、位相周波数比較器1や分周器5を構成する論理回路の状態遷移によって、電源電圧や電圧制御発振器3の入力電圧信号S3にスパイク状のノイズが発生したとしても、そのスパイクの発生は、電圧制御発振器3の内部に存在するいずれの発振波形の立ち上がり、または立ち下がりエッジからも最も乖離した時点となるため、電圧制御発振器3の動作は極力安定に保たれる。この結果、出力クロック信号S4に発生するジッタは極めて少なくなる。

【課題を解決するための手段】

本発明の発振回路は、従来の回路構成に加えて、電圧制御発振器3の出力と分周器5の入力との間に遅延回路を挿入することによって、上述の課題を解決した。遅延回路に設定される遅延量は、電圧制御発振器の構成によって異なり、帰還クロック信号S6の立ち上がりエッジおよび立ち下がりエッジが、電圧制御発振器3の内部に存在するすべてのクロック信号の立ち上がりエッジ、立ち下がりエッジから最も乖離した位置となるように設定される。すなわち、電圧制御発振器3が電気的あるいは機械的な共振現象を利用したものである場合は、帰還クロック信号S6の立ち上がりエッジ、立ち下がりエッジのいずれかと、電圧制御発振器3の出力クロック信号S4の立ち上がりエッジまたは立ち下がりエッジとの時間差が、電圧制御発振器3の出力クロック信号S4の発振周期に対して1/4またはその奇数倍に概ね等しく設定される。一方、電圧制御発振器3がK個のインバータ回路を環状に接続してなるリングオシレータ形式のものである場合は、帰還クロック信号S6の立ち上がりエッジ、立ち下がりエッジのいずれかと、電圧制御発振器3の出力クロック信号S4の立ち上がりエッジまたは立ち下がりエッジとの時間差が、電圧制御発振器3の出力クロック信号S4の発振周期に対し1/(4K)またはその奇数倍に概ね等しく設定される。このように構成することにより、位相周波数比較器1や分周器5を構成する論理回路の状態遷移によって、電源電圧や電圧制御発振器3の入力電圧信号S3にスパイク状のノイズが発生したとしても、そのスパイクの発生は、電圧制御発振器3の内部に存在するいずれの発振波形の立ち上がり、または立ち下がりエッジからも最も乖離した時点となるため、電圧制御発振器3の動作は極力安定に保たれる。この結果、出力クロック信号S4に発生するジッタは極めて少なくなる。

【0016】

本実施形態において、電圧制御発振器3はK個のインバータ回路を環状に接続してなるリングオシレータ形式のものである。このとき、定常状態における発振回路のタイミングチャートは図4で示される。電圧制御発振器3の出力クロック信号S4と、遅延回路4の出力信号S5との間には、遅延回路4の遅延量に応じた位相差が生じている。その結果として、分周回路5から出力される帰還クロック信号S6の立ち上がりエッジは、電圧制御発振器3の出力クロック信号S4の立ち上がりエッジから、一定量ずれた時点に現れる。このずれ量が、出力クロック信号S4の発振周期をTとして、T/(4K)、または、その奇数倍に概ね等しくなるように、遅延回路4の遅延量は調節されている。本実施形態においても、従来の発振回路と同様に、図4最下段に示されるようなスパイク状のノイズが電源電圧に重畳する。しかしながら、前述したように遅延回路4の遅延量が調節されているため、スパイク状のノイズの発生箇所は、電圧制御発振器3の内部信号A2,B2,C2のいずれの立ち上がりエッジ、立ち下がりエッジからも最も乖離した時点となっている。換言すると、スパイク状のノイズの発生箇所は、信号A2,B2,C2の波形がほぼ水平な時点となっている。波形が水平な状態においては、たとえノイズによって電圧制御発振器3が一時的に不安定になったとしても、その影響はすみやかに減衰し、次の立ち上がりもしくは立ち下がりエッジを揺らすには至らない。したがって、電圧制御発振器3の出力信号S4の立ち上がりエッジ、立ち下がりエッジには揺らぎが発生せず、ジッタの少ない発振回路が実現される。

本実施形態において、電圧制御発振器3はK個のインバータ回路を環状に接続してなるリングオシレータ形式のものである。このとき、定常状態における発振回路のタイミングチャートは図4で示される。電圧制御発振器3の出力クロック信号S4と、遅延回路4の出力信号S5との間には、遅延回路4の遅延量に応じた位相差が生じている。その結果として、分周回路5から出力される帰還クロック信号S6の立ち上がりエッジは、電圧制御発振器3の出力クロック信号S4の立ち上がりエッジから、一定量ずれた時点に現れる。このずれ量が、出力クロック信号S4の発振周期をTとして、T/(4K)、または、その奇数倍に概ね等しくなるように、遅延回路4の遅延量は調節されている。本実施形態においても、従来の発振回路と同様に、図4最下段に示されるようなスパイク状のノイズが電源電圧に重畳する。しかしながら、前述したように遅延回路4の遅延量が調節されているため、スパイク状のノイズの発生箇所は、電圧制御発振器3の内部信号A2,B2,C2のいずれの立ち上がりエッジ、立ち下がりエッジからも最も乖離した時点となっている。換言すると、スパイク状のノイズの発生箇所は、信号A2,B2,C2の波形がほぼ水平な時点となっている。波形が水平な状態においては、たとえノイズによって電圧制御発振器3が一時的に不安定になったとしても、その影響はすみやかに減衰し、次の立ち上がりもしくは立ち下がりエッジを揺らすには至らない。したがって、電圧制御発振器3の出力信号S4の立ち上がりエッジ、立ち下がりエッジには揺らぎが発生せず、ジッタの少ない発振回路が実現される。

Claims (1)

- 位相同期ループを構成することにより、入力クロック信号の周波数を逓倍して出力する方式の発振回路であって、前記位相同期ループは、入力クロック信号と帰還クロック信号との位相差を検出してその検出量に応じた誤差信号を発生する位相比較手段と、誤差信号を積分するフィルタ手段と、フィルタ手段から出力される電圧信号に応じて発振周波数が変化する電圧制御発振器と、電圧制御発振器の出力クロック信号を分周して前記帰還クロック信号を生成する分周手段とを含み、前記電圧制御発振器は、K個のインバータ回路を環状に接続してなるリングオシレータ形式の電圧制御発振器である発振回路において、電圧制御発振器の出力と分周手段の入力との間に遅延手段を挿入するとともに、前記帰還クロック信号の立ち上がりエッジ、立ち下がりエッジのいずれかと、電圧制御発振器の出力クロック信号の立ち上がりエッジまたは立ち下がりエッジとの時間差が、定常状態において、電圧制御発振器の出力クロック信号の発振周期に対し、1/(4K)またはその奇数倍に概ね等しくなるよう、前記遅延手段の遅延量が設定されてなることを特徴とする発振回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000361557A JP3772668B2 (ja) | 2000-11-28 | 2000-11-28 | 位相同期ループを用いた発振回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000361557A JP3772668B2 (ja) | 2000-11-28 | 2000-11-28 | 位相同期ループを用いた発振回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002164781A JP2002164781A (ja) | 2002-06-07 |

| JP2002164781A5 true JP2002164781A5 (ja) | 2005-02-03 |

| JP3772668B2 JP3772668B2 (ja) | 2006-05-10 |

Family

ID=18832975

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000361557A Expired - Fee Related JP3772668B2 (ja) | 2000-11-28 | 2000-11-28 | 位相同期ループを用いた発振回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3772668B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4660076B2 (ja) * | 2003-06-23 | 2011-03-30 | ルネサスエレクトロニクス株式会社 | クロック発生回路 |

| CN114826254B (zh) * | 2022-06-28 | 2022-09-20 | 浙江地芯引力科技有限公司 | 一种锁相环电路、本地振荡器及电子设备 |

-

2000

- 2000-11-28 JP JP2000361557A patent/JP3772668B2/ja not_active Expired - Fee Related

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2830735B2 (ja) | 位相同期型タイミング発生回路 | |

| JP3323054B2 (ja) | 周波数逓倍回路 | |

| JPH1065521A (ja) | 多相クロック発生回路 | |

| JPH1168559A (ja) | 位相同期ループ回路 | |

| JP3995552B2 (ja) | クロック逓倍回路 | |

| US20240022255A1 (en) | Methods and apparatus of charge-sharing locking with digital controlled oscillators | |

| JPH08316802A (ja) | 多相クロック信号形成装置 | |

| JP2002164781A5 (ja) | ||

| US7519087B2 (en) | Frequency multiply circuit using SMD, with arbitrary multiplication factor | |

| JPH08274629A (ja) | ディジタルpll回路 | |

| JP3772668B2 (ja) | 位相同期ループを用いた発振回路 | |

| JP3411120B2 (ja) | Pll回路 | |

| JP2003289248A (ja) | Pll回路 | |

| JPH07120944B2 (ja) | Pll回路 | |

| US7259635B2 (en) | Arbitrary frequency signal generator | |

| JPH0661848A (ja) | 位相同期発振器 | |

| KR101002925B1 (ko) | 지연고정루프회로 | |

| KR100829454B1 (ko) | Pll 회로의 전압 제어 발진기 및 그 제어 방법 | |

| JP4463441B2 (ja) | Pll回路 | |

| JP2000031818A (ja) | ディレイ回路及びこれを備えたpll回路 | |

| JP2006222879A (ja) | 多相クロック生成回路 | |

| JP2001274679A (ja) | Pll回路 | |

| JP2010074562A (ja) | Pll回路 | |

| JP2003348063A (ja) | クロック同期回路 | |

| JPH08172355A (ja) | Pll回路 |