CN101567408B - 光电转换装置的制造方法 - Google Patents

光电转换装置的制造方法 Download PDFInfo

- Publication number

- CN101567408B CN101567408B CN2009101369101A CN200910136910A CN101567408B CN 101567408 B CN101567408 B CN 101567408B CN 2009101369101 A CN2009101369101 A CN 2009101369101A CN 200910136910 A CN200910136910 A CN 200910136910A CN 101567408 B CN101567408 B CN 101567408B

- Authority

- CN

- China

- Prior art keywords

- semiconductor layer

- photoelectric conversion

- conversion device

- crystal semiconductor

- manufacture method

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000006243 chemical reaction Methods 0.000 title claims abstract description 148

- 238000000034 method Methods 0.000 title claims description 123

- 238000004519 manufacturing process Methods 0.000 title claims description 81

- 239000004065 semiconductor Substances 0.000 claims abstract description 714

- 239000013078 crystal Substances 0.000 claims abstract description 318

- 239000000758 substrate Substances 0.000 claims abstract description 222

- 239000012535 impurity Substances 0.000 claims abstract description 219

- 239000007790 solid phase Substances 0.000 claims abstract description 16

- 230000004888 barrier function Effects 0.000 claims description 61

- 239000001257 hydrogen Substances 0.000 claims description 55

- 229910052739 hydrogen Inorganic materials 0.000 claims description 55

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 52

- 239000007789 gas Substances 0.000 claims description 51

- 238000010438 heat treatment Methods 0.000 claims description 31

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 claims description 29

- 229910000077 silane Inorganic materials 0.000 claims description 29

- 230000015572 biosynthetic process Effects 0.000 claims description 19

- 238000005229 chemical vapour deposition Methods 0.000 claims description 15

- 230000007547 defect Effects 0.000 claims description 9

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 claims description 7

- 238000005468 ion implantation Methods 0.000 claims description 7

- 238000004151 rapid thermal annealing Methods 0.000 claims description 6

- 230000012010 growth Effects 0.000 abstract description 22

- 239000010410 layer Substances 0.000 description 577

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 47

- 229910052710 silicon Inorganic materials 0.000 description 47

- 239000010703 silicon Substances 0.000 description 47

- 239000012467 final product Substances 0.000 description 36

- 150000002500 ions Chemical class 0.000 description 35

- 239000011241 protective layer Substances 0.000 description 26

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 21

- 238000010276 construction Methods 0.000 description 20

- 125000004429 atom Chemical group 0.000 description 19

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 14

- 238000010586 diagram Methods 0.000 description 14

- 239000000463 material Substances 0.000 description 14

- 239000011521 glass Substances 0.000 description 13

- 238000010248 power generation Methods 0.000 description 13

- 238000005530 etching Methods 0.000 description 12

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 12

- 229910021417 amorphous silicon Inorganic materials 0.000 description 10

- 239000010408 film Substances 0.000 description 10

- 238000011282 treatment Methods 0.000 description 10

- 239000002994 raw material Substances 0.000 description 9

- 235000012431 wafers Nutrition 0.000 description 9

- 230000003287 optical effect Effects 0.000 description 8

- 230000008569 process Effects 0.000 description 8

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- 239000010409 thin film Substances 0.000 description 8

- 229910052581 Si3N4 Inorganic materials 0.000 description 7

- 239000003595 mist Substances 0.000 description 7

- 229910052757 nitrogen Inorganic materials 0.000 description 7

- 230000005693 optoelectronics Effects 0.000 description 7

- 238000002161 passivation Methods 0.000 description 7

- 238000000926 separation method Methods 0.000 description 7

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 7

- 238000000348 solid-phase epitaxy Methods 0.000 description 7

- 239000002800 charge carrier Substances 0.000 description 6

- 230000005284 excitation Effects 0.000 description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 6

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 5

- 238000009792 diffusion process Methods 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 238000010884 ion-beam technique Methods 0.000 description 5

- 239000001301 oxygen Substances 0.000 description 5

- 229910052760 oxygen Inorganic materials 0.000 description 5

- 229920005591 polysilicon Polymers 0.000 description 5

- 150000004756 silanes Chemical class 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- 238000000927 vapour-phase epitaxy Methods 0.000 description 5

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 4

- 239000004411 aluminium Substances 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 230000000052 comparative effect Effects 0.000 description 4

- 239000002322 conducting polymer Substances 0.000 description 4

- 229920001940 conductive polymer Polymers 0.000 description 4

- 239000013081 microcrystal Substances 0.000 description 4

- 150000004767 nitrides Chemical class 0.000 description 4

- 229910052709 silver Inorganic materials 0.000 description 4

- 239000004332 silver Substances 0.000 description 4

- 238000007740 vapor deposition Methods 0.000 description 4

- 238000001237 Raman spectrum Methods 0.000 description 3

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 3

- 230000004913 activation Effects 0.000 description 3

- 238000007600 charging Methods 0.000 description 3

- 230000008878 coupling Effects 0.000 description 3

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- 238000001678 elastic recoil detection analysis Methods 0.000 description 3

- 150000002431 hydrogen Chemical class 0.000 description 3

- 238000005286 illumination Methods 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- 230000031700 light absorption Effects 0.000 description 3

- 239000012071 phase Substances 0.000 description 3

- 239000000047 product Substances 0.000 description 3

- 230000006798 recombination Effects 0.000 description 3

- 238000005215 recombination Methods 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 2

- 241000500881 Lepisma Species 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 239000002585 base Substances 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 239000005388 borosilicate glass Substances 0.000 description 2

- 238000005266 casting Methods 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 239000000470 constituent Substances 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 230000004907 flux Effects 0.000 description 2

- UQEAIHBTYFGYIE-UHFFFAOYSA-N hexamethyldisiloxane Chemical compound C[Si](C)(C)O[Si](C)(C)C UQEAIHBTYFGYIE-UHFFFAOYSA-N 0.000 description 2

- GPRLSGONYQIRFK-UHFFFAOYSA-N hydron Chemical compound [H+] GPRLSGONYQIRFK-UHFFFAOYSA-N 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 2

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 238000011084 recovery Methods 0.000 description 2

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 2

- 238000004904 shortening Methods 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 235000014347 soups Nutrition 0.000 description 2

- 239000007921 spray Substances 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 238000004857 zone melting Methods 0.000 description 2

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical compound C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- TWDJIKFUVRYBJF-UHFFFAOYSA-N Cyanthoate Chemical compound CCOP(=O)(OCC)SCC(=O)NC(C)(C)C#N TWDJIKFUVRYBJF-UHFFFAOYSA-N 0.000 description 1

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical class F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 235000003140 Panax quinquefolius Nutrition 0.000 description 1

- 240000005373 Panax quinquefolius Species 0.000 description 1

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000002745 absorbent Effects 0.000 description 1

- 239000002250 absorbent Substances 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000003245 coal Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- AWFPGKLDLMAPMK-UHFFFAOYSA-N dimethylaminosilicon Chemical compound CN(C)[Si] AWFPGKLDLMAPMK-UHFFFAOYSA-N 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 238000005265 energy consumption Methods 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 238000005984 hydrogenation reaction Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- MRNHPUHPBOKKQT-UHFFFAOYSA-N indium;tin;hydrate Chemical compound O.[In].[Sn] MRNHPUHPBOKKQT-UHFFFAOYSA-N 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000009545 invasion Effects 0.000 description 1

- 238000009940 knitting Methods 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- ORUIBWPALBXDOA-UHFFFAOYSA-L magnesium fluoride Chemical compound [F-].[F-].[Mg+2] ORUIBWPALBXDOA-UHFFFAOYSA-L 0.000 description 1

- 229910001635 magnesium fluoride Inorganic materials 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 239000003345 natural gas Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 239000003921 oil Substances 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 230000001443 photoexcitation Effects 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 230000003405 preventing effect Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000002285 radioactive effect Effects 0.000 description 1

- 238000004064 recycling Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 230000001172 regenerating effect Effects 0.000 description 1

- 230000008929 regeneration Effects 0.000 description 1

- 238000011069 regeneration method Methods 0.000 description 1

- 239000010979 ruby Substances 0.000 description 1

- 229910001750 ruby Inorganic materials 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 239000005368 silicate glass Substances 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 238000010301 surface-oxidation reaction Methods 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- RSNQKPMXXVDJFG-UHFFFAOYSA-N tetrasiloxane Chemical compound [SiH3]O[SiH2]O[SiH2]O[SiH3] RSNQKPMXXVDJFG-UHFFFAOYSA-N 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 230000001052 transient effect Effects 0.000 description 1

- QQQSFSZALRVCSZ-UHFFFAOYSA-N triethoxysilane Chemical compound CCO[SiH](OCC)OCC QQQSFSZALRVCSZ-UHFFFAOYSA-N 0.000 description 1

- PQDJYEQOELDLCP-UHFFFAOYSA-N trimethylsilane Chemical compound C[SiH](C)C PQDJYEQOELDLCP-UHFFFAOYSA-N 0.000 description 1

- 229940094989 trimethylsilane Drugs 0.000 description 1

- -1 tungsten nitride Chemical class 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/1804—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof comprising only elements of Group IV of the Periodic System

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/02—Details

- H01L31/02002—Arrangements for conducting electric current to or from the device in operations

- H01L31/02005—Arrangements for conducting electric current to or from the device in operations for device characterised by at least one potential jump barrier or surface barrier

- H01L31/02008—Arrangements for conducting electric current to or from the device in operations for device characterised by at least one potential jump barrier or surface barrier for solar cells or solar cell modules

- H01L31/0201—Arrangements for conducting electric current to or from the device in operations for device characterised by at least one potential jump barrier or surface barrier for solar cells or solar cell modules comprising specially adapted module bus-bar structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/04—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices

- H01L31/042—PV modules or arrays of single PV cells

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/04—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices

- H01L31/06—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices characterised by at least one potential-jump barrier or surface barrier

- H01L31/072—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices characterised by at least one potential-jump barrier or surface barrier the potential barriers being only of the PN heterojunction type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/04—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices

- H01L31/06—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices characterised by at least one potential-jump barrier or surface barrier

- H01L31/075—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices characterised by at least one potential-jump barrier or surface barrier the potential barriers being only of the PIN type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/04—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices

- H01L31/06—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices characterised by at least one potential-jump barrier or surface barrier

- H01L31/075—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices characterised by at least one potential-jump barrier or surface barrier the potential barriers being only of the PIN type

- H01L31/076—Multiple junction or tandem solar cells

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/1804—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof comprising only elements of Group IV of the Periodic System

- H01L31/182—Special manufacturing methods for polycrystalline Si, e.g. Si ribbon, poly Si ingots, thin films of polycrystalline Si

- H01L31/1824—Special manufacturing methods for microcrystalline Si, uc-Si

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/186—Particular post-treatment for the devices, e.g. annealing, impurity gettering, short-circuit elimination, recrystallisation

- H01L31/1872—Recrystallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/1892—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof methods involving the use of temporary, removable substrates

- H01L31/1896—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof methods involving the use of temporary, removable substrates for thin-film semiconductors

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02S—GENERATION OF ELECTRIC POWER BY CONVERSION OF INFRARED RADIATION, VISIBLE LIGHT OR ULTRAVIOLET LIGHT, e.g. USING PHOTOVOLTAIC [PV] MODULES

- H02S40/00—Components or accessories in combination with PV modules, not provided for in groups H02S10/00 - H02S30/00

- H02S40/30—Electrical components

- H02S40/34—Electrical components comprising specially adapted electrical connection means to be structurally associated with the PV module, e.g. junction boxes

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/545—Microcrystalline silicon PV cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/547—Monocrystalline silicon PV cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/548—Amorphous silicon PV cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Abstract

所公开的发明的目的之一在于在有效地利用有限的资源的同时安全地提供具有优越的光电转换特性的光电转换装置。在所公开的发明中,在单晶半导体衬底中形成脆化层,并且在单晶半导体衬底的一个表面上形成第一杂质半导体层、第一电极以及绝缘层;通过在将绝缘层和支撑衬底贴紧来将单晶半导体衬底和支撑衬底贴在一起后,在脆化层中分离单晶半导体衬底,形成包括第一单晶半导体层的叠层体;在第一单晶半导体层上形成第一半导体层及第二半导体层;通过固相成长,提高第一半导体层及第二半导体层的结晶度,来形成第二单晶半导体层;在第二单晶半导体层上形成具有与第一杂质半导体层相反的导电型的第二杂质半导体层;在第二杂质半导体层上形成第二电极。

Description

技术领域

技术领域涉及一种利用单晶半导体的光电转换装置的制造方法。

背景技术

由于产业的发达,世界的能量消耗量日趋增加。然而,主要使用的石油、煤炭、天然气等能源的消费是二氧化碳的产生源,也一般说是急剧的地球温暖化的主要原因。因此,近年来,作为代替能量的太阳光发电得到普及。

虽然有利用热的太阳光发电,但是很多太阳光发电是使用如下方式的:利用半导体的光电特性来将光能量转换为电能量。将这种用来将光能量转换为电能量的装置一般称为光电转换装置(或者,光电动势装置、太阳能电池等)。

光电转换装置已经在市场上出售,并且由于世界各国政府的太阳能电池支援政策的缘故,其生产量逐年增加。例如,2006年的全世界的太阳能电池的生产量为2521MW,以超过年率40%的速度增加。在此,在世界上得到普及的是利用晶体半导体的光电转换装置,其中利用单晶硅衬底或多晶硅衬底的光电转换装置占有生产量的大部分。

作为光电转换装置的结构,建议了各种各样的方案。例如,除了在单晶硅衬底或多晶硅衬底中形成有n型或p型扩散层的典型结构以外,还已知组合由单晶半导体或多晶半导体构成的单元元件和由非晶半导体或微晶半导体构成的单元元件而成的结构(例如,参照专利文件1)。而且,也在此情况下,利用单晶硅衬底或多晶硅衬底。

随着如上所述的光电转换装置的生产量的增加,为单晶硅或多晶硅的原料的硅的供给不足、价格昂贵成为产业界的重大的问题。虽然世界的各大硅供给厂商公司已经谋求实现硅生产能力的增强,但是需求的增长超过其,预计无法消除供给不足。

在利用晶体硅的情况下,若是硅薄膜的厚度为10μm左右,就足够。然而,一般制造的单晶硅晶片的厚度为600μm以上且800μm以下左右,并且多晶硅晶片的厚度为200μm以上且350μm以下左右。就是说,单晶硅衬底或多晶硅衬底具有光电转换装置所需要的厚度的几十倍的厚度,而难说有效地利用原料。在这一点上,可以说现有的光电转换装置还有改善的余地。

近年来,对于包括形成在具有绝缘表面的衬底上的单晶硅薄膜的SOI(Silicon On Insulator;绝缘体上硅)结构的开发积极地进行。虽然SOI衬底是昂贵的,但是若可以用便宜的衬底如玻璃衬底等代替支撑衬底,则与利用单晶硅衬底的情况相比可以谋求实现低成本化。此外,还可以降低作为原料的硅的消耗量。作为这种技术,公开了将单晶硅薄膜固定到玻璃衬底的SOI衬底的制造方法(例如,参照专利文件2)。

[专利文件1]日本公告公报Hei6-044638号公报

[专利文件2]日本专利申请公开Hei11-097379号公报

与SIMOX法、在贴合后利用磨削或抛光进行薄膜化的方法等相比,当利用氢离子注入剥离法时,可以以低温形成均匀的单晶硅薄膜。此外,可以再次利用将单晶硅薄膜分离后的单晶硅衬底,而可以谋求实现资源的有效利用。

当利用氢离子注入剥离法时,根据离子的加速电压而决定相对于单晶硅衬底的离子的侵入深度,并且决定所得到的单晶硅薄膜的厚度,但是,考虑到光电转换效率,则优选将单晶硅薄膜的厚度设定为800nm以上。

另一方面,对离子注入装置的加速电压有装置上的限制,并且,有如下担心:当提高加速电压时,发生在安全上成为问题的放射线。因此,为了得到所希望的厚度的单晶硅薄膜而提高加速电压是不容易的。此外,在现有的装置中,在提高加速电压的同时照射大量离子是困难的,所以有如下担心:为了得到预定的注入量而需要很长时间,而生产节拍时间(tact time)恶化。

发明内容

鉴于上述问题,所公开的发明的一种方式的目的之一在于在有效地利用有限的资源的同时,安全提供具有优越的光电转换特性的光电转换装置。

在本说明书等(至少包括说明书、权利要求书、以及附图)所公开的发明的一种方式中,通过利用固相成长(固相外延成长)法,使单晶半导体层厚膜化。更具体地,通过如下那样的工序,制造单晶半导体层。首先,在使单晶半导体衬底薄片化而形成的单晶半导体层上形成薄的结晶度高的半导体层。并且,在该结晶度高的半导体层上形成厚的结晶度低的半导体层。然后,对上述的叠层结构施行加热处理等,通过固相成长来形成厚的单晶半导体层。

上述的“结晶度高的半导体层”可以通过使用硅烷类气体和氢的混合气体且利用等离子体CVD法来形成。例如,可以通过对混合气体包含相对于该硅烷类气体的流量比为50倍以上、优选为100倍以上的氢,来形成。而且,上述“结晶度高的半导体层”大大受到通过薄片化而形成的单晶半导体层的结晶度的影响,所以也可以将上述制造方法特别称为气相成长(气相外延成长)法。然而,其结晶度不局限于单晶,而只要其结晶度高于后面形成的“结晶度低的半导体层”的结晶度,就可以。

“结晶度低的半导体层”可以通过利用任一方法来形成。例如,与上述“结晶度高的半导体层”同样,可以通过使用硅烷类气体和氢的混合气体且利用等离子体CVD法来形成。在此情况下,优选使用与上述的“结晶度高的半导体层”的情况相比成膜速度高的条件。例如,可以通过使用对混合气体包含相对于该硅烷类气体的流量比为2倍以上且20倍以下(优选为5倍以上且15倍以下)的氢而成的原料气体来形成。

所公开的发明的一种方式的光电转换装置的制造方法包括如下步骤。首先,通过对单晶半导体衬底照射离子,在单晶半导体衬底中形成脆化层,并且在单晶半导体衬底的一个表面上形成第一杂质半导体层、第一电极以及绝缘层。接着,通过在将绝缘层和支撑衬底贴紧来将单晶半导体衬底和支撑衬底贴在一起,在脆化层中分离单晶半导体衬底,以在支撑衬底上形成包括绝缘层、第一电极、第一杂质半导体层及第一单晶半导体层的叠层体。接着,在第一单晶半导体层上形成第一半导体层,并且在第一半导体层上利用与第一半导体层不同的制造条件而形成第二半导体层,并且通过固相成长,提高第一半导体层及第二半导体层的结晶度,来形成第二单晶半导体层。并且,在第二单晶半导体层上形成具有与第一杂质半导体层相反的导电型的第二杂质半导体层,并且在第二杂质半导体层上形成第二电极。

在上述中,以第一半导体层的结晶度高于第二半导体层的结晶度的方式形成第一半导体层及第二半导体层即可。此外,以第一半导体层的氢浓度低于第二半导体层的氢浓度的方式形成第一半导体层及第二半导体层即可。此外,优选使第二半导体层的成膜速度大于第一半导体层的成膜速度。

而且,将第一半导体层的厚度设定为5nm以上且100nm以下(优选为10nm以上且50nm以下)左右。此外,优选以第一单晶半导体层和第二单晶半导体层的厚度的合计成为800nm以上的方式形成第一单晶半导体层和第二单晶半导体层。此外,作为上述离子,优选使用由包含氢的原料气体生成的离子。

此外,在上述中,可以将第一杂质半导体层设定为p型杂质半导体层,并且将第二杂质半导体层设定为n型杂质半导体层。当然,也可以将第一杂质半导体层设定为n型杂质半导体层,并且将第二杂质半导体层设定为p型杂质半导体层。

在上述中,通过将相对于硅烷类气体的氢(气体)的流量比设定为50倍以上的等离子体化学气相成长法来形成第一半导体层即可。由此,可以形成结晶度高(氢浓度低)的第一半导体层。在此,作为硅烷类气体,使用甲硅烷或乙硅烷即可。此外,等离子体化学气相成长法优选在1Pa以上且103Pa以下的压力下进行。

而且,在本说明书中,单晶是指结晶结构以具有一定的规律性的方式形成且结晶轴在哪部分都朝向一定方向的。但是,在本说明书中,不除外使结晶结构的规律性错乱的缺陷、晶格畸变等。

在所公开的发明的一种方式中,利用外延成长技术而谋求实现单晶半导体层的厚膜化。因此,可以在抑制原料的消耗量的同时谋求实现光电转换效率的提高。此外,因为使单晶半导体衬底的表层部薄片化且用作单晶半导体层,所以可以降低为原料的单晶半导体的消耗量。此外,因为没必要将单晶半导体层形成得厚,所以可以消除起因于离子照射时的加速电压的各种问题。再者,可以重复利用将单晶半导体层分离后的单晶半导体衬底。

而且,在所公开的发明的一种方式中,在单晶半导体层上形成结晶半导体层(也可以称为缓冲层)后,在结晶半导体层上形成结晶度低的半导体层(例如,非晶半导体层)。由此,可以防止当进行外延成长时的加热处理等所引起的半导体层的剥离。就是说,可以通过利用外延成长法成品率好地形成具有足够的厚度的单晶半导体层。

如上所述,通过利用所公开的发明的一种方式,可以有效地利用资源,并且提供具有优越的光电转换特性的光电转换装置。

附图说明

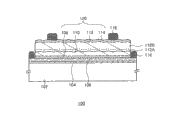

图1是表示光电转换装置的实例的截面图;

图2是表示光电转换装置的实例的平面图;

图3A至3D是表示光电转换装置的制造方法的实例的截面图;

图4A至4C是表示光电转换装置的制造方法的实例的截面图;

图5A至5C是表示光电转换装置的制造方法的实例的截面图;

图6A和6B是表示光电转换装置的制造方法的实例的截面图;

图7A和7B是对应于光电转换装置的单元元件的截面图的能带图;

图8是表示光电转换装置的实例的截面图;

图9A至9C是表示从圆形的单晶半导体衬底切割出预定形状的半导体衬底的方式的图;

图10A至10D是表示光电转换装置的制造方法的实例的截面图;

图11A至11D是表示光电转换装置的制造方法的实例的截面图;

图12A至12D是表示光电转换装置的制造方法的实例的截面图;

图13A和13B是表示光电转换装置的制造方法的实例的截面图;

图14是表示串联型光电转换装置的实例的截面图;

图15A和15B是表示串联型光电转换装置的制造方法的实例的截面图;

图16A和16B是表示串联型光电转换装置的制造方法的实例的截面图;

图17A和17B是对应于串联型光电转换装置的单元元件的截面图的能带图;

图18是表示叠层型光电转换装置的实例的截面图;

图19A和19B是对应于叠层型光电转换装置的单元元件的截面图的能带图;

图20是表示光电转换装置的制造方法的实例的截面图;

图21是表示离子掺杂装置的结构的示意图;

图22是表示光电转换装置的实例的截面图;

图23A和23B是说明太阳光发电模块的结构的示意图;

图24是说明太阳光发电系统的实例的示意图;

图25是表示实施例中的观察结果的图。

具体实施方式

参照附图详细说明实施方式。但是,所属技术领域的普通技术人员当然知道如下事实,即发明不局限于以下所示的实施方式所记载的内容,而其形式及详细内容可以在不脱离其宗旨的情况下被变换为各种各样的方式。此外,可以适当地组合根据不同的实施方式的结构来实施。而且,在以下说明的发明的结构中,对相同的部分或具有同样的功能的部分使用相同的附图标记,而省略其重复说明。

实施方式1

图1表示根据本实施方式的光电转换装置100的截面的示意图。此外,图2表示根据本实施方式的光电转换装置100的顶面的示意图(平面图)。而且,图1是对应于图2中的O-P切断线的截面图的一例。

本实施方式所示的光电转换装置100具有如下结构:在支撑衬底102上依次层叠有绝缘层104、第一电极106、单元元件120。在此,单元元件120具有由一种导电型的第一杂质半导体层108、第一单晶半导体层110、第二单晶半导体层112、第二杂质半导体层114构成的叠层结构。

在上述第一电极106中的不形成有单元元件120的区域中形成有辅助电极116,由此,可以将电能取出到外部。此外,在单元元件120上形成有第二电极118。就是说,用来将电能取出到外部的电极被形成为露出在支撑衬底102的一个表面上。而且,第二电极118的形状是格子状(梳状、梳形、梳齿状)。通过采用这种形状,可以使单元元件120的受光面积足够大。

支撑衬底102是具有绝缘表面的衬底或绝缘衬底。作为该绝缘衬底,例如可以使用铝硅酸盐玻璃、铝硼硅酸盐玻璃、钡硼硅酸盐玻璃等的用于电子工业的各种玻璃衬底。或者,除了上述玻璃衬底以外,还可以使用:陶瓷衬底、石英衬底、蓝宝石衬底等由绝缘体构成的绝缘衬底;对由金属或不锈钢等导电体构成的衬底的表面进行绝缘处理而成的衬底等。

绝缘层104具有将支撑衬底102和第一电极106贴在一起的功能。在这种意思上,可以将绝缘层104称为接合层。此外,因为第一电极106以接触于单元元件120的方式被形成,所以单元元件120被绝缘层104固定到支撑衬底102。

而且,绝缘层104的涉及与支撑衬底102(或第一电极106)的贴合的表面优选具有一定的平坦性。这是因为如下缘故:通过具有一定的平坦性,实现坚固的贴合。例如,将绝缘层104形成为其平均面粗糙度(Ra)成为0.5nm以下。更优选为0.3nm以下。而且,本说明书中的平均面粗糙度(Ra)是指将JIS B0601所定义的中心线平均粗糙度扩大为能够应用于面的。

在单元元件120中,第一杂质半导体层108和第二杂质半导体层114是添加有赋予预定的导电型的杂质元素的半导体层。在此,第一杂质半导体层108和第二杂质半导体层114被赋予有不同的导电型。就是说,在将第一杂质半导体层108设定为p型的情况下,第二杂质半导体层114成为n型,并且在将第一杂质半导体层108设定为n型的情况下,第二杂质半导体层114成为p型。作为赋予p型的杂质元素,可以使用硼、铝等第13族元素,并且,作为n型杂质元素,可以使用磷、砷等第15族元素。

第一单晶半导体层110和第二单晶半导体层112典型地由单晶硅形成。在此,第二单晶半导体层112具有其制造方法不同的下层区域112A和上层区域112B。而且,当第一单晶半导体层110的导电型和第二杂质半导体层114的导电型不同时,第一单晶半导体层110可以具有作为第一杂质半导体层108的功能,所以可以采用不设置第一杂质半导体层108的结构。

第一单晶半导体层110可以通过分割单晶半导体衬底来形成。例如,通过对单晶半导体衬底中以高浓度引入氢等离子,并且在该离子引入区域中分割单晶半导体衬底,来形成第一单晶半导体层110。作为上述单晶半导体衬底,使用单晶硅晶片即可。此外,也可以通过利用如下方法,来形成第一单晶半导体层110,即在多孔质半导体层(典型为多孔质硅层)上使单晶半导体层外延成长后,利用水射流(water-jetting)等进行分离。

第二单晶半导体层112以形成在第一单晶半导体层110上的半导体层为基础来形成。具体地,通过对该半导体层进行加热处理,进行以第一单晶半导体层110为晶种(seed crystal)的固相成长(SPE;Solid Phase Epitaxy),来形成第二单晶半导体层112。

在此,作为成为第二单晶半导体层112的基础的半导体层,使用具有叠层结构的半导体层。更具体地,使用由第一单晶半导体层上的结晶度高的第一半导体层和该第一半导体层上的结晶度低的第二半导体层构成的叠层结构。或者,也可以使用由第一单晶半导体层上的氢浓度低(氢含量小)的第一半导体层和该第一半导体层上的氢浓度高(氢含量大)的第二半导体层构成的叠层结构。而且,通过加热处理,第一半导体层成为第二单晶半导体层112的下层区域112A,并且第二半导体层成为第二单晶半导体层112的上层区域112B。

当考虑到光电转换效率时,优选将第一单晶半导体层110和第二单晶半导体层112的厚度的合计设定为800nm以上。更优选为1000nm以上。优选将第一单晶半导体层的厚度设定为5nm以上且500nm以下(更优选为300nm以下)左右,并且将第二单晶半导体层的厚度设定为300nm以上(更优选为500nm以上)。虽然对成为第二单晶半导体层的基础的第一半导体层及第二半导体层的厚度没有特别的限制,但是优选将第二半导体层形成得厚于第一半导体层。这是因为如下缘故:在其特性上,第一半导体层的成膜速度有小于第二半导体层的成膜速度的趋势。例如,可以将第一半导体层设定为5nm以上且100nm以下(优选为10nm以上且50nm以下),并且将第二半导体层设定为200nm以上(优选为400nm以上)。

而且,有上述第一单晶半导体层110和第二单晶半导体层112的导电型不同的情况。例如,利用p型单晶半导体衬底而制造的第一单晶半导体层110成为p型,并且利用n型单晶半导体衬底而制造的第一单晶半导体层110成为n型。另一方面,在形成时的原料气体不包含赋予导电型的杂质的情况下,第二单晶半导体层112成为i型(本征半导体)。

下面,参照图3A至图6B说明根据本实施方式的光电转换装置100的制造方法的一例。

首先,准备单晶半导体衬底103。对该单晶半导体衬底103来说,在离其一个表面有预定深度的区域中形成有脆化层105,并且在其一个表面附近形成有第一杂质半导体层108。此外,在单晶半导体衬底103的一个表面上(第一杂质半导体层108上)按顺序形成有第一电极106和绝缘层104(参照图3D)。

对脆化层105、第一杂质半导体层108、第一电极106、绝缘层104的形成顺序没有特别的限制,而例如可以采用下面的(1)至(4)所示的顺序。

(1)在单晶半导体衬底的一个表面上形成保护层,从该保护层的表面照射赋予一种导电型的杂质元素,来在单晶半导体衬底的一个表面一侧形成第一杂质半导体层之后,从保护层的表面照射离子,以在单晶半导体衬底的预定的深度的区域中形成脆化层。在去除保护层之后,在第一杂质半导体层上形成第一电极,并且在该第一电极上形成绝缘层。

(2)在单晶半导体衬底的一个表面上形成保护层,对该保护层的表面照射离子,来在单晶半导体衬底的预定的深度的区域中形成脆化层之后,从保护层的表面照射赋予一种导电型的杂质元素,以在单晶半导体衬底的一个表面一侧形成第一杂质半导体层。在去除保护层之后,在第一杂质半导体层上形成第一电极,并且在该第一电极上形成绝缘层。

(3)在单晶半导体衬底的一个表面上形成第一电极。对该第一电极的表面照射赋予一种导电型的杂质元素,来在单晶半导体衬底的一个表面一侧形成第一杂质半导体层。再者,对第一电极的表面照射离子,在单晶半导体衬底的预定的深度的区域中形成脆化层之后,在第一电极上形成绝缘层。

(4)在单晶半导体衬底的一个表面上形成第一电极。对该第一电极的表面照射离子,在单晶半导体衬底的预定的深度的区域中形成脆化层。再者,对第一电极的表面照射赋予一种导电型的杂质元素,在单晶半导体衬底的一个表面一侧形成第一杂质半导体层。并且,在第一电极上形成绝缘层。

而且,在本实施方式中,参照图3A至3D说明上述(1)的情况。

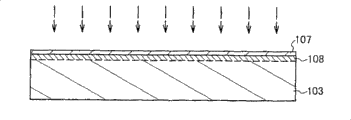

首先,在单晶半导体衬底103的一个表面上形成保护层107。并且,通过对保护层107的表面照射赋予一种导电型的杂质元素,对单晶半导体衬底103添加杂质元素,以形成第一杂质半导体层108(参照图3A)。

作为单晶半导体衬底103,可以使用硅或锗等半导体晶片、砷化镓或磷化铟等化合物半导体晶片等。其中,优选使用单晶硅晶片。对单晶半导体衬底103的平面形状没有特别的限制,但是在后面要固定的支撑衬底是矩形的情况下,优选将单晶半导体衬底103也设定为矩形。此外,单晶半导体衬底103的表面优选进行镜面抛光。

而且,在市场上流通的单晶硅晶片的多半是圆形,当使用这种圆形晶片时,将其加工为矩形或多角形即可。例如,如图9A至9C所示,可以从圆形的单晶半导体衬底101(参照图9A)切割出矩形的单晶半导体衬底103a(参照图9B)、多角形的单晶半导体衬底103b(参照图9C)。

而且,图9B表示切割出内接于圆形的单晶半导体衬底101且其面积成为最大的矩形的单晶半导体衬底103a的情况。在此,单晶半导体衬底103a的角部(顶点)的角度大约为90度。此外,图9C表示切割出其对边的间隔长于上述单晶半导体衬底103a的对边的间隔的单晶半导体衬底103b的情况。在此情况下,单晶半导体衬底103b的角部(顶点)的角度不是90度,并且该单晶半导体衬底103b是多角形,而不是矩形。

作为保护层107,优选使用氧化硅或氮化硅。作为制造方法,例如利用等离子体CVD法、溅射法等即可。此外,也可以通过使用氧化性的药液或氧基对单晶半导体衬底103进行氧化处理,形成保护层107。再者,还可以通过利用热氧化法使单晶半导体衬底103的表面氧化来形成保护层107。通过形成保护层107,当在单晶半导体衬底103中形成脆化层时,或者当对单晶半导体衬底添加赋予一种导电型的杂质元素时,可以防止衬底表面受到损坏。

第一杂质半导体层108通过对单晶半导体衬底103添加赋予一种导电型的杂质元素来形成。而且,因为在单晶半导体衬底103上形成有保护层107,所以赋予一种导电型的杂质元素经过保护层107而添加到单晶半导体衬底103。在此,将第一杂质半导体层108的厚度设定为30nm至150nm、优选为50nm至100nm。

作为上述赋予一种导电型的杂质元素,例如使用硼。由此,可以形成p型第一杂质半导体层108。而且,第一杂质半导体层108也可以通过热扩散法来形成。但是,因为在热扩散法中进行900℃左右或其以上的高温处理,所以需要在形成脆化层之前进行。

通过上述方法来形成的第一杂质半导体层108被配置在与光入射面相反一侧的面上。在此,当使用p型衬底作为单晶半导体衬底103时,第一杂质半导体层108成为高浓度p型区域。由此,从与光入射面相反一侧按顺序配置高浓度p型区域和低浓度p型区域,以形成背面电场(BSF;Back Surface Field)。就是说,电子不能进入高浓度p型区域,因此可以降低由于光激发而发生的载流子的重新组合。

接着,对保护层107的表面照射离子,在单晶半导体衬底103中形成脆化层105(参照图3B)。在此,作为上述离子,优选使用利用包含氢的原料气体而生成的离子(特别为H+、H2 +、H3 +等)。而且,形成脆化层105的深度由照射离子时的加速电压控制。此外,根据形成脆化层105的深度,决定从单晶半导体衬底103分离的单晶半导体层的厚度。

在离单晶半导体衬底103的表面(正确的是第一杂质半导体层的表面)有500nm以下的深度、优选有400nm以下的深度、更优选有50nm以上且300nm以下的深度的区域中形成脆化层105。通过在浅区域中形成脆化层105,分离后的单晶半导体衬底残留得厚,所以可以增加单晶半导体衬底的重复利用次数。但是,当在浅区域中形成脆化层105时,需要降低加速电压,而必须考虑到生产率等。

上述离子的照射可以通过利用离子掺杂装置、离子注入装置来进行。因为离子掺杂装置通常不伴随质量分离,所以即使单晶半导体衬底103大型化,也可以对单晶半导体衬底103的整个表面均匀地照射离子。

图21表示离子掺杂装置的结构的一例。对离子源2000从气体供应部2004供应氢等原料气体。此外,离子源2000具有灯丝2001。灯丝电源2002对灯丝2001施加电弧放电电压,调节流过灯丝2001的电流。从气体供应部2004供应的原料气体由排气系统排气。

供应到离子源2000的氢等通过与从灯丝2001放出的电子之间的反应而离子化。这样生成的离子由引出电极2005加速,以形成离子束2017。离子束2017被照射到设置于衬底支撑部2006的单晶半导体衬底103。而且,离子束2017所包含的离子的构成比由设置于衬底支撑部2006的附近的质量分析管2007测定。此外,质量分析管2007的测定结果通过质量分析计2008进行信号转换,而被反馈到电源控制部2003。由此,可以控制离子的构成比。

而且,因为经过第一杂质半导体层108照射上述离子束,所以也可以进行第一杂质半导体层108的氢化。

在形成上述脆化层105之后,去除保护层107,在第一杂质半导体层108上形成第一电极106(参照图3C)。

在此,第一电极106必须能够忍受后面的工序中的热处理。因此,第一电极106优选使用难熔金属材料来形成。例如,可以使用钛、钼、钨、钽、铬、镍等。此外,也可以采用由上述的金属材料和金属材料的氮化物构成的叠层结构。例如,也可以使用由氮化钛层和钛层构成的叠层结构、由氮化钽层和钽层构成的叠层结构、由氮化钨层和钨层构成的叠层结构等。当采用上述那样的利用氮化物的叠层结构时,以与第一杂质半导体层108接触的方式形成氮化物即可。通过这样形成氮化物,可以提高第一电极106和第一杂质半导体层108的紧密性。而且,第一电极106可以通过利用蒸镀法、溅射法来形成。此外,优选将其厚度设定为100nm以上。

接着,在第一电极106上形成绝缘层104(参照图3D)。虽然绝缘层104可以是单层结构或两层以上的叠层结构,但是其表面优选具有高平坦性。此外,其最外表面优选具有亲水性。作为上述绝缘层104,例如可以形成氧化硅层、氮化硅层、氧氮化硅层、氮氧化硅层等。作为绝缘层104的形成方法,可以举出等离子体CVD法、光CVD法、热CVD法等CVD法。特别地,通过应用等离子体CVD法,可以形成其平均面粗糙度(Ra)为0.5nm以下(优选为0.3nm以下)的平坦的绝缘层104。

在此,氧氮化硅是指在其组成上氧的含量多于氮的含量,例如是指以50原子%以上且70原子%以下的范围包含氧,以0.5原子%以上且15原子%以下的范围包含氮,以25原子%以上且35原子%以下的范围包含硅,并且以0.1原子%以上且10原子%以下的范围包含氢。此外,氮氧化硅是指在其组成上氮的含量多于氧的含量,例如是指以5原子%以上且30原子%以下的范围包含氧,以20原子%以上且55原子%以下的范围包含氮,以25原子%以上且35原子%以下的范围包含硅,并且以10原子%以上且25原子%以下的范围包含氢。但是,上述范围是在利用卢瑟福背散射光谱学法(RBS:RutherfordBackscattering Spectrometry)、氢前方散射法(HFS:HydrogenForward Scattering)来测定的情况下的范围。此外,构成元素的含有比率的合计不超过100原子%。

而且,作为上述绝缘层104,特别使用通过使用有机硅烷且利用化学气相成长法来制造的氧化硅层即可。作为有机硅烷,可以使用四乙氧基硅烷(tetraethoxysilane)(TEOS:Si(OC2H5)4)、三甲基硅烷(TMS:(CH3)3SiH)、四甲基环四硅氧烷(TMCTS)、八甲基环四硅氧烷(OMCTS)、六甲基二硅氮烷(HMDS)、三乙氧基硅烷(SiH(OC2H5)3)、三二甲氨基硅烷(SiH(N(CH3)2)3)等。当然,也可以通过利用甲硅烷、乙硅烷或丙硅烷等无机硅烷来形成氧化硅、氧氮化硅、氮化硅、氮氧化硅等。

此外,在绝缘层104具有叠层结构的情况下,优选采用包括氮化硅层、氮氧化硅层等包含氮的硅绝缘层的叠层结构。由此,可以防止来自支撑衬底102的碱金属、碱土金属等所引起的半导体的污染。而且,优选将绝缘层104形成为其厚度成为5nm至500nm左右。

而且,在第一电极106的表面具有一定的平坦性的情况下,具体地说,在其平均面粗糙度(Ra)为0.5nm以下(优选为0.3nm以下)的情况下,有即使不形成绝缘层104也可以实现贴合的情况。在此情况下,也可以采用不形成绝缘层104的结构。

接着,通过使上述绝缘层104的一个表面和支撑衬底102的一个表面贴紧且进行加压,将单晶半导体衬底103上的叠层结构和支撑衬底102贴在一起(参照图4A)。

此时,对涉及贴合的表面(在此,绝缘层104的一个表面和支撑衬底102的一个表面)进行足够的清洁化。这是因为如下缘故:当在涉及贴合的表面上存在有微小的尘埃等时,贴合不良的发生几率提高。而且,也可以使涉及贴合的表面活化,以降低贴合不良。例如,通过对涉及贴合的表面的一方或双方照射原子束或离子束,可以使其表面活化。此外,也可以通过利用等离子体处理、药液处理等来进行活化。如此,通过使涉及贴合的表面活化,即使在400℃以下的温度下也可以实现良好的贴合。

而且,也可以采用如下结构:在支撑衬底102上形成氮化硅层、氮氧化硅层等含有氮的硅绝缘层,并且将其与绝缘层104贴紧。在此情况下,也可以防止来自支撑衬底102的碱金属、碱土金属等所引起的半导体的污染。

接着,通过进行热处理,来加强贴合。此时的温度必须以脆化层105中不进行分离为条件。例如,可以将其设定为不足400℃、优选为300℃以下。对热处理时间没有特别的限制,而根据处理速度和贴合强度的关系适当地设定最适的条件即可。作为一例,可以采用200℃、2小时程度的热处理条件。在此,也可以仅对涉及贴合的区域照射微波,进行局部性的热处理。而且,在对贴合强度没有问题的情况下,也可以省略上述加热处理。

接着,在脆化层105中,将单晶半导体衬底103分离为分离衬底109和第一单晶半导体层110(参照图4B)。单晶半导体衬底103的分离通过热处理来进行。至于该热处理的温度,可以将支撑衬底102的耐热温度作为基准。例如,在使用玻璃衬底作为支撑衬底102的情况下,热处理温度优选为400℃以上且650℃以下。但是,若是短时间,则也可以进行400℃以上且700℃以下的热处理。当然,在玻璃衬底的耐热温度高于700℃的情况下,也可以将热处理温度设定得高于700℃。

通过进行上述那样的热处理,形成于脆化层105中的微小的空孔发生体积变化,而在脆化层105中发生裂缝。其结果,沿着脆化层105,单晶半导体衬底103分离。因为绝缘层104与支撑衬底102贴在一起,所以在支撑衬底102上残留从单晶半导体衬底103分离的第一单晶半导体层110。此外,通过该热处理,支撑衬底102和绝缘层104的涉及贴合的界面被加热,所以在涉及贴合的界面形成共价键,而进一步提高支撑衬底102和绝缘层104的结合力。

而且,第一单晶半导体层110和第一杂质半导体层108的厚度的合计大体上对应于形成脆化层105的深度,而成为500nm以下、优选为400nm以下、更优选为50nm以上且300nm以下。

通过上述工序,可以得到固定在支撑衬底102上的第一单晶半导体层110。而且,对分离衬底109来说,在进行再生处理之后,可以再次利用。再生处理后的分离衬底109既可以用于用来得到单晶半导体层的衬底(在本实施方式中,对应于单晶半导体层103),又可以用于其他用途。在用于用来得到单晶半导体层的衬底的情况下,可以使用一个单晶半导体衬底制造多个光电转换装置。

接着,在第一单晶半导体层110上形成第一半导体层111A(参照图4C)。例如,通过利用气相成长(气相外延成长)法来形成第一半导体层111A(参照图4C)。在此情况下,第一半导体层111A成为受到第一单晶半导体层110的结晶度的影响的半导体层。在此,根据第一单晶半导体层110来选择材料并形成第一半导体层111A即可。在形成硅层作为第一半导体层111A的情况下,例如可以通过以硅烷类气体(典型为硅烷)和氢的混合气体为原料且利用等离子体CVD法来形成。此外,将第一半导体层111A形成为其厚度成为10nm以上且100nm以下(优选为10nm以上且50nm以下)左右即可。

上述原料气体是相对于硅烷类气体的氢的流量比为50倍以上(优选为100倍以上)的混合气体。例如,以4sccm∶400sccm的比例混合硅烷(SiH4)和氢来使用即可。通过提高氢的流量,可以形成结晶度高的半导体层。由此,可以降低半导体层中的氢含量。

而且,不局限于使用硅烷作为硅烷类气体,也可以使用乙硅烷(Si2H6)等。此外,也可以对上述原料气体添加稀有气体。

当利用等离子体CVD法来形成第一半导体层111A时的其他条件为如下:频率为10MHz至200MHz、功率为5W以上且50W以下、反应室内的压力为10Pa以上且103Pa以下、电极间隔(平行平板型时)为15mm以上且30mm以下、支撑衬底102的温度为200℃以上且400℃以下,典型地说,分别为60MHz、15W、100Pa、20mm、280℃。而且,上述的成膜条件不过是一例,而所公开的发明的一种方式不被解释为仅局限于此。这里,重要的点是,形成结晶度高的半导体层(或氢浓度低的半导体层、氢含量小的半导体层)作为第一半导体层111A,所以只要可以达成该目的,就可以利用任一方法来形成第一半导体层111A。

而且,优选在进行第一半导体层111A的外延成长之前去除形成在第一单晶半导体层110的表面上的自然氧化层等。这是因为如下缘故:当在第一单晶半导体层110的表面上存在有氧化层时,不能进行受到第一单晶半导体层110的结晶度的影响的外延成长,而降低第一半导体层111A的结晶度。在此,可以通过利用氢氟酸类的溶液等来进行上述氧化层的去除。

接着,在第一半导体层111A上形成第二半导体层111B(参照图5A)。在此,第二半导体层111B通过根据第一半导体层111A选择材料来形成。此外,将第二半导体层111B形成为其厚度成为200nm以上(优选为400nm以上)。在此情况下,也优选去除形成在第一半导体层111A的表面上的氧化层。

将第二半导体层111B设定为其结晶度低于第一半导体层111A的半导体层。或者,将第二半导体层111B设定为其氢浓度高于第一半导体层111A的半导体层(氢含量大的半导体层)。作为这种第二半导体层111B,例如形成非晶半导体层即可。

虽然第二半导体层111B的形成方法是任意的,但是优选以成膜速度至少高于第一半导体层111A的条件形成。例如,在通过以硅烷类气体(典型为硅烷)和氢气体的混合气体为原料且利用等离子体CVD法来形成第二半导体层111B的情况下,将相对于硅烷类气体的氢气体的流量比设定为2倍以上且20倍以下(优选为5倍以上且15倍以下)即可。此外,将频率设定为10MHz至200MHz,将功率设定为5W以上且50W以下,将反应室内的压力设定为10Pa以上且103Pa以下,将电极间隔(平行平板型时)设定为15mm以上且30mm以下,并且将支撑衬底102的温度设定为200℃以上且400℃以下即可。典型地,将硅烷(SiH4)的流量设定为25sccm,将氢的流量设定为150sccm,将频率设定为27MHz,将功率设定为30W,将压力设定为66.6Pa,将电极间隔设定为25mm,并且将衬底温度设定为280℃。而且,上述成膜条件不过是一例,而所公开的发明的一种方式不被解释为仅局限于此。这里,重要的点是,形成即使结晶度低(或氢浓度高)也成膜速度高的半导体层作为第二半导体层111B,所以只要可以达成该目的,就可以利用任一方法来形成第二半导体层111B。

然后,进行热处理,通过固相成长(固相外延成长)形成第二单晶半导体层112(参照图5B)。而且,第一半导体层111A对应于第二单晶半导体层112的下层区域112A,并且第二半导体层111B对应于第二单晶半导体层112的上层区域112B。

上述热处理可以通过利用RTA(Rapid Thermal Anneal;快速热退火)、炉(furnace)、毫米波加热装置等热处理装置来进行。作为热处理装置的加热方式,可以举出电阻加热方式、灯加热方式、气体加热方式、电磁波加热方式等。也可以进行激光束的照射、热等离子体喷射(thermal plasma jet)的照射。

一般而言,炉是外热式,并且反应室内和被处理物成为热平衡状态。另一方面,RTA是通过对被处理物直接供应能量来进行瞬间加热(快速加热)的,并且反应室内和被处理物成为热不平衡状态。作为RTA装置,可以举出灯加热方式的RTA(LRTA;Lamp RapidThermal Anneal)装置、使用被加热的气体的气体加热方式的RTA(GRTA;Gas Rapid Thermal Anneal)装置、或具备灯加热方式和气体加热方式的双方的RTA装置等。

在使用RTA装置的情况下,优选将处理温度设定为500℃以上且750℃以下,并且将处理时间设定为0.5分钟以上且10分钟以下。在使用炉的情况下,优选将处理温度设定为500℃以上且650℃以下,并且将处理时间设定为1小时以上且4小时以下。

通过上述,形成由第一单晶半导体层110和第二单晶半导体层112构成的叠层结构。在此,当考虑到光电转换效率时,光电转换装置被要求800nm以上的厚度的单晶半导体层。因此,例如在将第一单晶半导体层110的厚度设定为300nm的情况下,优选将第二单晶半导体层112的厚度至少设定为500nm以上。在此,为了形成具有500nm以上的厚度的第二单晶半导体层112,仅利用气相外延成长法在成膜速度方面不是优选的。另一方面,在仅利用固相外延成长法来形成第二单晶半导体层112的情况下,起因于固相成长(固相外延成长)时的热处理等而发生半导体层的剥离的问题。可以认为这起因于刚成膜之后的半导体层(例如,非晶半导体层)包含大量氢。

在本实施方式中,在利用气相成长(气相外延成长)将第一半导体层111A形成得薄之后,利用不同条件的气相成长(气相外延成长)将第二半导体层111B形成得厚,然后进行固相成长(固相外延成长)来形成具有为第一半导体层111A的下层区域112A和为第二半导体层111B的上层区域112B的第二单晶半导体层112。由此,可以在确保成膜速度的同时消除半导体层的剥离的问题。就是说,可以生产率好且成品率好地形成单晶半导体层。

而且,可以认为:如本实施方式,通过在单晶半导体层上形成由结晶度高的半导体层和结晶度低的半导体层构成的叠层结构,然后进行固相成长来降低剥离的问题是因为相邻的层彼此的结晶度的差别变小,而界面上的原子彼此的结合强化,结果紧密性提高的缘故。

在本实施方式中,在单晶半导体层(第一单晶半导体层110)和结晶度低的半导体层(第二半导体层111B)之间形成一个结晶度高的半导体层(第一半导体层111A),但是从上述理由来看,没必要所公开的发明的一种方式被解释为仅局限于此。就是说,也可以采用在单晶半导体层和结晶度低的半导体层之间设置多个结晶度不同的半导体层的结构。例如,在单晶半导体层上形成结晶度高的半导体层,在其上形成结晶度稍微高的半导体层,并且在其上形成结晶度低的半导体层。通过采用这种结构,可以进一步提高紧密性。

此外,从界面上的紧密力的观点来说,优选以尽可能地不接触于大气等的方式形成上述叠层结构。例如,优选在相同的反应室内连续形成第一半导体层111A和第二半导体层111B。

接着,对第二单晶半导体层112的一个表面一侧(不接触于第一单晶半导体层110的表面一侧)添加赋予与第一杂质半导体层108不同的导电型的杂质元素,来形成第二杂质半导体层114(参照图5C)。例如,作为杂质元素添加磷或砷,来形成n型第二杂质半导体层114。在应用玻璃衬底作为支撑衬底102的情况下,不能忍受热扩散法的处理温度,所以通过离子注入或离子掺杂添加杂质元素。

此外,也可以在第二单晶半导体层112上利用非晶半导体形成第二杂质半导体层114(参照图13A、图13B)。因为主要用作光电转换层的区域由单晶半导体层形成,所以即使利用非晶半导体形成第二杂质半导体层114,也不成为很大的问题。

而且,优选将第二杂质半导体层114的厚度设定为20nm以上且200nm以下左右、更优选为50nm以上且100nm以下左右。通过将第二杂质半导体层114形成得薄,可以防止第二杂质半导体层114中的载流子的重新组合。

通过上述,可以得到按顺序层叠有一种导电型的第一杂质半导体层108、第一单晶半导体层110、第二单晶半导体层112、与上述一种导电型不同的导电型的第二杂质半导体层114的单元元件120。

然后,对设置在第一电极106上的第一杂质半导体层108、第一单晶半导体层110、第二单晶半导体层112以及第二杂质半导体层114进行蚀刻,使第一电极106的一部分(优选为第一电极106的端部)露出(参照图6A)。

在此,使第一电极106的一部分露出是为了在以后形成辅助电极(或者辅助布线)的缘故。为了用作光电转换装置,需要能够从对应于正极和负极的电极取出电能,然而第一电极106的上部由单晶半导体层等覆盖,并且在第一电极的下方设置有支撑衬底102,所以难以直接取出电能。于是,通过对形成在第一电极106的上方的层的一部分进行蚀刻,来使第一电极106的一部分露出,以便可以形成能够引绕的辅助电极(或者辅助布线)。

具体地,在第二杂质半导体层114上利用抗蚀剂、氮化硅层等绝缘层形成掩模,并且利用该掩模进行蚀刻即可。蚀刻例如可以是利用NF3、SF6等氟类气体的干蚀刻,至少在能够充分确保第一电极106和形成在第一电极106的上方的层(第一杂质半导体层108、第一单晶半导体层110、第二单晶半导体层112、第二杂质半导体层114)的选择比的条件下进行即可。而且,在蚀刻后,去除不需要了的掩模。

虽然在本实施方式中示出在形成第二杂质半导体层114之后使第一电极106露出的实例,但是也可以在使第一电极106露出之后形成第二杂质半导体层114。

接着,形成接触于露出的第一电极106的辅助电极116以及第二杂质半导体层114上的第二电极118(参照图6B)。

辅助电极116被设置以便容易取出受到光电转换的电能。就是说,辅助电极116用作取出电极(也称为集电极)。

如图2所示,将第二电极118形成为当从上方来看时成为格子状(或者梳状、梳形、梳齿状)。通过采用这种形状,可以对单元元件120照射足够的光,而可以提高单元元件120的光吸收效率。对第二电极118的形状没有特别的限制,但是当然单元元件120(第二杂质半导体层114)上的第二电极118的面积越小,光吸收效率越提高。而且,第二电极118可以以与辅助电极116相同的工序形成。

辅助电极116和第二电极118通过使用铝、银、铅锡(焊料)等且利用印刷法等方法形成即可。例如,可以通过使用银膏且利用丝网印刷法形成。

通过上述,可以制造光电转换装置100。

而且,优选在单元元件120上形成具有反射防止功能的钝化层119(参照图8)。

作为钝化层119,使用其折射率为单元元件120的入射面(在本实施方式中,第一杂质半导体层114)和空气的中间的材料。此外,为了不妨碍对单元元件120的光的入射,使用具有相对于预定的波长的光的透射性的材料。通过使用这种材料,可以防止在单元元件120的入射面上的反射。而且,作为这种材料,例如可以举出氮化硅、氮氧化硅、氟化镁等。

钝化层119设置在辅助电极116和单元元件120之间以及第二电极118和单元元件120之间。例如,在单元元件120上形成钝化层119之后,对钝化层119进行蚀刻以使第二杂质半导体层114和第一电极106的一部分露出。然后,形成接触于第一电极106的辅助电极116和接触于第二杂质半导体层114的第二电极118。而且,也可以通过应用剥离(lift-off)法等来形成设置有开口部的钝化层119。

图7A示出光电转换装置的单元元件120的截面示意图的一例。虽然在此示出按顺序配置有以高浓度添加有p型杂质元素的第一杂质半导体层108(p+层)、p型的第一单晶半导体层110(p层)、i型的第二单晶半导体层112(i层)、添加有n型杂质元素的第二杂质半导体层114(n+层、或n层)的结构,但是所公开的发明的一种方式不被解释为仅局限于此。而且,在将单元元件120中的单晶半导体层设定为单晶硅的情况下,其带隙能量大约为1.12eV。此外,光(能量:hv)从第二杂质半导体层114一侧入射。

图7B是图7A所示的单元元件120的能带图。在此,Ec表示传导带的底部,并且Ev表示价电子带的顶部(top)。此外,Ef表示费密能级的能量。此外,Egc1是第一单晶半导体层110及第二单晶半导体层112的带隙能量。

起因于图7B所示的带结构(band structure),由于光激发而生成的电子向n+层(或n层)的方向流过,并且由于光激发而生成的空穴向p+层的方向流过。这是光电转换的基本原理。在此,为了提高光电转换的效率,增多由于光激发而发生的载流子的数量是很重要的。为了增多光激发载流子,使光吸收层(在本实施方式中,单晶半导体层)具有一定程度的厚度即可。在使用单晶硅作为光吸收层的情况下,根据单晶硅的光吸收系数、太阳光的光谱,将其厚度设定为800nm以上(优选为1000nm以上)即可。

在这一点上,在本实施方式中,利用外延成长技术来谋求实现单晶半导体层的厚膜化,并且将第一单晶半导体层110和第二单晶半导体层112的厚度的合计设定为800nm以上。因此,可以在单晶半导体层中发生足够的载流子,而可以提高光电转换效率。

如上所述,通过利用本实施方式所示的外延成长技术,可以得到用作光电转换层的800nm以上、优选为1000nm以上的单晶半导体层。由此,与利用块状单晶半导体衬底的情况相比,可以抑制单晶半导体的消耗量。而且,虽然以前支撑光电转换装置的结构体部分也由单晶半导体形成,但是通过利用使单晶半导体衬底薄片化而成的单晶半导体层,可以大幅度地降低单晶半导体的消耗量。此外,因为可以重复利用将单晶半导体层分离后的单晶半导体衬底,所以可以有效地利用资源。

再者,在本实施方式中,通过利用由结晶度高(氢浓度低、氢含量小)的第一半导体层和结晶度低(氢浓度高、氢含量大)的第二半导体层构成的叠层结构来形成第二单晶半导体层。由此,即使在将第二单晶半导体层形成得厚的情况下,也可以防止第二单晶半导体层的剥离。就是说,因为可以在将第二半导体层形成得足够厚以提高生产率的同时防止起因于第二半导体层的厚膜化的剥离,所以可以有效地、成品率好地仅使用必要最小限度的材料来形成具有必要的厚度的光电转换层。

本实施方式可以与其他实施方式适当地组合来使用。

实施方式2

在本实施方式中,将说明与上述的实施方式不同的光电转换装置的制造方法的实例。具体地,虽然在上述的实施方式中,以(1)为例而说明脆化层105、第一杂质半导体层108、第一电极106、绝缘层104的形成顺序,但是在本实施方式中将说明(2)、(3)、(4)的实例。而且,因为除了脆化层105、第一杂质半导体层108、第一电极106、绝缘层104的形成顺序以外与上述的实施方式同样,所以省略说明。

下面,参照图10A至10D说明(2)的实例。

首先,在单晶半导体衬底103的一个表面上形成保护层107。然后,对保护层107的表面照射离子,以在单晶半导体衬底103中形成脆化层105(参照图10A)。

接着,通过对保护层107的表面照射赋予一种导电型的杂质元素,对单晶半导体衬底103添加杂质元素,以形成第一杂质半导体层108(参照图10B)。而且,因为在此已形成有脆化层105,所以优选利用离子注入法或离子掺杂法来添加杂质元素。这是因为如下缘故:在利用像热扩散法那样的必要高温处理的方法的情况下,单晶半导体衬底103在脆化层105中分离的可能性很高。

然后,去除保护层107,以形成第一电极106(参照图10C)。并且,在第一电极106上形成绝缘层104(参照图10D)。此后的工序与上述的实施方式同样。

如此,在(2)中,对没有添加杂质元素的单晶半导体衬底照射离子来形成脆化层,所以实现脆化层的不均匀性的降低。

下面,参照图11A至11D说明(3)的实例。

首先,在单晶半导体衬底103的一个表面上形成第一电极106(参照图11A)。

接着,对第一电极106的表面照射离子,以在单晶半导体衬底103中形成脆化层105(参照图11B)。

然后,通过对第一电极106的表面照射赋予一种导电型的杂质元素,对单晶半导体衬底103添加杂质元素,以形成第一杂质半导体层108(参照图11C)。

然后,在第一电极106上形成绝缘层104(参照图11D)。此后的工序与上述的实施方式同样。

如此,因为在(3)中,第一电极106用作保护层,所以没必要另行设置保护层,而实现工序的缩短。

下面,参照图12A至12D说明(4)的实例。

首先,在单晶半导体衬底103的一个表面上形成第一电极106(参照图12A)。

接着,通过对第一电极106的表面照射赋予一种导电型的杂质元素,对单晶半导体衬底103添加杂质元素,以形成第一杂质半导体层108(参照图12B)。

然后,对第一电极106的表面照射离子,以在单晶半导体衬底103中形成脆化层105(参照图12C)。

并且,在第一电极106上形成绝缘层104(参照图12D)。此后的工序与上述的实施方式同样。

如此,因为在(4)中,第一电极106用作保护层,所以没必要另行设置保护层,而实现工序的缩短。

而且,本实施方式可以与其他实施方式适当地组合来使用。

实施方式3

在本实施方式中,将说明光电转换装置的制造方法的另外的实例。

图22示出将第一电极106和支撑衬底102直接贴合而形成的光电转换装置的实例。在第一电极106的表面为平坦的情况下,例如在第一电极106的表面的平均面粗糙度(Ra)为0.5nm以下、优选为0.3nm以下的情况下,即使不形成绝缘层104(参照图1等),也可以将第一电极106和支撑衬底102贴在一起。

上述贴合通过将受到足够的清洁化的第一电极106的表面和支撑衬底102的表面贴紧来进行。当然,也可以在贴合之前使第一电极106的表面、支撑衬底102的表面活化。此外,也可以在贴合之后进行热处理、加压处理。通过像本实施方式那样地形成其表面为平坦的第一电极106,没必要设置绝缘层104,而缩短工序。而且,上述记载不排除绝缘层104的形成。例如,可以说形成用作阻挡层的绝缘层等从可靠性提高的观点来看是优选的。

而且,本实施方式可以与其他实施方式适当地组合来使用。

实施方式4

在本实施方式中,将说明光电转换装置的制造方法的另外的实例。

在上述的实施方式中,有如下情况:在从单晶半导体衬底103薄片化而得到的第一单晶半导体层110的表面上留下起因于脆化层105的晶体缺陷(参照图4B)。在存在有这种晶体缺陷的情况下,有由于载流子的捕捉等而光电转换效率降低的担心。因此,优选进行晶体缺陷的恢复或去除。具体地,可以应用激光束的照射处理、蚀刻处理等。

在对第一单晶半导体层110进行蚀刻处理的情况下,可以去除其晶体缺陷。作为这种蚀刻,可以利用干蚀刻或湿蚀刻。

图20示出进行激光束的照射处理的实例。在对第一单晶半导体层110照射适当的强度的激光束180的情况下,第一单晶半导体层110的至少表面附近的区域熔化,并且以不熔化的固相区域为晶种进行重新单晶化(recrystallized)。由此,可以恢复第一单晶半导体层110的晶体缺陷。而且,在此,采用如下结构:通过使形成有第一单晶半导体层110的支撑衬底102移动,对第一单晶半导体层110的整个表面照射激光束180,但是所公开的发明的一种方式不被解释为仅局限于此。

虽然激光束180使第一单晶半导体层110的表面附近的区域熔化,但是支撑衬底102几乎不被加热。因此,在使用像玻璃衬底那样的耐热性低的支撑衬底的情况下是优选的。在此,当将激光束180的照射区域加热到支撑衬底的耐热温度以下的温度(例如,250℃以上且600℃以下左右)时,可以有效地进行缺陷的恢复,所以是优选的。而且,通过上述激光束180的照射处理、加热处理,在形成第一电极106的金属和第一杂质半导体层108的界面上形成硅化物,而容易流过电流。此外,通过上述激光束180的照射处理、加热处理,可以使第一杂质半导体层108活化。

作为激光束180的波长,选择从紫外光到可见光程度的波长即可。但是,不局限于此。作为激光振荡器,可以使用Ar激光器、Kr激光器、受激准分子(ArF、KrF、XeCl)激光器、CO2激光器、YAG激光器、YVO4激光器、YLF激光器、YAlO3激光器、GdVO4激光器、Y2O3激光器、红宝石激光器、变石激光器、Ti:蓝宝石激光器、铜蒸汽激光器、金蒸汽激光器等。

而且,优选在减压气氛或惰性气氛下进行激光束的照射。为了在减压气氛或惰性气氛下照射激光束,控制具有气密性的反应室的气氛,并且在该反应室内照射激光束即可。在不使用反应室的情况下,也可以通过对激光束的被照射面喷上氮气体等惰性气体,形成惰性气氛。

当进行上述激光束的照射处理时,也可以使用相移掩模等在第一单晶半导体层110的表面上形成凹凸。例如,可以使用10μm平方的图案互相配置的像所谓的两种不同颜色相间的方格花纹那样的相移掩模。通过该相移掩模照射激光束,可以形成依赖于掩模的图案的表面凹凸。通过设置这种表面凹凸,可以提高后面形成的半导体层的紧密性来抑制剥离。此外,根据起因于表面凹凸的散射效果、反射防止效果,可以提高光电转换效率。

而且,也可以将上述蚀刻处理和激光束的照射处理组合来使用。

本实施方式可以与其他实施方式适当地组合来使用。

实施方式5

在本实施方式中,将说明层叠多个单元元件的所谓的串联型光电转换装置的实例。而且,在本实施方式中,将说明层叠两个单元元件的情况。

图14示出根据本实施方式的串联型光电转换装置200的截面的示意图。光电转换装置200具有在支撑衬底102上层叠有单元元件120(也可以称为第一单元元件)和单元元件230(也可以称为第二单元元件)的结构。在支撑衬底102和单元元件120之间设置有第一电极106,并且在第一电极106和支撑衬底102之间设置有绝缘层104。在本实施方式中,支撑衬底102、绝缘层104、第一电极106、单元元件120的结构及制造方法与实施方式1同样,所以省略对于重复部分的说明。

光电转换装置200具有从附图中的上方(单元元件230的表面一侧)入射光的结构。此外,构成单元元件230的半导体层的带隙能量大于构成单元元件120的半导体层的带隙能量。具体地,例如,可以将非单晶半导体层用于单元元件230,并且将单晶半导体层用于单元元件120。通过层叠带隙不同的光电转换层,能够吸收的波长区域(wavelength range)扩大,而可以提高光电转换效率。特别地,对太阳光来说,其波长区域很广泛即从短波长一侧到长波长一侧,所以采用像本实施方式那样的结构是非常有效的。此外,通过在光入射一侧配置带隙大的光电转换层,可以有效地吸收光。

单元元件230具有在单元元件120上按顺序层叠有赋予有一种导电型的第三杂质半导体层222、非单晶半导体层224、赋予有与第三杂质半导体层222不同的导电型的第四杂质半导体层226的结构。在此,对第三杂质半导体层222赋予与单元元件120的第二杂质半导体层114相反的导电型。

作为单元元件230的非单晶半导体层224,例如可以使用非晶硅、微晶硅等。第三杂质半导体层222和第四杂质半导体层226是包含预定的导电型的杂质元素的非晶半导体层或微晶半导体层。除此以外,还可以使用非晶碳化硅等。在将第三杂质半导体层222设定为p型的情况下,第四杂质半导体层226成为n型,但是也可以将第三杂质半导体层222设定为n型,并且将第四杂质半导体层226设定为p型。

非单晶半导体层224可以通过等离子体CVD法来形成。例如,通过利用硅烷类的原料气体来形成非晶硅即可。而且,非单晶半导体层224也可以通过溅射法来形成。在使用非晶硅作为非单晶半导体层224的情况下,将其厚度设定为50nm以上且300nm以下、优选为100nm以上且200nm以下。因为非晶硅的带隙大约为1.75eV,所以通过采用这种厚度,可以充分吸收短于600nm的波长区域的光。

此外,也可以将微晶半导体(典型为微晶硅)用于非单晶半导体层224。在此情况下,在单元元件120上形成几nm左右的极薄的非晶半导体层之后,形成微晶半导体即可。通过这样做,可以防止从单晶半导体进行外延成长来形成单晶半导体层。而且,因为第三杂质半导体层222也可以由单晶半导体层形成,所以将几nm左右的薄的非晶半导体层形成在第二杂质半导体层114上或第三杂质半导体层222上即可。

在单元元件120的支撑衬底102一侧设置有第一电极106,并且在单元元件230的表面一侧设置有第二电极232。此外,设置有与第一电极106连接的辅助电极217、以及与第二电极232连接的辅助电极219。辅助电极217和辅助电极219用作取出在光电转换层中转换了的电能的取出电极(也称为集电极)。

在单元元件230由非单晶半导体形成的情况下,有载流子的使用寿命变短的趋势,并且有起因于此而光电转换效率降低的担心。为了防止此,在本实施方式中将第二电极232形成在衬底的整个表面上。在此,为了对单元元件230及单元元件120入射足够的光,利用太阳光的透射率高的材料来形成第二电极232。此外,将接触于第二电极232的辅助电极219设定为格子状(或者梳状、梳形、梳齿状)。

接着,参照图15A至图16B说明根据本实施方式的光电转换装置200的制造方法的一例。而且,因为直到第二杂质半导体层114的制造方法与实施方式1同样,所以在此省略说明。

在形成第二杂质半导体层114之后,在该第二杂质半导体层114上按顺序形成第三杂质半导体层222、非单晶半导体层224、第四杂质半导体层226(参照图15A)。

在此,将第三杂质半导体层222设定为与第二杂质半导体层114不同的导电型的非晶半导体层或微晶半导体层。例如,在第二杂质半导体层114是n型的情况下,将第三杂质半导体层222设定为p型的非晶半导体层(例如,p型的非晶硅层)或者p型的微晶半导体层(例如,p型的微晶硅层)。将第三杂质半导体层222的厚度设定为10nm以上且100nm以下左右即可。

此外,优选将非单晶半导体层224设定为不包含赋予导电型的杂质元素的本征半导体层(例如,i型的非晶硅层或者i型的非单晶硅层)。将其厚度设定为50nm以上且300nm以下、优选为100nm以上且200nm以下。

此外,将第四杂质半导体层226设定为与第三杂质半导体层222不同的导电型的非晶半导体层或微晶半导体层。例如,在第三杂质半导体层222是p型的情况下,将第四杂质半导体层226设定为n型的非晶半导体层(例如,n型的非晶硅层)或者n型的微晶半导体层(例如,n型的微晶硅层)。将第四杂质半导体层226的厚度设定为10nm以上且100nm以下左右即可。

第三杂质半导体层222、非单晶半导体层224、第四杂质半导体层226可以通过CVD法、溅射法来形成。而且,在利用等离子体CVD法等气相成长法来形成非单晶硅层的情况下,通过对原料气体添加乙硼烷等,可以赋予p型。另一方面,在想要赋予n型的情况下,对原料气体添加磷化氢等即可。

通过上述,可以得到按顺序层叠有赋予有一种导电型的第三杂质半导体层222、非单晶半导体层224、赋予有与第三杂质半导体层222不同的导电型的第四杂质半导体层226的单元元件230。

接着,在第四杂质半导体层226上形成第二电极232(参照图15B)。第二电极232可以通过溅射法、真空蒸镀法来形成。此外,第二电极232优选通过利用充分透射太阳光的材料来形成。作为上述材料,使用氧化铟·锡合金(ITO)、氧化铟·氧化锌合金、氧化锌、氧化锡等氧化物金属即可。将第二电极232形成为其厚度成为40nm以上且200nm以下左右(优选为50nm以上且100nm以下左右)且其薄层电阻成为20Ω/sq.以上且200Ω/sq.以下左右即可。

在本实施方式中,在单元元件230上选择性地形成第二电极232。例如,通过利用阴影掩模(shadow mask)来形成第二电极232。通过选择性地形成第二电极232,可以将其用作后面使第一电极106的一部分(优选为端部)露出时的蚀刻用掩模。

而且,也可以利用导电高分子材料(也称为导电聚合物)来形成第二电极232。作为导电高分子材料,可以使用π电子共轭类导电高分子。例如,使用聚苯胺、聚吡咯、聚噻吩或这些的衍生物、这些的两种以上的共聚物等即可。

接着,以第二电极232为掩模,对第四杂质半导体层226、非单晶半导体层224、第三杂质半导体层222、第二杂质半导体层114、第二单晶半导体层112、第一单晶半导体层110以及第一杂质半导体层108进行蚀刻,来使第一电极106的一部分露出(参照图16A)。

上述蚀刻采用使用NF3、SF6等的氟类气体的干蚀刻即可。并且,以能够充分确保第一电极106和形成在第一电极106的上方的叠层(构成单元元件120及单元元件230的各层)的选择比的条件进行即可。在此,第二电极232可以用作掩模,所以没必要另行设置蚀刻用掩模。当然,也可以使用抗蚀剂、绝缘层来形成掩模。

然后,形成连接到第一电极106的辅助电极217、连接到第二电极232的辅助电极219(参照图16B)。

如图2所示,将辅助电极219形成为当从上方来看时成为格子状(或者梳状、梳形、梳齿状)。通过采用这种形状,可以对单元元件230及单元元件120入射足够的光,而可以提高光吸收效率。此外,以接触于通过上述的蚀刻而露出的第一电极106的方式形成辅助电极217。

辅助电极217和辅助电极219通过使用铝、银、铅锡(焊料)等且利用印刷法等方法形成即可。例如,可以通过使用银膏且利用丝网印刷法形成。

通过上述,可以制造所谓的串联型光电转换装置200。

而且,虽然在本实施方式中没图示,但是至于上述串联型光电转换装置200,也优选形成具有反射防止功能的钝化层119。

图17A示出光电转换装置的单元元件120和单元元件230的截面示意图的一例。虽然在此示出按顺序层叠有以高浓度添加有p型杂质元素的第一杂质半导体层108(p+层)、p型第一单晶半导体层110(p层)、i型第二单晶半导体层112(i层)、添加有n型杂质元素的第二杂质半导体层114(n+层、或n层)的单元元件120以及按顺序配置有p型第三杂质半导体层222(p+层、或p层)、i型非单晶半导体层224(i层)、n型第四杂质半导体层226(n+层、或n层)的单元元件230,但是所公开的发明的一种方式不被解释为仅局限于此。而且,在将单元元件120中的单晶半导体层设定为单晶硅的情况下,其带隙能量大约为1.12eV,并且在将单元元件230中的非单晶半导体层设定为非晶硅的情况下,其带隙能量大约为1.75eV。此外,光(能量:hv)从第四杂质半导体层226一侧入射。

图17B是图17A所示的单元元件120和单元元件230的能带图。在此,Ec表示传导带的底部,并且Ev表示价电子带的顶部。此外,Ef表示费密能级的能量。此外,Egc1是单元元件120的带隙能量(大约为1.12eV),并且Egc2是单元元件230的带隙能量(大约为1.75eV)。

起因于图17B所示的带结构,在各单元元件中由于光激发而生成的电子向各单元元件的n+层(或n层)的方向流过,并且空穴向各单元元件的p+层(或p层)的方向流过。这是光电转换的基本原理。因为在单元元件120和单元元件230的连接部分流过复合电流(recombination current),所以可以将电流取出到外部。

通过使用具有单晶半导体层的单元元件120作为底部元件(bottom cell),可以吸收800nm以上的波长的光来进行光电转换。此外,通过使用具有非单晶半导体层的单元元件230作为顶部元件(top cell),可以吸收单晶半导体层不吸收的不足800nm的波长的光来进行光电转换。通过采用这种层叠有带隙不同的单元元件的结构(所谓的串联型结构),可以大大提高光电转换效率。

而且,本实施方式可以与其他实施方式适当地组合来使用。

实施方式6

在本实施方式中,将说明层叠有多个单元元件的光电转换装置的一例。具体地,将说明层叠有三个单元元件的所谓的叠层型光电转换装置300。

图18示出根据本实施方式的叠层型光电转换装置300的截面的示意图。光电转换装置300具有在支撑衬底102上层叠有单元元件120(也可以称为第一单元元件)、单元元件230(也可以称为第二单元元件)和单元元件340(也可以称为第三单元元件)的结构。在支撑衬底102和单元元件120之间设置有第一电极106,并且在第一电极106和支撑衬底102之间设置有绝缘层104。在本实施方式中,支撑衬底102、绝缘层104、第一电极106、单元元件120的结构及制造方法与实施方式1同样,所以省略对于重复部分的说明。此外,单元元件230的结构及制造方法与实施方式5同样,所以省略对于重复部分的说明。

光电转换装置300具有从附图中的上方(单元元件340的表面一侧)入射光的结构。此外,构成单元元件340、单元元件230、单元元件120的半导体层的带隙能量越接近光的入射一侧越大。就是说,按带隙能量大的顺序说,是单元元件340、单元元件230、单元元件120。如此,通过使各单元元件的带隙能量不同,并且按带隙能量大的顺序从入射一侧配置,可以有效地吸收光。

例如,在使用单晶硅作为构成单元元件120的半导体层的情况下,其带隙能量大约为1.12eV,所以将带隙能量更大的材料用于单元元件230及单元元件340。具体地,例如,使用带隙能量为1.45eV以上且1.65eV以下左右的材料(非晶硅锗等)作为单元元件230的半导体层,并且使用带隙能量为1.7eV以上且2.0eV以下左右的材料(非晶硅、非晶碳化硅等)作为单元元件340的半导体层即可。

单元元件340具有在单元元件230上按顺序层叠有赋予有一种导电型的第五杂质半导体层342、非单晶半导体层344、赋予有与第五杂质半导体层342不同的导电型的第六杂质半导体层346的结构。在此,对第五杂质半导体层342赋予与单元元件230的第四杂质半导体层226相反的导电型。

在单元元件120的支撑衬底102一侧设置有第一电极106,并且在单元元件340的表面一侧设置有第二电极352。此外,设置有与第一电极106连接的辅助电极353、以及与第二电极352连接的辅助电极354。辅助电极353和辅助电极354用作取出在光电转换层中转换了的电能的取出电极(也称为集电极)。

图19A示出光电转换装置的单元元件120、单元元件230和单元元件340的截面示意图的一例。虽然在此示出按顺序层叠有以高浓度添加有p型杂质元素的第一杂质半导体层108(p+层)、p型第一单晶半导体层110(p层)、i型第二单晶半导体层112(i层)、添加有n型杂质元素的第二杂质半导体层114(n+层、或n层)的单元元件120、按顺序配置有p型第三杂质半导体层222(p+层、或p层)、i型非单晶半导体层224(i层)、n型第四杂质半导体层226(n+层、或n层)的单元元件230以及按顺序配置有p型第五杂质半导体层342(p+层、或p层)、i型非单晶半导体层344(i层)、n型第六杂质半导体层346(n+层、或n层)的单元元件340,但是所公开的发明的一种方式不被解释为仅局限于此。

图19B是图19A所示的单元元件120、单元元件230和单元元件340的能带图。在此,Ec表示传导带的底部,并且Ev表示价电子带的顶部。此外,Ef表示费密能级的能量。此外,Egc1是单元元件120的带隙能量,Egc2是单元元件230的带隙能量,并且Egc3是单元元件340的带隙能量。

起因于图19B所示的带结构,在各单元元件中由于光激发而生成的电子向各单元元件的n+层(或n层)的方向流过,并且空穴向各单元元件的p+层(或p层)的方向流过。这是光电转换的基本原理。因为在单元元件120和单元元件230的连接部分、在单元元件230和单元元件340的连接部分流过复合电流,所以可以将电流取出到外部。

如上所述,通过采用所谓的叠层型结构,可以得到广泛的吸收波长区域,所以可以大大提高光电转换效率。

而且,本实施方式可以与其他实施方式适当地组合。

实施方式7

通过使用根据实施方式1至6等而得到的光电转换装置,可以制造太阳光发电模块。在本实施方式中,图23A示出使用实施方式1所示的光电转换装置的太阳光发电模块的实例。太阳光发电模块1028由设置在支撑衬底102上的单元元件120构成。在支撑衬底102和单元元件120之间从支撑衬底102一侧设置有绝缘层104、第一电极106。此外,第一电极106连接到辅助电极116。

辅助电极116及第二电极118被形成在支撑衬底102的一个表面一侧(形成有单元元件120的一侧),并且在支撑衬底102的端部与外部端子连接用的背面电极1026及背面电极1027分别连接。图23B是对应于图23A的C-D的截面图,并且示出如下情况:通过支撑衬底102的贯穿口,辅助电极116与背面电极1026连接,并且第二电极118与背面电极1027连接。

而且,本实施方式可以与其他实施方式适当地组合来使用。

实施方式8

图24示出使用实施方式7所示的太阳光发电模块1028的太阳光发电系统的实例。充电控制电路1029利用一个或多个太阳光发电模块1028所供应的电力,对蓄电池1030进行充电。此外,在蓄电池1030受到足够的充电的情况下,将太阳光发电模块1028所供应的电力直接输出到负载(load)1031。

当使用双电层电容器作为蓄电池1030时,充电不需要化学反应,所以可以进行迅速的充电。此外,与利用化学反应的铅蓄电池等相比,可以将使用寿命提高为8倍左右并且将充放电效率提高为1.5倍左右。本实施方式所示的太阳光发电系统可以用于照明、电子设备等使用电力的各种各样的负载1031。

而且,本实施方式可以与其他实施方式适当地组合来使用。

实施例1

在本实施例中,参照图25而说明利用所公开的发明的一种方式在玻璃衬底上形成的单晶硅层的特性。

首先,通过使用上述实施方式所说明的方法,在玻璃衬底上形成单晶硅层。在本实施例中,在厚度为0.7mm的玻璃衬底上形成由厚度为50nm的氧化硅层、厚度为50nm的氮氧化硅层、厚度为120nm的单晶硅层构成的叠层结构。并且,然后,在上述单晶硅层上按顺序形成结晶度高的硅层和结晶度低的硅层。

结晶度高的硅层的制造条件为如下。

.成膜法:等离子体CVD

.原料气体:硅烷(4sccm)+氢(400sccm)

.功率(频率):15W(60MHz)

.压力:100Pa

.电极间隔:20mm

.玻璃衬底温度:280℃

.厚度:20nm

此外,结晶度低的硅层的制造条件为如下。

.成膜法:等离子体CVD法

.原料气体:硅烷(25sccm)+氢(150sccm)

.功率(频率):30W(27MHz)

.压力:66.6Pa

.电极间隔:25mm

.玻璃衬底温度:280℃

.厚度:480nm

当制造上述结晶度低的硅层时,观察半导体层的特性。具体地,进行利用显微镜的硅层表面的观察、拉曼光谱观察、EBSP(ElectronBack Scattering Pattern;电子背散射衍射花样)观察。

此后,通过固相外延成长,使结晶度低的半导体层单晶化。具体地说,利用气体加热方式的RTA(GRTA;Gas Rapid Thermal Anneal:气体快速热退火)装置进行650℃且6分钟的热处理。而且,由于在本实施例中形成的结晶度高的硅层是单晶硅层,所以没可能会通过上述加热处理而其结晶度大大变化。当然,在结晶度高的硅层不是单晶硅层的情况下,通过固相成长而单晶化。此外,在该阶段中,不发生上述硅层的剥离。在上述热处理后,再次进行表面观察、拉曼光谱观察、EBSP观察。

图25总结上述观察结果来示出。左列是热处理之前的观察结果,并且右列是热处理之后的观察结果。根据这些的比较,可以知道如下事实:在加热处理之前后,半导体层的特性大大变化。例如,加热处理之后的拉曼光谱的峰波数(peak wavenumber)为519.1cm-1,并且,其峰值陡峭(半峰全宽为5.33cm-1)。再者,通过EBSP观察,可以知道如下事实:结晶的排列十分整齐,在实质上单晶化。

通过使用这种半导体层,可以制造具有优越的特性的光电转换装置。

(比较例)

为了比较,在单晶硅层上直接形成结晶度低的硅层,进行为固相成长的加热处理。而且,虽然在本比较例中使用结晶度低的硅层(厚度:500nm)而代替由结晶度高的硅层和结晶度低的硅层构成的叠层结构,但是对于其以外的条件,采用与上述实施例相同的条件。

加热处理的结果,在本比较例中,发生半导体层的剥离。可以认为,这是因为如下缘故:单晶半导体层和结晶度低的硅层之间的紧密性低。根据本比较例,可以确认到所公开的发明的一种方式的有效性。

本说明书根据2008年4月25日在日本专利局受理的日本专利申请编号2008-114744而制作,所述申请内容包括在本说明书中。

Claims (52)

1.一种光电转换装置的制造方法,包括如下步骤:

在单晶半导体衬底上形成第一杂质半导体层;

对所述单晶半导体衬底照射离子以在所述单晶半导体衬底中形成脆化层;

在所述第一杂质半导体层上形成第一电极;

在所述第一电极上形成绝缘层;

将所述绝缘层和支撑衬底贴紧来将所述单晶半导体衬底和所述支撑衬底贴在一起,然后,沿着所述脆化层分离所述单晶半导体衬底,从而在所述支撑衬底上提供包括所述绝缘层、所述第一电极、所述第一杂质半导体层及第一单晶半导体层的叠层体;

在所述第一单晶半导体层上形成第一半导体层;

在与所述第一半导体层不同的条件下在所述第一半导体层上形成第二半导体层;

通过进行热处理,经由固相成长来提高所述第一半导体层及所述第二半导体层的结晶度,以形成第二单晶半导体层;

在所述第二单晶半导体层上形成具有与所述第一杂质半导体层相反的导电型的第二杂质半导体层;以及

在所述第二杂质半导体层上形成第二电极。

2.根据权利要求1所述的光电转换装置的制造方法,其中所述第一半导体层及所述第二半导体层被形成为所述第一半导体层的结晶度高于所述第二半导体层的结晶度。

3.根据权利要求1所述的光电转换装置的制造方法,其中所述第一半导体层及所述第二半导体层被形成为所述第一半导体层的氢浓度低于所述第二半导体层的氢浓度。

4.根据权利要求1所述的光电转换装置的制造方法,其中将所述第一半导体层形成为10nm至50nm厚。

5.根据权利要求1所述的光电转换装置的制造方法,其中

使用由包含氢的原料气体产生的离子作为所述离子。

6.根据权利要求1所述的光电转换装置的制造方法,其中所述第一单晶半导体层及所述第二单晶半导体层被形成为所述第一单晶半导体层及所述第二单晶半导体层的膜厚度之和为800nm以上。

7.根据权利要求1所述的光电转换装置的制造方法,其中所述第一杂质半导体层是p型杂质半导体层,并且所述第二杂质半导体层是n型杂质半导体层。

8.根据权利要求1所述的光电转换装置的制造方法,其中所述第一半导体层通过氢气体对硅烷类气体的流量比为50倍以上的等离子体化学气相成长法来形成。

9.根据权利要求8所述的光电转换装置的制造方法,其中所述硅烷类气体是硅烷或乙硅烷。

10.根据权利要求8或9所述的光电转换装置的制造方法,其中所述等离子体化学气相成长法在从1Pa到103Pa的压力下进行。

11.根据权利要求1所述的光电转换装置的制造方法,其中所述第一杂质半导体层和所述第二杂质半导体层通过离子注入法或离子掺杂法来形成。

12.根据权利要求1所述的光电转换装置的制造方法,其中对所述第一单晶半导体层照射激光束以修复或去掉包括在所述第一单晶半导体层中的晶体缺陷。

13.根据权利要求1所述的光电转换装置的制造方法,其中利用快速热退火来进行所述热处理。

14.一种光电转换装置的制造方法,包括如下步骤:

对单晶半导体衬底照射离子以在所述单晶半导体衬底中形成脆化层;

在所述单晶半导体衬底上形成第一杂质半导体层;

在所述第一杂质半导体层上形成第一电极;

在所述第一电极上形成绝缘层;

将所述绝缘层和支撑衬底贴紧来将所述单晶半导体衬底和所述支撑衬底贴在一起,然后,沿着所述脆化层分离所述单晶半导体衬底,从而在所述支撑衬底上提供包括所述绝缘层、所述第一电极、所述第一杂质半导体层及第一单晶半导体层的叠层体;

在所述第一单晶半导体层上形成第一半导体层;

在与所述第一半导体层不同的条件下在所述第一半导体层上形成第二半导体层;

通过进行热处理,经由固相成长来提高所述第一半导体层及所述第二半导体层的结晶度,以形成第二单晶半导体层;

在所述第二单晶半导体层上形成具有与所述第一杂质半导体层相反的导电型的第二杂质半导体层;以及

在所述第二杂质半导体层上形成第二电极。

15.根据权利要求14所述的光电转换装置的制造方法,其中所述第一半导体层及所述第二半导体层被形成为所述第一半导体层的结晶度高于所述第二半导体层的结晶度。

16.根据权利要求14所述的光电转换装置的制造方法,其中所述第一半导体层及所述第二半导体层被形成为所述第一半导体层的氢浓度低于所述第二半导体层的氢浓度。

17.根据权利要求14所述的光电转换装置的制造方法,其中将所述第一半导体层形成为10nm至50nm厚。

18.根据权利要求14所述的光电转换装置的制造方法,其中使用由包含氢的原料气体产生的离子作为所述离子。

19.根据权利要求14所述的光电转换装置的制造方法,其中所述第一单晶半导体层及所述第二单晶半导体层被形成为所述第一单晶半导体层及所述第二单晶半导体层的膜厚度之和为800nm以上。

20.根据权利要求14所述的光电转换装置的制造方法,其中所述第一杂质半导体层是p型杂质半导体层,并且所述第二杂质半导体层是n型杂质半导体层。

21.根据权利要求14所述的光电转换装置的制造方法,其中所述第一半导体层通过氢气体对硅烷类气体的流量比为50倍以上的等离子体化学气相成长法来形成。

22.根据权利要求21所述的光电转换装置的制造方法,其中所述硅烷类气体是硅烷或乙硅烷。

23.根据权利要求21或22所述的光电转换装置的制造方法,其中所述等离子体化学气相成长法在从1Pa到103Pa的压力下进行。

24.根据权利要求14所述的光电转换装置的制造方法,其中所述第一杂质半导体层和所述第二杂质半导体层通过离子注入法或离子掺杂法来形成。

25.根据权利要求14所述的光电转换装置的制造方法,其中对所述第一单晶半导体层照射激光束以修复或去掉包括在所述第一单晶半导体层中的晶体缺陷。

26.根据权利要求14所述的光电转换装置的制造方法,其中利用快速热退火来进行所述热处理。

27.一种光电转换装置的制造方法,包括如下步骤:

在单晶半导体衬底上形成第一电极;

对所述单晶半导体衬底照射离子以在所述单晶半导体衬底中形成脆化层;

在所述单晶半导体衬底上形成第一杂质半导体层;

在所述第一电极上形成绝缘层;

将所述绝缘层和支撑衬底贴紧来将所述单晶半导体衬底和所述支撑衬底贴在一起,然后,沿着所述脆化层分离所述单晶半导体衬底,从而在所述支撑衬底上提供包括所述绝缘层、所述第一电极、所述第一杂质半导体层及第一单晶半导体层的叠层体;

在所述第一单晶半导体层上形成第一半导体层;

在与所述第一半导体层不同的条件下在所述第一半导体层上形成第二半导体层;

通过进行热处理,经由固相成长来提高所述第一半导体层及所述第二半导体层的结晶度,以形成第二单晶半导体层;

在所述第二单晶半导体层上形成具有与所述第一杂质半导体层相反的导电型的第二杂质半导体层;以及

在所述第二杂质半导体层上形成第二电极。

28.根据权利要求27所述的光电转换装置的制造方法,其中所述第一半导体层及所述第二半导体层被形成为所述第一半导体层的结晶度高于所述第二半导体层的结晶度。

29.根据权利要求27所述的光电转换装置的制造方法,其中所述第一半导体层及所述第二半导体层被形成为所述第一半导体层的氢浓度低于所述第二半导体层的氢浓度。

30.根据权利要求27所述的光电转换装置的制造方法,其中将所述第一半导体层形成为10nm至50nm厚。

31.根据权利要求27所述的光电转换装置的制造方法,其中

使用由包含氢的原料气体产生的离子作为所述离子。

32.根据权利要求27所述的光电转换装置的制造方法,其中所述第一单晶半导体层及所述第二单晶半导体层被形成为所述第一单晶半导体层及所述第二单晶半导体层的膜厚度之和为800nm以上。

33.根据权利要求27所述的光电转换装置的制造方法,其中所述第一杂质半导体层是p型杂质半导体层,并且所述第二杂质半导体层是n型杂质半导体层。

34.根据权利要求27所述的光电转换装置的制造方法,其中所述第一半导体层通过氢气体对硅烷类气体的流量比为50倍以上的等离子体化学气相成长法来形成。

35.根据权利要求34所述的光电转换装置的制造方法,其中所述硅烷类气体是硅烷或乙硅烷。

36.根据权利要求34或35所述的光电转换装置的制造方法,其中所述等离子体化学气相成长法在从1Pa到103Pa的压力下进行。

37.根据权利要求27所述的光电转换装置的制造方法,其中所述第一杂质半导体层和所述第二杂质半导体层通过离子注入法或离子掺杂法来形成。

38.根据权利要求27所述的光电转换装置的制造方法,其中对所述第一单晶半导体层照射激光束以修复或去掉包括在所述第一单晶半导体层中的晶体缺陷。

39.根据权利要求27所述的光电转换装置的制造方法,其中利用快速热退火来进行所述热处理。

40.一种光电转换装置的制造方法,包括如下步骤:

在单晶半导体衬底上形成第一电极及第一杂质半导体层;

对所述单晶半导体衬底照射离子以在所述单晶半导体衬底中形成脆化层;

在所述第一电极上形成绝缘层;

将所述绝缘层和支撑衬底贴紧来将所述单晶半导体衬底和所述支撑衬底贴在一起,然后,沿着所述脆化层分离所述单晶半导体衬底,从而在所述支撑衬底上提供包括所述绝缘层、所述第一电极、所述第一杂质半导体层及第一单晶半导体层的叠层体;

在所述第一单晶半导体层上形成第一半导体层;

在与所述第一半导体层不同的条件下在所述第一半导体层上形成第二半导体层;

通过进行热处理,经由固相成长来提高所述第一半导体层及所述第二半导体层的结晶度;

在所述第二半导体层上形成具有与所述第一杂质半导体层相反的导电型的第二杂质半导体层;以及

在所述第二杂质半导体层上形成第二电极。

41.根据权利要求40所述的光电转换装置的制造方法,其中所述第一半导体层及所述第二半导体层被形成为所述第一半导体层的结晶度高于所述第二半导体层的结晶度。

42.根据权利要求40所述的光电转换装置的制造方法,其中所述第一半导体层及所述第二半导体层被形成为所述第一半导体层的氢浓度低于所述第二半导体层的氢浓度。

43.根据权利要求40所述的光电转换装置的制造方法,其中将所述第一半导体层形成为10nm至50nm厚。

44.根据权利要求40所述的光电转换装置的制造方法,其中

使用由包含氢的原料气体产生的离子作为所述离子。

45.根据权利要求40所述的光电转换装置的制造方法,其中所述第一单晶半导体层、所述第一半导体层及所述第二半导体层被形成为它们的膜厚度之和为800nm以上。

46.根据权利要求40所述的光电转换装置的制造方法,其中所述第一杂质半导体层是p型杂质半导体层,并且所述第二杂质半导体层是n型杂质半导体层。

47.根据权利要求40所述的光电转换装置的制造方法,其中所述第一半导体层通过氢气体对硅烷类气体的流量比为50倍以上的等离子体化学气相成长法来形成。

48.根据权利要求47所述的光电转换装置的制造方法,其中所述硅烷类气体是硅烷或乙硅烷。

49.根据权利要求47或48所述的光电转换装置的制造方法,其中所述等离子体化学气相成长法在从1Pa到103Pa的压力下进行。

50.根据权利要求40所述的光电转换装置的制造方法,其中所述第一杂质半导体层和所述第二杂质半导体层通过离子注入法或离子掺杂法来形成。

51.根据权利要求40所述的光电转换装置的制造方法,其中对所述第一单晶半导体层照射激光束以修复或去掉包括在所述第一单晶半导体层中的晶体缺陷。

52.根据权利要求40所述的光电转换装置的制造方法,其中利用快速热退火来进行所述热处理。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008-114744 | 2008-04-25 | ||

| JP2008114744 | 2008-04-25 | ||

| JP2008114744 | 2008-04-25 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101567408A CN101567408A (zh) | 2009-10-28 |

| CN101567408B true CN101567408B (zh) | 2013-08-14 |

Family

ID=41215408

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2009101369101A Expired - Fee Related CN101567408B (zh) | 2008-04-25 | 2009-04-24 | 光电转换装置的制造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7947523B2 (zh) |

| JP (1) | JP5286146B2 (zh) |

| KR (1) | KR101512785B1 (zh) |

| CN (1) | CN101567408B (zh) |

| TW (1) | TWI478360B (zh) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5496540B2 (ja) * | 2008-04-24 | 2014-05-21 | 株式会社半導体エネルギー研究所 | 半導体基板の作製方法 |

| JP5552276B2 (ja) * | 2008-08-01 | 2014-07-16 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法 |

| US20100154874A1 (en) * | 2008-09-29 | 2010-06-24 | Takashi Hirose | Photoelectric conversion device and manufacturing method thereof |

| SG162675A1 (en) * | 2008-12-15 | 2010-07-29 | Semiconductor Energy Lab | Manufacturing method of soi substrate and manufacturing method of semiconductor device |

| US8466447B2 (en) * | 2009-08-06 | 2013-06-18 | Alliance For Sustainable Energy, Llc | Back contact to film silicon on metal for photovoltaic cells |

| JP5663254B2 (ja) * | 2010-02-08 | 2015-02-04 | シャープ株式会社 | 水素製造装置および水素製造方法 |

| JP5755931B2 (ja) | 2010-04-28 | 2015-07-29 | 株式会社半導体エネルギー研究所 | 半導体膜の作製方法、電極の作製方法、2次電池の作製方法、および太陽電池の作製方法 |

| JP5894379B2 (ja) * | 2010-06-18 | 2016-03-30 | 株式会社半導体エネルギー研究所 | 光電変換装置 |

| JP6010809B2 (ja) * | 2010-08-31 | 2016-10-19 | 国立大学法人 琉球大学 | 半導体装置の製造方法 |

| JP5719555B2 (ja) | 2010-09-28 | 2015-05-20 | シャープ株式会社 | 水素製造装置および水素製造方法 |

| US9263611B2 (en) | 2011-11-17 | 2016-02-16 | Solar Junction Corporation | Method for etching multi-layer epitaxial material |

| US9142615B2 (en) * | 2012-10-10 | 2015-09-22 | Solar Junction Corporation | Methods and apparatus for identifying and reducing semiconductor failures |

| JP6359525B2 (ja) * | 2013-04-18 | 2018-07-18 | 株式会社東芝 | 太陽光発電モジュール |

| CN104319316B (zh) * | 2014-10-31 | 2017-04-05 | 中国科学院上海微系统与信息技术研究所 | 高效薄膜晶硅太阳电池及其自主能源芯片集成技术 |

| WO2017163931A1 (ja) * | 2016-03-22 | 2017-09-28 | 株式会社村田製作所 | セラミック電子部品およびセラミック電子部品の製造方法 |

| KR101758347B1 (ko) * | 2016-08-01 | 2017-07-18 | 주식회사 엘케이엔지니어링 | 정전 척 및 리페어 방법 |

| US11508820B2 (en) | 2019-11-22 | 2022-11-22 | Samsung Electronics Co., Ltd. | Single crystal semiconductor structure and method of fabricating the same |

| JP7347350B2 (ja) | 2020-07-10 | 2023-09-20 | 信越半導体株式会社 | エピタキシャル成長条件の設定方法及びエピタキシャルウェーハの製造方法 |

| US11955374B2 (en) * | 2021-08-29 | 2024-04-09 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method for forming SOI substrate |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4496788A (en) | 1982-12-29 | 1985-01-29 | Osaka Transformer Co., Ltd. | Photovoltaic device |

| JPS59175170A (ja) | 1983-03-24 | 1984-10-03 | Yoshihiro Hamakawa | タンデム型太陽電池 |

| JPH0644638B2 (ja) | 1982-12-29 | 1994-06-08 | 圭弘 濱川 | 異質単位セル同士のスタック形光起電力素子 |

| JP2687393B2 (ja) * | 1988-02-23 | 1997-12-08 | セイコーエプソン株式会社 | 半導体装置の製造方法 |

| FR2681472B1 (fr) | 1991-09-18 | 1993-10-29 | Commissariat Energie Atomique | Procede de fabrication de films minces de materiau semiconducteur. |

| JP3381443B2 (ja) * | 1995-02-02 | 2003-02-24 | ソニー株式会社 | 基体から半導体層を分離する方法、半導体素子の製造方法およびsoi基板の製造方法 |

| JPH1093122A (ja) * | 1996-09-10 | 1998-04-10 | Nippon Telegr & Teleph Corp <Ntt> | 薄膜太陽電池の製造方法 |

| JP3962465B2 (ja) * | 1996-12-18 | 2007-08-22 | キヤノン株式会社 | 半導体部材の製造方法 |

| JPH1197379A (ja) | 1997-07-25 | 1999-04-09 | Denso Corp | 半導体基板及び半導体基板の製造方法 |

| US6534380B1 (en) | 1997-07-18 | 2003-03-18 | Denso Corporation | Semiconductor substrate and method of manufacturing the same |

| JPH1140786A (ja) | 1997-07-18 | 1999-02-12 | Denso Corp | 半導体基板及びその製造方法 |

| JPH11121310A (ja) | 1997-10-09 | 1999-04-30 | Denso Corp | 半導体基板の製造方法 |

| JP3358550B2 (ja) | 1998-07-07 | 2002-12-24 | 信越半導体株式会社 | Soiウエーハの製造方法ならびにこの方法で製造されるsoiウエーハ |

| JP2001085715A (ja) * | 1999-09-09 | 2001-03-30 | Canon Inc | 半導体層の分離方法および太陽電池の製造方法 |

| JP4364553B2 (ja) * | 2002-08-30 | 2009-11-18 | シャープ株式会社 | 光電変換装置及びその製造方法 |

| JP2004103855A (ja) * | 2002-09-10 | 2004-04-02 | Canon Inc | 基板及びその製造方法 |

| EP1667274A4 (en) * | 2003-08-06 | 2007-08-01 | Fujikura Ltd | PHOTOELECTRIC CONVERTER AND METHOD FOR MANUFACTURING THE SAME |