CN100483687C - 用于cmos工艺的金属栅极晶体管及其制造方法 - Google Patents

用于cmos工艺的金属栅极晶体管及其制造方法 Download PDFInfo

- Publication number

- CN100483687C CN100483687C CNB2005800412068A CN200580041206A CN100483687C CN 100483687 C CN100483687 C CN 100483687C CN B2005800412068 A CNB2005800412068 A CN B2005800412068A CN 200580041206 A CN200580041206 A CN 200580041206A CN 100483687 C CN100483687 C CN 100483687C

- Authority

- CN

- China

- Prior art keywords

- area

- metal oxide

- barrier layer

- accordance

- oxidation resistant

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

- H01L27/092—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate complementary MIS field-effect transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823864—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the gate sidewall spacers, e.g. double spacers, particular spacer material or shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823828—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the gate conductors, e.g. particular materials, shapes

- H01L21/823835—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the gate conductors, e.g. particular materials, shapes silicided or salicided gate conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823828—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the gate conductors, e.g. particular materials, shapes

- H01L21/823842—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the gate conductors, e.g. particular materials, shapes gate conductors with different gate conductor materials or different gate conductor implants, e.g. dual gate structures

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Electrodes Of Semiconductors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

一种形成半导体器件(100)的方法,包括具有第一区域(104)的半导体衬底、在所述第一区域上形成栅极电介质(108)、在所述栅极电介质上形成导电金属氧化物(110)、在所述导电金属氧化物上形成抗氧化屏障层(111)和在所述抗氧化屏障层上形成覆盖层(116)。在一种实施方式中,所述导电金属氧化物是IrO2、MoO2和RuO2,而所述抗氧化屏障层包括TiN。

Description

技术领域

本发明涉及半导体制造领域,并且更具体地讲,涉及用于NMOS(n沟道金属氧化物半导体)和PMOS(p沟道MOS)器件的金属栅极。

背景技术

在CMOS(互补金属氧化物半导体)制造领域中,现在考虑使用包含金属和氧化物二者的栅极。在双金属栅极工艺中,使用第一金属来形成PMOS器件用的栅极电极,而使用不同的第二金属来形成NMOS器件用的栅极电极。使用不同金属的原因是,这样会使各种类型器件的功函数最佳化。功函数的改变将会影响阈值电压(VT)。对于PMOS器件,希望功函数接近于硅价带边缘5.2eV,而对于NMOS器件,希望功函数接近于硅导带边缘4.1eV。

使用导电金属氧化物作为栅极材料的一个问题是,在高温退火期间,即,高于450摄氏度,金属氧化物可能会丢失氧。不期望的氧丢失会造成栅极的功函数发生改变,这样就改变了器件的VT。

因此,非常希望有一种能够形成抵制在退火处理步骤期间发生的变化的双金属栅极的生产工艺。

发明内容

根据本发明,提供了一种用于形成半导体器件的方法,包括:制备半导体衬底,其中该半导体衬底具有第一区域;在所述第一区域上形成栅极电介质;在所述栅极电介质上形成导电金属氧化物;在所述导电金属氧化物上形成阻止形成连续绝缘氧化物层的抗氧化屏障层;和在所述抗氧化屏障层上形成覆盖层。

根据本发明,提供了一种用于形成半导体器件的方法,包括:制备半导体衬底,其中所述半导体衬底具有第一区域和第二区域,并且所述第一区域具有与所述第二区域不同的导电类型;在所述第一区域和所述第二区域上形成栅极电介质;在所述第一区域中的所述栅极电介质上形成导电金属氧化物;在所述第一区域中的所述导电金属氧化物上形成阻止形成连续绝缘氧化物层的抗氧化屏障层;和在所述第二区域中的所述栅极电介质上形成导电材料。

根据本发明,提供了一种半导体器件,包括:半导体衬底,其中所述半导体衬底具有第一区域;位于所述第一区域上的栅极电介质;位于所述栅极电介质上的导电金属氧化物;位于所述导电金属氧化物上的阻止形成连续绝缘氧化物层的抗氧化屏障层;和位于所述抗氧化屏障层上的覆盖层。

附图说明

本发明是用举例的方式加以说明的,并且附图中没有任何对本发明的限制,在附图中,相同的附图标记指代相同的要素,并且其中:

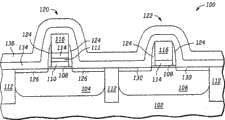

附图1是部分完成了的按照本发明的一种实施方式的半导体器件的局部横截面图;

附图2是附图1之后的处理步骤,其中从半导体器件的一些部分中选择性地除去导电金属氧化物和屏障层;

附图3是附图2之后的处理步骤,其中在第一栅极金属上沉积第二栅极金属、多晶硅覆盖层和ARC;

附图4是附图3之后的处理步骤,其中将所沉积的金属图案化成栅极结构并且与该栅极结构相邻地形成第一间隔物;

附图5是附图4之后的处理步骤,其中在衬底上沉积氧化物层和氮化物层,包括在栅极结构和第一间隔物上方;

附图6是附图5之后的处理步骤,其中由氮化物层形成第二间隔物,同时使氧化物层变薄,并且随后形成源极/漏极区域;和

附图7是附图6之后的处理步骤,其中去除栅极和源极/漏极区域上方的薄氧化物层,并且随后对这些区域进行硅化,以形成基本完成的器件。

附图8说明按照本发明的另一种实施方式的半导体器件的横截面图。

本领域技术人员将会意识到,附图中的要素是为了简明而示出的,并且不一定按比例画出。例如,可能将附图中某些要素的尺寸相对于其它要素进行了夸大,以帮助理解本发明的实施方式。

具体实施方式

总地来说,本发明通过在导电栅极氧化物上引入抗氧化屏障层而克服了前面介绍的栅极电极在高温退火期间丢失氧的问题。在抗氧化屏障层上沉积多晶硅覆盖层,从而可以以常规方式形成栅极自对准硅化物工艺。

在连同相应的图解说明一起考虑的时候,通过阅读下面的详细说明,将会更加容易理解这些益处和优点。要注意,这些图解并不是在各方面都是按比例画出的,对于理解本发明而言,比例的精确度并非是必要的。而且,还可能存在没有具体图示的处于本发明范围之内的其它实施方式。

附图1-7示出按照本发明的半导体工艺的一种实施方式的各个不同阶段的横截面图。在附图1中,示出的是部分完成的半导体器件100。如附图1中所示的半导体器件100包括半导体衬底102,在该半导体衬底内,形成有第一阱104和第二阱106。典型地,半导体衬底102包括轻度掺杂的n型或p型单晶硅,不过也可以使用其它的半导体材料,比如硅、锗和绝缘体上硅(SOI)。所图示的半导体器件100的实施方式是利用双阱工艺生产的,在双阱工艺中,将第一阱104有选择地注入到衬底102中将要形成第一导电类型器件的部分中,而将第二阱106有选择地注入到衬底102中将要形成第二种不同的且相反导电类型的晶体管的部分中。在双阱工艺的一种实施方式中,第一阱104自身可以包围在槽形区(未示出)中,第一阱104与该槽形区(tub)的导电类型是相反的。在另一种实施方式中,衬底102可以包括形成在重度掺杂块(bulk)上的轻度掺杂外延层。在一种实施方式中,例如,衬底102的图示部分是p+块上形成的p-外延层,而第一阱104是n型掺杂的,第二阱106是p型的。n型传导结构可以通过用适当的n型杂质(比如磷或砷)对半导体衬底102进行注入来形成,而p型结构可以通过用适当的p型杂质(比如硼)进行注入来形成。第一阱104和第二阱106,如附图1所示,是利用沟槽隔离结构112相互隔离开的。沟槽隔离结构112可以包括适当的绝缘体,比如电介质材料。沟槽隔离结构112可以包括氧化物、氮化物或其它适当的电绝缘体材料。在优选实施方式中,沟槽隔离结构112包括二氧化硅。

在衬底102的第一阱104和第二阱106上形成栅极电介质108。在一种实施方式中,栅极电介质108包括常规的、用加热方法形成的厚度最好小于10纳米的二氧化硅或氮氧化硅。在另一种实施方式中,栅极电介质108可以包括另一种可供选用的栅极材料,比如第一或第二过渡金属氧化物或稀土氧化物材料。这些可供选用的栅极电介质材料因它们具有高介电常数(K)而适合选用,高介电常数使得能够使用较厚的栅极电介质层而又不对薄膜的电气和电容特性造成负面影响。一种优选的高K栅极电介质是二氧化铪(HfO2)。对于这些可供选用的栅极电介质,可以使用从锆、铪、铝、镧、锶、钽、钛、硅的氧化物以及它们的组合物中选取的适当过渡金属氧化物混合物。也可以为栅极电介质使用过渡金属硅酸盐和铝酸盐,比如硅酸铪(HfxSiyOz)、铝酸铪(HfxAlyOz)和钛酸铪(HfxTiyOz)。

如附图1中进一步示出的,在栅极电介质108上沉积有第一金属类型的导电金属氧化物110。下面将会更加详细地介绍,将从半导体衬底102中制作一种导电类型的晶体管的部分有选择地上去除第一金属110,从而导电金属氧化物110将仅仅存在于另一种导电类型的晶体管所处的位置上。最好,用化学汽相沉积(CVD)、原子层沉积(ALD)或分子束沉积(MBD)工艺来沉积导电金属氧化物110,以保证栅极电介质108的完整性。在另一种可选实施方式中,第一金属110可以是用溅渡工艺物理汽相沉积的。在将导电金属氧化物110最终保留在p型晶体管上(即,在如附图1中所示要在装置100的左半部分中形成PMOS器件时)的实施方式中,当衬底102是硅时,希望第一金属类型具有接近于硅的价带的功函数(即,接近5.1eV的功函数)。导电金属氧化物110包括从由Ir、Mo、Ru、W、Os、Nb、Ti、V、Ni和Re构成的组中选取的元素。

在沉积了层110之后,通过物理汽相沉积(PVD)、化学汽相沉积(CVD)和原子层沉积(ALD)在层110上沉积抗氧化屏障层111。屏障层111可以具有介于一纳米(nm)到50nm之间的厚度。屏障层111应当能够阻止形成连续的绝缘氧化物层,其中氧来源是导电氧化物栅极电极。在温度升高后,导电氧化物栅极电极可能向周围薄膜释放氧。温度的升高可能是因为例如高温退火、沉积或其它工艺步骤造成的。如果栅极电极材料失去过多的氧,则栅极电极的功函数可能会发生改变。此外,如果导电金属氧化物向随后形成的层释放氧,比如向多晶硅释放氧,则可能在屏障层111与多晶硅之间形成绝缘介质层。绝缘层可能会造成在栅极材料与多晶硅覆盖层之间形成不希望有的电容。抗氧化屏障层111在导电金属氧化物与屏障层111上方的层之间形成屏障。抗氧化屏障层111阻止氧从导电金属氧化物110中扩散出来并且还抵抗由屏障层111与导电金属氧化物110之间的接触造成的氧化。抗氧化屏障层111可以包括TiN。

注意,在所示的实施方式中,将屏障层111用在PMOS器件的形成中。不过,本领域的技术人员将会认识到,可以将类似于屏障层111的屏障层引入到NMOS器件的形成中。

现在转到附图2,使用湿法或干法蚀刻选择性地去除了导电金属氧化物110和抗氧化层111的一部分。在所示的实施方式中,层110和111的选择性去除是使用用来形成第二阱106的阱掩模借助掩模和蚀刻工艺来实现的。在这种实施方式中,将第二阱106(在该第二阱上方,将最终制作出第二类型的晶体管)上方的导电金属氧化物110和抗氧化屏障层111去除。这样,在晶体管形成过程完成之后,导电金属氧化物110和屏障层111将会仍然保留在第一导电类型的晶体管的结构中,而在第二导电类型的晶体管中将不存在导电金属氧化物110和屏障层111。并不需要使用严格尺寸(CD)容差的掩模来定义如附图2中所示的导电金属氧化物110和屏障层111的选择性去除的部分,因为掩模错位不会对后续处理造成不利影响。

在优选实施方式中,使用硅氧化物或硅氮化物硬掩模(未示出)来图案化层110和111,因为很多适用的用于从第二导电类型的区域(即,从第二阱106上方)去除层110和111的金属蚀刻剂也会蚀刻或分解光致抗蚀剂掩模。因此,需要能够充分抵御金属蚀刻剂的掩模。可以使用用来形成第二阱106的同一掩模来图案化该硬掩模。还要不对底下的栅极电介质108造成破坏地去除层110和111,这可以使用适当的湿法、等离子或气态蚀刻来实现。

现在转到附图3,在半导体衬底102的第一和第二阱104和106上方形成金属114,从而覆盖屏障层111和栅极电介质108的暴露部分。金属114的金属类型具有不同于导电金属氧化物110所使用的金属类型的功函数。在用于导电金属氧化物110的金属类型具有接近于衬底材料(例如,硅)价带的功函数的实施方式中,用于金属114的金属类型具有更加接近于衬底材料的导带的功函数。相反,在用于导电金属氧化物110的金属类型具有接近于衬底材料的导带的功函数时,用于金属114的金属类型具有接近于衬底材料的价带的功函数。

仍如附图3中所示,在金属114上方沉积了硅包含层116,该硅包含层116是作为导电材料沉积的或者是随后制作成导电的。在优选实施方式中,硅包含层116是针对例如栅极电极应用而原地掺杂或随后掺杂成为充分导电的多晶硅层或多晶硅-锗层。硅包含层116也可以是掺杂或不掺杂的非晶硅或硅-锗层。

最好将金属114沉积成厚度与导电金属氧化物110近似相同,同时各个金属层处于10-1000埃(1-100纳米)的厚度范围之内。最好将硅包含层116沉积成厚度处于100-1500埃(10-150纳米)的范围内。硅包含层厚度并没有严格要求,但是厚度越厚,随后的间隔物形成工艺中的余地越大,这将在下面加以介绍。硅包含层的厚度可以是栅极叠层的可变厚度层。换句话说,如果某种栅极结构应当被限制为某一总厚度或者应当以某一总厚度为目标,则硅包含层可以是可改变其厚度以实现所述总厚度的层。

在硅包含层116上方沉积有抗反射涂层(ARC)。ARC 118最好是富含硅的氮化硅层、有机ARC、氮氧化硅或者对特定光刻工艺起到ARC功能的任何ARC材料。在优选实施方式中,ARC是通过常规技术沉积成厚度介于大约1nm和20nm之间的。

现在转到附图4,示出的是在已经进行了栅极掩模和蚀刻工艺来图案化导电金属氧化物层110、屏障层111、金属层114和硅包含层116,结果在第一阱104上方形成第一栅极120和在第二阱106上方形成第二栅极122之后的半导体器件100。第一栅极120包括栅极电介质108上的层110、层110上的屏障层111和形成在屏障层111上的第二金属114。与此不同,第二栅极122包括与栅极电介质108接触的第二金属114。第一栅极120和第二栅极122都具有由硅包含层116形成的叠置覆盖层。ARC层118最初在栅极叠层蚀刻期间也被图案化,但是在栅极蚀刻之后可以将它完全去除,因此未在附图4中示出。因为硅包含层116起到在后续蚀刻和清洗期间保护金属栅极的作用,所以没有必要将ARC层保留在栅极顶部。这是有利的,因为不需要以后在接触蚀刻工艺期间单独对ARC进行蚀刻来形成与栅极的接触,而是可以对其进行湿法蚀刻。而且,完全去除ARC能够在栅极的顶部实现更加强健的硅化处理。

栅极120和122是用光致抗蚀剂同时图案化的,并且然后加以蚀刻。因为这些栅极具有不同的高度,所以应当将栅极蚀刻化学制品选择成将栅极向下蚀刻到栅极电介质108,如附图4中所示。在所示的实施方式中,栅极蚀刻没有去除栅极电介质108。

继续参照附图4,在图案化第一栅极120和第二栅极122之后,沿着两个栅极的侧面形成第一间隔物124。在优选实施方式中,第一间隔物124是这样形成的:沉积薄的氮化硅层(100-300埃或10-30纳米),然后各向异性地蚀刻晶圆,从而仅仅沿着栅极的侧壁留下氮化硅。这一蚀刻的结果是,结果得到的间隔物将会具有锥形形状,如附图4中所示,靠近各个栅极底部的地方具有50-200埃(5-20纳米)的最大厚度或宽度。在所示的实施方式中,第一间隔物124起到保护金属栅极免于在随后去除注入掩模期间遭到蚀刻的作用。如前面所提到的,用于剥离光致抗蚀剂掩模的常规Piranha和SC-1清洗液也会侵蚀很多打算用于金属栅极的金属。在另一种实施方式中,可以取消间隔物124。

如附图4中所示,第一间隔物124相对于栅极的总高度或厚度可以变化。例如,第一间隔物124沿着第二栅极122的侧壁与第一栅极120相比上升得较高。这并不是问题,因为硅包含层116的存在为金属栅极在后续蚀刻期间提供了充分的保护(这是因为硅包含层116能够抵御来自这些蚀刻的侵蚀)。这样,由于硅包含层116的存在,使得这种工艺在构形和栅极叠层高度方面有很大的处理余量。只要间隔物覆盖了在硅包含层116之下的底层金属的所有侧壁,栅极叠层就能够得到充分保护。

在形成第一间隔物124之后,在栅极电介质108是高K介质(例如,K大于3.9)的情况下,栅极电介质108未受保护的部分(例如,在第一栅极120、第二栅极122和第一间隔物124之下的部分以外的部分)被去除。对于较低的K值,例如在硅二氧化硅的情况下,栅极电介质可以保留下来。栅极电介质的去除可以使用干法或湿法化学处理来实现,或者通过进行退火以将该材料转换成挥发性物质来实现,所采用的方法取决于所使用的具体介质材料。

接下来,分别与第一栅极120和第二栅极122自对准地形成扩展区域126和130,如附图4中所示。在MOS晶体管结构中形成扩展区域作为对源极和漏极区域的扩展,以防止短沟道效应。因为扩展区域126和130将会具有两种不同的导电类型(扩展区域126具有第一导电类型,而扩展区域130具有第二导电类型),所以在各个注入步骤期间需要用掩模来遮挡该器件的一部分。例如,在形成扩展区域126期间将该器件与第二阱106相关联的部分遮挡起来,并且在形成扩展区域130期间将该器件与第一阱104相关联的部分遮挡起来。在注入步骤期间使用的掩模可以是常规的光致抗蚀掩模。如前面所提到的,在常规的双金属栅极工艺中,在这个阶段去除光致抗蚀掩模可能是有害的,因为清洗溶液可能会侵蚀栅极金属。不过,按照本发明,第一间隔物124和硅包含层116的组合使得注入掩模能够用常规的清洗化学试剂(比如Piranha和SC-1)容易地去除,且不会对金属栅极本身造成有害影响。

虽然没有示出,但是按照常规的实践方法,此时还可以进行卤化物注入。同样,需要使用注入掩模,并且通过实践本发明,能够不对金属栅极材料造成任何伤害地容易地实现这些掩模的去除。

参照附图5,在形成扩展区域126和130之后,在该器件上沉积一层氧化物衬里(liner)134,包括在第一栅极120和第二栅极122以及第一间隔物124上。在氧化物衬里134上形成层136。氧化物衬里134一般来说厚度为大约50-250埃(5-25纳米),而层136一般来说厚度为100-1000埃(10-100纳米)。氧化物衬里134最好是由二氧化硅形成的,而层136最好是氮化硅形成的,不过也可以是由能够相对于氧化物衬里134充分选择性地得到蚀刻并且不与硅化物形成金属(如果晶体管的栅极或源极/漏极区域将会受到硅化)发生反应的另一种材料形成的。

如附图6中所示,层136受到各向异性蚀刻,以形成第二间隔物138而不完全去除氧化物衬里134。这可以采用二氧化硅和氮化硅的组合并且使用常规的干法蚀刻化学试剂CF4、HBr和Ar来实现。氧化物衬里134可能会在形成间隔物138期间变薄,但这是无害的,只要在该工艺中此时没有露出底下的衬底材料(例如,硅)。

仍如附图6所示,通过在形成间隔物138之后透过变薄的氧化物衬里134进行注入,在器件100中以自对准的方式形成了源极/漏极区域。源极/漏极区域140形成为包括第一栅极120的晶体管部分,而源极/漏极142形成为包括第二栅极122的晶体管部分。源极/漏极区域是使用常规注入技术形成的。

现在参照附图7,接下来进行退火,以将扩展区域和源极/漏极区域扩散成期望的分布形态并且激活掺杂物。同样,这是使用常规实践方法完成的。此后,使用常规湿法蚀刻从该器件的未受保护区域上(例如,从源极/漏极区域、栅极和绝缘区域上方)去除氧化物衬里134的剩余部分。然后使用自对准工艺通过例如下述处理对暴露的源极/漏极区域和栅极加以硅化:沉积钛、钴或镍包覆层,并且使这一金属与相邻的硅区域发生反应以形成如附图17中所示的硅化物区域144。这样,从阻抗的角度来说,在第一栅极120和第二栅极122上使用硅包含覆盖层几乎没有有害影响,因为用于硅化源极/漏极区域的硅化工艺可以用来同时将栅极硅化到令人满意的阻抗等级。倘若按照需要对源极/漏极区域上方的硅化区域和源极/漏极区域本身进行调节,可以通过完全硅化栅极叠层中的硅包含层116来进一步减小阻抗。

附图8图解说明按照本发明的另一实施方式的半导体器件200的横截面。半导体器件200与半导体器件100类似,只是在半导体器件200中,用于NMOS晶体管的金属层是在沉积用于PMOS晶体管的金属层之前沉积的。附图标记与附图1-7相同,并且处理步骤与前面针对附图1-7讨论的处理步骤类似。

此刻,双金属栅极器件基本上完成了。本领域普通技术人员将会认识到并且理解,随后会形成各种不同的层间电介质和金属连接线,按照器件设计为各个晶体管安排连接线路。然后加上焊盘和钝化层并且测试、单片化和封装各集成电路,以便最终销售出去。

到现在应该很显然,已经给出了一种用在CMOS工艺中的克服了之前介绍的问题的双金属栅极结构。更加具体地讲,本发明给出了一种使用由导电金属氧化物形成的栅极电极形成双栅极金属结构的可靠方法。氧从导电金属氧化物向后续层的转移可以通过在导电金属氧化物上形成抗氧化屏障层来加以防止。此外,防止了导电金属氧化物与后续层之间形成额外的绝缘层。还避免了导电金属氧化物栅极电极的功函数发生变化,因为屏障层防止氧从导电金属氧化物栅极电极中丧失。

在前面的说明书中,参照具体实施方式对本发明进行了介绍。不过,本领域普通技术人员会意识到,在不超出所附权利要求中提出的本发明的范围的前提下,可以做出各种不同的改变和变化。例如,虽然本发明是针对特定的导电类型或电位极性加以介绍的,但是本领域技术人员会意识到,导电类型和电位极性是可以倒转的。此外,可以将本发明扩展为形成三个或更多个具有不同金属栅极材料的栅极叠层。例如,除了具有包括一个覆盖有硅包含层的金属的栅极叠层和包括两个覆盖有硅包含层的金属的栅极叠层之外,还可以有包括三个覆盖有硅包含层的金属的第三栅极叠层。第三栅极叠层对于形成器件的输入/输出晶体管(在一般情况下具有比逻辑晶体管更高的阈值电压要求)是很有益处的。第三栅极叠层可以是这样实现的:沉积和图案化如附图2所示的第一金属层,然后在用于第二栅极叠层的区域上类似地沉积第二金属并且对其进行图案化。接下来如附图3所示那样沉积第三金属层和硅包含覆盖层。可以将此进一步类似地扩展成形成第四栅极叠层、第五栅极叠层等等。由此,要以图解说明的观点而非限制的观点来看待说明书和附图,并且所有这些改变都是要包含在本发明的范围之内的。

前面已经针对具体实施方式介绍了益处、其它优点和对问题的解决方案。不过,不应将这些益处、优点和对问题的解决方案以及可能引起任何益处、优点或解决方案出现或变得更加明显的任何要素解释为任何或全部权利要求的关键、需要或必须的特征或要素。如本文所用,术语“包括”、“包括有”以及它们的任何其它同义词都是用来涵盖非排它的包括,从而包括要素列表的工艺、方法、产品或设备并不仅仅包括这些要素,而是可以包括其它没有明确列出或这一工艺、方法、产品或设备本身固有的其它要素。

Claims (20)

1.一种用于形成半导体器件的方法,包括:

制备半导体衬底,其中该半导体衬底具有第一区域;

在所述第一区域上形成栅极电介质;

在所述栅极电介质上形成导电金属氧化物;

在所述导电金属氧化物上形成阻止形成连续绝缘氧化物层的抗氧化屏障层;和

在所述抗氧化屏障层上形成覆盖层。

2.按照权利要求1所述的方法,其中所述第一区域是n型掺杂的。

3.按照权利要求2所述的方法,其中所述导电金属氧化物形成PMOS栅极电极的至少一部分。

4.按照权利要求2所述的方法,其中:

所述半导体衬底包括第二区域;

所述第二区域是p型掺杂的;并且

所述形成半导体器件还包括在所述抗氧化屏障层上并且在所述覆盖层下形成NMOS栅极电极材料。

5.按照权利要求1所述的方法,其中形成所述NMOS栅极电极包括形成从由TaC和TaSiN构成的组中选取的材料。

6.按照权利要求1所述的方法,其中所述形成导电金属氧化物包括形成包括从由Ir、Mo、Ru、W、Os、Nb、Ti、V、Ni和Re构成的组中选取的元素的导电金属氧化物。

7.按照权利要求6所述的方法,其中所述形成抗氧化屏障层包括形成TiN。

8.按照权利要求1所述的方法,其中所述形成覆盖层包括形成多晶硅层。

9.按照权利要求1所述的方法,其中形成所述抗氧化屏障层发生在对所述半导体衬底进行退火之前。

10.一种用于形成半导体器件的方法,包括:

制备半导体衬底,其中所述半导体衬底具有第一区域和第二区域,并且所述第一区域具有与所述第二区域不同的导电类型;

在所述第一区域和所述第二区域上形成栅极电介质;

在所述第一区域中的所述栅极电介质上形成导电金属氧化物;

在所述第一区域中的所述导电金属氧化物上形成阻止形成连续绝缘氧化物层的抗氧化屏障层;和

在所述第二区域中的所述栅极电介质上形成导电材料。

11.按照权利要求10所述的方法,还包括在所述第一区域中的所述抗氧化屏障层和所述第二区域中的所述导电材料上形成覆盖层。

12.按照权利要求11所述的方法,其中形成所述覆盖层包括在所述第一区域中的所述抗氧化屏障层和所述第二区域中的所述导电材料上形成多晶硅层。

13.按照权利要求10所述的方法,其中所述第一区域是n型掺杂的,而所述第二区域是p型掺杂的。

14.按照权利要求10所述的方法,其中所述导电金属氧化物形成P-MOS栅极电极的至少一部分,并且所述导电材料形成N-MOS栅极电极的至少一部分。

15.按照权利要求10所述的方法,其中形成所述导电材料包括形成从由TaC和TaSiN构成的组中选取的材料。

16.按照权利要求10所述的方法,其中所述形成导电金属氧化物包括形成包括从由Ir、Mo、Ru、W、Os、Nb、Ti、V、Ni和Re构成的组中选取的元素的导电金属氧化物。

17.按照权利要求10所述的方法,其中所述形成抗氧化屏障层包括形成TiN。

18.按照权利要求10所述的方法,其中形成所述抗氧化屏障层发生在对所述半导体衬底进行退火之前。

19.一种半导体器件,包括:

半导体衬底,其中所述半导体衬底具有第一区域;

位于所述第一区域上的栅极电介质;

位于所述栅极电介质上的导电金属氧化物;

位于所述导电金属氧化物上的阻止形成连续绝缘氧化物层的抗氧化屏障层;和

位于所述抗氧化屏障层上的覆盖层。

20.按照权利要求19所述的半导体器件,其中

所述导电金属氧化物包括从由Ir、Mo、Ru、W、Os、Nb、Ti、V、Ni和Re构成的组中选取的元素的氧化物;并且所述抗氧化屏障层包括钛和氮。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/043,337 US7109079B2 (en) | 2005-01-26 | 2005-01-26 | Metal gate transistor CMOS process and method for making |

| US11/043,337 | 2005-01-26 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101091244A CN101091244A (zh) | 2007-12-19 |

| CN100483687C true CN100483687C (zh) | 2009-04-29 |

Family

ID=36697371

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2005800412068A Expired - Fee Related CN100483687C (zh) | 2005-01-26 | 2005-12-16 | 用于cmos工艺的金属栅极晶体管及其制造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7109079B2 (zh) |

| JP (1) | JP4685882B2 (zh) |

| KR (1) | KR101185685B1 (zh) |

| CN (1) | CN100483687C (zh) |

| TW (1) | TWI385733B (zh) |

| WO (1) | WO2006081003A2 (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102569366A (zh) * | 2010-12-22 | 2012-07-11 | 格罗方德半导体公司 | 高介电系数金属栅极电极结构 |

Families Citing this family (74)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4429036B2 (ja) * | 2004-02-27 | 2010-03-10 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US7588988B2 (en) | 2004-08-31 | 2009-09-15 | Micron Technology, Inc. | Method of forming apparatus having oxide films formed using atomic layer deposition |

| US20060172480A1 (en) * | 2005-02-03 | 2006-08-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Single metal gate CMOS device design |

| US7687409B2 (en) | 2005-03-29 | 2010-03-30 | Micron Technology, Inc. | Atomic layer deposited titanium silicon oxide films |

| US7572695B2 (en) * | 2005-05-27 | 2009-08-11 | Micron Technology, Inc. | Hafnium titanium oxide films |

| JP2007019396A (ja) * | 2005-07-11 | 2007-01-25 | Renesas Technology Corp | Mos構造を有する半導体装置およびその製造方法 |

| US7927948B2 (en) | 2005-07-20 | 2011-04-19 | Micron Technology, Inc. | Devices with nanocrystals and methods of formation |

| US7972974B2 (en) | 2006-01-10 | 2011-07-05 | Micron Technology, Inc. | Gallium lanthanide oxide films |

| US7579282B2 (en) * | 2006-01-13 | 2009-08-25 | Freescale Semiconductor, Inc. | Method for removing metal foot during high-k dielectric/metal gate etching |

| US7510956B2 (en) * | 2006-01-30 | 2009-03-31 | Fressscale Semiconductor, Inc. | MOS device with multi-layer gate stack |

| US20070228480A1 (en) * | 2006-04-03 | 2007-10-04 | Taiwan Semiconductor Manufacturing Co., Ltd. | CMOS device having PMOS and NMOS transistors with different gate structures |

| KR100729366B1 (ko) * | 2006-05-19 | 2007-06-15 | 삼성전자주식회사 | 반도체 장치 및 그 형성 방법 |

| US7655550B2 (en) * | 2006-06-30 | 2010-02-02 | Freescale Semiconductor, Inc. | Method of making metal gate transistors |

| JP2008016538A (ja) * | 2006-07-04 | 2008-01-24 | Renesas Technology Corp | Mos構造を有する半導体装置及びその製造方法 |

| US9070759B2 (en) * | 2006-09-25 | 2015-06-30 | Infineon Technologies Ag | Semiconductor device and method of making same |

| US7378713B2 (en) * | 2006-10-25 | 2008-05-27 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor devices with dual-metal gate structures and fabrication methods thereof |

| US7812414B2 (en) * | 2007-01-23 | 2010-10-12 | Taiwan Semiconductor Manufacturing Company, Ltd. | Hybrid process for forming metal gates |

| JP2008210874A (ja) * | 2007-02-23 | 2008-09-11 | Toshiba Corp | 半導体装置の製造方法 |

| JP2008288364A (ja) * | 2007-05-17 | 2008-11-27 | Sony Corp | 半導体装置および半導体装置の製造方法 |

| US8173532B2 (en) | 2007-07-30 | 2012-05-08 | International Business Machines Corporation | Semiconductor transistors having reduced distances between gate electrode regions |

| US20090045458A1 (en) * | 2007-08-15 | 2009-02-19 | Advanced Micro Devices, Inc. | Mos transistors for thin soi integration and methods for fabricating the same |

| US8030709B2 (en) * | 2007-12-12 | 2011-10-04 | International Business Machines Corporation | Metal gate stack and semiconductor gate stack for CMOS devices |

| US20090206416A1 (en) * | 2008-02-19 | 2009-08-20 | International Business Machines Corporation | Dual metal gate structures and methods |

| US8536660B2 (en) * | 2008-03-12 | 2013-09-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Hybrid process for forming metal gates of MOS devices |

| US7955926B2 (en) * | 2008-03-26 | 2011-06-07 | International Business Machines Corporation | Structure and method to control oxidation in high-k gate structures |

| US7994036B2 (en) * | 2008-07-01 | 2011-08-09 | Panasonic Corporation | Semiconductor device and fabrication method for the same |

| US20100038715A1 (en) * | 2008-08-18 | 2010-02-18 | International Business Machines Corporation | Thin body silicon-on-insulator transistor with borderless self-aligned contacts |

| US20100044804A1 (en) * | 2008-08-25 | 2010-02-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | Novel high-k metal gate structure and method of making |

| US7947588B2 (en) * | 2008-08-26 | 2011-05-24 | Taiwan Semiconductor Manufacturing Company, Ltd. | Structure and method for a CMOS device with doped conducting metal oxide as the gate electrode |

| US7816243B2 (en) * | 2009-02-18 | 2010-10-19 | United Microelectronics Corp. | Semiconductor device and method of fabricating the same |

| US8026539B2 (en) * | 2009-02-18 | 2011-09-27 | Globalfoundries Inc. | Metal oxide semiconductor devices having doped silicon-compromising capping layers and methods for fabricating the same |

| US8350586B2 (en) | 2009-07-02 | 2013-01-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method and apparatus of deembedding |

| US8232154B2 (en) * | 2009-09-21 | 2012-07-31 | United Microelectronics Corp. | Method for fabricating semiconductor device |

| US8617946B2 (en) * | 2009-11-11 | 2013-12-31 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated circuits including metal gates and fabrication methods thereof |

| DE102009055395B4 (de) * | 2009-12-30 | 2011-12-29 | Globalfoundries Dresden Module One Limited Liability Company & Co. Kg | Vordotiertes Halbleitermaterial für eine Metallgateelektrodenstruktur mit großem ε von p-und n-Kanaltransistoren |

| US8088685B2 (en) * | 2010-02-09 | 2012-01-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integration of bottom-up metal film deposition |

| US8436422B2 (en) * | 2010-03-08 | 2013-05-07 | Sematech, Inc. | Tunneling field-effect transistor with direct tunneling for enhanced tunneling current |

| US8163620B2 (en) | 2010-04-21 | 2012-04-24 | Institute of Microelectronics, Chinese Academy of Sciences | Method for etching Mo-based metal gate stack with aluminium nitride barrier |

| CN102237269B (zh) * | 2010-04-21 | 2013-08-28 | 中国科学院微电子研究所 | 以氮化铝为势垒层的Mo基金属栅叠层结构的刻蚀方法 |

| KR101675319B1 (ko) | 2010-10-04 | 2016-11-14 | 삼성전자주식회사 | 반도체 소자의 제조 방법 |

| US9166020B2 (en) | 2011-03-01 | 2015-10-20 | United Microelectronics Corp. | Metal gate structure and manufacturing method thereof |

| US8519487B2 (en) | 2011-03-21 | 2013-08-27 | United Microelectronics Corp. | Semiconductor device |

| KR20120107762A (ko) * | 2011-03-22 | 2012-10-04 | 삼성전자주식회사 | 반도체 소자의 제조 방법 |

| US9384962B2 (en) | 2011-04-07 | 2016-07-05 | United Microelectronics Corp. | Oxygen treatment of replacement work-function metals in CMOS transistor gates |

| US8530980B2 (en) | 2011-04-27 | 2013-09-10 | United Microelectronics Corp. | Gate stack structure with etch stop layer and manufacturing process thereof |

| US9269634B2 (en) | 2011-05-16 | 2016-02-23 | Globalfoundries Inc. | Self-aligned metal gate CMOS with metal base layer and dummy gate structure |

| US8841733B2 (en) | 2011-05-17 | 2014-09-23 | United Microelectronics Corp. | Semiconductor device and method of fabricating the same |

| CN102420187B (zh) * | 2011-06-07 | 2014-02-05 | 上海华力微电子有限公司 | 一种改善先栅极工艺中高k栅电介质pmos负偏置温度不稳定性效应的方法 |

| US9490342B2 (en) | 2011-06-16 | 2016-11-08 | United Microelectronics Corp. | Method for fabricating semiconductor device |

| US8673758B2 (en) | 2011-06-16 | 2014-03-18 | United Microelectronics Corp. | Structure of metal gate and fabrication method thereof |

| TWI509667B (zh) * | 2011-06-20 | 2015-11-21 | United Microelectronics Corp | 金屬閘極之結構及其製作方法 |

| US8536038B2 (en) | 2011-06-21 | 2013-09-17 | United Microelectronics Corp. | Manufacturing method for metal gate using ion implantation |

| US9269580B2 (en) | 2011-06-27 | 2016-02-23 | Cree, Inc. | Semiconductor device with increased channel mobility and dry chemistry processes for fabrication thereof |

| US8486790B2 (en) | 2011-07-18 | 2013-07-16 | United Microelectronics Corp. | Manufacturing method for metal gate |

| US8551876B2 (en) | 2011-08-18 | 2013-10-08 | United Microelectronics Corp. | Manufacturing method for semiconductor device having metal gate |

| US8872286B2 (en) | 2011-08-22 | 2014-10-28 | United Microelectronics Corp. | Metal gate structure and fabrication method thereof |

| US8691681B2 (en) | 2012-01-04 | 2014-04-08 | United Microelectronics Corp. | Semiconductor device having a metal gate and fabricating method thereof |

| US8860181B2 (en) | 2012-03-07 | 2014-10-14 | United Microelectronics Corp. | Thin film resistor structure |

| US9093559B2 (en) * | 2012-03-09 | 2015-07-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of hybrid high-k/metal-gate stack fabrication |

| US9105623B2 (en) | 2012-05-25 | 2015-08-11 | United Microelectronics Corp. | Semiconductor device having metal gate and manufacturing method thereof |

| US8883583B2 (en) * | 2012-06-26 | 2014-11-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor devices, transistors, and methods of manufacture thereof |

| US8975666B2 (en) | 2012-08-22 | 2015-03-10 | United Microelectronics Corp. | MOS transistor and process thereof |

| US9054172B2 (en) | 2012-12-05 | 2015-06-09 | United Microelectrnics Corp. | Semiconductor structure having contact plug and method of making the same |

| US8735269B1 (en) | 2013-01-15 | 2014-05-27 | United Microelectronics Corp. | Method for forming semiconductor structure having TiN layer |

| US9653300B2 (en) | 2013-04-16 | 2017-05-16 | United Microelectronics Corp. | Structure of metal gate structure and manufacturing method of the same |

| US9159798B2 (en) | 2013-05-03 | 2015-10-13 | United Microelectronics Corp. | Replacement gate process and device manufactured using the same |

| US9196542B2 (en) | 2013-05-22 | 2015-11-24 | United Microelectronics Corp. | Method for manufacturing semiconductor devices |

| US8921947B1 (en) | 2013-06-10 | 2014-12-30 | United Microelectronics Corp. | Multi-metal gate semiconductor device having triple diameter metal opening |

| US20150069534A1 (en) | 2013-09-11 | 2015-03-12 | United Microelectronics Corp. | Semiconductor device and method for fabricating the same |

| US9105720B2 (en) | 2013-09-11 | 2015-08-11 | United Microelectronics Corp. | Semiconductor device having metal gate and manufacturing method thereof |

| US9196546B2 (en) | 2013-09-13 | 2015-11-24 | United Microelectronics Corp. | Metal gate transistor |

| US9231071B2 (en) | 2014-02-24 | 2016-01-05 | United Microelectronics Corp. | Semiconductor structure and manufacturing method of the same |

| CN106601605B (zh) | 2015-10-19 | 2020-02-28 | 中芯国际集成电路制造(北京)有限公司 | 栅极堆叠结构、nmos器件、半导体装置及其制造方法 |

| US10096596B2 (en) | 2015-12-15 | 2018-10-09 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor device structure having a plurality of gate structures |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1227969A (zh) * | 1998-01-29 | 1999-09-08 | 日本电气株式会社 | 半导体器件的制造方法 |

| CN1263357A (zh) * | 1998-12-28 | 2000-08-16 | 因芬尼昂技术北美公司 | 半导体器件及其制造方法 |

| US6255698B1 (en) * | 1999-04-28 | 2001-07-03 | Advanced Micro Devices, Inc. | Separately optimized gate structures for n-channel and p-channel transistors in an integrated circuit |

| CN1162903C (zh) * | 2000-07-26 | 2004-08-18 | 国际商业机器公司 | 用选择性外延淀积制造应变硅cmos结构的方法 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA2178091A1 (en) * | 1994-10-04 | 1996-04-11 | Robertus Adrianus Maria Wolters | Semiconductor device comprising a ferroelectric memory element with a lower electrode provided with an oxygen barrier |

| JPH10173169A (ja) * | 1996-12-16 | 1998-06-26 | Toshiba Corp | 半導体装置及びその製造方法 |

| US6160282A (en) * | 1998-04-21 | 2000-12-12 | Foveon, Inc. | CMOS image sensor employing silicide exclusion mask to reduce leakage and improve performance |

| JP2000208720A (ja) * | 1999-01-13 | 2000-07-28 | Lucent Technol Inc | 電子デバイス、momキャパシタ、mosトランジスタ、拡散バリア層 |

| JP2001044428A (ja) * | 1999-08-03 | 2001-02-16 | New Japan Radio Co Ltd | 半導体装置及びその製造方法 |

| JP4074734B2 (ja) * | 1999-10-29 | 2008-04-09 | 株式会社東芝 | 強誘電体キャパシタ及びその製造方法並びに強誘電体メモリ |

| US6444512B1 (en) | 2000-06-12 | 2002-09-03 | Motorola, Inc. | Dual metal gate transistors for CMOS process |

| US6423632B1 (en) | 2000-07-21 | 2002-07-23 | Motorola, Inc. | Semiconductor device and a process for forming the same |

| KR20020056260A (ko) * | 2000-12-29 | 2002-07-10 | 박종섭 | 반도체 소자의 금속 게이트 형성방법 |

| JP3771801B2 (ja) * | 2001-01-16 | 2006-04-26 | 株式会社ルネサステクノロジ | 半導体装置 |

| TW587302B (en) * | 2001-03-07 | 2004-05-11 | United Microelectronics Corp | Manufacturing method for MOS capacitor |

| JP3779556B2 (ja) * | 2001-03-27 | 2006-05-31 | 株式会社東芝 | 電界効果トランジスタ |

| US6518106B2 (en) | 2001-05-26 | 2003-02-11 | Motorola, Inc. | Semiconductor device and a method therefor |

| US6894353B2 (en) | 2002-07-31 | 2005-05-17 | Freescale Semiconductor, Inc. | Capped dual metal gate transistors for CMOS process and method for making the same |

| US6806126B1 (en) * | 2002-09-06 | 2004-10-19 | Advanced Micro Devices, Inc. | Method of manufacturing a semiconductor component |

| US6790719B1 (en) * | 2003-04-09 | 2004-09-14 | Freescale Semiconductor, Inc. | Process for forming dual metal gate structures |

| US6933227B2 (en) * | 2003-10-23 | 2005-08-23 | Freescale Semiconductor, Inc. | Semiconductor device and method of forming the same |

| JP2008511149A (ja) * | 2004-08-24 | 2008-04-10 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 半導体装置及びその製造方法 |

-

2005

- 2005-01-26 US US11/043,337 patent/US7109079B2/en not_active Expired - Fee Related

- 2005-12-16 KR KR1020077017127A patent/KR101185685B1/ko not_active IP Right Cessation

- 2005-12-16 CN CNB2005800412068A patent/CN100483687C/zh not_active Expired - Fee Related

- 2005-12-16 JP JP2007552131A patent/JP4685882B2/ja not_active Expired - Fee Related

- 2005-12-16 WO PCT/US2005/045727 patent/WO2006081003A2/en active Application Filing

-

2006

- 2006-01-05 TW TW095100491A patent/TWI385733B/zh not_active IP Right Cessation

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1227969A (zh) * | 1998-01-29 | 1999-09-08 | 日本电气株式会社 | 半导体器件的制造方法 |

| CN1263357A (zh) * | 1998-12-28 | 2000-08-16 | 因芬尼昂技术北美公司 | 半导体器件及其制造方法 |

| US6255698B1 (en) * | 1999-04-28 | 2001-07-03 | Advanced Micro Devices, Inc. | Separately optimized gate structures for n-channel and p-channel transistors in an integrated circuit |

| CN1162903C (zh) * | 2000-07-26 | 2004-08-18 | 国际商业机器公司 | 用选择性外延淀积制造应变硅cmos结构的方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102569366A (zh) * | 2010-12-22 | 2012-07-11 | 格罗方德半导体公司 | 高介电系数金属栅极电极结构 |

| CN102569366B (zh) * | 2010-12-22 | 2014-12-17 | 格罗方德半导体公司 | 高介电系数金属栅极电极结构 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20060166424A1 (en) | 2006-07-27 |

| CN101091244A (zh) | 2007-12-19 |

| TWI385733B (zh) | 2013-02-11 |

| KR101185685B1 (ko) | 2012-09-24 |

| US7109079B2 (en) | 2006-09-19 |

| TW200636875A (en) | 2006-10-16 |

| JP2008529274A (ja) | 2008-07-31 |

| KR20070094807A (ko) | 2007-09-21 |

| JP4685882B2 (ja) | 2011-05-18 |

| WO2006081003A3 (en) | 2007-04-26 |

| WO2006081003A2 (en) | 2006-08-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100483687C (zh) | 用于cmos工艺的金属栅极晶体管及其制造方法 | |

| TWI710013B (zh) | 使用單元隔離柱對主動奈米結構間的 n-p 空間之功函數金屬圖案化 | |

| US6894353B2 (en) | Capped dual metal gate transistors for CMOS process and method for making the same | |

| US9000534B2 (en) | Method for forming and integrating metal gate transistors having self-aligned contacts and related structure | |

| US7820500B2 (en) | Single mask scheme method and structure for integrating PMOS and NMOS transistors using strained silicon | |

| US20120211807A1 (en) | System and Method for Source/Drain Contact Processing | |

| US20050156208A1 (en) | Device having multiple silicide types and a method for its fabrication | |

| US20120299101A1 (en) | Thin body silicon-on-insulator transistor with borderless self-aligned contacts | |

| CN101263594A (zh) | 制造具有不同金属栅极的半导体器件的方法 | |

| US9142547B2 (en) | Methods of manufacturing resistors and structures thereof | |

| US7432566B2 (en) | Method and system for forming dual work function gate electrodes in a semiconductor device | |

| JP2007165558A (ja) | 半導体装置およびその製造方法 | |

| US6949455B2 (en) | Method for forming a semiconductor device structure a semiconductor layer | |

| US20080138950A1 (en) | Method To Increase Charge Retention Of Non-Volatile Memory Manufactured In A Single-Gate Logic Process | |

| US7312129B2 (en) | Method for producing two gates controlling the same channel | |

| CN103178012A (zh) | 具有金属栅极的cmos器件及其形成方法 | |

| US8502325B2 (en) | Metal high-K transistor having silicon sidewalls for reduced parasitic capacitance | |

| US7217610B2 (en) | Method for fabricating a semiconductor product with a memory area and a logic area | |

| KR100549006B1 (ko) | 완전한 실리사이드 게이트를 갖는 모스 트랜지스터 제조방법 | |

| JP2842842B2 (ja) | Mos型半導体装置およびその製造方法 | |

| KR100549001B1 (ko) | 완전한 실리사이드 게이트를 갖는 모스 트랜지스터 제조방법 | |

| CN220856579U (zh) | 半导体装置 | |

| US10957578B2 (en) | Single diffusion break device for FDSOI | |

| US20110037127A1 (en) | Cmos integrated circuit | |

| KR20050013817A (ko) | 선택적 실리사이드 형성방법을 이용한 반도체 소자의제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20090429 Termination date: 20171216 |