发明内容

在依据第一传统示例的半导体集成电路验证方法中,在具有验证工具的验证装置中提供了用于存储专用库的存储器,并且另外还必须进行额外的动态验证。因此,当集成电路已经通过在其上集成数目增加的设备而小型化时,所要处理的数据量会变得巨大,这可能导致第一种传统方法需要大量的时间来处理这些数据。

此外,在第二传统示例的测试模式准备方法中,使用延迟信息的动态验证是必需的,并且设计者必须向测试矢量准备支持部分1015输入对于通过静态时序分析所产生的最小和最大延迟时间的偏移时间。因此,在具有较高密度的小型化集成电路的情况下,电路的验证可能需要更长的时间。

因此,本发明的一个目的是提供其中当抑制了验证时间的增加时允许执行稳定测试的半导体集成电路验证方法,以及提供用于准备在该验证方法中使用的测试模式的方法。

发明的第一种半导体集成电路验证方法是这样一种半导体集成电路验证方法,其中使用从一个要被验证的集成电路中输出的信号、依据已经输入到该集成电路中的测试模式来执行操作验证。本发明的方法包括:使用操作期望值和在测试周期内信号发生变化的时段提取期望值比较时间的步骤(a),其中在该期望比较时间处将该信号的值和操作期望值进行比较。

该方法允许在不执行动态验证的情况下执行集成电路的操作验证,这与传统方法相比显著地缩短了电路操作验证所需的时间量。该方法因此可更佳地应用到具有较高密度的小型化集成电路中。另外,因为减少了准备测试模式所需要的步骤数目,所以和传统方法相比较,能够用较少数目的处理步骤准备用于稳定地测试该集成电路的测试模式。这降低了包括开发成本在内的半导体集成电路制造成本。此外,在步骤(a)中,如果设置期望值比较时间以使它处于其中信号值不稳定的时段之内,则能够稳定地测试集成电路。

至少通过集成电路的时序验证获得在该测试周期中的信号变化时段。然后,能够利用诸如STA工具之类的商用工具获得在该测试周期中的信号变化时段。

在该测试周期中的信号变化时段包括一个其中的信号上升或下降时间变化的信号可变性时段,以及在步骤(a)中,在一个不同于信号可变性时段的时段内设置该期望值比较时间。然后,准备一种其中考虑了变化的测试模式,由此使得测试更可靠。

该发明的方法进一步包括,在步骤(a)之前,在多个延迟条件下执行时序验证由此至少获得在该测试周期中的信号变化时段的步骤(b)。然后,能够考虑由各种条件所引起的变化,执行该电路操作验证。因此,利用该验证结果,执行了更可靠的测试。

在步骤(a)中,在其中在各个延迟条件下获得的信号值都等于操作期望值的时段内,设置期望值比较时间。然后,就有可能准备一种经得起各种变化的测试模式。

该方法进一步包括步骤(c),其中如果该测试周期不包括其中在各个延迟条件下获得的信号值都等于操作期望值的时段,则将该周期视作一个不可能在其中进行期望值比较的周期。然后,就有可能准备一种能够经得起由于各种因素所导致的信号延迟时间中的任何变化的稳定测试模式。通过使用这种测试模式,能够执行准确的测试。

该测试模式是从一个测试装置中输入的,而且该方法进一步包括步骤(d),确定在测试装置的测量能力范围内是否执行步骤(a)中的期望值比较时间的提取。然后,能够调整测量条件等,以便使得在该测试装置的测量能力范围之内执行期望值比较时间的提取,由此使得操作验证更加准确。

在步骤(d)中,确定在该测试周期中的信号延迟时间是否在测试装置的延迟约束之内。然后,更具体和更准确地执行操作验证。

本发明的方法进一步包括:在步骤(a)之前,获得信号的电平改变所需的时段作为信号跃迁时段的步骤(e);以及在步骤(e)之后并且在步骤(a)之前,将信号跃迁时段加到在测试周期中的信号变化时段中由此获得一个组合的信号变化时段的步骤(f),其中在步骤(a)中提取期望值比较时间时,使用组合的信号变化时段。然后,能够设置期望值比较时间,以便使得不在诸如信号的上升或下降时间期间之类的其中信号变得不稳定的信号跃迁时段内执行期望值比较。因此,有可能准备一种允许以稳定方式对集成电路进行测试的测试模式。

在步骤(a)中,至少在信号跃迁时段内不设置期望值比较时间。因此,获得了高度准确的验证结果。

在步骤(e)中,信号跃迁时段计算装置通过至少使用测试装置的负载容量作为参数来计算信号跃迁时段。然后,即使使用了具有不同内部负载容量的测试装置,也能够准确地执行该操作验证。

更佳地,本发明的方法进一步包括:获得有关该信号的没有负载的延迟信息的步骤(g),其中该信息在假定在测试装置中没有负载容量时由测试装置所接收;以及获得有关该信号的有负载的延迟信息的步骤(h),其中该信息在测试装置中有负载容量时由测试装置所接收。更佳地,在步骤(e)中,信号跃迁时段计算装置使用没有负载的延迟信息和有负载的延迟信息计算该信号跃迁时段。

在步骤(e)中,信号跃迁时段计算装置通过至少使用在集成电路中传播该信号的频率作为参数来计算信号跃迁时段。因此,有可能考虑由集成电路的操作频率所引起的信号延迟而执行该电路操作验证。

例如,该发明的方法进一步包括:在步骤(e)之前,使用一个模拟装置执行集成电路的模拟的步骤(i),以及信号频率提取装置至少使用该模拟的结果提取信号的频率的步骤(j),其中在步骤(e)中,信号跃迁时段计算装置基于在步骤(j)中提取的信号频率计算信号跃迁时段。这允许考虑由集成电路的操作频率所引起的信号延迟而执行上述电路操作验证。应当注意到:可以基于该频率自动地计算信号跃迁时段。

该发明的方法进一步包括:准备一个数据库的步骤(k),在该数据库中存储影响信号跃迁时段的条件、以及当使用该条件时获得的信号跃迁时段,其中在步骤(f)中,将从数据库中得到的信号跃迁时段加到在测试周期中的信号变化时段中。因此,与其中基于电路验证的条件使用工具等计算延迟时间的情况相比,能够在更短的时间内执行电路验证。

通过分组来执行在步骤(a)中的期望值比较时间的提取。然后,与其中不执行分组的情况相比,有效地使用了测试装置的功能,由此获得了更短的测试时间。还有可能获得允许高度准确测试的测试模式验证和测试模式准备,其中没有减小故障范围,而是减少了准备测试模式所需要的步骤数目。因此,减少了屏蔽部分的数量,这使得更容易提取出在其处稳定地执行期望值比较的期望值比较时间。

该集成电路包括一个端子,用于依据和基准时钟信号异步的时钟信号输出该信号,该方法进一步包括步骤(i),基于基准时钟信号中的信号变化和基准时钟信号的时段,将从该端子输出的信号转换成为另一个信号;以及通过使用在步骤(i)中获得的另一个信号,为从该端子输出的信号计算在测试周期中的信号变化时段。因此,即使集成电路基于多个时钟信号进行操作,也能稳定地进行期望值比较,由此允许更准确地执行电路操作验证。

该集成电路具有多条信号路径,以及该方法进一步包括:在步骤(a)之前,验证工具从集成电路的动态验证结果中获得信号变化中的延迟时间、然后检测该信号在该信号的每个周期中通过哪条信号路径的步骤(m)。因此,通过组合路径检测结果和时序验证结果,就有可能使用对于各个周期不同的延迟时间来设定期望值比较时间。此外,作为路径检测的结果,例如,能够识别出不期望通过信号的不必要路径的输出,以便不将其与期望值进行比较。

该发明的方法进一步包括:步骤(n),获得在和集成电路的动态验证相同的模式中执行的时序验证结果,其中该结果包括路径信息和对于每条信号路径在测试周期中的信号变化时段;以及在步骤(a)之前,基于路径信息、对于每条信号路径在该测试周期中的信号变化时段、以及在步骤(m)中获得的路径检测结果,提取路径中的一条有效路径的步骤(o)。因此,有可能使用对于各个周期不同的延迟时间来设定期望值比较时间,这允许更准确地执行电路操作验证。

通过在多种模式下执行动态验证,获得动态验证的结果。因此,与其中使用了在单种模式下获得的动态验证结果的情况相比,电路中的故障范围的准确度增加到更高的程度。

该发明的方法进一步包括:获得至少在一种模式下的集成电路的动态验证结果的步骤(p);使用动态验证结果提取一条有效路径的步骤(q);获得包括有关该集成电路的路径信息和在测试周期中的信号变化时段的时序验证结果的步骤(r);以及步骤(s),通过使用时序验证结果和有效路径提取的结果,以一种伪方式准备在与步骤(p)中获得的动态验证结果的模式不同的模式中的动态验证结果。因此,例如,缩短了在多种模式下执行动态验证所需要的时间量,同时获得了其中考虑到在该多种模式下发生的信号变化的电路操作验证。

该发明的方法进一步包括:获得集成电路的动态验证结果的步骤(t),以及通过使用动态验证结果和操作期望值来确认信号的跃迁顺序的步骤(u)。因此,有可能检测出仅通过执行传统测试不能检测出的故障类型。例如,有可能识别出这样一种情况,其中因为该集成电路以逐个周期为单位进行测试,所以不能检测出有故障的集成电路。

该发明的方法进一步包括:获得集成电路的动态验证结果的步骤(v),以及通过使用动态验证结果和操作期望值来确认信号的跃迁数目的步骤(w)。因此,有可能准备一种用于检测仅通过执行传统测试不能检测出的故障类型的测试模式。

第二种半导体集成电路验证方法是这样一种半导体集成电路验证方法,其中使用从一个要被验证的集成电路中输出的信号、依据已经输入到该集成电路中的测试模式来执行操作验证。该发明的方法包括:获得集成电路的时序验证结果的步骤(a);获得信号的电平改变所需的时段作为信号跃迁时段的步骤(b);以及将该信号跃迁时段加到时序验证结果中的步骤(c)。

依据这种方法,有可能防止在诸如信号的上升或下降时间期间之类的其中信号变得不稳定的信号跃迁时段内设定期望值比较时间。因此,准备了更稳定的测试模式。此外,和传统的方法相比,降低了执行动态验证的次数,这显著地缩短了电路操作验证所需要的时间量。

第三种半导体集成电路验证方法是这样一种半导体集成电路验证方法,其中使用从一个要被验证的集成电路中输出的信号、依据已经输入到该集成电路中的测试模式来执行操作验证。该发明的方法包括:获得集成电路的动态验证结果的步骤(a),以及通过使用该动态验证结果和用于该测试模式的信号操作期望值来确认该信号的跃迁顺序的步骤(b)。

这种方法使得可以识别出其中由于以逐个周期为单位对该集成电路进行测试所以不能检测出有故障的集成电路的情况。

第四种半导体集成电路验证方法是这样一种半导体集成电路验证方法,其中使用从一个要被验证的集成电路中输出的信号、依据已经输入到该集成电路中的测试模式来执行操作验证。该发明的方法包括:获得集成电路的动态验证结果的步骤(a),以及通过使用该动态验证结果和用于该测试模式的信号操作期望值来确认信号的跃迁数目的步骤(b)。

该方法还允许准备一种允许检测出仅通过执行传统测试不能检测出的故障类型的测试模式。

发明的一种测试模式准备方法是这样一种测试模式准备方法,其中输入一种测试模式以验证一个集成电路的操作,并且使用依据该测试模式输出的信号来处理该测试模式。该发明的方法包括:通过使用操作期望值和在测试周期中信号变化的时段来处理测试模式的步骤(a),其中该信号变化时段是通过集成电路的时序验证获得的。

依据该方法,例如,能够屏蔽该测试模式或者移动期望值比较时间,以便使得不在其中信号电平变化的变化时段内执行期望值验证。因此,准备了一种具有更稳定的期望值比较时间的测试模式,由此允许高质量的测试。

另外,如果上述半导体集成电路验证方法发现具有不可能在其中进行稳定的期望值比较的(一个或多个)部分,则可以屏蔽该测试模式或者移动期望值比较时间,以便在一个可能在其中进行稳定的期望值比较的部分内设置期望值比较时间。因此,实现了更准确的电路操作验证。

依据本发明的半导体集成电路验证方法和测试模式准备方法,基于(一个或多个)稳定的时序,考虑到在LSI处理、温度、电压等中的变化和测试装置的约束而准备测试模式。因此,提高了测试模式的准确性。此外,不同于传统方法中,在本发明的方法中动态验证不需要大量的步骤。因此减少了测试模式准备所需的步骤数目,这最终允许高质量的测试。

具体实施方式

在依据本发明优选实施例的半导体集成电路验证方法和测试模式准备方法中,对一种测试模式是否适当进行验证。而且将该验证的测试模式(测试数据)从一个测试装置输入到一个半导体集成电路中,然后由该测试装置检测响应于该测试模式输出的信号,以测试该半导体集成电路。在下面的优选实施例中,将要描述考虑了在LSI处理、温度、电压等中的变化以及测试装置的约束而开发的半导体集成电路验证方法,并且还将讨论用于处理在那些半导体集成电路验证方法中使用的测试模式的方法。

(第一实施例)

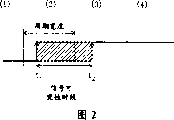

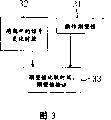

图1和图2是分别都说明了逻辑验证的示例波形结果的视图。图3是表示依据本发明第一实施例的半导体集成电路验证方法的流程图。图4表示在该实施例的半导体集成电路验证方法中使用验证工具提取信号发生改变的时段的示例。

如图3和图4所示,在下列过程中执行该实施例的半导体集成电路验证方法。

首先,准备在输入时钟的每个周期中的操作期望值31。例如,通过RTL验证获得那些操作期望值31,并且将这些值保存在存储设备等中。在此处使用的周期等于该输入时钟的一个时段。作为输入时钟,可以使用将要被验证的电路的操作时钟,或者可以使用从测试装置输入的时钟信号。操作期望值是输出信号的值,在正在输入时钟时对于各个周期确定操作期望值。

接下来,准备在给定周期中的信号变化时段32。在给定周期中的信号变化时段32可以从要被验证的电路的时序验证结果中获得。可选地,可以使用测试装置对一个实际设备进行测量,而且可以从该测量结果中提取出在给定周期中的信号变化时段32。时序验证包括通过动态验证和通过静态时序分析(STA)执行的情况。对于那些情况,其中如图4所示使用STA工具执行静态时序分析的情况是特别优选的,这是因为能够显著地缩短验证所需的时间量。

在本发明的各个实施例中,“在一个(测试)周期中的信号变化时段”是指在每个(测试)周期中信号电平发生变化的时间范围、以及与那个时间范围相关的信息。

接下来,如图3和图4所示,使用操作期望值31和在周期中的信号变化时段32,执行期望值比较时间的提取33。例如,通过专用的验证工具来执行该提取。在该实施例的验证方法中,以下列方式设定期望值比较时间,以便将操作期望值31和将要验证的电路的测量值正确地进行比较。

当将测试模式输入到将要验证的半导体集成电路中时,由于在LSI处理、测量温度和输入信号中的变化、以及在电源电压等中的变化,产生输出信号的时间发生改变。由于这个原因,如图1和图2所示,当输出信号从L电平上升到H电平时,输出信号的上升时间落入在时间t1和时间t2之间。时间t1是在以最小延迟产生输出信号的情况中的上升时间,时间t2是在以最大延迟产生输出信号的情况中的上升时间。从时间t1到时间t2的间隔在下文中将被称为“信号可变性时段”。如果一个期望值比较时间设定在信号可变性时段内,则不能正确地进行期望值比较。

因此,在如图1所示信号可变性时段短于输入时钟的周期宽度的情况中,如果在一个周期(2)中的操作期望值例如是H,则在其中执行上述期望值比较时间提取33的步骤中将期望值比较时间设置在在周期(2)之内的时间t2之后。

在如图2所示时间t2移动到出现在周期(3)中的情况中,如果在周期(2)内设置一个选通点,则不能准确地执行期望值比较。因此,存在其中在周期(2)内不设定期望值比较时间以便不进行期望值比较的情况。

例如,由通过专用软件控制的CPU执行如上所述的期望值比较时间提取33。

在其中已经预先设定了期望值比较时间33的情况中,可以在进行期望值比较时间提取33的步骤中执行有关实际产生的输出信号是否和操作期望值31相匹配的期望值验证。更具体地,可以将所测量的信号电平与期望值进行比较,以便确定测量的值是否和期望值相匹配。鉴于此,在包括图3和图4在内的随后的附图中以及在下列实施例中,执行期望值比较时间提取的步骤将被称为“期望值比较时间/期望值验证”。

应当注意到,如图4所示,在执行了期望值比较时间提取33之后,可以输出一个验证结果文件43。该验证结果文件43可以在使用计算机的分析等中使用。

在该实施例的半导体集成电路验证方法中,在其中输出信号的值可能由于在将要验证的LSI的处理、测试时的温度、输入信号的电压、电源电压等中的变化而发生改变的(一个或多个)时段中,不进行期望值比较。因此,设定了比传统的期望值比较时间更稳定的期望值比较时间,使得测试的可靠性增加。特别地,如图4所示,当使用STA工具时,不需要动态验证,这与传统示例相比减少了测试模式准备步骤的数目,由此使得显著地减少了验证所需的时间量。因此,甚至在具有较高密度的小型化集成电路的情况下,也能够在比以前更短的时间内对该电路进行验证,由此降低了制造成本和LSI设计时间的长度。

此外,如果使用了由该实施例的方法所提取的期望值比较时间,则不会在其中信号值变得不稳定的时间处执行期望值比较,这可以消除测试中的浪费并且缩短测试时间。

应当注意到:在依据该实施例的半导体集成电路集成方法中,可以将用于执行期望值比较时间提取33的验证工具并入到测试装置或者外部计算机等中。在将验证工具并入测试装置的情况下,可以在测试装置本身内部进行期望值比较时间提取33。另一方面,当将验证工具并入外部计算机等中时,缩短了使用运行成本较高的测试装置的时间量,这导致半导体集成电路制造成本的降低。

在该实施例中,已经描述了其中时间t1是延迟最小的时间而时间t2是延迟最大的时间。然而,只要信号电平变化以不同的延迟在那些时间发生,时间t1和t2可以是任何时间。

(第二实施例)

图5是表示依据本发明第二实施例的半导体集成电路验证方法的流程图。

在该实施例的验证方法中,将其中由于在LSI处理、测量时的温度、电源电压等中的变化而使信号变化时段发生改变的变化范围用作期望值验证的一个条件。

如图5所示,在下列过程中执行该实施例中的半导体集成电路验证方法。

首先,对于输入时钟的每个周期获取在最小延迟条件(以下称为“MIN延迟条件”)下的输出信号变化时段51。考虑到在LSI处理、温度、电压等中的变化而确定MIN延迟条件,并且在MIN延迟条件下,在最早的时间处产生输出信号,以便使得在将要验证的电路中该输出信号的延迟是最小的。例如,通过将与在将要验证的电路中发生的变化相关的信息输入到STA工具中,可以获得在该MIN延迟条件下的输出信号变化时段51。可选地,可以从将要验证的电路的测量结果中获得输出信号变化时段51。

接下来,为该输入时钟的每个周期获得在最大延迟条件(以下称为“MAX延迟条件”)下的输出信号变化时段52。考虑到在LSI处理、测量时的温度、电源电压等中的变化而确定MAX延迟条件,并且在MAX延迟条件下,在最晚的时间处产生一个输出信号,以便使得在将要验证的电路中该输出信号的延迟是最大的。与在MIN延迟条件下的输出信号变化时段类似,例如,可以通过输入与该变化相关的信息到STA工具中,获得在MAX延迟条件下的输出信号变化时段52。应当注意到:有可能通过获得在MAX延迟条件下的输出信号变化时段52,来省略获得在MIN延迟条件下的输出信号变化时段51的步骤。

接下来,准备操作期望值53。例如,通过RTL验证获得操作期望值53。

然后,执行期望值比较时间的提取或者期望值验证54。在该步骤中,如果事先已经设定了期望值比较时间,则执行关于实际产生的输出信号是否和操作期望值54相匹配的期望值验证。

如果并没有设定期望值比较时间,则在每个选定周期中设定期望值比较时间。在其中在MIN延迟条件下获得的在输出信号变化时段51中的信号值和在MAX延迟条件下获得的在输出信号变化时段52中的信号值都等于在那个选定周期中的期望值的时段之内,设置期望值比较时间。

以这种方式,通过覆盖所有期望在集成电路的验证期间发生的延迟变化,确定经得起那些变化的稳定选通,并且准备稳定的测试模式。此外,象在第一个实施例中那样,在没有使用动态验证的情况下对集成电路进行验证,这使得缩短了验证时间并且增加了在其中使用通过验证获得的测试模式的测试的质量。因此,缩短了半导体集成电路的开发周期,这最终降低了包括开发成本在内的整体制造成本。

在上述描述中所讨论的是一种示例性情况,其中使用在MIN延迟条件下获得的输出信号变化时段51和在MAX延迟条件下获得的输出信号变化时段52来执行期望值比较时间的提取。然而,延迟条件不局限于MIN和MAX延迟条件,并且可以使用在其它多个延迟条件下获得的输出信号变化时段来执行期望值比较时间的提取。在那种情况下,由于覆盖了那些其它多个延迟条件,所以与其中仅仅使用单个延迟条件的情况相比,还有可能确定更多的稳定选通,然后准备稳定的测试模式。

(第三实施例)

图6是用于说明依据本发明第三实施例的半导体集成电路验证方法的流程图。图7、图8和图9是时序图,表示输入时钟、输出信号的操作期望值、以及在不同的MIN延迟条件和MAX延迟条件下获得的输出信号的具体示例。

第三实施例中的半导体集成电路验证方法是一种其中使用通过时序验证获得的信号延迟状态和操作期望值的方法。

如图6所示,在该实施例的验证方法中,首先获得与MIN延迟条件下的信号状态61相关的信息。然后获得与MAX延迟条件下的信号状态62相关的信息。随后,获得操作期望值63。接下来,通过使用MIN延迟条件下的信号状态61、MAX延迟条件下的信号状态62、以及操作期望值63,由其中并入了验证工具的计算机等提取期望值比较时间或者执行期望值验证64。

在期望值比较时间提取的步骤中,如果预先已经设定了期望值比较时间,则可以执行关于实际输出信号的值是否与期望值相匹配的期望值验证。如果并没有设定期望值比较时间,则在该步骤中提取期望值比较时间。

该实施例的特征在于:考虑到分别由在MIN延迟条件和MAX延迟条件下产生的输出信号进行的跃迁,执行期望值比较时间的设置或者期望值验证。输出信号跃迁意味着信号值改变,例如从L电平到H电平的上升或者从H电平到L电平的下降。信号值包括“H”、“L”、“不固定”(这意味着信号值是未知的)等。信号强度可以由“正常电平”、“Z电平”、即断开连接状态(高阻抗)、“中间状态”(有阻抗)等表示。

接下来,将参考图7到图9讨论其中使用通过时序验证获得的信号状态来提取期望值比较时间的三个具体示例。

首先,在图7所示的示例中,在输入时钟的第一到第三周期中输出信号的操作期望值分别是L、H、和L。

在MIN延迟条件下产生的输出信号的跃迁状态中,图7中的Umin表示信号从L电平上升到H电平的时段,而图7所示的Dmin表示信号从H电平下降到L电平的时段。

此外,在MAX延迟条件下的输出信号的跃迁状态中,图7中的Umax表示信号从L电平上升到H电平的时段,而Dmax表示信号从H电平下降到L电平的时段。特别地,在MAX延迟条件下,取决于电路的结构,可能出现长的延迟,这可能导致信号变化时段延长到超过相应周期。该现象被称为“NCC(下一周期比较)”。在图7表示的示例情况中,没有出现NCC。

在这种情况下,在其中分别在MIN延迟条件和MAX延迟条件下产生的输出信号的值都等于相应操作期望值的时段中,设置期望值比较时间。然后,甚至在实际产生的输出信号的上升和下降时间发生改变的情况中也能够稳定地执行期望值比较。

更具体地,如果在图7所示的“L的通过范围”和“H的通过范围”的双头箭头指示的时间范围内设置期望值比较时间,则能够在第一到第三周期中的每一个周期中稳定地执行期望值比较。在图7的示例中,将期望值比较时间设置为信号的下降沿,即Dmax,并且从Dmax开始,设定对于输入时钟的各个周期的其它期望值比较时间,由此使得在第一到第三周期的每一个周期中稳定地进行期望值比较。在该示例中,利用处于L电平的Dmax处的期望值执行这个比较。此外,虽然在该示例中仅仅示例性地讨论了第一到第三个周期,但是依据相同时序在各个周期中设定的时间处可以在所有周期中进行期望值比较。例如,可以相对于在MAX延迟条件下获得的输出信号的下降时间Dmax设定在所有周期中的期望值比较时间。考虑到能够在测试装置中设置的时序数量是有限的,并且考虑到输入这些设置到测试装置中要耗费时间,优选的是相对于相同的时序设置在各个周期中的期望值比较时间。然而,如果存在其中不能稳定地进行期望值比较的一个(或多个)周期,并且那个(或那些)周期对于测试是重要的,则可以改变在那个(那些)周期中执行期望值比较的时间。

接下来,图8说明了在其中在MIN延迟条件下的Dmin和在MAX延迟条件下的Dmax之间的关系是(Dmax-Dmin)<1额定值的情况中获得的信号波形,其中1额定值是输入时钟的一个时段。图8表示了在其中在MAX延迟条件下获得的输出信号从H电平下降到L电平的下降时间Dmax延伸到超过周期宽度从而使得信号电平在下一个周期(即,第四周期)中发生改变的情况。

在这种情况下,在其中分别在MIN延迟条件和MAX延迟条件下产生的输出信号的值都等于相应操作期望值的时段中,设置期望值比较时间。然后,甚至在实际产生的输出信号的上升和下降时间发生改变的情况中也能够稳定地执行期望值比较。将在其中在MIN延迟条件下的输出信号电平不同于在MAX延迟条件下的输出信号电平的时段设置为“不可能稳定选通的范围”,并且在那些时段内不设置期望值比较时间。

更具体地,如果在如图8所示的“L的通过范围”和“H的通过范围”的双头箭头指示的时间范围内设置期望值比较时间,则能够在第一到第三周期的每一个周期中稳定地执行期望值比较。在图8的示例中,通过为输入时钟的各个周期相对于Dmax设置期望值比较时间,能够在第一到第三周期的每一个周期中稳定地执行期望值比较。

接下来,图9说明了在其中在MIN延迟条件下获得的Dmin和在MAX延迟条件下获得的Dmax之间的关系是(Umax-1额定值)<Dmin的情况中获得的信号波形。在该示例中,在其中在MAX延迟条件下获得的输出信号从L电平上升到H电平的时段Umax的宽度大于在其中在MIN延迟条件下获得的输出信号从H电平下降到L电平的时段Dmin的宽度。在这种情况下,不能在任何时候稳定地执行对作为第二周期的期望值的“H”的比较。在那种情况下,采用了某些测量:例如,在相对于一个不同的时序所确定的时间处执行第二周期的期望值“H”的比较。然后,即使实际上从集成电路产生的输出信号的延迟时间发生变化,也能够稳定地执行期望值比较。

如上所述,在该实施例的验证方法中,如果预先已经设定了期望值比较时间,则使用操作期望值、以及从时序验证中获得的与信号在何时以及如何发生跃迁相关的信息,来提取期望值比较时间,或者来执行关于实际产生的输出信号的值是否与期望值相匹配的期望值验证。因此,依据该实施例的验证方法,确定了经得起变化的稳定选通,并且准备了稳定的测试模式。

(第四实施例)

图10是用于说明依据本发明第四实施例的半导体集成电路验证方法的流程图。图11是表示在MAX延迟条件和测试装置的约束下获得的输出信号的时序图。

不可能将所有类型的测试模式输入到测试装置中,并且其中存在有约束。如果输入超过约束范围的测试模式,则可能不会正确地进行测试,或者测试装置可能不会接受该测试模式。作为该实施例的半导体集成电路验证方法,将要描述一种用于使用测试装置的约束对期望值比较时间和用于测试模式的期望值进行验证的方法。

如图10所示,在该实施例的半导体集成电路验证方法中,获得在测试周期中的信号变化时段101,然后将其输入到一台并入了验证工具的计算机等中(在下文中,将其简单地称为“计算机等”)。测试装置的约束102也被输入到该计算机等中。然后获得操作期望值103,并且将其输入到计算机等中。接下来,计算机等提取期望值比较时间或者执行期望值验证104。通过诸如在第一到第三实施例中讨论的时序验证获得在周期中的信号变化时段101。

如果利用等于或者大于预定值的延迟产生输出信号,则测试装置不能够执行测量。测试装置约束102包括测试装置能够测量的信号容许范围及其它项目。

在执行期望值比较时间提取时,使用了在测试周期中的信号变化时段101、测试装置约束102以及操作期望值103,使得不但考虑了测试周期信号变化时段101,而且还检查了是否满足测试装置约束102。在该步骤的最后阶段,提取期望值比较时间,或者如果预先已经设定了期望值比较时间,则可以执行关于实际输出信号的值是否与期望值相匹配的期望值验证。

例如,在其中在MAX延迟条件下获得的输出信号呈现出诸如图11所示的波形的情况中,测试装置的延迟约束在由箭头指示的时间处结束。然而,实际输出信号波形在超过该约束的时间点处从L电平上升到H电平。在那种情况下,不满足测试装置约束,这会导致测试不准确。因此,如下面将要描述的那样,如果存在一个(或多个)在其中不满足测试装置约束的周期,则处理测试模式,使得在这样的一个(或多个)周期内不执行期望值比较,以便防止包括不正确的期望值比较结果,由此增加了电路验证的可靠性。特别地,当半导体集成电路以高速运行时,相对于时钟周期的延迟增加了。因此,更佳地,该实施例的验证方法适用于以高速运行的半导体集成电路。

如上所述,依据第四实施例的验证方法,能够考虑到测试装置约束而对测试模式进行验证,这使得验证考虑了测试装置约束。

(第五实施例)

图12是用于说明依据本发明第五实施例的测试模式准备方法的流程图。图13是表示输入时钟、输出信号的操作期望值、以及分别在MIN延迟条件和MAX延迟条件下获得的输出信号的具体示例的时序图。

在第一到第四实施例中所描述的验证方法中,使用在测试周期中的信号变化时段和操作期望值来提取期望值比较时间,或者在其中已经预先设定了期望值比较时间的情况中,执行关于实际产生的输出信号的值是否与期望值相匹配的期望值验证。作为提取或者验证的结果,如果发现存在一个(或多个)其中不能进行稳定期望值比较的周期,则需要处理该测试模式,使得不在这样的一个(或多个)周期内执行期望值比较。在下文中,将要描述如何基于通过期望值验证获得的与稳定期望值比较的不可能性相关的信息来处理测试模式。

如在图12中具体所示,象在第一到第四实施例中那样,将通过STA工具等获得的在测试周期中的信号变化时段121和操作期望值122输入到验证工具等中,以提取期望值比较时间或者执行期望值验证123。在该步骤中,如果预先已经设置了期望值比较时间,则进行关于实际产生的输出信号的值是否与期望值相匹配的期望值验证。

作为期望值比较时间提取的结果,如果测试装置等确定存在一个(或多个)其中不能执行稳定期望值比较的周期,则为那个(或那些)周期产生与稳定期望值比较的不可能性相关的信息124。通过使用作为软件的验证工具控制测试装置或者计算机来实现该步骤和期望值验证步骤。

随后,基于与稳定期望值比较的不可能性相关的信息124,执行原有测试模式125的处理126,来产生一个处理过的测试模式127。

接下来,将参考图13所示的具体波形描述上述方法。

图13表示了这样一种示例,其中在MAX延迟条件下获得的输出信号中,信号从L电平上升到H电平的上升时间Umax和信号从H电平下降到L电平的下降时间Dmax都被延迟到输入时钟的第二周期之后,并且其中满足表达式Dmax-Dmin>1额定值。在这种情况下,如图13中的“方法1”所示,如果相对于Dmax确定期望值比较时间,则不能在MIN延迟条件下执行对于第一个周期的期望值“L”和第二个周期的期望值“H”的期望值比较(参见图13中所示的叉形标记)。

此外,如图13中的方法2所示,如果相对于Dmin确定期望值比较时间,则不能在MIN延迟条件下执行对于第一个周期的期望值“L”的期望值比较,而且也不能在MAX延迟条件下执行对于第三个周期的期望值“L”的期望值比较(参见图13中的叉形标记)。

象在这种情况下中那样,当在相对于单个时序确定的各个期望值比较时间处在所有周期中不能稳定地执行期望值比较时,将这样的在其中不可能进行期望值比较的一个(或多个)周期进行屏蔽,或者执行其它的处理。可选地,如方法3所示,仅可以相对于Dmax确定对于第三个周期的期望值“L”的期望值比较时间。在这种情况下,没有相对于单个时序设置在所有周期中的期望值比较时间,而是基于多个时序设定期望值比较时间。此外,如方法4表示的那样,可以相对于Umin确定期望值比较时间。

不仅可以基于Dmax和Dmin而且可以基于Umax和Umin确定在该示例中的期望值比较时间。在那种情况下,必要时还通过屏蔽其中不可能进行期望值比较的周期,通过改变在某些周期中的期望值比较时间,或者通过执行其它的处理,来稳定地执行期望值比较。

由于近来LSI已经变得日益小型化,所以存在这样一些情况,其中不能相对于单个时序(即,在每个周期中的同一个点)设置对应于延迟中的变化的稳定期望值比较时间。在这种情况下,需要对测试模式进行处理,以便屏蔽其中不能稳定地执行测试模式期望值比较的周期,或者使得在对于各个周期的适当时间处执行期望值比较,以便防止故障覆盖范围的缩小。依据该实施例的测试模式处理方法,甚至在小型化LSI的验证中,也确定了对应于变化的稳定选通,并且准备了稳定的测试模式,从而提高了测试模式的准确性,并且减少了用于准备该测试模式的步骤数目。因此,依据上述方法准备的测试模式的使用增加了半导体集成电路测试的可靠性。

(第六实施例)

图14是表示来自于测试装置的输出波形的时序图。图15是用于说明依据本发明第六实施例的半导体集成电路验证方法的流程图。图16是表示输入时钟、输出信号的操作期望值、以及分别在MIN延迟条件和MAX延迟条件下获得的输出信号的具体示例的时序图。

如图14的上部所示,在典型的逻辑验证中使用的信号波形数字地进行变化。然而,如图14的中部所示,从实际测试装置输出的测试信号的波形占用一个时段(一个跃迁时段),以改变逻辑电平。在其中信号电平发生变化的跃迁时段中,信号值不是明确的。因此,如果在这些跃迁时段内设置了诸如时间(1)和(2)的期望值比较时间,则不可能进行稳定的测试。将要在下面讨论的该实施例的半导体集成电路验证方法的特征在于:考虑了信号跃迁时段,使得在信号跃迁时段期间不执行期望值比较。

在图15中具体显示的验证方法中,通过其中使用了STA工具的时序验证等获得在测试周期中的信号变化时段151。

然后,向在测试周期中的每一个信号变化时段151中添加一个对应的信号跃迁时段(152)。该步骤提供了在测试周期中的包括跃迁时段的信号变化时段153。

接下来,将在测试周期中包括跃迁时段的信号变化时段153以及(基准)操作期望值154输入到计算机等中,以提取期望值比较时间或者执行期望值验证155。在这个步骤中,如果还没有设定期望值比较时间,则设置期望值比较时间,并且如果已经设定了期望值比较时间,则执行关于实际输出信号的值是否与期望值相匹配的期望值验证。

随后,将利用图16中所示的具体信号波形讨论上述方法。在图16所示的示例中,在输入时钟的第一到第三个周期中的输出信号的操作期望值分别是L、H、和L。

此外,在MAX延迟条件下,可以取决于电路结构增加延迟,以使得信号变化时段延长到超过相应的周期(NCC)。然而,图16表示了一种其中在MAX延迟条件下产生的输出信号中不发生NCC的情况。将图16中用斜线阴影表示的测试装置输出信号的跃迁时段分别添加到在MIN延迟条件下产生的输出信号的上升时间Umin和下降时间Dmin中。类似地,将用斜线阴影表示的跃迁时间分别添加到在MAX延迟条件下产生的输出信号的上升时间Umax和下降时间Dmax中。

在这种情况下,在其中在MIN延迟条件和MAX延迟条件下获得的各个输出信号的值都等于操作期望值的时段内,设置期望值比较时间。然后,获得在信号变化时段中经得起变化的稳定期望值比较时间。在该步骤中,不在信号跃迁时段内设置期望值比较时间。更具体地,由图16中的“L的通过范围”和“H的通过范围”的双头箭头所指示的时间范围是其中能够设置稳定期望值比较时间的时段。通过在其中在MAX延迟条件和MIN延迟条件下获得的各个输出信号的值彼此相等的时段期间指定期望值比较时间,有可能在第一到第三个周期的每一个周期中稳定地执行期望值比较。在图16所示的示例中,在信号的下降时间Dmax处设置期望值比较时间,并且从时间Dmax开始,为输入时钟的各个周期设定其它期望值比较时间,由此使得在第一到第三个周期的每一个周期中进行稳定的期望值比较。

如上所述,通过考虑信号跃迁时段,执行了基于从实际测试装置输出的信号波形的更准确的验证。因此,有可能确定稳定选通并且准备稳定的测试模式,这能够增加测试模式的准确性并且减少用于准备该测试模式的步骤数目。

应当注意到:随着测试装置内负载容量的增加,信号跃迁时段也增加了。其它导致跃迁时段发生的因素大概包括信号的反映。

在上述描述中,使用了分别在MAX延迟条件下和MIN延迟条件下产生的输出信号。然而,可以使用在彼此不同的其它多个延迟条件下产生的输出信号,来代替在这些条件下获得的输出信号。信号跃迁时段不局限于信号上升和下降所需的跃迁时段,而是可以包括信号改变到Z电平或者不固定的值所需的跃迁时段,以及信号改变所需的其它时段。

(第七实施例)

在第七实施例中,将要讨论这样一种半导体集成电路验证方法,其中对于在来自于测试装置的输出中出现的跃迁时段,考虑了由于在该测试装置内的负载容量而产生的跃迁时段。

象在第六实施例中讨论的那样,从实际测试装置输出的波形占据了一段时间(跃迁时段)来改变电平。例如,该跃迁时段是由信号波形舍入而产生的,并且依据包括测试板的测试装置的状态和信号频率的状态发生变化。特别地,测试装置之内的负载容量显著地影响信号波形的舍入。更具体地,随着负载容量的降低,信号波形的舍入也降低,而随着负载容量的增加,信号波形的舍入也增加了。

另一方面,当从LSI输出的信号处于高阻抗时,使用了这样一种方法,其中当由测试装置执行测试时使用恒流源调整信号电平。此外,在这种情况下,在跃迁时段已经过去之后,在信号到达期望电平的时间处执行测试。

接下来,参考相关附图讨论该实施例中的集成电路验证方法的过程。

图17是表示从测试装置输出的测试信号的示例性波形的时序图。图18是一个流程图,表示在对信号跃迁时段进行计算的步骤之前的该实施例中的半导体集成电路验证方法的步骤。图19是表示在提取期望值比较时间或者执行期望值验证的步骤之前的该实施例中的半导体集成电路验证方法的其它步骤。

如图18所示,将对于一种其中在测试装置内没有负载的情况的延迟信息(以下称为“没有负载的延迟信息181”)和对于一种其中在测试装置中有负载的情况的延迟信息(以下称为“有负载的延迟信息182”)输入到该测试装置的一个跃迁时段计算装置(未示出)中,以便使得跃迁时段计算部分进行信号跃迁时段的计算184。如图17所示,在来自测试装置的输出信号中,从在测试装置中有负载时获得的延迟时间中减去基于没有负载的假定而获得的延迟时间,从而计算信号跃迁时段。跃迁时段计算装置可以设置在测试装置中或者设置在一个在该测试装置外部的设备中。此外,在该步骤中,当执行高阻抗测量时,因为该测量取决于使用的(一个或多个)单元的性能,所以使用了用于计算一个信号跃迁时段的方程组。将该方程组存储作为库183。更具体地,将电源电压、恒流源的电流值、负载容量等作为参数给出,从而执行对应于所用的(一个或多个)单元的计算。如果该(一个或多个)单元包括上拉电阻,则添加该上拉电阻的值作为参数,以便更准确地计算信号跃迁时段。

另一方面,如图19所示,例如依据在第一到第四实施例中说明的过程,通过时序验证等获得在测试周期中的信号变化时段191。

接下来,使用在测试周期中的信号变化时段191和信号跃迁时段185执行信号跃迁时段的添加192,从而计算其中考虑了跃迁时段的、在测试周期中的信号变化时段(这在下面称为“包括跃迁时段的信号变化时段193”)。

然后,使用包括跃迁时段的信号变化时段193和操作期望值196,来提取期望值比较时间或者执行期望值验证197。在该步骤中,如果还没有设定期望值比较时间,则提取期望值比较时间,并且如果已经设定了期望值比较时间,则执行期望值验证。

如上所述,在该实施例的验证方法中,计算依据该测试装置的负载容量而改变的跃迁时段,并且考虑到那些跃迁时段而执行期望值比较时间的提取或者期望值验证。这能够基于从实际测试装置输出的测试信号的波形进行更准确的验证。此外,这由此允许确定稳定选通和准备稳定的测试模式,这能够提高测试模式的准确性并且减少用于准备该测试模式的步骤数目。

应当注意到:上述添加信号跃迁时段的方法不仅适用于静态验证,而且还适用于典型的动态验证。

图20是一个流程图,表示一个其中使用了动态验证的、本实施例中的半导体集成电路验证方法的改进示例。

在该改进示例中,首先,为将要验证的半导体集成电路执行动态验证,并且获得结果(即,动态验证结果201)。

另一方面,如上所述,执行信号跃迁时段计算203,以便获得信号跃迁时段204。

接下来,在信号跃迁时段204的添加之后,使用动态验证结果201和信号跃迁时段204来获得验证结果205。基于在跃迁时段添加之后的验证结果,有可能确定不适于期望值比较的时间。

(第八实施例)

图21是表示依据本发明第八实施例的半导体集成电路验证方法的流程图。

当测试高速运行的LSI时,不能将包括测试板的测试装置的负载容量视作简单的固定值来对待,而是作为一个取决于信号频率的分布常数来对待。具体地,信号跃迁时段可以表示为信号频率的一个函数。该实施例的验证方法使用一个用于从LSI的信号频率计算信号跃迁时段的装置。

更具体地,如图21所示,对将要验证的LSI执行电路模拟,从而获得模拟结果211。然后,从模拟结果211中,得出一种适当的测试模式212。

接下来,信号频率提取装置213从模拟结果211和测试模式212中提取信号频率214。例如,信号频率提取装置213是一个专用工具,而且可以并入到测试装置中,或者并入到一台在测试装置外部提供的计算机等中。

随后,跃迁时段计算装置(即,验证工具等)基于信号频率214执行信号跃迁时段计算215,由此计算信号上升和下降所需的跃迁时段(即,信号跃迁时段216)。

在该步骤中,可以基于信号频率214计算一个相应的假定负载容量,以获得其中考虑了频率的有负载的延迟信息和没有负载的延迟信息。没有负载的延迟信息和有负载的延迟信息与图18所示并且在第七实施例中所描述的那些信息相同。

作为有关该信号频率214的信息,不仅可以使用通过输入模拟结果和测试模式所提取的信息,而且还可以使用预先存储在一个在测试装置外部的设备中的频率信息。将频率信息提供给跃迁时段计算装置,并且该跃迁时段计算装置对信号跃迁时段216进行计算。

在确定了信号跃迁时段216之后,以与图19所示第七实施例中相同的方式执行后续的处理步骤。具体地,考虑到信号跃迁时段216而提取期望值比较时间,并且如果预先已经设定了期望值比较时间,则执行关于实际产生的输出信号的值是否和期望值相匹配的期望值验证。

以这种方式,通过依据信号频率计算信号跃迁时段,即使将来LSI变得能够以更高速运行,也能够基于从实际测试装置输出的波形执行高度准确的验证。更具体地,在上述方法中,能够确定稳定选通,并且能够准备稳定的测试模式,从而增加了测试模式的准确性,并且减少了用于准备该测试模式的处理步骤的数目。

应当注意到:在本实施例的半导体集成电路验证方法中,可以通过直接将模拟结果输入到信号频率提取装置213中而不是通过使用模拟结果211准备适当的测试模式212,来获得信号跃迁时段。

(第九实施例)

图22表示一个包括了在依据本发明第九实施例的半导体集成电路验证方法中使用的各种条件和延迟时间的数据库。图23是表示该实施例中的半导体集成电路验证方法的流程图。

当信号电平改变时使得信号变得不稳定的因素不仅包括由测试装置的负载容量产生的信号跃迁时段,而且还包括其它的原因,例如在测试时间期间和测试装置相关的线路阻抗的不匹配以及反射。

在实际的LSI测试中,其中信号电平由于各种因素变得不稳定的信号不稳定时段会发生变化。例如,会引起不稳定信号电平的因素(它们是影响信号跃迁时段的条件)包括:诸如测试装置、板、插座和布线之类的所采用的测试台;电源电压;诸如使用的单元类型之类的LSI的规格;以及诸如频率之类的操作条件。

本实施例的验证方法包括这样一种技术,其中计算或测量了对应于那些各种参数的信号不稳定时段,以便将其汇编到一个数据库中,使得在执行集成电路验证时,通过基于当对集成电路进行测试时那些参数可能的具体数值对数据库进行搜索,来确定信号不稳定时段(即,信号跃迁时段)。

图22所示的数据库例如包括诸如测试台、LSI规格、操作条件以及跃迁时段之类的数据项。例如,在第一行中的数据表示从LSI产生的信号从H电平改变到L电平所需要的跃迁时段是0.5纳秒。以这种方式,在该实施例中使用的数据库包括有关在各种情况中获得的跃迁时段的数据,其中这些参数以各种方式相互结合。

在下文中,将要讨论其中使用了该数据库的验证流程。

首先,如图23所示,准备在测试周期中的信号变化时段231。

接下来,向在测试周期中的信号变化时段231添加从信号跃迁时段数据库233中提取出的信号跃迁时段(232)。通过该步骤,产生在测试周期中的包括跃迁时段的信号变化时段234。

随后,通过使用操作期望值235和在测试周期中的包括跃迁时段的信号变化时段234,提取期望值比较时间或者执行期望值验证236。

以这种方式,将影响跃迁时段的条件保存在数据库中,并且将从数据库中提取出来的跃迁时段添加到在测试周期中的信号变化时段中,借此即使LSI以更高速运行,也能够执行稳定的验证。更具体地,依据该实施例的半导体集成电路验证方法,还基于从实际测试装置输出的波形执行高准确性验证。因此,确定了稳定选通,并且准备了稳定的测试模式,这提高了测试模式的准确性,并且减少了用于准备该测试模式的步骤数目。

(第十实施例)

图24是表示其中从三态输出缓冲器输出信号的示例电路的视图。图25是表示来自如图24所示的电路的输出信号的时序图。图26是表示依据本发明第十实施例的半导体集成电路验证方法的流程图。

从图24所示的三态输出缓冲器输出的信号通过两条路径(信号传输路径)C→OUT和A→OUT之中的一条。

参见在图25中从该电路产生的输出波形的具体示例,当信号通过路径C→OUT时进行涉及Z的变化,例如H到Z的变化(3)。当信号通过路径A→OUT时,进行其它的变化,例如H到L的变化(1)。以这种方式,当信号在其不同的周期中通过不同的路径时,取决于信号通过哪一条路径,信号的延迟时间发生改变。因此,为了可靠地执行期望值比较,可能要设置具体对应于各条路径的期望值比较时间。

然而,在某些测试装置中,能够在其中进行设置的时序数是有限的。因此,更佳地,基于其设置期望值比较时间的时序数尽可能少。即使设定的时序数在测试装置的约束之内,在测试装置中设置多个时序也要花费很长时间,在这种情况下进行快速的测试是不可能的。因此,最期望的情况是:相对于公共时序设置允许执行各个期望值比较的期望值比较时间,而不管信号通过哪条路径。如上所述,基本上期望的情况是:相对于单个时序设置期望值比较时间,而不管信号通过哪条路径。然而,因为近来LSI已经日益小型化,所以这样做是很困难的。相对于单个时序设置期望值比较时间,可能导致其中在信号的一个(或多个)周期中不执行期望值比较(也就是,发生期望值屏蔽)的情况。

然而,如果在对于电路操作验证关键的周期中屏蔽了期望值,则会导致诸如发生故障之类的问题。在这种情况下,需要依据测试装置的约束对执行期望值比较的时间进行划分。特别地,在图24所示的输出缓冲器的情况中,当信号通过路径C→OUT时呈现的延迟趋势可以显著地不同于当信号通过路径A→OUT时呈现的延迟趋势。因此,如果依据各个条件将期望值比较时间进行分组,则最终减少了屏蔽部分的数目,这使得更容易提取能够稳定地执行期望值比较的期望值比较时间。

该实施例的半导体集成电路验证方法是这样一种方法,其中依据信号期望值(即,信号路径)对期望值比较时间进行分组。下面将讨论这种方法。

在图24的示例中,将图25所示的部分(1)到部分(6)分成其中进行Z相关的变化的部分(3)、(4)和(6),以及其它的部分(1)、(2)和(5)。不仅可以基于信号值而且可以基于延迟量执行分组。更具体地,可以将在获得时序验证结果之后发现的具有类似延迟长度的那些部分分组在一起。

接下来,如图26所示,提取期望值比较时间,或者在其中已经预先设定了期望值比较时间的情况中,执行关于实际输出信号的值是否与期望值相匹配的期望值验证(期望值比较时间的提取或者期望值验证263)。在该步骤之前,将在测试周期中的信号变化时段261和操作期望值262输入到验证工具中。

如上所述,该方法的使用使得有效地使用了测试装置的功能,由此缩短了测试时间。此外,该方法允许测试模式验证和测试模式准备,以执行其中不减小故障覆盖范围同时允许减少为准备测试模式所需的步骤数目的高度准确的测试。

图24表示了其中存在两条信号路径的情况。然而,即使存在三条或更多路径,也能够以相同的方式执行分组以提取期望值比较时间,或者能够执行期望值验证。

(第十一实施例)

图27是用于说明依据本发明第十一实施例的半导体集成电路验证方法的时序图。图28是表示该实施例中的半导体集成电路验证方法的流程图。

在一些情况中,LSI不仅基于系统时钟(即,基准时钟)进行运行,而且基于包括异步时钟信号的多个时钟信号进行运行。在这种情况下,在一个周期接着一个周期的基础上执行电路的操作验证,并且在与异步时钟信号同步输出的信号转换为基于系统时钟的信号之后,执行该处理。该实施例的验证方法包括这样一种技术,其中通过将来自异步端子的输出信号转换成为基于基准时钟的信号来执行验证。下面将讨论该验证方法。

将如图27所示的来自端子OUT1的信号与系统时钟信号CKIN同步地输出。另一方面,将来自端子OUT2的信号与时钟信号CK同步地输出,其中时钟信号CK与系统时钟信号CKIN是异步的。

在这种情况下,使用转换成为基于系统时钟信号CKIN的周期的信号来执行测试。例如,来自端子OUT2的输出在它从L电平上升到H电平时达到最大电压值的时间最初是Umax1,它与异步时钟信号CK是同步的。在该实施例的验证方法中,转换Umax1以便使其基于系统时钟信号CKIN并且变为Umax2。执行该转换的示例性方法如下所述。在其中系统时钟信号CKIN和时钟信号CK具有相同时段但是它们的时序彼此不同的情况中,通过将Umax1移动在各个信号的上升时间或者下降时间之间的时间差值来将Umax1转换为Umax2。在其中时钟信号具有不同时段的情况中,例如,依据系统时钟信号校正时钟信号CK的时段,由此获得Umax2。

当来自端子OUT2的输出从H电平下降到L电平时,Dmax1以和在Umax1情况中相同的方式转换为Dmax2。以这种方式,不是基于异步时钟信号CK,而是基于被转换为基于系统时钟信号的信号,执行期望值比较时间的提取和期望值验证。在该实施例中,仅描述了其各个延迟最大的、来自各个端子OUT1和OUT2的输出信号,但是如在第二实施例中所述,还可以考虑到最小延迟的情况而设置期望值比较时间。

接下来,将描述该实施例中的验证方法的具体流程。

首先,如图28所示,通过使用与来自与系统时钟不同步的端子的输出的延迟相关的信息、即异步信息281,对来自与异步时钟信号同步的端子的输出进行转换,以便使其基于系统时钟(步骤282)。在该步骤中,通过上述方法执行转换。通过诸如专用验证工具之类的转换装置进行该处理。

接下来,使用所转换的信号提取在测试周期中的信号变化时段283。

随后,将在测试周期中的信号变化时段283和操作期望值284输入到验证工具等中,以便提取期望值比较时间或者执行期望值验证285。在该步骤中,设定期望值比较时间,或者在预先已经设定了期望值比较时间的情况中,执行关于实际输出信号的值是否与期望值相匹配的期望值验证。

在该步骤中,可以逐个考虑来自端子OUT1的输出和来自端子OUT2的输出,并且可以对于每一个输出设置期望值比较时间。可选地,如图27所示,在其中能够相对于单个时序设置来自端子OUT1和OUT2的输出的期望值比较时间的情况中,可以以那种方式设定期望值比较时间。相对于单个时序设置期望值比较时间是合乎需要的,这是因为能够缩短验证时间。

如上所述,依据该实施例的验证方法,既能验证来自取决于系统时钟信号(即,基准时钟信号)的端子的信号,同时又能验证来自取决于异步时钟信号的端子的信号,这扩展了该方法的应用范围。

(第十二实施例)

图29是示意地说明了将要验证的示例性集成电路的视图。图30是表示来自如图29所示的电路的输出信号的波形的时序图。图31是表示依据本发明第十二实施例的半导体集成电路验证方法的流程图。

如图29所示,依据系统时钟信号操作的电路通过几个最后级触发器和逻辑门将信号输出到一个外部端子。因此,取决于信号通过哪个触发器或者哪条路径,适当的期望值比较时间可能发生改变。

在图29所示的电路中,当将信号输出到端子OUT时发生的每个周期中的延迟,取决于信号在那个周期中通过路径A到E中的哪一条路径而发生变化。虽然信号在它的各个周期中通过的路径可能彼此不同,但是在每个周期中产生的延迟反映了相应的一条路径。通过执行动态模拟(动态验证)获得信号变化时段,能够确认信号在它的各个周期中通过的路径。

在图30所示的示例中,从动态验证结果中确认当信号从L电平上升到H电平时信号通过两条路径(即路径A和C)中的一条路径输出,并且确认当信号从H电平下降到L电平时信号通过一条路径(即,路径A)输出。因为用于每条路径的延迟时间是已知的,因此能够从每个周期中信号变化的延迟时间,确定信号在那个周期中通过的那条路径。

接下来,将参考图31描述该实施例中的路径提取方法的具体流程。

首先,执行动态验证311以获得模拟结果312。在这个步骤中,可以在可能的条件中的一个条件下,诸如MAX延迟条件、MIN延迟条件、或者其中考虑了由于测试装置内的容量而引起延迟的条件等条件下,执行该模拟。

然后,使用模拟结果312执行路径检测313。在该步骤中,验证工具从模拟结果312中检测在信号变化中的延迟时间,由此,例如,提取对于每个信号变化点的信号路径。在该步骤中,路径结果314可以输出作为检测结果。

图32表示在该实施例的验证方法中获得的路径检测结果。图32包括诸如输出端子、周期数、信号变化以及延迟时间之类的数据项,并且显示了在哪个周期中具有多少延迟以及信号如何变化。如果各个期望周期的开始时间是已知的,则还可以从动态验证中获得图32中所示的延迟时间。

在该实施例中,显示的路径结果用来设定期望值比较时间或者执行期望值验证。

路径结果可以输出作为文件。如果在一个(或多个)周期中存在不期望的信号变化,则可以使用这个文件执行用于屏蔽那个(或那些)周期的处理,以便不在那个(或那些)周期中执行期望值比较。

如上所述,在该实施例的验证方法中,即使在将要验证的电路中存在多条路径,仅通过执行动态验证至少一次来执行路径检测,这与其中必须多次执行动态验证的情况相比较,缩短了执行电路验证所需的时间量。此外,作为路径检测的结果,能够识别出来自不期望该信号通过的不必要路径的输出,以便使得不将这种输出和期望值进行比较。这因此允许准备一种允许稳定测试的测试模式,从而增加了试验的准确性。

(第十三实施例)

图33表示在依据本发明第十三实施例的半导体集成电路验证方法中获得的路径检测结果。图34是表示该实施例中的半导体集成电路验证方法的流程图。

能够使用静态时序分析计算在目标电路路径中的信号延迟。例如,通过相对于图30所示的输出信号执行静态时序分析,能够计算诸如图33所示的结果。在该示例中,在信号从L电平上升到H电平的情况中,信号通过五条路径中的一条路径,并且在每个上升段中都存在延迟时间。如果将如图33中所示的结果和通过动态验证获得的如图32所示的路径结果一起检查,则可以发现在模拟过程中在第一个周期中信号通过路径A输出,在第三个周期中信号通过路径A输出,在第六个周期中信号通过路径C输出,以及在第七个周期中信号通过路径A输出。如上所述,该实施例中的验证方法包括一种用于指定路径的技术,其通过使用静态时序分析和动态验证结果在模拟期间起作用。

接下来,将参考图34描述该实施例中的有效路径提取方法的具体流程。

首先,执行动态验证341以获得模拟结果342。

然后,使用模拟结果342执行路径检测343。考虑到动态验证需要非常长的时间,所以以该方法中的至少一种模式获得模拟结果是足够的,这是因为在该方法中将该模拟结果用作用于执行路径提取的信息。

另一方面,以与动态验证相同的模式执行静态时序分析344,以便输出诸如图33所示的路径信息和对于各条路径的在测试周期中的信号变化时段345。

随后,使用路径信息、对于各条路径的测试周期信号变化时段345、以及路径检测343的结果(即,路径结果347)执行有效的路径提取346。在该步骤中,使用的有效路径提取装置是一种专用工具等,而且路径结果347可以包括但不是必须包括在有效路径提取装置中。

以这种方式,为各条路径指定有效路径,并且以此为基础,设定期望值比较时间或者执行期望值比较。这最终确定了经得起变化的稳定选通,从而允许准备稳定的测试模式。此外,依据如上所述的验证方法,不需要以多种模式进行耗时的动态验证。因此,与使用动态验证的传统验证方法相比,更加快速地执行了具有多条路径的电路的操作验证。

象在扫描测试的情况中那样,在其中目标输出端子是有限的情况中,如果在验证中没有使用其它非目标端子,则在上述方法中缩短了处理时间。在这种情况下,在没有考虑在动态模拟和静态时序分析中的那些其它非目标端子的情况下执行该处理,以便最终提取有效的路径。-第十三实施例中的半导体集成电路验证方法的改进示例-

图35是表示在MIN延迟条件和MAX延迟条件下获得的、来自将要验证的集成电路的输出信号的时序图。图36是表示第十三实施例的验证方法的一个改进示例的流程图。

如图36所示,在该改进示例的半导体集成电路验证方法中,分别以多种模式执行动态验证341和静态时序分析344,并且以各种模式执行有效路径提取346。而且在一个周期接着一个周期的基础上将在各种模式中提取的、在该周期中的有效路径相互进行比较。

在图35所示的示例中,其中在MIN延迟条件和MAX延迟条件下提取有效路径,在MIN延迟条件下在第一个周期中使用的路径不同于在MAX延迟条件下在第一个周期中使用的路径。象在这种情况下那样,如果为相同的周期提取了不同的路径,则假定该电路操作是异常的。

在该实施例的验证方法中,有效路径提取装置具有在两种或更多种模式下获得的有效路径之间进行比较以便检查该电路操作的功能。包括有效路径提取装置的验证工具可以用于自动地屏蔽其中提取了不同有效路径的任何检测到的周期,以便在那些周期中不执行期望值比较。

这与其中使用在单种模式中获得的模拟结果和时序分析结果的第十三实施例的方法相比,将故障检测的准确度提高到一个更高的程度。然而,在该改进示例的验证方法中,动态验证执行两次或更多次,使得验证时间增加。因此,根据需要可以适当地选择第十三实施例的验证方法和这个改进示例的验证方法。

(第十四实施例)

图37表示这样的数据,例如当来自图29所示的电路的输出信号在其中没有负载和有负载的情况下电平改变时出现的延迟时间。图38A到图38C表示依据本发明第十四实施例的半导体集成电路验证方法和测试模式准备方法。

LSI需要依据不同的负载容量进行操作。例如,在设计的上游阶段,LSI需要执行没有负载的逻辑操作、以及具有其中使用了LSI的设置的具有负载容量的操作。而且当使用测试装置执行测试时,LSI需要在测试装置内存在负载容量的情况下进行操作。在测试装置内的负载容量取决于测试装置的类型而发生改变。因此,当将测试装置替换为不同的一个测试装置时,就必须考虑对应于那个不同设备的负载容量的操作。此外,假定LSI的操作发生了变化,LSI必须在多种模式(例如,MIN和MAX)下可靠地操作。

传统上,为了确保这样的操作,必需依据各个负载容量以多种模式执行动态验证。

相反,在该实施例的半导体集成电路验证方法中,在实际上没有执行耗时的动态验证的情况下输出动态验证的伪结果。

假定在图29所示的电路中,以给定模式进行诸如如图30所示的动态信号变化。更具体地,假定其中将要分析的电路与第十三实施例中的电路相同的情况,并且有效的路径指定结果表明在第一个周期中信号通过路径A并且从L电平变化到H电平,在第三个周期中信号通过路径A并且从H电平变化到L电平,且在第六个周期中信号通过路径C并且从H电平变化到L电平。

首先,如图38A所示,执行静态时序分析361,以便产生在多种模式下对应于假定的负载容量的、在各条路径中的信号变化时段。通过这样做,获得了信号变化时段的列表362。在图37中的信号变化时段列表的具体示例显示了在各种负载条件下在MIN延迟和MAX延迟的情况中,信号如何在通过路径A和C时发生变化,例如从L电平改变到H电平以及从H电平改变到L电平,其中各种负载条件包括:没有负载、具有其中并入了LSI的设置的负载容量、具有测试装置(测试器)A的负载容量;以及具有测试装置B的负载容量。每个延迟值都可以表示为利用认为是0的给定基准负载容量得到的差值。

接下来,如图38B所示,伪模拟结果计算装置366基于由第十三实施例中的方法产生的信号变化时段362和有效路径指定结果364来输出伪模拟结果367。伪模拟结果367能够作为在各种模式中各个负载容量存在时获得的动态验证结果进行处理。在这个步骤中,如果已经获得了至少在一种模式中的动态验证结果,则可以输出在多个模式下的伪模拟结果。例如,伪模拟结果计算装置366是诸如验证工具之类的软件,而且可以将其并入到测试装置或者外部设备中。

接下来,如图38C所示,可以让测试模式验证装置370使用多个伪模拟结果367执行测试模式验证,并且由此提取一种其在多种模式中存在各个负载容量时稳定操作的测试模式371。应当注意到:在其中期望提取期望值比较时间的情况中,不需要输入信号,并且如果基于伪模拟结果367而不使用任何输入信号产生期望值比较时间,则能够显著地减小数据大小。

如上所述,在该方法中,仅通过至少在一种模式下执行动态验证,就能够以一种伪方式计算在其它模式中或者在其它负载容量条件下的动态验证结果。特别地,在该方法中,无须多次执行动态验证,这使得有可能在与传统方法相比更短的时间内输出和动态验证等效的结果。此外,能够在更短的时间内执行对应于各种负载容量的期望值比较时间的提取以及执行期望值验证。

(第十五实施例)

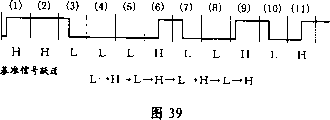

图39是表示来自于将要验证的电路的示例输出信号的时序图。图40是表示依据本发明第十五实施例用于检查半导体集成电路的操作的方法的流程图。图41是表示该实施例中的半导体集成电路验证方法的流程图。

通常,已经确定了操作电路时所参考的期望值,并且还已经确定了由一个信号造成的跃迁。

在下文中,将要描述诸如图39所示、期望其输出的信号会进行跃迁的示例电路。在该示例中,输出信号整个来说进行了L→H→L→H→L→H→L→H的跃迁。例如,如果比较的信号进行L→H→L→Z的跃迁,则确定该电路没有正确地操作。另一方面,当查看每个周期时,信号在第三个周期中进行H到L的跃迁。除非信号电平H和L在第三个周期中都存在,否则H到L的跃迁是不可能的。因此,在那种情况下,也确定该电路没有正确地操作。此外,如果预期的H到L的跃迁在所有周期中都不存在,则该周期中也没有正确地操作。另一方面,如果在一个其中不应该发生L到H的跃迁的周期中存在L到H的跃迁,则发现该电路没有正确地操作。如上所述,第十五实施例涉及一种用于基于信号跃迁确定电路是否正确操作的方法。

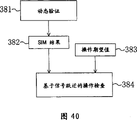

将参考图40和图41描述该实施例中的半导体集成电路验证方法的具体过程。

首先,为将要验证的集成电路执行动态验证381,并且获得模拟结果382。

然后,使用已经分别准备了的模拟结果382和操作期望值383,以便基于信号跃迁执行操作检查。通过例如在第一和第二实施例中使用的验证工具执行该步骤,或者由一个专用工具执行该步骤。在其中仅期望对信号电平跃迁进行检测的情况中,该过程可以结束于这个步骤。在其中将对集成电路的操作进行验证的情况中,该过程进行到下一步骤。

接下来,如图41所示,通过有效路径提取装置执行有效路径提取395。在该步骤中,例如,通过在第十三实施例中说明的方法在每个周期中指定有效路径。

随后,使用基于信号跃迁和有效路径提取结果执行的操作检查结果,执行期望值比较时间的提取或者期望值验证396。通过在该步骤之前执行有效路径提取395,有可能预先检查到在期望值比较时间提取或者期望值验证中使用的、诸如模拟结果382和操作期望值383之类的数据是否是电路正确操作时获得的数据。

在该实施例的验证方法中,如果仅按照信号跃迁简单地检查电路操作,则能够使用基于验证结果准备的测试模式来执行和周期无关的操作检查。在这种情况下,有可能识别出一种其中即使LSI在通过常规方法执行的测试中似乎正确地操作但是该LSI实际是有缺陷的情况,这是因为这种传统测试在一个周期接着一个周期的基础上进行。

在上述示例性情况中,使用了将要参考的操作期望值和在目标模式中获得的模拟结果。然而,这个实施例的验证方法适用于其中在输入诸如MIN条件和MAX条件之类的多个模式中获得的模拟结果的情况。这提供了更准确的电路验证。

(第十六实施例)

图42是表示依据本发明第十六实施例的用于检查半导体集成电路的操作的方法的流程图。图43是表示该实施例的半导体集成电路验证方法的流程图。

在图37所示并且在第十五实施例中说明的示例中,信号整个来说进行了L→H→L→H→L→H→L→H的跃迁,这意味着信号总共进行了七次跃迁。在图37所示的那些部分中,如果所比较的信号进行的跃迁数目不是七次,则确定要验证的电路没有正确地操作。另一方面,当查看下降次数和上升次数时,发现进行了四次L到H的跃迁和三次H到L的跃迁。如果L到H的跃迁的次数不是四次,则确定该电路没有正确地操作。此外,当查看每个周期中的信号跃迁时,信号在第一个周期中经历一次L到H的跃迁。因此,如果在第一个周期中的信号跃迁次数不是一次,则确定该电路没有正确地操作。以这种方式,在该实施例的操作检查方法和半导体集成电路验证方法中,根据信号跃迁次数确定电路是否正确地操作。

将参考图42和图43,描述该实施例中的半导体集成电路验证方法的具体过程。

首先,为将要验证的集成电路执行动态验证401,并且获得模拟结果402。

然后,依据信号跃迁使用已经分别准备了的模拟结果402和操作期望值403,以进行操作检验。在该步骤中,通过如上所述监视信号跃迁的次数确定集成电路是否正确地操作。在一种其中仅期望检查信号电平跃迁次数的情况中,该过程可以在该步骤结束。在一种其中验证集成电路的操作的情况中,该过程进行到下一步骤。

随后,如图43所示,通过有效路径提取装置执行有效路径提取415。在该步骤中,例如,通过在第十三实施例中说明的方法指定在每个周期中的有效路径。

随后,使用基于信号跃迁和有效路径提取结果的操作检查结果,执行期望值比较时间的提取或者期望值验证416。通过在该步骤之前执行有效路径提取415,可以预先快速地检查在期望值比较时间提取或者期望值验证中使用的数据是否是电路正确操作时获得的数据。

在该实施例的半导体集成电路验证方法中,可以有效地准备用于检测不能由传统测试所检测的故障类型的测试模式。此外,如果还执行了期望值比较时间提取或者期望值验证,则能够进行电路操作验证,而不导致验证时间的显著增加。

在上述示例性的情况中,使用了将要参考的操作期望值和在目标模式中获得的模拟结果。然而,该实施例的验证方法适用于其中输入在诸如MIN条件和MAX条件之类的多种模式中获得的模拟结果的情况。

(第十七实施例)

图44和图45是分别都表示依据本发明第十七实施例的测试模式处理方法的流程图。

在前面的实施例中描述的半导体集成电路验证方法中,使用在测试周期中的信号变化时段和操作期望值来提取期望值比较时间,并且在一种其中已经预先设定了期望值比较时间的情况中,执行关于实际输出信号的值是否与操作期望值相匹配的期望值验证。

另一方面,如图44和图45所示,将在该实施例中描述如何通过使用通过时序验证获得的在测试周期中的信号变化时段421和原有测试模式中的操作期望值422执行原有测试模式的处理423,来准备所处理的测试模式424。

在下文中,将参考图44和图45描述该实施例的测试模式准备方法的具体过程。

首先,准备在测试周期中的信号变化时段421。如图45所示,可以通过诸如STA之类的验证工具提取在测试周期中的信号变化时段421,或者可以在实际设备中使用测试装置提取该信号变化时段421。当使用STA时,动态验证不是必需的,这使得处理更快。

接下来,使用在测试周期中的信号变化时段421执行测试模式处理423,由此产生处理的测试模式424。在该步骤中,例如,屏蔽其中不能进行期望值比较的一个(或多个)周期,或者改变在那个(或那些)周期中的期望值比较时间,以便使得它们能基于不同的时序。

以这样的方式,依据该方法,准备了具有稳定选通点的测试模式以增加测试模式的准确性,同时减少了准备测试模式所必需的步骤数目,这与传统情况相比较,最终允许了更精确和高度准确的电路测试。

如上所述,本发明中的半导体集成电路验证方法和测试模式准备方法用于对LSI进行测试,并且例如,适用于开发和制造半导体集成电路。