BR112018005973B1 - Armazenadores de tensão-retardo inversamente proporcionais para armazenar dados de acordo com níveis de tensão de dados - Google Patents

Armazenadores de tensão-retardo inversamente proporcionais para armazenar dados de acordo com níveis de tensão de dados Download PDFInfo

- Publication number

- BR112018005973B1 BR112018005973B1 BR112018005973-0A BR112018005973A BR112018005973B1 BR 112018005973 B1 BR112018005973 B1 BR 112018005973B1 BR 112018005973 A BR112018005973 A BR 112018005973A BR 112018005973 B1 BR112018005973 B1 BR 112018005973B1

- Authority

- BR

- Brazil

- Prior art keywords

- signal

- data

- data input

- input signal

- logic state

- Prior art date

Links

- 230000007704 transition Effects 0.000 claims abstract description 33

- 230000004044 response Effects 0.000 claims description 41

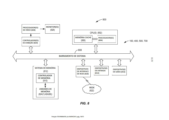

- 238000000034 method Methods 0.000 claims description 17

- 239000004065 semiconductor Substances 0.000 claims description 8

- 229910044991 metal oxide Inorganic materials 0.000 claims description 7

- 150000004706 metal oxides Chemical class 0.000 claims description 7

- 238000004891 communication Methods 0.000 claims description 3

- 230000003139 buffering effect Effects 0.000 claims 1

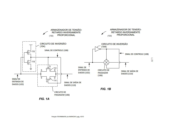

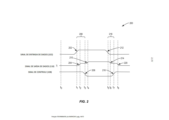

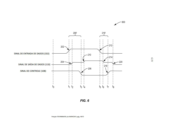

- 238000010586 diagram Methods 0.000 description 19

- 230000008569 process Effects 0.000 description 8

- 230000004913 activation Effects 0.000 description 6

- 230000008859 change Effects 0.000 description 2

- 230000001934 delay Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000008901 benefit Effects 0.000 description 1

- 239000000872 buffer Substances 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 210000004027 cell Anatomy 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 238000003874 inverse correlation nuclear magnetic resonance spectroscopy Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 210000002569 neuron Anatomy 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/003—Modifications for increasing the reliability for protection

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/003—Modifications for increasing the reliability for protection

- H03K19/00315—Modifications for increasing the reliability for protection in field-effect transistor circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0175—Coupling arrangements; Interface arrangements

- H03K19/0185—Coupling arrangements; Interface arrangements using field effect transistors only

- H03K19/018507—Interface arrangements

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Logic Circuits (AREA)

- Pulse Circuits (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/863,710 | 2015-09-24 | ||

| US14/863,710 US9467143B1 (en) | 2015-09-24 | 2015-09-24 | Inversely proportional voltage-delay buffers for buffering data according to data voltage levels |

| PCT/US2016/051073 WO2017053090A1 (en) | 2015-09-24 | 2016-09-09 | Inversely proportional voltage-delay buffers for buffering data according to data voltage levels |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| BR112018005973A2 BR112018005973A2 (pt) | 2018-10-16 |

| BR112018005973B1 true BR112018005973B1 (pt) | 2023-04-25 |

Family

ID=57046514

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| BR112018005973-0A BR112018005973B1 (pt) | 2015-09-24 | 2016-09-09 | Armazenadores de tensão-retardo inversamente proporcionais para armazenar dados de acordo com níveis de tensão de dados |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US9467143B1 (enExample) |

| EP (1) | EP3353894A1 (enExample) |

| JP (1) | JP7159044B2 (enExample) |

| KR (1) | KR102604585B1 (enExample) |

| CN (1) | CN108141213B (enExample) |

| BR (1) | BR112018005973B1 (enExample) |

| WO (1) | WO2017053090A1 (enExample) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9467143B1 (en) | 2015-09-24 | 2016-10-11 | Qualcomm Incorporated | Inversely proportional voltage-delay buffers for buffering data according to data voltage levels |

| US10796729B2 (en) * | 2019-02-05 | 2020-10-06 | Micron Technology, Inc. | Dynamic allocation of a capacitive component in a memory device |

| US10979049B2 (en) * | 2019-05-03 | 2021-04-13 | Taiwan Semiconductor Manufacturing Company Ltd. | Logic buffer circuit and method |

| US11349458B1 (en) * | 2021-09-22 | 2022-05-31 | Microsoft Technology Licensing, Llc | Transistor aging monitor circuit for increased stress-based aging compensation precision, and related methods |

Family Cites Families (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS532315B2 (enExample) * | 1972-10-18 | 1978-01-26 | ||

| US4700089A (en) * | 1984-08-23 | 1987-10-13 | Fujitsu Limited | Delay circuit for gate-array LSI |

| JPH0834418B2 (ja) * | 1984-08-23 | 1996-03-29 | 富士通株式会社 | 遅延回路 |

| JPH07107978B2 (ja) | 1985-11-07 | 1995-11-15 | ロ−ム株式会社 | C−mos回路 |

| KR900008436B1 (ko) | 1987-12-08 | 1990-11-20 | 삼성반도체통신 주식회사 | 듀얼 슬로프 파형 발생회로 |

| US5151622A (en) * | 1990-11-06 | 1992-09-29 | Vitelic Corporation | CMOS logic circuit with output coupled to multiple feedback paths and associated method |

| US5120992A (en) * | 1991-07-03 | 1992-06-09 | National Semiconductor Corporation | CMOS output driver with transition time control circuit |

| JPH05191232A (ja) * | 1992-01-08 | 1993-07-30 | Oki Micro Design Miyazaki:Kk | 遅延回路 |

| JPH05218828A (ja) * | 1992-02-04 | 1993-08-27 | Hitachi Ltd | 遅延回路 |

| US5376848A (en) * | 1993-04-05 | 1994-12-27 | Motorola, Inc. | Delay matching circuit |

| US5903169A (en) * | 1996-07-24 | 1999-05-11 | Lg Semicon Co., Ltd. | Charge recycling differential logic (CRDL) circuit and storage elements and devices using the same |

| US6031393A (en) | 1997-12-31 | 2000-02-29 | Intel Corporation | Pass gate input buffer for a mixed voltage environment |

| US6084430A (en) * | 1997-12-31 | 2000-07-04 | Intel Corporation | Input buffer for a mixed voltage environment |

| US6236237B1 (en) | 1998-02-27 | 2001-05-22 | Altera Corporation | Output buffer predriver with edge compensation |

| KR100297715B1 (ko) * | 1998-09-01 | 2001-08-07 | 윤종용 | 출력버퍼제어회로및출력제어신호발생방법 |

| US6150862A (en) | 1998-10-15 | 2000-11-21 | Intel Corporation | Stable delay buffer |

| US6198308B1 (en) | 1999-03-30 | 2001-03-06 | Fairchild Semiconductor Corp. | Circuit for dynamic switching of a buffer threshold |

| US6292041B1 (en) * | 2000-02-16 | 2001-09-18 | Hewlett Packard Company | Circuit and method for limiting subthreshold leakage |

| JP2001256785A (ja) * | 2000-03-13 | 2001-09-21 | Toshiba Corp | クロックバッファ回路およびこのクロックバッファ回路を有するインタフェースならびに同期型半導体記憶装置 |

| JP2002009606A (ja) * | 2000-06-27 | 2002-01-11 | Nec Corp | 半導体回路 |

| US7098694B2 (en) | 2004-11-12 | 2006-08-29 | Agere Systems Inc. | Overvoltage tolerant input buffer |

| US7562271B2 (en) * | 2005-09-26 | 2009-07-14 | Rambus Inc. | Memory system topologies including a buffer device and an integrated circuit memory device |

| KR100632626B1 (ko) * | 2005-10-14 | 2006-10-09 | 주식회사 하이닉스반도체 | 데이터 입출력 동작시 소비 전류를 감소시키는 클럭 제어회로와 이를 포함하는 반도체 메모리 장치 및 그 데이터입출력 동작 방법 |

| US7405606B2 (en) * | 2006-04-03 | 2008-07-29 | Intellectual Ventures Fund 27 Llc | D flip-flop |

| KR101197272B1 (ko) | 2009-10-30 | 2012-11-05 | 에스케이하이닉스 주식회사 | 데이터출력회로 |

| TWI445310B (zh) * | 2010-12-27 | 2014-07-11 | Au Optronics Corp | 移位暫存器 |

| CN102204105B (zh) * | 2011-05-30 | 2013-08-07 | 华为技术有限公司 | 一种i/o电路和集成电路 |

| KR20130042244A (ko) | 2011-10-18 | 2013-04-26 | 에스케이하이닉스 주식회사 | 신호 전달 회로 및 이를 포함하는 플립플롭 회로 |

| US8872570B2 (en) * | 2012-12-28 | 2014-10-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Multiple power domain circuit and related method |

| KR20150080098A (ko) * | 2013-12-30 | 2015-07-09 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| JP2015177347A (ja) * | 2014-03-14 | 2015-10-05 | 株式会社東芝 | レベルシフト回路 |

| US9467143B1 (en) | 2015-09-24 | 2016-10-11 | Qualcomm Incorporated | Inversely proportional voltage-delay buffers for buffering data according to data voltage levels |

-

2015

- 2015-09-24 US US14/863,710 patent/US9467143B1/en active Active

-

2016

- 2016-08-31 US US15/252,335 patent/US9667250B2/en active Active

- 2016-09-09 CN CN201680054591.8A patent/CN108141213B/zh active Active

- 2016-09-09 WO PCT/US2016/051073 patent/WO2017053090A1/en not_active Ceased

- 2016-09-09 EP EP16778137.6A patent/EP3353894A1/en not_active Withdrawn

- 2016-09-09 JP JP2018515039A patent/JP7159044B2/ja active Active

- 2016-09-09 BR BR112018005973-0A patent/BR112018005973B1/pt active IP Right Grant

- 2016-09-09 KR KR1020187011520A patent/KR102604585B1/ko active Active

Also Published As

| Publication number | Publication date |

|---|---|

| KR102604585B1 (ko) | 2023-11-20 |

| JP7159044B2 (ja) | 2022-10-24 |

| WO2017053090A1 (en) | 2017-03-30 |

| US9667250B2 (en) | 2017-05-30 |

| US20170093397A1 (en) | 2017-03-30 |

| KR20180058793A (ko) | 2018-06-01 |

| JP2018534819A (ja) | 2018-11-22 |

| EP3353894A1 (en) | 2018-08-01 |

| US9467143B1 (en) | 2016-10-11 |

| CN108141213B (zh) | 2021-07-09 |

| BR112018005973A2 (pt) | 2018-10-16 |

| CN108141213A (zh) | 2018-06-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN105900177B (zh) | 读出电阻式存储器比特单元的状态的方法和系统 | |

| BR112018005973B1 (pt) | Armazenadores de tensão-retardo inversamente proporcionais para armazenar dados de acordo com níveis de tensão de dados | |

| US8913425B2 (en) | Phase change memory mask | |

| CN111798891B (zh) | 生成四相时钟信号的时钟信号生成器 | |

| US9960596B2 (en) | Automatic voltage switching circuit for selecting a higher voltage of multiple supply voltages to provide as an output voltage | |

| US9768779B2 (en) | Voltage level shifters employing preconditioning circuits, and related systems and methods | |

| JP6639391B2 (ja) | メモリ読取りアクセス中のパワーグリッチを低減するためのスタティックランダムアクセスメモリ(sram)グローバルビット線回路、ならびに関連する方法およびシステム | |

| KR102398541B1 (ko) | 반도체장치 및 반도체시스템 | |

| JP5595240B2 (ja) | 半導体装置 | |

| US10558255B2 (en) | Hybrid hardware/firmware power management controller for media devices | |

| CN107852150A (zh) | 采用脉冲产生电路的动态电压电平移位器以及相关系统和方法 | |

| CN110047526A (zh) | 包括校准设备的存储设备 | |

| TW201841159A (zh) | 半導體裝置 | |

| US9412434B1 (en) | Semiconductor device and semiconductor system for performing an initialization operation | |

| CN105322942A (zh) | 半导体装置的接收器电路 | |

| BR112018002833B1 (pt) | Circuito comutado de controle de potência para controlar a taxa de fornecimento de tensões a circuitos alimentados, e método e sistema relacionados | |

| CN106469568B (zh) | 周期信号发生电路和包括其的半导体系统 | |

| WO2017122418A1 (ja) | 半導体記憶装置、および、半導体記憶装置の制御方法 | |

| CN106024045A (zh) | 半导体器件 | |

| WO2016157719A1 (ja) | 半導体記憶装置の書き換え方法及び半導体記憶装置 | |

| CN103903643B (zh) | 半导体装置的数据写入电路 | |

| US8861303B2 (en) | Circuit and method for address transition detection | |

| CN108694965A (zh) | 半导体器件、操作半导体器件的方法以及包括其的系统 | |

| US8634269B2 (en) | Data output circuit of semiconductor memory apparatus | |

| TW202316429A (zh) | 積體電路、資料暫存器裝置及正反器電路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| B06U | Preliminary requirement: requests with searches performed by other patent offices: procedure suspended [chapter 6.21 patent gazette] | ||

| B09A | Decision: intention to grant [chapter 9.1 patent gazette] | ||

| B16A | Patent or certificate of addition of invention granted [chapter 16.1 patent gazette] |

Free format text: PRAZO DE VALIDADE: 20 (VINTE) ANOS CONTADOS A PARTIR DE 09/09/2016, OBSERVADAS AS CONDICOES LEGAIS |