WO2022106953A1 - 半導体装置、及び半導体装置の作製方法 - Google Patents

半導体装置、及び半導体装置の作製方法 Download PDFInfo

- Publication number

- WO2022106953A1 WO2022106953A1 PCT/IB2021/060296 IB2021060296W WO2022106953A1 WO 2022106953 A1 WO2022106953 A1 WO 2022106953A1 IB 2021060296 W IB2021060296 W IB 2021060296W WO 2022106953 A1 WO2022106953 A1 WO 2022106953A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- layer

- insulating layer

- conductive layer

- transistor

- semiconductor

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 562

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 59

- 239000000758 substrate Substances 0.000 claims abstract description 150

- 238000000034 method Methods 0.000 claims abstract description 130

- 238000012545 processing Methods 0.000 claims description 33

- 238000009413 insulation Methods 0.000 abstract description 20

- 239000010410 layer Substances 0.000 description 1746

- 239000010408 film Substances 0.000 description 349

- 229910052760 oxygen Inorganic materials 0.000 description 166

- 239000001301 oxygen Substances 0.000 description 166

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 165

- 229910044991 metal oxide Inorganic materials 0.000 description 137

- 150000004706 metal oxides Chemical class 0.000 description 137

- 239000011701 zinc Substances 0.000 description 127

- 239000007789 gas Substances 0.000 description 90

- 230000006870 function Effects 0.000 description 82

- 239000004973 liquid crystal related substance Substances 0.000 description 64

- MWUXSHHQAYIFBG-UHFFFAOYSA-N nitrogen oxide Inorganic materials O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 61

- 239000001257 hydrogen Substances 0.000 description 54

- 229910052739 hydrogen Inorganic materials 0.000 description 54

- 239000000463 material Substances 0.000 description 53

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 50

- 230000015572 biosynthetic process Effects 0.000 description 50

- 238000010438 heat treatment Methods 0.000 description 44

- 239000012298 atmosphere Substances 0.000 description 43

- 238000009832 plasma treatment Methods 0.000 description 43

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 40

- 229910001868 water Inorganic materials 0.000 description 40

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 34

- 238000004140 cleaning Methods 0.000 description 34

- 229910052581 Si3N4 Inorganic materials 0.000 description 33

- 229910052814 silicon oxide Inorganic materials 0.000 description 32

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 29

- 239000012535 impurity Substances 0.000 description 29

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 28

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 25

- 238000004544 sputter deposition Methods 0.000 description 25

- 230000001590 oxidative effect Effects 0.000 description 24

- 230000008569 process Effects 0.000 description 24

- 229910052751 metal Inorganic materials 0.000 description 23

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical group [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 22

- 229910021529 ammonia Inorganic materials 0.000 description 22

- 239000013078 crystal Substances 0.000 description 22

- 230000007547 defect Effects 0.000 description 22

- 239000002184 metal Substances 0.000 description 22

- 239000000203 mixture Substances 0.000 description 21

- 239000004020 conductor Substances 0.000 description 20

- 150000002431 hydrogen Chemical class 0.000 description 20

- 230000001603 reducing effect Effects 0.000 description 20

- 238000009792 diffusion process Methods 0.000 description 19

- 230000001965 increasing effect Effects 0.000 description 18

- 229910052738 indium Inorganic materials 0.000 description 18

- 239000011347 resin Substances 0.000 description 18

- 229920005989 resin Polymers 0.000 description 18

- 238000005477 sputtering target Methods 0.000 description 18

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 17

- 229910052782 aluminium Inorganic materials 0.000 description 17

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 17

- 229910052802 copper Inorganic materials 0.000 description 17

- 239000010949 copper Substances 0.000 description 17

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 16

- 239000010409 thin film Substances 0.000 description 16

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 15

- 229910052710 silicon Inorganic materials 0.000 description 15

- 239000010703 silicon Substances 0.000 description 15

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 14

- 229910001882 dioxygen Inorganic materials 0.000 description 14

- 229910052733 gallium Inorganic materials 0.000 description 14

- 239000011241 protective layer Substances 0.000 description 14

- -1 silicon nitride nitride Chemical class 0.000 description 14

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 13

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 12

- 206010021143 Hypoxia Diseases 0.000 description 12

- 229910052757 nitrogen Inorganic materials 0.000 description 12

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 11

- 238000005530 etching Methods 0.000 description 11

- 150000004767 nitrides Chemical class 0.000 description 11

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 11

- 229910045601 alloy Inorganic materials 0.000 description 10

- 239000000956 alloy Substances 0.000 description 10

- 230000004888 barrier function Effects 0.000 description 10

- 239000012528 membrane Substances 0.000 description 10

- 230000003287 optical effect Effects 0.000 description 10

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 9

- 238000005229 chemical vapour deposition Methods 0.000 description 9

- 230000007812 deficiency Effects 0.000 description 9

- 239000011521 glass Substances 0.000 description 9

- 229910000449 hafnium oxide Inorganic materials 0.000 description 9

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 9

- 239000011810 insulating material Substances 0.000 description 9

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 9

- 229910052721 tungsten Inorganic materials 0.000 description 9

- 239000010937 tungsten Substances 0.000 description 9

- 238000001039 wet etching Methods 0.000 description 9

- 229910052725 zinc Inorganic materials 0.000 description 9

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 8

- 125000004429 atom Chemical group 0.000 description 8

- 238000001312 dry etching Methods 0.000 description 8

- 230000001747 exhibiting effect Effects 0.000 description 8

- 238000007254 oxidation reaction Methods 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- VZSRBBMJRBPUNF-UHFFFAOYSA-N 2-(2,3-dihydro-1H-inden-2-ylamino)-N-[3-oxo-3-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propyl]pyrimidine-5-carboxamide Chemical compound C1C(CC2=CC=CC=C12)NC1=NC=C(C=N1)C(=O)NCCC(N1CC2=C(CC1)NN=N2)=O VZSRBBMJRBPUNF-UHFFFAOYSA-N 0.000 description 7

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 7

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 7

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 7

- 230000000694 effects Effects 0.000 description 7

- 230000005684 electric field Effects 0.000 description 7

- 229910001195 gallium oxide Inorganic materials 0.000 description 7

- 229910052750 molybdenum Inorganic materials 0.000 description 7

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 7

- 230000001681 protective effect Effects 0.000 description 7

- 239000002096 quantum dot Substances 0.000 description 7

- 229910052709 silver Inorganic materials 0.000 description 7

- 239000004332 silver Substances 0.000 description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 6

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 6

- 238000000231 atomic layer deposition Methods 0.000 description 6

- 238000003795 desorption Methods 0.000 description 6

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 6

- 239000011733 molybdenum Substances 0.000 description 6

- 239000002159 nanocrystal Substances 0.000 description 6

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 6

- 239000001272 nitrous oxide Substances 0.000 description 6

- 230000003647 oxidation Effects 0.000 description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 6

- 229910052715 tantalum Inorganic materials 0.000 description 6

- 229910052718 tin Inorganic materials 0.000 description 6

- 229910052719 titanium Inorganic materials 0.000 description 6

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 5

- 239000012790 adhesive layer Substances 0.000 description 5

- 229910052804 chromium Inorganic materials 0.000 description 5

- 239000011651 chromium Substances 0.000 description 5

- 230000006378 damage Effects 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 5

- 229910052737 gold Inorganic materials 0.000 description 5

- 239000010931 gold Substances 0.000 description 5

- 239000002356 single layer Substances 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 4

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 4

- 238000010894 electron beam technology Methods 0.000 description 4

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- 229910052742 iron Inorganic materials 0.000 description 4

- 238000010030 laminating Methods 0.000 description 4

- 239000007788 liquid Substances 0.000 description 4

- 150000002739 metals Chemical class 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 4

- 238000000851 scanning transmission electron micrograph Methods 0.000 description 4

- 238000007789 sealing Methods 0.000 description 4

- 125000006850 spacer group Chemical group 0.000 description 4

- MUBZPKHOEPUJKR-UHFFFAOYSA-N Oxalic acid Chemical compound OC(=O)C(O)=O MUBZPKHOEPUJKR-UHFFFAOYSA-N 0.000 description 3

- 239000004983 Polymer Dispersed Liquid Crystal Substances 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 230000000903 blocking effect Effects 0.000 description 3

- 229910000420 cerium oxide Inorganic materials 0.000 description 3

- 230000009977 dual effect Effects 0.000 description 3

- 230000005685 electric field effect Effects 0.000 description 3

- 230000012447 hatching Effects 0.000 description 3

- 229910052756 noble gas Inorganic materials 0.000 description 3

- 150000002835 noble gases Chemical class 0.000 description 3

- BMMGVYCKOGBVEV-UHFFFAOYSA-N oxo(oxoceriooxy)cerium Chemical compound [Ce]=O.O=[Ce]=O BMMGVYCKOGBVEV-UHFFFAOYSA-N 0.000 description 3

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 3

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 3

- 238000006213 oxygenation reaction Methods 0.000 description 3

- 229920000642 polymer Polymers 0.000 description 3

- 238000004549 pulsed laser deposition Methods 0.000 description 3

- 239000002994 raw material Substances 0.000 description 3

- 239000003566 sealing material Substances 0.000 description 3

- 238000009751 slip forming Methods 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- 229910001936 tantalum oxide Inorganic materials 0.000 description 3

- 229910001928 zirconium oxide Inorganic materials 0.000 description 3

- YLZOPXRUQYQQID-UHFFFAOYSA-N 3-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)-1-[4-[2-[[3-(trifluoromethoxy)phenyl]methylamino]pyrimidin-5-yl]piperazin-1-yl]propan-1-one Chemical compound N1N=NC=2CN(CCC=21)CCC(=O)N1CCN(CC1)C=1C=NC(=NC=1)NCC1=CC(=CC=C1)OC(F)(F)F YLZOPXRUQYQQID-UHFFFAOYSA-N 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 230000002411 adverse Effects 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 238000003776 cleavage reaction Methods 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000018044 dehydration Effects 0.000 description 2

- 238000006297 dehydration reaction Methods 0.000 description 2

- 238000006356 dehydrogenation reaction Methods 0.000 description 2

- 230000008034 disappearance Effects 0.000 description 2

- 238000002003 electron diffraction Methods 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 229910052735 hafnium Inorganic materials 0.000 description 2

- 230000001771 impaired effect Effects 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 239000000395 magnesium oxide Substances 0.000 description 2

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 2

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 239000013081 microcrystal Substances 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- 150000002894 organic compounds Chemical class 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 238000006722 reduction reaction Methods 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- 230000007017 scission Effects 0.000 description 2

- 239000011734 sodium Substances 0.000 description 2

- 229910052708 sodium Inorganic materials 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 230000000007 visual effect Effects 0.000 description 2

- MGWGWNFMUOTEHG-UHFFFAOYSA-N 4-(3,5-dimethylphenyl)-1,3-thiazol-2-amine Chemical compound CC1=CC(C)=CC(C=2N=C(N)SC=2)=C1 MGWGWNFMUOTEHG-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical group [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 229910052684 Cerium Inorganic materials 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 239000005264 High molar mass liquid crystal Substances 0.000 description 1

- MKYBYDHXWVHEJW-UHFFFAOYSA-N N-[1-oxo-1-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propan-2-yl]-2-[[3-(trifluoromethoxy)phenyl]methylamino]pyrimidine-5-carboxamide Chemical compound O=C(C(C)NC(=O)C=1C=NC(=NC=1)NCC1=CC(=CC=C1)OC(F)(F)F)N1CC2=C(CC1)NN=N2 MKYBYDHXWVHEJW-UHFFFAOYSA-N 0.000 description 1

- NIPNSKYNPDTRPC-UHFFFAOYSA-N N-[2-oxo-2-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)ethyl]-2-[[3-(trifluoromethoxy)phenyl]methylamino]pyrimidine-5-carboxamide Chemical compound O=C(CNC(=O)C=1C=NC(=NC=1)NCC1=CC(=CC=C1)OC(F)(F)F)N1CC2=C(CC1)NN=N2 NIPNSKYNPDTRPC-UHFFFAOYSA-N 0.000 description 1

- AFCARXCZXQIEQB-UHFFFAOYSA-N N-[3-oxo-3-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propyl]-2-[[3-(trifluoromethoxy)phenyl]methylamino]pyrimidine-5-carboxamide Chemical compound O=C(CCNC(=O)C=1C=NC(=NC=1)NCC1=CC(=CC=C1)OC(F)(F)F)N1CC2=C(CC1)NN=N2 AFCARXCZXQIEQB-UHFFFAOYSA-N 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 229910008813 Sn—Si Inorganic materials 0.000 description 1

- 239000004974 Thermotropic liquid crystal Substances 0.000 description 1

- 229910010967 Ti—Sn Inorganic materials 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000003373 anti-fouling effect Effects 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000011258 core-shell material Substances 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000002050 diffraction method Methods 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 239000004815 dispersion polymer Substances 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000010494 dissociation reaction Methods 0.000 description 1

- 230000005593 dissociations Effects 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 238000001962 electrophoresis Methods 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 238000007687 exposure technique Methods 0.000 description 1

- 238000010304 firing Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- 238000004868 gas analysis Methods 0.000 description 1

- 230000004313 glare Effects 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 229910052746 lanthanum Inorganic materials 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 239000011572 manganese Substances 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 239000003094 microcapsule Substances 0.000 description 1

- 238000012806 monitoring device Methods 0.000 description 1

- 239000010955 niobium Substances 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- JCXJVPUVTGWSNB-UHFFFAOYSA-N nitrogen dioxide Inorganic materials O=[N]=O JCXJVPUVTGWSNB-UHFFFAOYSA-N 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 125000002524 organometallic group Chemical group 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 235000006408 oxalic acid Nutrition 0.000 description 1

- 125000004430 oxygen atom Chemical group O* 0.000 description 1

- 238000010422 painting Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 239000012466 permeate Substances 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000009993 protective function Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

- 238000005488 sandblasting Methods 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 150000004756 silanes Chemical class 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 238000010897 surface acoustic wave method Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- VEDJZFSRVVQBIL-UHFFFAOYSA-N trisilane Chemical compound [SiH3][SiH2][SiH3] VEDJZFSRVVQBIL-UHFFFAOYSA-N 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41733—Source or drain electrodes for field effect devices for thin film transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1218—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition or structure of the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66969—Multistep manufacturing processes of devices having semiconductor bodies not comprising group 14 or group 13/15 materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134372—Electrodes characterised by their geometrical arrangement for fringe field switching [FFS] where the common electrode is not patterned

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

- H01L2029/42388—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor characterised by the shape of the insulating material

Definitions

- One aspect of the present invention relates to a semiconductor device and a method for manufacturing the semiconductor device.

- One aspect of the present invention relates to a transistor and a method for manufacturing the transistor.

- one aspect of the present invention is not limited to the above technical fields.

- the technical fields of one aspect of the present invention disclosed in the present specification and the like include semiconductor devices, display devices, light emitting devices, power storage devices, storage devices, electronic devices, lighting devices, input devices, input / output devices, and driving methods thereof. Or those manufacturing methods can be mentioned as an example.

- Semiconductor devices refer to all devices that can function by utilizing semiconductor characteristics.

- Oxide semiconductors using metal oxides are attracting attention as semiconductor materials applicable to transistors.

- a plurality of oxide semiconductor layers are laminated, and among the plurality of oxide semiconductor layers, the oxide semiconductor layer serving as a channel contains indium and gallium, and the ratio of indium is the ratio of gallium.

- a semiconductor device having an increased electric field effect mobility (sometimes referred to simply as mobility or ⁇ FE) is disclosed.

- the metal oxide that can be used for the semiconductor layer can be formed by using a sputtering method or the like, it can be used for the semiconductor layer of a transistor constituting a large display device.

- the metal oxide that can be used for the semiconductor layer can be formed by using a sputtering method or the like, it can be used for the semiconductor layer of a transistor constituting a large display device.

- the transistor using the metal oxide has higher field effect mobility than the case using amorphous silicon, it is possible to realize a high-performance display device provided with a drive circuit.

- Patent Document 2 describes an oxide having a low resistance region containing at least one of the group consisting of aluminum, boron, gallium, indium, titanium, silicon, germanium, tin, and lead as a dopant in the source region and drain region.

- a thin film to which a semiconductor film is applied is disclosed.

- increasing the on-current of the transistor of the semiconductor device can be mentioned.

- increasing the on-current of the transistor for example, miniaturization of the transistor, specifically, reduction of the channel length of the transistor can be mentioned.

- a BGTC (Bottom Gate Top Contact) type transistor For example, a BGTC (Bottom Gate Top Contact) type transistor, a BGBC (Bottom Gate Bottom Contact) type transistor, a TGTC (Top Gate Top Contact) type transistor, and a TGBC (Top Gate) type transistor, and a TGBC (Top Gate) type transistor.

- a TGBC (Top Gate) type transistor To reduce the length, it is necessary to shorten the distance between the source electrode and the drain electrode.

- One aspect of the present invention is to provide a semiconductor device having a transistor having a high on-current and a method for manufacturing the same.

- one aspect of the present invention is to provide a semiconductor device having good electrical characteristics and a method for manufacturing the same.

- one aspect of the present invention is to provide a method for manufacturing a highly productive semiconductor device.

- one aspect of the present invention is to provide a novel semiconductor device and a method for manufacturing the same.

- One aspect of the present invention is a semiconductor device having a substrate, an island-shaped insulating layer on the substrate, and a transistor on the substrate and the insulating layer.

- the transistor has a gate electrode, a gate insulating layer, a semiconductor layer, and a pair of conductive layers.

- One of the pair of conductive layers has a region that overlaps with the insulating layer, and the other of the pair of conductive layers has a region that does not overlap with the insulating layer.

- the height of the other end face of the pair of conductive layers is lower than the height of one end face of the pair of conductive layers.

- Each of the pair of conductive layers is in contact with the semiconductor layer.

- the semiconductor layer has a region overlapping the gate electrode via the gate insulating layer.

- the conductive layer is in contact with the upper surface and the side surface of the insulating layer, and the pair of conductive layers are in contact with the upper surface of the semiconductor layer, respectively.

- the conductive layer is in contact with the upper surface and the side surface of the insulating layer, and the pair of conductive layers are in contact with the lower surface of the semiconductor layer, respectively.

- the semiconductor layer is in contact with the upper surface and the side surface of the insulating layer, and the pair of conductive layers are in contact with the upper surface of the semiconductor layer, respectively.

- one of the pair of conductive layers is in contact with the upper surface of the insulating layer and the other of the pair of conductive layers is in contact with the side surface of the insulating layer. Further, it is preferable that each of the pair of conductive layers is in contact with the lower surface of the semiconductor layer.

- the taper angle of the insulating layer is preferably 45 degrees or more and less than 90 degrees.

- the semiconductor layer has a first layer and a second layer in order from the gate insulating layer side. Further, it is preferable that the second layer has a region having higher crystallinity than the first layer.

- the semiconductor layer preferably has a first layer, a second layer, and a third layer in order from the gate insulating layer side. Further, it is preferable that the first layer has a region having higher crystallinity than the second layer, and the third layer has a region having higher crystallinity than the second layer.

- One aspect of the present invention is a step of forming an island-shaped first insulating layer and an island-shaped second insulating layer on a substrate, and a gate electrode in contact with the upper surface and side surfaces of the first insulating layer.

- a step of forming a first resist mask and a second resist mask, and a step of processing a conductive film using the first resist mask and the second resist mask as masks to form a pair of conductive layers It is a method of manufacturing a semiconductor device having.

- the pair of conductive layers are preferably provided apart on the semiconductor layer.

- a semiconductor device having a transistor having a high on-current and a method for manufacturing the same it is possible to provide a semiconductor device having good electrical characteristics and a method for manufacturing the same.

- one aspect of the present invention can provide a method for manufacturing a highly productive semiconductor device.

- a novel semiconductor device and a method for manufacturing the same can be provided.

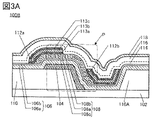

- FIG. 1A and 1B are cross-sectional views showing a configuration example of a transistor.

- 2A and 2B are cross-sectional views showing a configuration example of a transistor.

- 3A and 3B are cross-sectional views showing a configuration example of a transistor.

- 4A and 4B are cross-sectional views showing a configuration example of a transistor.

- 5A and 5B are cross-sectional views showing a configuration example of a transistor.

- 6A and 6B are cross-sectional views showing a configuration example of a transistor.

- FIG. 7 is a cross-sectional view showing a configuration example of a semiconductor device.

- FIG. 8 is a cross-sectional view showing a configuration example of the transistor.

- FIG. 9 is a cross-sectional view showing a configuration example of a semiconductor device.

- FIG. 10 is a cross-sectional view showing a configuration example of a semiconductor device.

- 11A, 11B and 11C are cross-sectional views illustrating a method for manufacturing a semiconductor device.

- 12A and 12B are cross-sectional views illustrating a method for manufacturing a semiconductor device.

- 13A and 13B are cross-sectional views illustrating a method for manufacturing a semiconductor device.

- FIG. 14 is a cross-sectional view illustrating a method for manufacturing a semiconductor device.

- FIG. 15 is a cross-sectional view illustrating a method for manufacturing a semiconductor device.

- FIG. 16 is a cross-sectional view illustrating a method for manufacturing a semiconductor device.

- FIG. 17 is a cross-sectional view illustrating a method for manufacturing a semiconductor device.

- FIG. 18 is a cross-sectional view illustrating a method for manufacturing a semiconductor device.

- 19A and 19B are cross-sectional views illustrating a method for manufacturing a semiconductor device.

- 20A, 20B and 20C are top views of the display device.

- FIG. 21 is a cross-sectional view of the display device.

- FIG. 22 is a cross-sectional view of the display device.

- FIG. 23 is a cross-sectional view of the display device.

- FIG. 24 is a cross-sectional view of the display device.

- FIG. 25 is a cross-sectional view of the display device.

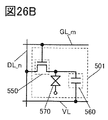

- FIG. 26A is a block diagram of the display device.

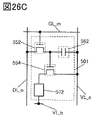

- 26B and 26C are circuit diagrams of the display device.

- 27A, 27C and 27D are circuit diagrams of the display device.

- 27B is a timing chart of the display device.

- 28A and 28B are configuration examples of the display module.

- 29A and 29B are configuration examples of electronic devices.

- 30A, 30B, 30C and 30D are configuration examples of electronic devices.

- 31A and 31B are STEM images according to the embodiment.

- 32A and 32B are STEM images according to the embodiment.

- 33A and 33B are STEM images according to the embodiment.

- source and drain functions of a transistor may be interchanged when transistors having different polarities are used or when the direction of current changes in circuit operation. Therefore, the terms source and drain can be used interchangeably.

- “electrically connected” includes the case of being connected via "something having some kind of electrical action”.

- the “thing having some kind of electrical action” is not particularly limited as long as it enables the exchange of electric signals between the connection targets.

- “things having some kind of electrical action” include electrodes and wirings, switching elements such as transistors, resistance elements, inductors, capacitors, and other elements having various functions.

- membrane and the term “layer” can be interchanged with each other.

- conductive layer may be interchangeable with the term “conductive layer”.

- insulating layer may be interchangeable with the term “insulating film”.

- the off current means a drain current when the transistor is in an off state (also referred to as a non-conducting state or a cutoff state).

- the off state is a state in which the voltage V gs between the gate and the source is lower than the threshold voltage V th in the n-channel transistor (higher than V th in the p-channel transistor) unless otherwise specified. To say.

- the display panel which is one aspect of the display device, has a function of displaying (outputting) an image or the like on the display surface. Therefore, the display panel is an aspect of the output device.

- an IC is mounted on a display panel board, for example, a connector such as FPC (Flexible Printed Circuit) or TCP (Tape Carrier Package) is attached, or an IC is mounted on the board by a COG (Chip On Glass) method or the like. It may be referred to as a display panel module, a display module, or simply a display panel.

- a connector such as FPC (Flexible Printed Circuit) or TCP (Tape Carrier Package) is attached, or an IC is mounted on the board by a COG (Chip On Glass) method or the like.

- COG Chip On Glass

- the touch panel which is one aspect of the display device, has a function of displaying an image or the like on the display surface, and the display surface is touched, pressed, or approached by a detected object such as a finger or a stylus. It has a function as a touch sensor for detection. Therefore, the touch panel is one aspect of the input / output device.

- the touch panel can also be referred to as, for example, a display panel with a touch sensor (or a display device) or a display panel with a touch sensor function (or a display device).

- the touch panel may be configured to have a display panel and a touch sensor panel. Alternatively, it may be configured to have a function as a touch sensor inside or on the surface of the display panel.

- a touch panel board on which a connector or an IC is mounted may be referred to as a touch panel module, a display module, or simply a touch panel.

- One aspect of the present invention is a semiconductor device having a substrate, an island-shaped first insulating layer on the substrate, and a transistor on the substrate and the first insulating layer.

- the transistor has a gate electrode, a gate insulating layer, a semiconductor layer, and a pair of conductive layers.

- One of the pair of conductive layers functions as one of the source electrode or the drain electrode, and the other of the pair of conductive layers functions as the other of the source electrode or the drain electrode.

- One of the pair of conductive layers is provided on the first insulating layer and has a region overlapping with the first insulating layer.

- the other of the pair of conductive layers has a region that does not overlap with the first insulating layer.

- the height of the other end face of the pair of conductive layers is lower than the height of one end face of the pair of conductive layers.

- an island-shaped first insulating layer and an island-shaped second insulating layer are provided on a substrate, and a transistor is provided on the substrate and the first insulating layer.

- a transistor is provided on the substrate and the first insulating layer.

- the pair of conductive layers possessed by the transistor forms a resist on the conductive film to be the pair of conductive layers, and the resist is exposed and developed using a photomask having a light-shielding portion to form a resist mask.

- a photomask having a light-shielding portion to form a resist mask.

- the thickness of the resist is thin on the first insulating layer and thicker between the first insulating layer and the second insulating layer.

- a first unexposed region that is shielded by the light-shielding portion of the photomask is formed on the first insulating layer.

- a second insulating layer is provided between the first insulating layer and the second insulating layer. Form an unexposed area.

- a first resist mask and a second resist mask can be formed in the first unexposed region and the second unexposed region, respectively.

- a pair of conductive layers can be formed by processing a conductive film using the first resist mask and the second resist mask as masks.

- one of the pair of conductive layers and the pair of conductive layers are formed.

- the distance between the layer and the other can be made smaller than the exposure limit of the exposure apparatus.

- the transistor 100 has a conductive layer 104, an insulating layer 106, a semiconductor layer 108, a conductive layer 112a, and a conductive layer 112b.

- the conductive layer 104 functions as a gate electrode.

- a part of the insulating layer 106 functions as a gate insulating layer.

- the conductive layer 112a functions as one of the source electrode and the drain electrode, and the conductive layer 112b functions as the other.

- the region of the semiconductor layer 108 that overlaps with the conductive layer 104 functions as a channel forming region.

- the transistor 100 is a so-called bottom gate type transistor having a gate electrode below the semiconductor layer 108. Further, since the source electrode and the drain electrode are provided above the semiconductor layer 108, it can be said to be a BGTC type transistor. Here, the surface of the semiconductor layer 108 opposite to the conductive layer 104 side may be referred to as a back channel side surface.

- the transistor 100 is a transistor having a so-called channel etch structure, which does not have a protective layer between the back channel side of the semiconductor layer 108 and the source electrode and the drain electrode.

- the transistor 100 is provided on the insulating layer 110.

- the insulating layer 110 has an island-like shape and is provided on the substrate 102.

- the conductive layer 104 is provided on the insulating layer 110 and is in contact with the upper surface and the side surface of the insulating layer 110.

- the conductive layer 104 has a curved shape along the shape of the upper surface and the side surface of the insulating layer 110. Further, the conductive layer 104 may be further in contact with the substrate 102. One end of the conductive layer 104 may be in contact with the insulating layer 110, and the other end may be in contact with the substrate 102.

- the step between the end portion of the conductive layer 104 and the substrate 102 becomes small. Therefore, the step covering property of the layer (for example, the insulating layer 106) formed on the conductive layer 104 is improved, and it is possible to suppress the occurrence of problems such as step breakage or voids in the layer.

- the insulating layer 106 is provided on the insulating layer 110, the conductive layer 104, and the substrate 102, and is in contact with the upper surface of the insulating layer 110, the upper surface and side surfaces of the conductive layer 104, and the substrate 102.

- the insulating layer 106 may be provided on the island-shaped insulating layer 110A adjacent to the insulating layer 110 and may be in contact with the upper surface and the side surface of the insulating layer 110A.

- the semiconductor layer 108 has an island-like shape and is in contact with the upper surface of the insulating layer 106.

- the semiconductor layer 108 has a region that overlaps with the conductive layer 104 via the insulating layer 106.

- the conductive layer 112a and the conductive layer 112b are each provided on the semiconductor layer 108 and are in contact with the upper surface of the semiconductor layer 108. Further, the conductive layer 112a and the conductive layer 112b may be in contact with the side surface of the semiconductor layer 108 and the upper surface of the insulating layer 106, respectively.

- the conductive layer 112a has a region overlapping with the insulating layer 110 and is provided on the insulating layer 110.

- the conductive layer 112b is provided in the groove 111 between the insulating layer 110 and the island-shaped insulating layer 110A adjacent to the insulating layer 110.

- the conductive layer 112b has a region that does not overlap with the insulating layer 110.

- the conductive layer 112b has a U-shaped shape in a cross-sectional view. Therefore, the height of the side surface of the conductive layer 112b may be higher than the height of the upper surface of the conductive layer 112b.

- the height of the upper surface of the conductive layer 112b located in the groove 111 is lower than the height of the upper surface of the conductive layer 112a located on the insulating layer 110.

- the height of the side surface of the conductive layer 112b is lower than the height of the side surface of the conductive layer 112a.

- the height of the end face of the conductive layer 112b is lower than the height of the end face of the conductive layer 112a.

- the end surface of the layer includes the upper surface and the side surface when the surface in contact with the surface to be formed of the layer is the lower surface.

- the height from the substrate to the highest portion of the upper surface of the layer is used.

- the height from the substrate to the highest part of the sides of the layer is used.

- the height from the substrate to the highest portion of the end faces (top and side surfaces) of the layer is used.

- FIG. 1A shows an example in which the height of one end of the conductive layer 112b and the height of the other end are the same or substantially the same, but one aspect of the present invention is not limited to this.

- the height of one end of the conductive layer 112b and the height of the other end may be different.

- the same material for the conductive layer 112a and the conductive layer 112b it is preferable to use the same material for the conductive layer 112a and the conductive layer 112b.

- the resistivity of the conductive layer 112a and the conductive layer 112b can be the same or substantially the same.

- the end of the insulating layer 110 is preferably tapered.

- the taper angle ⁇ at the end of the insulating layer 110 is preferably less than 90 degrees.

- the taper angle ⁇ at the end of the insulating layer 110 is preferably 45 degrees or more and less than 90 degrees, more preferably 50 degrees or more and 85 degrees or less, further preferably 55 degrees or more and 85 degrees or less, and further preferably 60 degrees or more and 85 degrees.

- the following is preferable, more preferably 60 degrees or more and 80 degrees or less, further preferably 65 degrees or more and 80 degrees or less, and further preferably 70 degrees or more and 80 degrees or less.

- the step covering property of the layer (for example, the conductive layer 104) formed on the insulating layer 110 is improved, and the layer has problems such as step breakage or voids. It can be suppressed from occurring.

- the distance between the conductive layer 112a and the conductive layer 112b can be made smaller than the exposure limit of the exposure apparatus.

- the end portion of the insulating layer 110A has a tapered shape.

- the taper angle of the insulating layer 110A the description of the insulating layer 110 can be referred to, and detailed description thereof will be omitted.

- the taper angle ⁇ of the insulating layer 110 and the taper angle of the insulating layer 110A may be the same or different.

- the taper angle refers to the angle formed by the end surface of the layer and the formed surface of the layer.

- FIG. 1A shows an example in which the insulating layer 110 and the insulating layer 110A have the same thickness.

- the insulating layer 110 and the insulating layer 110A can be formed in the same process.

- the insulating layer 110 and the insulating layer 110A may be formed in different steps. Further, the thicknesses of the insulating layer 110 and the insulating layer 110A may be different.

- FIG. 1A shows an example in which the insulating layer 110 and the insulating layer 110A are provided in contact with the substrate 102, but one aspect of the present invention is not limited to this.

- Another insulating layer may be provided on the substrate 102, and the insulating layer 110 and the insulating layer 110A may be provided on the insulating layer.

- the insulating layer may be provided between the conductive layer 104 and the substrate 102, and between the insulating layer 106 and the substrate 102.

- Another insulating layer may be provided on the substrate 102, the insulating layer 110, and the insulating layer 110A, and the conductive layer 104 may be provided on the insulating layer.

- the insulating layer may be provided between the insulating layer 106 and the substrate 102, between the insulating layer 106 and the insulating layer 110, and between the insulating layer 106 and the insulating layer 110A.

- FIG. 1B An enlarged view of the region P surrounded by the alternate long and short dash line in FIG. 1A is shown in FIG. 1B.

- the channel length L100 can be the length of the semiconductor layer 108 between the conductive layer 112a and the conductive layer 112b. Further, the channel length L100 can be said to be the length of the semiconductor layer 108 in the region between the conductive layer 112a and the conductive layer 112b, which is in contact with neither the conductive layer 112a nor the conductive layer 112b.

- the semiconductor layer 108 has a curved region between the conductive layer 112a and the conductive layer 112b. It can be said that the transistor 100 has a channel forming region having a curved shape. Further, the interval SP100 and the channel length L100 are different values, and the channel length L100 is a value larger than the interval SP100.

- the channel length L100 can be set to a value smaller than the exposure limit of the exposure apparatus.

- the channel length L100 is preferably 0.2 ⁇ m or more and less than 1.5 ⁇ m, more preferably 0.3 ⁇ m or more and 1.3 ⁇ m or less, further preferably 0.4 ⁇ m or less and 1.2 ⁇ m, and further preferably 0.5 ⁇ m or less 1. .1 ⁇ m is preferable, and more preferably 0.6 ⁇ m or less and 1.0 ⁇ m.

- the transistor 100 can have a channel length L100 smaller than the exposure limit of the exposure apparatus by providing the conductive layer 112a on the insulating layer 110 and providing the conductive layer 112b in the groove 111. For example, when the exposure limit of the exposure apparatus is 1.5 ⁇ m, the channel length L100 can be set to less than 1.5 ⁇ m.

- the on-current of the transistor 100 can be increased.

- the transistor 100 it is possible to manufacture a circuit capable of high-speed operation.

- An insulating layer 114, an insulating layer 116, and an insulating layer 118 are provided so as to cover the conductive layer 112a, the conductive layer 112b, and the semiconductor layer 108.

- the insulating layer 114, the insulating layer 116, and the insulating layer 118 each function as a protective layer for the transistor 100.