WO2018230312A1 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- WO2018230312A1 WO2018230312A1 PCT/JP2018/020231 JP2018020231W WO2018230312A1 WO 2018230312 A1 WO2018230312 A1 WO 2018230312A1 JP 2018020231 W JP2018020231 W JP 2018020231W WO 2018230312 A1 WO2018230312 A1 WO 2018230312A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- layer

- collector

- drift

- region

- semiconductor substrate

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 88

- 239000000758 substrate Substances 0.000 claims abstract description 49

- 238000011084 recovery Methods 0.000 claims abstract description 23

- 239000010410 layer Substances 0.000 claims description 269

- 239000012535 impurity Substances 0.000 claims description 12

- 238000002347 injection Methods 0.000 claims description 9

- 239000007924 injection Substances 0.000 claims description 9

- 239000002344 surface layer Substances 0.000 claims description 6

- 230000007423 decrease Effects 0.000 abstract description 4

- 239000000969 carrier Substances 0.000 description 4

- 239000011229 interlayer Substances 0.000 description 4

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 238000004088 simulation Methods 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- MXSJNBRAMXILSE-UHFFFAOYSA-N [Si].[P].[B] Chemical compound [Si].[P].[B] MXSJNBRAMXILSE-UHFFFAOYSA-N 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

Definitions

- the present disclosure relates to a semiconductor device in which an insulated gate bipolar transistor (hereinafter referred to as an IGBT) element having an insulated gate structure and a free wheel diode (hereinafter referred to as an FWD) element are formed on a common semiconductor substrate.

- IGBT insulated gate bipolar transistor

- FWD free wheel diode

- a base layer is formed in a surface layer portion of a semiconductor substrate constituting an N ⁇ type drift layer, and a plurality of trenches are formed so as to penetrate the base layer.

- a gate insulating film and a gate electrode are sequentially formed.

- an N + -type emitter region is formed on the surface layer portion of the base layer so as to be in contact with the trench.

- a P + -type collector layer and an N + -type cathode layer are formed on the other side of the semiconductor substrate.

- An N-type field stop layer (hereinafter referred to as an FS layer) having a higher impurity concentration than the drift layer is formed on the collector layer and the cathode layer.

- the FS layer is formed in contact with the collector layer and the cathode layer.

- An upper electrode electrically connected to the base layer and the emitter region is formed on one side of the semiconductor substrate.

- a lower electrode electrically connected to the collector layer and the cathode layer is formed on the other surface side of the semiconductor substrate.

- the region where the collector layer is formed on the other side of the semiconductor substrate is the IGBT region having the IGBT element, and the region where the cathode layer is formed is the FWD region having the FWD element.

- the FWD element having a PN junction is configured by the N-type cathode layer, the FS layer, the drift layer, and the P-type base layer because of the above configuration.

- the IGBT element when a lower voltage than the lower electrode is applied to the upper electrode and a predetermined voltage is applied to the gate electrode, the IGBT element has an N-type inversion layer (that is, a portion in contact with the trench in the base layer). Channel). In the IGBT element, electrons are supplied from the emitter region to the drift layer via the inversion layer, and holes are supplied from the collector layer to the drift layer. It becomes.

- the FWD element when a higher voltage is applied to the upper electrode than the lower electrode, the FWD element is turned on by supplying holes from the base layer to the drift layer and electrons from the cathode layer to the drift layer. Thereafter, when a voltage higher than that of the upper electrode is applied to the lower electrode of the FWD element, holes accumulated in the FWD element are attracted to the upper electrode and electrons are attracted to the lower electrode, thereby generating a recovery current. The recovery state is entered, and the off state is entered after the recovery state has elapsed.

- the depletion layer formed between the drift layer and the base layer extends to the lower electrode side (that is, the other surface side of the semiconductor substrate).

- the surge peak voltage in the recovery state (hereinafter, also simply referred to as surge peak voltage) tends to increase.

- surge peak voltage tends to increase.

- the semiconductor device may be destroyed due to the surge peak voltage becoming large.

- This disclosure is intended to provide a semiconductor device capable of reducing the surge peak voltage in the recovery state.

- the IGBT region (1) having the IGBT element (1a) and the FWD region (2) having the FWD element (2a) are formed on a common semiconductor substrate (10).

- the semiconductor device includes a first conductivity type drift layer (11), a second conductivity type base layer (12) formed on the drift layer, and a surface layer portion of the base layer, and drifts with the base layer interposed therebetween.

- the first conductivity type emitter region (16) formed at a position away from the layer and having a higher impurity concentration than the drift layer, and the side opposite to the base layer across the drift layer and formed in the IGBT region A second conductivity type collector layer (20), and a first conductivity type cathode layer (21) formed in the FWD region on the opposite side of the base layer across the drift layer and adjacent to the collector layer;

- Base layer and collector layer A semiconductor substrate having an FS layer (22) formed between the emitter layer and the cathode layer, and a gate insulating film (14) disposed on a surface of the base layer located between the emitter region and the drift layer, A gate electrode (15) disposed on the gate insulating film, a first electrode (18) electrically connected to the base layer and the emitter region, and a second electrode electrically connected to the collector layer and the cathode layer (23), and the FS layer is formed away from the collector layer and the cathode layer.

- the second carrier capable of reducing the surge peak voltage is injected. For this reason, it can suppress that a semiconductor device is destroyed.

- FIG. 1 is a schematic plan view of a semiconductor device according to a first embodiment.

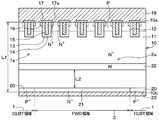

- FIG. 2 is a cross-sectional view taken along line II-II in FIG. It is a schematic diagram which shows the state of the electron which flows into the collector layer in a recovery state, and the hole inject

- a first embodiment will be described with reference to the drawings. Note that the semiconductor device of this embodiment is preferably used as a power switching element used in a power supply circuit such as an inverter or a DC / DC converter.

- the semiconductor device is an RC (ie, Reverse Conducting) -IGBT in which an IGBT region 1 having an IGBT element 1a and an FWD region 2 having an FWD element 2a are formed on a common semiconductor substrate 10. It is said that.

- the IGBT regions 1 and the FWD regions 2 extend along one direction and are alternately formed in a direction crossing the extending direction.

- the IGBT region 1 and the FWD region 2 extend along the horizontal direction of the paper surface and are alternately formed in the vertical direction of the paper surface.

- the semiconductor substrate 10 has an N ⁇ type drift layer 11.

- the semiconductor substrate 10 is comprised with a silicon substrate, for example.

- a P-type base layer 12 is formed on the drift layer 11 (that is, on the one surface 10a side of the semiconductor substrate 10).

- a plurality of trenches 13 are formed in the semiconductor substrate 10 so as to penetrate the base layer 12 and reach the drift layer 11. Thereby, the base layer 12 is separated into a plurality by the trench 13.

- the plurality of trenches 13 are formed in the IGBT region 1 and the FWD region 2, respectively, and are formed in stripes formed at equal intervals along one direction of the surface direction of the one surface 10a of the semiconductor substrate 10. ing. In FIG. 2, each trench 13 is formed along the direction perpendicular to the paper surface.

- Each trench 13 is embedded with a gate insulating film 14 formed so as to cover the wall surface of each trench 13 and a gate electrode 15 made of polysilicon or the like formed on the gate insulating film 14. . Thereby, a trench gate structure is configured.

- An N + -type emitter region 16 having a higher impurity concentration than that of the drift layer 11 is formed in the surface layer portion of the base layer 12 (that is, the one surface 10 a side of the semiconductor substrate 10). Specifically, the emitter region 16 is formed so as to terminate in the base layer 12 and to be in contact with the side surface of the trench 13. More specifically, the emitter region 16 extends in a rod shape so as to be in contact with the side surface of the trench 13 along the longitudinal direction of the trench 13 in the region between the trenches 13 and terminates inside the tip of the trench 13.

- the portion of the wall surface of the trench 13 located between the emitter region 16 and the drift layer 11 corresponds to the surface of the base layer located between the emitter region and the drift layer.

- An interlayer insulating film 17 made of BPSG (ie, Boron Phosphorus Silicon Glass) or the like is formed on one surface 10a of the semiconductor substrate 10.

- An upper electrode 18 electrically connected to the emitter region 16 and the base layer 12 is formed on the interlayer insulating film 17 through a contact hole 17 a formed in the interlayer insulating film 17. That is, an upper electrode 18 that functions as an emitter electrode in the IGBT region 1 and functions as an anode electrode in the FWD region 2 is formed on the interlayer insulating film 17.

- the upper electrode 18 corresponds to the first electrode.

- a plurality of pad portions 19 connected to the gate electrode 15, a temperature sensor (not shown), and the like are formed on one surface 10 a of the semiconductor substrate 10.

- a P + -type collector layer 20 is formed on the drift layer 11 on the side opposite to the base layer 12 side (that is, the other surface 10 b side) of the drift layer 11.

- an N + -type cathode layer 21 is formed on the side of the drift layer 11 opposite to the base layer 12 side (that is, the other surface 10 b side of the semiconductor substrate 10). That is, the IGBT region 1 and the FWD region 2 are partitioned depending on whether the layer formed on the other surface 10 b side of the semiconductor substrate 10 is the collector layer 20 or the cathode layer 21.

- the portion on the collector layer 20 is the IGBT region 1 and the portion on the cathode layer 21 is the FWD region 2.

- the collector layer 20 and the cathode layer 21 are formed to the same depth from the other surface 10b of the semiconductor substrate 10 toward the one surface 10a.

- an N-type FS layer 22 having a higher impurity concentration than the drift layer 11 is formed on the drift layer 11 on the side opposite to the base layer 12 side (that is, the other surface 10b side of the semiconductor substrate 10).

- the FS layer 22 is formed at a position away from the collector layer 20 and the cathode layer 21.

- the FS layer 22 is formed in the drift layer 11. That is, the FS layer 22 is formed so that a part of the drift layer 11 remains between the collector layer 20 and the cathode layer 21.

- the FS layer 22 is formed such that the ratio of the distance L2 between the FS layer 22, the collector layer 20, and the cathode layer 21 to the thickness L1 of the semiconductor substrate 10 is a predetermined value. Yes.

- a lower electrode 23 electrically connected to the collector layer 20 and the cathode layer 21 is formed on the opposite side of the drift layer 11 (that is, the other surface 10b of the semiconductor substrate 10) with the collector layer 20 and the cathode layer 21 interposed therebetween. ing. That is, the lower electrode 23 that functions as a collector electrode in the IGBT region 1 and functions as a cathode electrode in the FWD region 2 is formed. In the present embodiment, the lower electrode 23 corresponds to the second electrode.

- the FWD region 2 includes the FWD element 2a that is PN-junctioned with the base layer 12 as an anode and the drift layer 11, the FS layer 22, and the cathode layer 21 as a cathode. ing.

- the N type, N + type, and N ⁇ type correspond to the first conductivity type

- the P type and P + type correspond to the second conductivity type

- the semiconductor substrate 10 includes the collector layer 20, the cathode layer 21, the drift layer 11, the FS layer 22, the base layer 12, and the emitter region 16 as described above. Next, the operation of the semiconductor device will be described.

- the semiconductor device when a voltage higher than that of the upper electrode 18 is applied to the lower electrode 23, the PN junction formed between the base layer 12 and the drift layer 11 is in a reverse conducting state, and a depletion layer is formed. The At this time, no current flows between the upper electrode 18 and the lower electrode 23 when a low level (for example, 0 V) voltage lower than the threshold voltage Vth of the insulated gate structure is applied to the gate electrode 15.

- a low level for example, 0 V

- a high level voltage equal to or higher than the threshold voltage Vth of the insulated gate structure is applied to the gate electrode 15 while a voltage higher than that of the upper electrode 18 is applied to the lower electrode 23.

- an inversion layer is formed in a portion of the base layer 12 that is in contact with the trench 13.

- electrons are supplied from the emitter region 16 to the drift layer 11 through the inversion layer, whereby holes are supplied from the collector layer 20 to the drift layer 11, and the resistance of the drift layer 11 is controlled by conductivity modulation. When the value decreases, it is turned on.

- the IGBT element 1a is turned off and the FWD element 2a is turned on (that is, the FWD element 2a is diode-operated)

- the voltage applied to the upper electrode 18 and the lower electrode 23 is switched, and the upper electrode A voltage higher than that of the lower electrode 23 is applied to 18.

- a low level voltage for example, 0 V

- the threshold voltage Vth of the insulated gate structure is applied to the gate electrode 15.

- the inversion layer is not formed in the portion of the base layer 12 in contact with the trench 13, holes are supplied from the upper electrode 18 through the base layer 12, and from the lower electrode 23 through the cathode layer 21. Electrons are supplied, and the FWD element 2a operates as a diode.

- a reverse voltage is applied to the lower electrode 23 to apply a voltage higher than that of the upper electrode 18. That is, when the current is cut off from a state in which a forward current flows through the FWD element 2a, reverse voltage application is performed to apply a voltage higher than that of the upper electrode 18 to the lower electrode 23. As a result, the FWD element 2a enters a recovery state. Then, holes in the base layer 12 are attracted to the upper electrode 18 side, and electrons in the drift layer 11 are attracted to the lower electrode 23 side, so that a recovery current is generated, and the gap between the base layer 12 and the drift layer 11 is generated. The depletion layer grows.

- the FS layer 22 is formed away from the collector layer 20 and the cathode layer 21. Therefore, in the semiconductor device of this embodiment, the internal resistance of the region located on and near the collector layer 20 is higher than that of the conventional semiconductor device in which the FS layer 22 is in contact with the collector layer 20 and the cathode layer 21. growing. For this reason, in the semiconductor device of this embodiment, the voltage drop when electrons flow into the collector layer 20 is larger than that in the conventional semiconductor device. That is, in the semiconductor device of this embodiment, the potential of the region on the collector layer 20 and in the vicinity thereof is likely to be lower than that of the conventional semiconductor device.

- the semiconductor device of this embodiment in the recovery state, electrons easily flow into the collector layer 20, and accordingly, the amount of holes injected into the drift layer 11 via the collector layer 20 increases. Then, since holes injected from the collector layer 20 spread along the surface direction of the semiconductor substrate 10, the holes are also supplied to the region on the cathode layer 21. For this reason, in the semiconductor device of this embodiment, in the recovery state, carriers are not easily depleted in the FWD region 2, and the depletion layer is difficult to extend to the other surface 10 b side of the semiconductor substrate 10. That is, in the semiconductor device of this embodiment, in the recovery state, the space charge density of the FWD region 2 is increased, and the depletion layer is difficult to extend to the other surface 10 b side of the semiconductor substrate 10. Thereby, in the semiconductor device of this embodiment, complete depletion can be suppressed and the surge peak voltage can be reduced in the recovery state.

- electrons correspond to first carriers and holes correspond to second carriers.

- the FS layer 22 of the present embodiment is formed at a position where an appropriate amount of holes with a reduced surge peak voltage is injected in the recovery state.

- the inventors further examined the magnitude of the surge peak voltage and the ratio of the distance L2 between the FS layer 22, the collector layer 20, and the cathode layer 21 with respect to the thickness L1 of the semiconductor substrate 10, and FIG. The results shown are obtained.

- the thickness L1 of the semiconductor substrate 10 is the length between the one surface 10a and the other surface 10b of the semiconductor substrate 10.

- the distance L2 between the FS layer 22, the collector layer 20, and the cathode layer 21 is the length along the thickness direction of the semiconductor substrate 10 between the FS layer 22, the collector layer 20, and the cathode layer 21.

- the distance L ⁇ b> 2 between the FS layer 22, the collector layer 20, and the cathode layer 21 is simply indicated as the distance between the FS layers 22.

- the ratio [%] of the distance L2 between the FS layer 22, the collector layer 20, and the cathode layer 21 with respect to the thickness L1 of the semiconductor substrate 10 is simply referred to as L2 / L1.

- the surge peak voltage decreases as L2 / L1 is gradually increased from 0.

- the case where L2 / L1 is 0 is a case where the FS layer 22 is in contact with the collector layer 20 and the cathode layer 21.

- the surge peak voltage is almost equal when L2 / L1 is 2 to 17%. Further, the surge peak voltage is sharply reduced when L2 / L1 is further increased from 17%, and is minimized when L2 / L1 is about 19%. The surge peak voltage sharply decreases when L2 / L1 is between 17% and 19% because the number of holes injected into the drift layer 11 increases, so that the constant voltage is reached when the surge peak voltage is reached. This is because the sustain voltage up to the time point increases.

- the surge peak voltage gradually increases when L2 / L1 is greater than 19%, and becomes the same magnitude as when L1 / L2 is 0 when L2 / L1 is 21.5%. .

- the surge peak voltage further increases when L2 / L1 is made larger than 21.5%.

- the reason why the surge peak voltage is further increased when L2 / L1 is made larger than 21.5% is that holes are excessively injected when L2 / L1 becomes too large, and the sustain voltage becomes too large. That is, if the distance L2 between the FS layer 22, the collector layer 20 and the cathode layer 21 becomes too large, the surge peak voltage will increase.

- the FS layer 22 is formed at a position where L2 / L1 is less than 21.5% so that an appropriate amount of holes with a small surge peak voltage is injected. More specifically, the FS layer 22 is preferably formed so that L2 / L1 is 2 to 19% so that the surge peak voltage is stably reduced.

- the thickness of the semiconductor substrate 10 is 80 ⁇ m

- the impurity concentration of the drift layer 11 is 1.0 ⁇ 10 14 cm ⁇ 3

- the impurity concentration of the FS layer 22 is 1.0 ⁇ 10 16 cm ⁇ 3

- the base This is a simulation result when the impurity concentration of the layer 12 is 2.5 ⁇ 10 17 cm ⁇ 3 and the impurity concentration of the cathode layer 21 is 5.0 ⁇ 10 19 cm ⁇ 3 .

- the semiconductor device of this embodiment can reduce the surge peak voltage regardless of the impurity concentration or the like by forming the FS layer 22 so that L2 / L1 is less than 21.5%.

- the FS layer 22 is formed at a position away from the collector layer 20 and the cathode layer 21.

- an appropriate amount of holes is injected from the collector layer 20 into the drift layer 11 so that the surge peak voltage can be reduced. That is, L1 / L2 is set to be less than 21.5%. For this reason, a surge peak voltage can be made small and it can suppress that a semiconductor device is destroyed.

- a plurality of P + type carrier injection layers 24 are formed in the cathode layer 21.

- the plurality of carrier injection layers 24 are formed in a stripe shape along the extending direction of the cathode layer 21.

- the holes in the drift layer 11 flow into the carrier injection layer 24 located in the cathode layer 21 together with the collector layer 20. Then, holes are also injected into the drift layer 11 via the carrier injection layer 24. For this reason, in the recovery state, the carriers are more difficult to be depleted in the FWD region 2, and the surge peak voltage can be reduced.

- the FS layer 22 is formed at a position where the distance L2 between the collector layer 20 and the cathode layer 21 is adjusted so that an appropriate amount of holes for reducing the surge peak voltage is injected.

- the first conductivity type is N type and the second conductivity type is P type has been described.

- the first conductivity type is P type

- the second conductivity type is N type.

- a P + -type contact region having a higher impurity concentration than that of the base layer 12 is formed on the surface layer portion of the base layer 12 (that is, on the one surface 10a side of the semiconductor substrate 10). Also good.

- a plurality of FS layers 22 may be formed in the thickness direction of the semiconductor substrate 10.

- two FS layers 22 may be formed along the thickness direction of the semiconductor substrate 10.

- the distance L2 between the FS layer 22 located closest to the other surface 10b of the semiconductor substrate 10 and the collector layer 20 and the cathode layer 21 is such that an appropriate amount of holes that reduce the surge peak voltage is injected. It may be adjusted so as to be the same as in the first embodiment.

- a trench gate type semiconductor device not a trench gate type semiconductor device but a planar type semiconductor device in which the gate electrode 15 is disposed on the one surface 10a of the semiconductor substrate 10 may be used.

- the gate electrode 15 since the gate electrode 15 is disposed on the one surface 10a of the semiconductor substrate 10 via the gate insulating film 14, a portion of the base layer 12 constituting the one surface 10a of the semiconductor substrate 10 is on the surface of the base layer. Equivalent to.

- the plurality of carrier injection layers 24 may be formed in a lattice shape, for example, instead of a stripe shape. Moreover, the carrier injection layer 24 may be formed only one instead of plural.

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

IGBT領域(1)およびFWD領域(2)が共通の半導体基板(10)に形成されている半導体装置において、フィールドストップ層(22)をコレクタ層(20)およびカソード層(21)から離れて形成する。そして、FWD素子(2a)に順方向電流が流れている状態から当該電流を遮断してリカバリ状態となった際、FWD素子(2a)内の第1キャリアの一部がコレクタ層(20)へと流れることにより、サージピーク電圧を小さくする量の第2キャリアが第2電極(23)からコレクタ層(20)を介してドリフト層(11)に注入されるようにする。

Description

本出願は、2017年6月14日に出願された日本特許出願番号2017-117072号に基づくもので、ここにその記載内容が参照により組み入れられる。

本開示は、絶縁ゲート構造を有する絶縁ゲートバイポーラトランジスタ(以下では、IGBTという)素子とフリーホイールダイオード(以下では、FWDという)素子とが共通の半導体基板に形成された半導体装置に関する。

従来より、例えば、インバータ等に使用されるスイッチング素子として、IGBT素子を有するIGBT領域と、FWD素子を有するFWD領域とが共通の半導体基板に形成された半導体装置が提案されている(例えば、特許文献1参照)。

具体的には、この半導体装置では、N-型のドリフト層を構成する半導体基板の表層部にベース層が形成され、ベース層を貫通するように複数のトレンチが形成されている。そして、各トレンチには、ゲート絶縁膜およびゲート電極が順に形成されている。また、ベース層の表層部には、トレンチに接するようにN+型のエミッタ領域が形成されている。半導体基板の他面側には、P+型のコレクタ層およびN+型のカソード層が形成されている。そして、コレクタ層およびカソード層上には、ドリフト層よりも高不純物濃度とされたN型のフィールドストップ層(以下では、FS層という)が形成されている。詳しくは、FS層は、コレクタ層およびカソード層と接するように形成されている。

半導体基板の一面側にはベース層およびエミッタ領域と電気的に接続される上部電極が形成されている。半導体基板の他面側にはコレクタ層およびカソード層と電気的に接続される下部電極が形成されている。

このような半導体装置では、半導体基板の他面側にコレクタ層が形成されている領域がIGBT素子を有するIGBT領域とされ、カソード層が形成されている領域がFWD素子を有するFWD領域とされている。なお、FWD領域では、上記構成とされていることにより、N型のカソード層、FS層、およびドリフト層と、P型のベース層とによってPN接合を有するFWD素子が構成される。

上記半導体装置では、IGBT素子は、上部電極に下部電極より低い電圧が印加されると共にゲート電極に所定電圧が印加されると、ベース層のうちのトレンチと接する部分にN型の反転層(すなわち、チャネル)が形成される。そして、IGBT素子は、エミッタ領域から反転層を介して電子がドリフト層に供給されると共にコレクタ層から正孔がドリフト層に供給され、伝導度変調によりドリフト層の抵抗値が低下してオン状態となる。

また、FWD素子は、上部電極に下部電極より高い電圧が印加されると、ベース層から正孔がドリフト層に供給されると共にカソード層から電子がドリフト層に供給されてオン状態となる。その後、FWD素子は、下部電極に上部電極より高い電圧が印加されると、FWD素子内に蓄積された正孔が上部電極に引き寄せられると共に電子が下部電極に引き寄せられることでリカバリ電流が発生するリカバリ状態となり、リカバリ状態が経過した後にオフ状態となる。

しかしながら、このような半導体装置では、リカバリ状態において、ドリフト層とベース層との間に構成される空乏層が下部電極側(すなわち、半導体基板の他面側)に伸びる。このため、リカバリ状態でのサージピーク電圧(以下では、単にサージピーク電圧ともいう)が大きくなり易い。そして、サージピーク電圧が大きくなることにより、半導体装置が破壊されてしまうことが懸念される。

本開示は、リカバリ状態でのサージピーク電圧を小さくできる半導体装置を提供することを目的とする。

本開示の1つの観点によれば、IGBT素子(1a)を有するIGBT領域(1)と、FWD素子(2a)を有するFWD領域(2)とが共通の半導体基板(10)に形成されている半導体装置は、第1導電型のドリフト層(11)と、ドリフト層上に形成された第2導電型のベース層(12)と、ベース層の表層部であって、ベース層を挟んでドリフト層から離れた位置に形成され、ドリフト層よりも高不純物濃度とされた第1導電型のエミッタ領域(16)と、ドリフト層を挟んでベース層と反対側であって、IGBT領域に形成された第2導電型のコレクタ層(20)と、ドリフト層を挟んでベース層と反対側であって、FWD領域に形成され、コレクタ層と隣接する第1導電型のカソード層(21)と、ベース層と、コレクタ層およびカソード層との間に形成されたFS層(22)と、を有する半導体基板と、エミッタ領域とドリフト層との間に位置するベース層の表面に配置されたゲート絶縁膜(14)と、ゲート絶縁膜上に配置されたゲート電極(15)と、ベース層およびエミッタ領域と電気的に接続される第1電極(18)と、コレクタ層およびカソード層と電気的に接続される第2電極(23)と、を備え、FS層は、コレクタ層およびカソード層から離れて形成されている。そして、半導体装置は、FWD素子に順方向電流が流れている状態から当該電流を遮断してリカバリ状態となった際、FWD素子内の第1キャリアの一部がコレクタ層へと流れることにより、サージピーク電圧を小さくする量の第2キャリアが第2電極からコレクタ層を介してドリフト層に注入されるようになっている。

これによれば、リカバリ状態において、サージピーク電圧を小さくできる第2キャリアが注入されるようにしている。このため、半導体装置が破壊されることを抑制できる。

なお、上記および特許請求の範囲における括弧内の符号は、特許請求の範囲に記載された用語と後述の実施形態に記載される当該用語を例示する具体物等との対応関係を示すものである。

以下、本開示の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。

(第1実施形態)

第1実施形態について図面を参照しつつ説明する。なお、本実施形態の半導体装置は、例えば、インバータ、DC/DCコンバータ等の電源回路に使用されるパワースイッチング素子として利用されると好適である。

第1実施形態について図面を参照しつつ説明する。なお、本実施形態の半導体装置は、例えば、インバータ、DC/DCコンバータ等の電源回路に使用されるパワースイッチング素子として利用されると好適である。

図1に示されるように、半導体装置は、IGBT素子1aを有するIGBT領域1と、FWD素子2aを有するFWD領域2とが共通の半導体基板10に形成されたRC(すなわち、Reverse Conducting)-IGBTとされている。特に限定されるものではないが、本実施形態では、IGBT領域1およびFWD領域2は、一方向に沿って延設されていると共に、延設方向と交差する方向に交互に形成されている。なお、図1中では、IGBT領域1およびFWD領域2は、紙面左右方向に沿って延設され、紙面上下方向に交互に形成されている。

図2に示されるように、半導体基板10は、N-型のドリフト層11を有している。なお、半導体基板10は、例えば、シリコン基板で構成される。そして、ドリフト層11上(すなわち、半導体基板10の一面10a側)には、P型のベース層12が形成されている。

また、半導体基板10には、ベース層12を貫通してドリフト層11に達するように複数のトレンチ13が形成されている。これにより、ベース層12は、トレンチ13によって複数個に分離されている。本実施形態では、複数のトレンチ13は、IGBT領域1およびFWD領域2にそれぞれ形成され、半導体基板10の一面10aの面方向のうちの一方向に沿って等間隔に形成されたストライプ状とされている。なお、図2中では、各トレンチ13は、紙面垂直方向に沿って形成されている。

各トレンチ13は、各トレンチ13の壁面を覆うように形成されたゲート絶縁膜14と、このゲート絶縁膜14の上に形成されたポリシリコン等により構成されるゲート電極15とにより埋め込まれている。これにより、トレンチゲート構造が構成されている。

ベース層12の表層部(すなわち、半導体基板10の一面10a側)には、ドリフト層11よりも高不純物濃度とされたN+型のエミッタ領域16が形成されている。具体的には、エミッタ領域16は、ベース層12内において終端し、かつ、トレンチ13の側面に接するように形成されている。より詳しくは、エミッタ領域16は、トレンチ13間の領域において、トレンチ13の長手方向に沿ってトレンチ13の側面に接するように棒状に延設され、トレンチ13の先端よりも内側で終端する構造とされている。なお、本実施形態では、トレンチ13の壁面のうちのエミッタ領域16とドリフト層11との間に位置する部分が、エミッタ領域とドリフト層との間に位置するベース層の表面に相当する。

半導体基板10の一面10a上には、BPSG(すなわち、Boron Phosphorus Silicon Glass)等で構成される層間絶縁膜17が形成されている。そして、層間絶縁膜17上には、層間絶縁膜17に形成されたコンタクトホール17aを介してエミッタ領域16およびベース層12と電気的に接続される上部電極18が形成されている。つまり、層間絶縁膜17上には、IGBT領域1においてエミッタ電極として機能し、FWD領域2においてアノード電極として機能する上部電極18が形成されている。

なお、本実施形態では、上部電極18が第1電極に相当している。また、図1に示されるように、半導体基板10の一面10a上には、ゲート電極15や図示しない温度センサ等と接続される複数のパッド部19が形成されている。

そして、図2に示されるように、IGBT領域1では、ドリフト層11のうちのベース層12側と反対側(すなわち、半導体基板10の他面10b側)にP+型のコレクタ層20が形成されている。また、FWD領域2では、ドリフト層11のうちのベース層12側と反対側(すなわち、半導体基板10の他面10b側)にN+型のカソード層21が形成されている。つまり、IGBT領域1とFWD領域2とは、半導体基板10の他面10b側に形成される層がコレクタ層20であるかカソード層21であるかによって区画されている。そして、本実施形態では、コレクタ層20上の部分がIGBT領域1とされ、カソード層21上の部分がFWD領域2とされている。なお、コレクタ層20およびカソード層21は、半導体基板10の他面10bから一面10aに向かって同じ深さまで形成されている。

また、ドリフト層11には、ベース層12側と反対側(すなわち、半導体基板10の他面10b側)に、ドリフト層11よりも高不純物濃度とされたN型のFS層22が形成されている。具体的には、FS層22は、コレクタ層20およびカソード層21と離れた位置に形成されている。言い換えると、FS層22は、ドリフト層11内に形成されている。つまり、FS層22は、コレクタ層20およびカソード層21との間にドリフト層11の一部が残存するように形成されている。なお、FS層22は、具体的には後述するが、半導体基板10の厚さL1に対するFS層22とコレクタ層20およびカソード層21との間隔L2の比率が所定値となるように形成されている。

コレクタ層20およびカソード層21を挟んでドリフト層11と反対側(すなわち、半導体基板10の他面10b)には、コレクタ層20およびカソード層21と電気的に接続される下部電極23が形成されている。つまり、IGBT領域1においてはコレクタ電極として機能し、FWD領域2においてはカソード電極として機能する下部電極23が形成されている。本実施形態では、下部電極23が第2電極に相当している。

そして、上記のように構成されていることにより、FWD領域2においては、ベース層12をアノードとし、ドリフト層11、FS層22、カソード層21をカソードとしてPN接合されたFWD素子2aが構成されている。

以上が本実施形態における半導体装置の構成である。なお、本実施形態では、N型、N+型、N-型が第1導電型に相当しており、P型、P+型が第2導電型に相当している。また、本実施形態では、半導体基板10は、上記のように、コレクタ層20、カソード層21、ドリフト層11、FS層22、ベース層12、エミッタ領域16を含んで構成されている。次に、上記半導体装置の作動について説明する。

まず、半導体装置は、下部電極23に上部電極18より高い電圧が印加されると、ベース層12とドリフト層11との間に形成されるPN接合が逆導通状態となって空乏層が形成される。この際、ゲート電極15に、絶縁ゲート構造の閾値電圧Vth未満であるローレベル(例えば、0V)の電圧が印加されているときには、上部電極18と下部電極23との間に電流は流れない。

そして、IGBT素子1aをオン状態にするには、下部電極23に上部電極18より高い電圧が印加された状態で、ゲート電極15に、絶縁ゲート構造の閾値電圧Vth以上であるハイレベルの電圧が印加されるようにする。これにより、ベース層12のうちのトレンチ13と接している部分には、反転層が形成される。そして、IGBT素子1aは、エミッタ領域16から反転層を介して電子がドリフト層11に供給されることによってコレクタ層20から正孔がドリフト層11に供給され、伝導度変調によりドリフト層11の抵抗値が低下することでオン状態となる。

また、IGBT素子1aをオフ状態にし、FWD素子2aをオン状態にする(すなわち、FWD素子2aをダイオード動作させる)際には、上部電極18と下部電極23に印加する電圧をスイッチングし、上部電極18に下部電極23より高い電圧を印加する。そして、ゲート電極15に絶縁ゲート構造の閾値電圧Vth未満であるローレベル(例えば、0V)の電圧を印加する。これにより、ベース層12のうちのトレンチ13と接する部分に反転層が形成されなくなり、上部電極18からベース層12を介して正孔が供給されると共に、下部電極23からカソード層21を介して電子が供給され、FWD素子2aがダイオード動作をする。

その後、FWD素子2aをオン状態からオフ状態にする際には、下部電極23に上部電極18より高い電圧を印加する逆電圧印加を行う。つまり、FWD素子2aに順方向電流が流れている状態から当該電流を遮断する際、下部電極23に上部電極18より高い電圧を印加する逆電圧印加を行う。これにより、FWD素子2aがリカバリ状態となる。そして、ベース層12中の正孔が上部電極18側に引き寄せられると共にドリフト層11中の電子が下部電極23側に引き寄せられることでリカバリ電流が発生し、ベース層12とドリフト層11との間の空乏層が伸びる。

ここで、リカバリ状態では、図3に示されるように、ドリフト層11中の電子の一部がコレクタ層20を介しても下部電極23に流れ込む。そして、コレクタ層20に電子が流れ込むことにより、下部電極23からコレクタ層20を介して正孔がドリフト層11に注入される。

この際、本実施形態の半導体装置では、FS層22がコレクタ層20およびカソード層21から離れて形成されている。このため、本実施形態の半導体装置では、FS層22がコレクタ層20およびカソード層21と接している従来の半導体装置と比較して、コレクタ層20上およびその近傍に位置する領域の内部抵抗が大きくなる。このため、本実施形態の半導体装置では、従来の半導体装置と比較して、電子がコレクタ層20に流れ込む際の電圧降下が大きくなる。つまり、本実施形態の半導体装置では、従来の半導体装置と比較して、コレクタ層20上およびその近傍の領域の電位が低くなり易い。

したがって、本実施形態の半導体装置では、リカバリ状態において、電子がコレクタ層20へと流れ込み易くなり、これに伴ってコレクタ層20を介してドリフト層11に注入される正孔の量が増加する。そして、コレクタ層20から注入される正孔は、半導体基板10の面方向に沿っても広がるため、カソード層21上の領域にも正孔が供給される。このため、本実施形態の半導体装置では、リカバリ状態において、FWD領域2でキャリアが枯渇し難くなり、空乏層が半導体基板10の他面10b側に伸び難くなる。つまり、本実施形態の半導体装置では、リカバリ状態において、FWD領域2の空間電荷密度が上昇し、空乏層が半導体基板10の他面10b側に伸び難くなる。これにより、本実施形態の半導体装置では、リカバリ状態において、完全空乏化を抑制でき、サージピーク電圧を小さくできる。

なお、本実施形態では、電子が第1キャリアに相当し、正孔が第2キャリアに相当している。また、本実施形態のFS層22は、後述するように、リカバリ状態において、サージピーク電圧が小さくなる適量の正孔が注入される位置に形成されている。

そして、本発明者らは、さらに、サージピーク電圧の大きさと、半導体基板10の厚さL1に対するFS層22とコレクタ層20およびカソード層21との間隔L2の比率について検討を行い、図4に示す結果を得た。

なお、図2に示されるように、半導体基板10の厚さL1とは、半導体基板10の一面10aと他面10bとの間の長さのことである。FS層22とコレクタ層20およびカソード層21との間隔L2とは、FS層22とコレクタ層20およびカソード層21との間の半導体基板10の厚さ方向に沿った長さのことである。但し、図4中では、FS層22とコレクタ層20およびカソード層21との間隔L2を、単にFS層22の間隔と示してある。また、以下では、半導体基板10の厚さL1に対するFS層22とコレクタ層20およびカソード層21との間隔L2の比率[%]を単にL2/L1として説明する。

図4に示されるように、L2/L1が0の場合を基準とすると、サージピーク電圧は、L2/L1を0から徐々に大きくすると小さくなる。なお、L2/L1が0の場合とは、FS層22がコレクタ層20およびカソード層21と接している場合のことである。

そして、サージピーク電圧は、L2/L1が2~17%の間ではほぼ等しくなる。また、サージピーク電圧は、L2/L1が17%よりさらに大きくなるようにすると急峻に小さくなり、L2/L1が約19%となる場合に最も小さくなる。L2/L1が17%から19%の間にサージピーク電圧が急峻に小さくなるのは、ドリフト層11に注入される正孔が増加することにより、サージピーク電圧に到達した時点から定電圧になる時点までの間のサステイン電圧が大きくなることに起因するものである。

しかしながら、サージピーク電圧は、L2/L1が19%より大きくなるようにすると徐々に上昇し、L2/L1が21.5%となる場合にL1/L2が0である場合と同様の大きさとなる。そして、サージピーク電圧は、L2/L1が21.5%より大きくなるようにすると、さらに上昇する。サージピーク電圧がL2/L1を21.5%より大きくした場合にさらに大きくなるのは、L2/L1が大きくなり過ぎることによって正孔が過度に注入され、サステイン電圧が大きくなりすぎるためである。つまり、FS層22とコレクタ層20およびカソード層21との間隔L2が広くなり過ぎると、サージピーク電圧が逆に大きくなってしまう。

したがって、本実施形態では、FS層22は、サージピーク電圧が小さくなる適量の正孔が注入されるように、L2/L1が21.5%未満となる位置に形成されている。より詳しくは、FS層22は、サージピーク電圧が安定して小さくなるように、L2/L1が2~19%となるように形成されることが好ましい。

なお、図4は、半導体基板10の厚さを80μm、ドリフト層11の不純物濃度を1.0×1014cm-3、FS層22の不純物濃度を1.0×1016cm-3、ベース層12の不純物濃度を2.5×1017cm-3、カソード層21の不純物濃度を5.0×1019cm-3としたときのシミュレーション結果である。但し、不純物濃度等を変更したとしても、サージピーク電圧の大きさは変化するが、サージピーク電圧の波形と、L2/L1との関係は変化しない。つまり、本実施形態の半導体装置は、L2/L1が21.5%未満となるようにFS層22を形成することにより、不純物濃度等に関わらずサージピーク電圧を小さくできる。

以上説明したように、本実施形態では、FS層22をコレクタ層20およびカソード層21と離れた位置に形成している。そして、リカバリ状態において、サージピーク電圧を小さくできるように、コレクタ層20から適量の正孔がドリフト層11に注入されるようにしている。つまり、L1/L2が21.5%未満となるようにしている。このため、サージピーク電圧を小さくでき、半導体装置が破壊されることを抑制できる。

(第2実施形態)

第2実施形態について説明する。第2実施形態は、第1実施形態に対して、カソード層21内にキャリア注入層を形成したものであり、その他に関しては第1実施形態と同様であるため、ここでは説明を省略する。

第2実施形態について説明する。第2実施形態は、第1実施形態に対して、カソード層21内にキャリア注入層を形成したものであり、その他に関しては第1実施形態と同様であるため、ここでは説明を省略する。

本実施形態では、図5に示されるように、カソード層21内にP+型のキャリア注入層24が複数形成されている。本実施形態では、複数のキャリア注入層24は、カソード層21の延設方向に沿ってストライプ状となるように形成されている。

これによれば、リカバリ状態では、ドリフト層11内の正孔は、コレクタ層20と共にカソード層21内に位置するキャリア注入層24にも流れ込む。そして、ドリフト層11には、キャリア注入層24を介しても正孔が注入される。このため、リカバリ状態において、FWD領域2でさらにキャリアが枯渇し難くなり、サージピーク電圧を小さくできる。

なお、上記のように、リカバリ状態では、正孔が過度に注入されるとサージピーク電圧が逆に大きくなってしまう。このため、FS層22は、サージピーク電圧が小さくなる適量の正孔が注入されるように、コレクタ層20およびカソード層21との間隔L2が調整された位置に形成されている。

(他の実施形態)

本開示は、実施形態に準拠して記述されたが、本開示は当該実施形態や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。

本開示は、実施形態に準拠して記述されたが、本開示は当該実施形態や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。

例えば、上記第1実施形態では、第1導電型をN型とし、第2導電型をP型とした例について説明したが、第1導電型をP型とし、第2導電型をN型とすることもできる。

また、上記各実施形態において、ベース層12の表層部(すなわち、半導体基板10の一面10a側)に、ベース層12よりも高不純物濃度とされたP+型のコンタクト領域を形成するようにしてもよい。

そして、上記各実施形態において、FS層22は、半導体基板10の厚さ方向に複数形成されていてもよい。例えば、第1実施形態において、図6に示されるように、FS層22は、半導体基板10の厚さ方向に沿って2つ形成されていてもよい。この場合は、サージピーク電圧が小さくなる適量の正孔が注入されるように、最も半導体基板10の他面10b側に位置するFS層22とコレクタ層20およびカソード層21との間隔L2が上記第1実施形態と同様となるように調整されていればよい。

さらに、上記各実施形態において、トレンチゲート型の半導体装置ではなく、半導体基板10の一面10a上にゲート電極15が配置されるプレーナ型の半導体装置としてもよい。この場合は、半導体基板10の一面10a上にゲート絶縁膜14を介してゲート電極15が配置されるため、ベース層12のうちの半導体基板10の一面10aを構成する部分がベース層の表面に相当する。

また、上記第2実施形態において、複数のキャリア注入層24は、ストライプ状ではなく、例えば、格子状に形成されていてもよい。また、キャリア注入層24は複数ではなく、1つのみ形成されていてもよい。

Claims (5)

- IGBT素子(1a)を有するIGBT領域(1)と、FWD素子(2a)を有するFWD領域(2)とが共通の半導体基板(10)に形成されている半導体装置であって、

第1導電型のドリフト層(11)と、

前記ドリフト層上に形成された第2導電型のベース層(12)と、

前記ベース層の表層部であって、前記ベース層を挟んで前記ドリフト層から離れた位置に形成され、前記ドリフト層よりも高不純物濃度とされた第1導電型のエミッタ領域(16)と、

前記ドリフト層を挟んで前記ベース層と反対側であって、前記IGBT領域に形成された第2導電型のコレクタ層(20)と、

前記ドリフト層を挟んで前記ベース層と反対側であって、前記FWD領域に形成され、前記コレクタ層と隣接する第1導電型のカソード層(21)と、

前記ベース層と、前記コレクタ層および前記カソード層との間に形成されたフィールドストップ層(22)と、を有する前記半導体基板と、

前記エミッタ領域と前記ドリフト層との間に位置する前記ベース層の表面に配置されたゲート絶縁膜(14)と、

前記ゲート絶縁膜上に配置されたゲート電極(15)と、

前記ベース層および前記エミッタ領域と電気的に接続される第1電極(18)と、

前記コレクタ層および前記カソード層と電気的に接続される第2電極(23)と、を備え、

前記フィールドストップ層は、前記コレクタ層および前記カソード層から離れて形成されており、

前記FWD素子に順方向電流が流れている状態から当該電流を遮断してリカバリ状態となった際、前記FWD素子内の第1キャリアの一部が前記コレクタ層へと流れることにより、サージピーク電圧を小さくする量の第2キャリアが前記第2電極から前記コレクタ層を介して前記ドリフト層に注入される半導体装置。 - 前記フィールドストップ層は、前記半導体基板の厚さ(L1)に対する前記フィールドストップ層と前記コレクタ層および前記カソード層との間隔(L2)の比率が21.5%未満となる位置に形成されている請求項1に記載の半導体装置。

- 前記フィールドストップ層は、前記半導体基板の厚さ(L1)に対する前記フィールドストップ層と前記コレクタ層および前記カソード層との間隔(L2)の比率が2~21%となる位置に形成されている請求項1に記載の半導体装置。

- 前記カソード層には、前記コレクタ層と離れた位置に、前記第2電極と電気的に接続される第2導電型のキャリア注入層(24)が形成されている請求項1に記載の半導体装置。

- 前記キャリア注入層は、複数形成されている請求項4に記載の半導体装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017117072A JP2019004030A (ja) | 2017-06-14 | 2017-06-14 | 半導体装置 |

| JP2017-117072 | 2017-06-14 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2018230312A1 true WO2018230312A1 (ja) | 2018-12-20 |

Family

ID=64660825

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2018/020231 WO2018230312A1 (ja) | 2017-06-14 | 2018-05-25 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2019004030A (ja) |

| WO (1) | WO2018230312A1 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7409326B2 (ja) | 2019-01-15 | 2024-01-09 | ソニーグループ株式会社 | サーバおよび学習システム |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2007055352A1 (ja) * | 2005-11-14 | 2007-05-18 | Fuji Electric Device Technology Co., Ltd. | 半導体装置およびその製造方法 |

| JP2013065735A (ja) * | 2011-09-19 | 2013-04-11 | Denso Corp | 半導体装置 |

| JP2015177057A (ja) * | 2014-03-14 | 2015-10-05 | 株式会社東芝 | 半導体装置 |

| JP2015213193A (ja) * | 2015-07-21 | 2015-11-26 | ルネサスエレクトロニクス株式会社 | Igbt |

| JP2016006891A (ja) * | 2011-07-27 | 2016-01-14 | トヨタ自動車株式会社 | ダイオード、半導体装置およびmosfet |

| EP3154091A1 (en) * | 2015-10-07 | 2017-04-12 | ABB Technology AG | Reverse-conducting semiconductor device |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012142537A (ja) * | 2010-12-16 | 2012-07-26 | Mitsubishi Electric Corp | 絶縁ゲート型バイポーラトランジスタとその製造方法 |

| JP5751125B2 (ja) * | 2011-10-20 | 2015-07-22 | 株式会社デンソー | 半導体装置 |

| JP6119577B2 (ja) * | 2013-11-26 | 2017-04-26 | 三菱電機株式会社 | 半導体装置 |

| JP6261494B2 (ja) * | 2014-12-03 | 2018-01-17 | 三菱電機株式会社 | 電力用半導体装置 |

-

2017

- 2017-06-14 JP JP2017117072A patent/JP2019004030A/ja active Pending

-

2018

- 2018-05-25 WO PCT/JP2018/020231 patent/WO2018230312A1/ja active Application Filing

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2007055352A1 (ja) * | 2005-11-14 | 2007-05-18 | Fuji Electric Device Technology Co., Ltd. | 半導体装置およびその製造方法 |

| JP2016006891A (ja) * | 2011-07-27 | 2016-01-14 | トヨタ自動車株式会社 | ダイオード、半導体装置およびmosfet |

| JP2013065735A (ja) * | 2011-09-19 | 2013-04-11 | Denso Corp | 半導体装置 |

| JP2015177057A (ja) * | 2014-03-14 | 2015-10-05 | 株式会社東芝 | 半導体装置 |

| JP2015213193A (ja) * | 2015-07-21 | 2015-11-26 | ルネサスエレクトロニクス株式会社 | Igbt |

| EP3154091A1 (en) * | 2015-10-07 | 2017-04-12 | ABB Technology AG | Reverse-conducting semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2019004030A (ja) | 2019-01-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10062760B2 (en) | Semiconductor device | |

| US10170607B2 (en) | Semiconductor device | |

| WO2017199679A1 (ja) | 半導体装置 | |

| JP5787853B2 (ja) | 電力用半導体装置 | |

| WO2017155122A1 (ja) | 半導体装置 | |

| WO2018220879A1 (ja) | 半導体装置 | |

| JP2018073911A (ja) | 半導体装置 | |

| JP2016136620A (ja) | 半導体装置 | |

| JP2007184486A (ja) | 半導体装置 | |

| JP5480084B2 (ja) | 半導体装置 | |

| JP2008053648A (ja) | 絶縁ゲート型半導体装置及びその製造方法 | |

| CN107148675A (zh) | 半导体装置 | |

| JP2016157934A (ja) | 半導体装置 | |

| JPH09283754A (ja) | 高耐圧半導体装置 | |

| JP5537359B2 (ja) | 半導体装置 | |

| JP2008311301A (ja) | 絶縁ゲートバイポーラトランジスタ | |

| JP2013080796A (ja) | 半導体装置 | |

| WO2016114131A1 (ja) | 半導体装置 | |

| JP2018041845A (ja) | 半導体装置 | |

| US20170309704A1 (en) | Semiconductor device and manufacturing method therefor | |

| US20150357450A1 (en) | Charge reservoir igbt top structure | |

| JP2011238681A (ja) | 半導体装置 | |

| JP2014154739A (ja) | 半導体装置 | |

| WO2018230312A1 (ja) | 半導体装置 | |

| WO2019098122A1 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| 121 | Ep: the epo has been informed by wipo that ep was designated in this application |

Ref document number: 18816891 Country of ref document: EP Kind code of ref document: A1 |

|

| NENP | Non-entry into the national phase |

Ref country code: DE |

|

| 122 | Ep: pct application non-entry in european phase |

Ref document number: 18816891 Country of ref document: EP Kind code of ref document: A1 |