KR910002039B1 - 반도체기억장치의 제조방법 - Google Patents

반도체기억장치의 제조방법 Download PDFInfo

- Publication number

- KR910002039B1 KR910002039B1 KR1019870004316A KR870004316A KR910002039B1 KR 910002039 B1 KR910002039 B1 KR 910002039B1 KR 1019870004316 A KR1019870004316 A KR 1019870004316A KR 870004316 A KR870004316 A KR 870004316A KR 910002039 B1 KR910002039 B1 KR 910002039B1

- Authority

- KR

- South Korea

- Prior art keywords

- insulating film

- capacitor

- electrode

- forming

- relay electrode

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/038—Making the capacitor or connections thereto the capacitor being in a trench in the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

Abstract

내용 없음.

Description

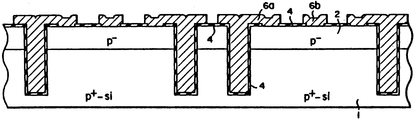

제1a도 내지 제1h도는 본 발명의 제1실시예에 따른 dRAM의 연속적인 제조공정을 나타낸 단면도.

제2도는 본 발명의 제1실시예에 의해 구현된 메모리셀어레이의 평면도.

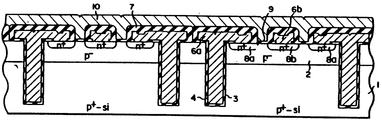

제3a, 3b, 3c도는 각각 제2도의 a-a', b-b', c-c' 선에 따른 단면도.

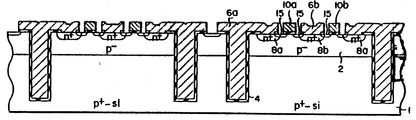

제4a도 및 제4b도는 본 발명의 제2실시예에 따른 dRAM의 연속적인 제조공정을 나타낸 단면도.

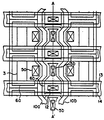

제5a도 및 제5b도는 각각 본 발명의 제2실시예에 의해 구현된 메모리셀어레이의 평면도 및 그 a-a'선 단면도이다.

* 도면의 주요부분에 대한 부호의 설명

1 : 고농도 Si 기판 2 : 저농도 P형 층(웨이퍼)

3 : 도랑 4 : 캐패시터절연막

5a, 5b, 12 : 접촉구멍 6 : 다결정실리콘막(제1도전막)

6a : 캐패시터전극 6b : 중계용 전극

7 : 제1층간절연막 8a, 8b, 15 : n형 층

9 :게이트절연막 10 : 다결정실리콘막(제2도전막)

10a, 10b : 게이트전극 11 : 제2층간절연막

13 : 비트선 14 : 소자분리용 절연막

[산업상의 이용분야]

본 발명은 캐패시터에 축적된 전하에 의해 정보기억을 행하는 하나의 트랜지스터와 하나의 캐패시터로 이루어진 메모리셀구조를 갖춘 반도체기억장치의 제조방법에 관한 것이다.

[종래의 기술 및 그 문제점]

일반적으로 다이나믹 RAM(dRAM)의 메모리셀은 정보를 전하의 형태로 보존유지하는 MOS 캐패시터와, 그 전하를 외부회로와 교환하기 위한 스위칭 MOS 트랜지스터로 구성되어 있는데, dRAM의 대용량화에 따라 하나의 메모리 셀의 점유면적은 필연적으로 감소되는 추세에 잇지만, 정보를 독축할때의 신호레벨이 MOS 캐패시터에 축전된 전하의 양에 의해 결정되므로 그 캐패시터의 실효면적을 대폭적으로 감소시킬 수가 없는바, 이 때문에 반도체기판에 도랑을 형성시켜 캐패시터를 3차원적으로 형성함으로써 칩상의 점유면적을 적게 하면서 캐패시터의 실효면적을 더욱 크게 유지하는 여러방법이 제안되어 있다.

그러나 캐패시터의 미세한 도랑을 깊게 형성시키는 것은 가공기술상 한계가 있으며, 극단적으로 깊게 도랑을 형성시킬 수 없을 뿐만 아니라 메모리 셀의 다른 구성요소인 MOS 트랜지스터도 반도체기억장치의 고집적화를 위해 미세화시킬 목적하에 게이트의 길이를 짧게 하면, 핫캐리어효과등에 의해 반도체기억장치의 신뢰성이 저하된다고 하는 문제가 생긴다.

더욱이 dRAM의 고집적화 및 소자의 미세화로 다음과 같은 문제가 생긴다. 즉, 고집적화에 의해 트랜지스터와 캐패시터등의 구성요소는 가로방향길이가 감소되지만 두께방향의 길이는 가로방향길이만큼 감소되지 않기 때문에 각 층의 가로방향길이에 대한 두께방향길이의 비가 증가되어, 예컨대 접촉구멍이 형성될때 포토리소그래픽시의 정재파효과에 의한 길이가공정밀도의 저하나 에칭시의 배선단 및 에칭잔류물이 남게 된다.

이상과 같이 dRAM의 고집적화 및 소자의 미세화에는 여러가지 문제가 있으며, 더욱 고집적화하고 미세화하기 위해서는 캐패시터와 트랜지스터의 정합마진이나 비트선접촉구멍과 트랜지스터의 정합마진(alignment margin)을 없게 하는것과 미세가공의 정밀도를 높이기 위해서는 기판의 평탄성을 확보하는 것 등이 중요한 해결과제로 되어 있다.

[발명의 목적]

본 발명은 상기와 같은 문제점을 해결할 수 있도록된 반도체기억장치의 제조방법을 제공함에 그 목적이 있다.

[발명의 구성]

상기한 목적을 달성하기 위한 본 발명은, 반도체기판(1, 2)의 캐패시터형성영역에 도랑(3)을 형성하는 단계와, 상기 도랑(3)의 내부를 포함하는 반도체기판(1, 2)에 캐패시터절연막(4)을 형성하는 단계, 상기 캐패시터절연막(4)에 제1 및 제2 접촉구멍(5a, 5b)을 형성하는 단계, 상기 단계들을 거쳐 형성된 매체의 전체표면에 제1도전막(6)을 형성하는 단계, 상기 도랑(3)의 내부표면과 제1접촉구멍(5a)을 덮은 캐패시터전극(6a)과 제2접촉구멍(5b)을 덮은 중계용 전극(6b)을 형성시키기 위해 제1도전막(6)을 패터닝하는 단계, 상기 캐패시터전극(6a)과 중계용 전극(6b)의 표면상에 제1층간절연막(7)을 형성하는 단계, 상기 캐패시터전극(6a)과 중계용 전극(6b) 사이의 기판(1, 2) 부분에 게이트절연막(9)을 형성하는 단계, 상기 단계들을 거쳐 형성된 매체의 전체표면에 제2도전막(10)을 형성하는 단계 ,및 상기 캐패시터(6a)과 중계용 전극(6b)사이의 게이트절연막(9)에 게이트전극(10a, 10b)을 형성시키기 위해 제2도전막(10)을 벡에칭시키는 단계를 구비하여 이루어진 것을 특징으로 한다.

(작용)

상기와 같이 구성된 본 발명의 방법에 의하면, 캐패시터전극과 비트선을 기판에 접속하기 위한 중계용 전극이 동시에 형성되어 이들 사이에 MOS 트랜지스터의 게이트전극이 자기정합적으로 형성된다. 따라서 MOS 트랜지스터와 캐패시터의 정합마진(alignment margin)을 필요로 하지 않는다. 더욱이 비트선을 기판에 접속하기 위한 중계용 전극이 미리 형성되기 때문에 비트선과 MOS 트랜지스터 및 캐패시터의 정합마진도 충분하게 된다.

따라서 dRAM 셀의 점유면적을 종래의 메모리셀에 비해 대폭적으로 축소시킬 수 있다. 또 종래 필요로 했던 게이트전극의 리소그래픽공정이 생략되고, 리소그래픽시의 정재파효과에 의한 가공길이의 정밀도 저하도 발생되지 않게 된다. 더욱이 게이트전극형성직후의 기판표면은 캐패시터전극과 중계용 전극 및 게이트전극이 죽 깔려져서 평탄하게 되어 있기 때문에 상층이 배선가공이 용이하게 되어 신뢰성이 높은 미세가공이 가능하게 된다.

실시예

이하, 예시도면을 참조해서 본 발명에 따른 실시예를 상세히 설명한다.

제1a도 내지 제1h도는 본 발명의 제1실시예에 따른 dRAM의 연속적인 제조공정을 나타낸 단면도로서, 제1a도에 도시한 바와 같이 고농도(1×1018cm-3)의 P형 Si 기판(1)상에 저농도(1×1016cm-3)의 P형 층(2)을 에피택셜성장시킨 웨이퍼에 제1b도에 도시한 바와 같이 캐패시터의 형성영역에 실질적으로 수 ㎛의 면을 갖는 사각형(깊이 ; 5㎛)도랑(3)을 형성시킨 다음 열산화에 의해 상기 사각형 도랑(3)의 내부표면을 포함한 웨이퍼(2)의 전체표면에 캐패시터절연막(4)을 형성시킨다.

이어, 도랑(3)을 이온에칭수단에 의해 P형 층(2)과 기판(1)의 경계면보다 충분히 깊게 형성시킨 후, 제1c도에 도시한 바와 같이 캐패시터절연막(4)에 두종류의 접촉구멍(5a, 5b)을 통상의 리소그래픽기술에 의해 형성시키고, 기판(1) 전체면에 제1전극막인 다결정실리콘막(6)을 퇴적시키는데, 상기 다결정실리콘막(6)은 CVD법에 의해 인이 도핑된 다결정실리콘으로서, 예컨대 4000Å 정도의 두께로 형성된다.

이제 제1c에 도시한 바와 같이 도랑(3)에는 다결정실리콘막(6)이 완전히 매설되어 윗면이 거의 평탄하게 되는바, 이것은 도랑(3)의 폭에 따라 다결정실리콘막(6)의 두께를 선택함으로써 가능하게 된다.

다음에 제1d도에 도시한 바와 같이 통상의 리소그래픽기술 및 에칭기술을 이용하여 다결정실리콘막(6)을 패터닝하고 캐패시터전극(6a)과 비트선을 기판(1)을 접속하기 위해 중계용 전극(6b)을 형성시킨 다음 제1e도에 도시한 바와 같이 습식산화(wet oxidation)에 의해 캐패시터전극(6a) 및 중계용 전극(6b)의 표면에 제1층간절연막(7)을 형성시키는바, 여기서 상기 제1층간절연막(7)을 2000Å정도의 두께로 형성시키지만, 제1층간절연막(7)의 두께를 인접하는 메모리셀의 캐패시터전극사이의 거리가 없도록 선정함에 따라 도시한 바와 같이 인접하는 메모리셀의 캐패시터전극(6a)사이의 간격을 메울 수 있게 된다.

또한, 습식산화의 공정에서 캐패시터전극(6a) 및 중계용 전극(6b)중에 포함된 인이 P형 층(2)내로 확산되어 MOS 트랜지스터의 소오스·드레인으로 되는 n형 층(8a, 8b)이 각각 형성된다. 또 상기 습식산화의 공정에서 기판표면에도 산화막이 형성되는바, 그 두께는 캐패시터전극(6a) 및 중계용 전극(6b)의 표면에 산화막의 두께보다 얇은 예컨대 400Å 정도이다. 여기서 필요하다면 상기 산화막(7 ; 제1층간절연막)을 통해 MOS 트랜지스터의 임계치를 제어하거나 펀치드로우(punch-through)를 방지하기 위해 이온을 주입시키게 된다. 그 다음 기판표면의 산화막을 제거하여 새로운 열산화로 예컨대 두께 200Å인 MOS 트랜지스터의 게이트절연막(9)을 형성시킨다.

다음에 제1F도에 도시한 바와 같이 기판전체면에 CVD법에 의해 예컨대 5000Å 두께의 제2전극막인 다결정실리콘막(10)을 퇴적시키고, 상기 다결정실리콘막(10)을 소위 에치백(etch-back)이라고 하는 에칭을 시켜 제1g도에 도시한 바와 같이 캐패시터전극(6a)과 중계용 전극(6b)의 사이에 MOS 트랜지스터의 게이트전극(10a, 10b)을 형성시키게 되는바, 여기서 에치백은 이방성에칭에 의해 수행된다. 이 상태에서 기판(1)의 표면은 캐패시터전극(6a) 및 게이트전극(10a, 10b)이 죽 깔려진 상태로 되어 평탄한 것으로 된다. 그리고 마지막으로 제1H도에 도시한 바와 같이 CVD 산화막 또는 PSG 산화막등의 제2층간절연막(11)을 퇴적형성시키고, 이 절연막(11)의 중계용 전극(6b) 상에 접촉구멍(12)을 개공시켜 알루미늄막에 의한 비트선(13)을 설치한다.

제2도는 본 발명의 제1실시예에 의해 얻어진 메모리셀어레이의 평면도로서, 제1a도 내지 제1h도에 도시된 공정단면도는 제2도의 비트선(13)에 따른 단면도이다. 여기서 제2도의 a-a', b-b' 및 c-c'선에 따른 단면도가 각각 제3a도 및 제3b도 및 제3c도로 되는바, 인접하는 비트선(13)사이, 즉, 제2도의 세로방향으로 소자분리용 절연막(14)이 매립되어 있지만, 비트선(13)방향으로 제1a도 내지 제1h도에서 분명히 도시한 바와 같이 소자분리용 절연막은 설치되어 있지 않다.

종래의 일반적인 dRAM 셀에서는 기판측에 기억노드가 형성되고, 이 기억노드상에 형성되는 캐패시터전극이 소위 셀플레이트로서 전체 메모리셀에 공통으로 형성되지만, 본 실시예에서는 캐패시터전극(6a)이 각 메모리셀마다 독립의 기억노드로서 이용되는 것으로 되어 있다.

상기한 바와 같이 본 발명에 의하면, 캐패시터전극(6a)과 MOS 트랜지스터의 게이트전극(10a, 10b)이 자기정합적으로 형성되어 게이트전극형성에서의 리소그래픽공정을 필요로 하지 않는다. 따라서 제조공정이 단축될 뿐만 아니라 캐패시터전극과 게이트전극을 가까이 배치할 수 있고, 비트선(13)을 기판에 접속하기 위한 중계용 전극(6b)이 캐패시터전극(6a)과 동시에 형성되기 때문에 제2도에 도시한 바와 같이 비트선용접촉구멍(12)은 중계용 전극(6b) 위에 위치하게 되어 이 비트선접촉구멍의 정합마진이 충분하게 된다. 더욱이 비트선용접촉구멍(12)은 중계용 전극(6b)이 형성되어 있기 때문에 종래보다 얇은 것으로 되어 미세가공이 용이하게 된다.

또, 캐패시터전극(6a)과 중계용 전극(6b) 및 게이트전극(10a, 10b)이 형성된 상태에서 기판표면이 극히 평탄하게 되므로 그후에 배선형성공정에서의 리소그래픽정밀도는 높아지게 된다. 따라서 본 실시예에 의하면 소자의 미세화와 고집적화를 이룩한 dRAM을 얻을 수가 있다.

상기 실시예에서는 MOS 트랜지스터의 소오스 및 드레인영역이 캐패시터전극 및 중계용 전극을 확산원으로 한 고체상태의 확산만을 이용하여 형성하였는데, 이 방법에서는 확산층의 제어가 충분히 이루어지지 않을 가능성이 있다.

예컨대 확산층의 가로방향확산이 불충분하게 되며, MOS 트랜지스터가 오프셋게이트구조로 될 가능성이 있게 된다. 이점을 개량한 실시예를 다음에 설명한다.

제4a도 및 제4b도는 본 발명의 제2실시예에 따른 dRAM의 연속적인 제조공정을 나타낸 단면도로서, 이 실시예의 경우 게이트전극을 형성시키는 제조공정은 앞의 실시예와 동일하다. 즉, 제1A도∼제1G도에 도시한 공정으로 게이트전극을 형성시키고, 그 다음 캐패시터전극(6a) 및 중계용 전극(6b) 표면의 제1층간절연막(7)을 에칭제거시켜 제4a도의 상태를 얻는다. 이 상태에서 불순물을 이온주입시켜 제4b도에 도시한 바와 같이 게이트전극(10a, 10b)과 캐패시터전극(6a) 및 중계용 전극(6b) 각각의 간격부분인 기판표면에 소오스 및 드레인영역의 일부로 되는 n형 층(15)을 형성시키고, 그 다음에 앞의 실시예와 동일한 제조공정이 이루어지게 된다.

본 실시예에 의하면 다결정실리콘층에서의 확산만으로 소오스, 드레인영역을 형성시키는 경우에 비해 더 높은 정밀도의 불순물프로파일이 얻어지게 되어 게이트오프셋이 발생되지 않을 뿐만 아니라 MOS 트랜지스터특성의 변동을 제어할 수가 있게 된다.

다음에 본 발명의 제2실시예에 의해 얻어진 메모리셀어레이의 평면도인 제5a도 및 그 a-a' 선 단면도인 제5b도를 참조하여 dRAM의 제조공정을 설명한다.

앞의 실시예에서는 중계용 전극(6b)을 기판에 접속시키기 위해 접촉구멍(5b)과 중계용 전극(6b) 위의 접촉구멍(12)을 동일위치에 형성시켰다. 이 경우 정합마진 때문에 중계용 저극(6b)의 길이를 어느 정도 길게 할 필요가 있으며, 이것은 더욱 더 고집적화를 방해하는 요인이 된다.

제5a도 및 제5b도의 실시예에서는 중계용 전극(6b)을 소자분리영역위로까지 연장형성시켜 소자분리영역위에 접촉구멍(12)을 형성시키고, 비트선(13)을 소자분리영역위에 설치하게 된다. 제5a도에 도시한 바와 같이 소자분리영역위에 있는 중계용 전극(6b)의 폭을 충분히 크게 할 수가 있다.

따라서 본 실시예에 의하면, 메모리셀의 가로방향길이를 충분히 축소하여 더욱 비트선의 접촉을 여유있게 형성시킬 수가 있다. 또한, 본 발명은 상기 실시예에 한정되지 않는바, 예컨대 상기 실시예에서는 캐패시터 절연막에다 캐패시터전극 및 중계용 전극을 기판에 접속하기 위한 접촉구멍(5a, 5b)을 각각 별개로 형성시켰지만, 이들 접촉구멍(5a, 5b)을 별개로 형성시킬 필요만은 없다.

즉, 캐패시터절연막(4)은 캐패시터절연막에 필요한 부분만을 남기고 다른 부분을 제거하여 폭넓게 기판표면을 노출시켜도 된다. 또 본 발명의 실시예는 개방형 비트선(open bit line)방식의 메모리셀어레이인 경우에 대해 설명했지만, 주름형 비트선(folded bit line) 방식에도 같은 방법을 적용할 수가 있다.

[발명의 효과]

상기한 바와 같이 본 발명에 의하면, 에칭기술을 이용하여 게이트전극을 캐패시터전극 및 비트선접촉부에 대해 자기정합적으로 형성시킬 수 있어 메모리셀면적이 축소되므로 dRAM의 고집적화를 꾀할 수 있을 뿐만 아니라 게이트전극은 리소그래픽공정을 생략하여 형성시킬 수 있기 때문에, 제조공정이 간단하게 됨과 더불어 가공정밀도가 향상되어 배선공정앞의 기판표면의 평탄성이 우수하게 되므로 리소그래픽공정의 생략과 함께 메모리셀의 고집적화를 도모할 수 있게 된다.

Claims (8)

- 반도체기판(1, 2)의 캐패시터형성영역에 도랑(3)을 형성하는 단계와, 상기 도랑(3)의 내부를 포함하는 반도체기판(1, 2)에 캐패시터절연막(4)을 형성하는 단계, 상기 캐패시터절연막(4)에 제1 및 제2접촉구멍(5a, 5b)을 형성하는 단계, 상기 단계들을 거쳐 형성된 매체의 전체표면에 제1도전막(6)을 형성하는 단계, 상기 도랑(3)의 내부표면과 제1접촉구멍(5a)을 덮은 캐패시터전극(6a)과 제2접촉구멍(5b)을 덮은 중계용전극(6b)을 형성시키기 위해 제1도전막(6)을 패터닝하는 단계, 상기 캐패시터전극(6a)과 중계용 전극(6b)의 표면상에 제1층간절연막(7)을 형성하는 단계, 상기 캐패시터전극(6a)과 중계용 전극(6b) 사이의 기판(1, 2)부분에 게이트절연막(9)을 형성하는 단계, 상기 단계들을 거쳐 형성된 매체의 전체표면에 제2도전막(10)을 형성하는 단계 및 상기 캐패시터전극(6a)과 중계용 전극(6b) 사이의 게이트절연막(9)에 게이트전극(10a, 10b)을 형성시키기 위해 제2도전막(10)을 백에칭시키는 단계를 구비하여 이루어진 것을 특징으로 하는 캐패시터와 트랜지스터를 구비한 반도체기억장치의 제조방법.

- 제1항에 있어서, 상기 제1도전막(6)은 불순물이 도핑된 다결정실리콘이고, 이 불순물을 캐패시터전극(6a)과 중계용 전극(6b)으로 부터 제1 및 제2접촉구멍(5a, 5b)을 통해 기판(2)으로 확산시켜 소오스와 드레인영역(8a, 8b)을 형성시키도록 된 것을 특징으로 하는 반도체기억장치의 제조방법.

- 제1항에 있어서, 게이트전극(10a, 10b)의 형성후에 제1층간절연막(7)을 제거시키고, 게이트전극(10a, 10b)과 캐패시터전극(6a) 및 중계용 전극(6b)을 마스크로 이용하여 이온주입을 실행함으로써 소오스 및 드레인영역(8a, 8b)을 형성시킬 수 있도록 된 것을 특징으로 하는 반도체기억장치의 제조방법.

- 제1항에 있어서, 다수의 캐패시터전극(6a)과 중계용 전극(6b)상의 제1층간절연막(7)이 습식산화에 의해 형성되고, 상기 기판(1, 2)에 형성된 상기 제1층간절연막(7)을 통해 기판(1, 2)내로 이온을 주입시키도록 된 것을 특징으로 하는 반도체기억장치의 제조방법.

- 제4항에 있어서, 상기 기판(1, 2)상에 형성된 캐패시터절연막(4)을 미리 제거시킨 다음에 열산화시켜 게이트절연막(9)을 형성시키도록 된 것을 특징으로 하는 반도체기억장치의 제조방법.

- 제1항에 있어서, 백에칭제조공정은 이방성에칭에 의해 수행되도록 된 것을 특징으로 하는 반도체기억장치의 제조방법.

- 제1항에 있어서, 상기 게이트전극(10a, 10b)을 형성시킨 다음 제1층간절연막(7)과 상기 게이트전극(10a, 10b)의 전체표면에 걸쳐 제2층간절연막(11)을 형성하고, 제2 및 제3접촉구멍(5b, 12)을 중계용 전극(6b)상에 형성된 제2층간절연막(11)에 형성시키며, 비트선(13)을 상기 접촉구멍(12)을 통해 중계용 전극(6b)에 접촉되도록 형성시킨 것을 특징으로 하는 반도체기억장치의 제조방법.

- 제7항에 있어서, 상기 제2 및 제3접촉구멍(5b, 12)이 각각 서로 겹쳐지지 않도록 형성시켜 준 것을 특징으로 하는 반도체기억장치의 제조방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP61-102456 | 1986-05-02 | ||

| JP61102456A JPS62259464A (ja) | 1986-05-02 | 1986-05-02 | 半導体記憶装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR870011695A KR870011695A (ko) | 1987-12-26 |

| KR910002039B1 true KR910002039B1 (ko) | 1991-03-30 |

Family

ID=14327968

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019870004316A KR910002039B1 (ko) | 1986-05-02 | 1987-05-02 | 반도체기억장치의 제조방법 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US4784969A (ko) |

| JP (1) | JPS62259464A (ko) |

| KR (1) | KR910002039B1 (ko) |

| DE (1) | DE3714338A1 (ko) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0824169B2 (ja) * | 1989-05-10 | 1996-03-06 | 富士通株式会社 | 半導体記憶装置の製造方法 |

| US5065273A (en) * | 1990-12-04 | 1991-11-12 | International Business Machines Corporation | High capacity DRAM trench capacitor and methods of fabricating same |

| DE4132140A1 (de) * | 1991-09-26 | 1993-04-08 | Siemens Ag | Verfahren zur herstellung einer selbstjustierten kontaktlochanordnung und selbstjustierte kontaktlochanordnung |

| US5395784A (en) * | 1993-04-14 | 1995-03-07 | Industrial Technology Research Institute | Method of manufacturing low leakage and long retention time DRAM |

| US5406515A (en) * | 1993-12-01 | 1995-04-11 | International Business Machines Corporation | Method for fabricating low leakage substrate plate trench DRAM cells and devices formed thereby |

| US6750091B1 (en) * | 1996-03-01 | 2004-06-15 | Micron Technology | Diode formation method |

| US5998821A (en) * | 1997-05-21 | 1999-12-07 | Kabushiki Kaisha Toshiba | Dynamic ram structure having a trench capacitor |

| JP2003197770A (ja) * | 2001-12-25 | 2003-07-11 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| US8480569B2 (en) * | 2006-05-18 | 2013-07-09 | Smart Medical Systems Ltd. | Flexible endoscope system and functionality |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5812739B2 (ja) * | 1975-05-07 | 1983-03-10 | 株式会社日立製作所 | 半導体記憶装置 |

| DE3243125A1 (de) * | 1982-11-22 | 1984-05-24 | Siemens AG, 1000 Berlin und 8000 München | Verfahren zum herstellen von mos-transistoren mit flachen source/drain-gebieten, selbstjustierten polysiliziumkontakten und kurzen kanallaengen |

| JPS60152058A (ja) * | 1984-01-20 | 1985-08-10 | Toshiba Corp | 半導体記憶装置 |

| JPS60175448A (ja) * | 1984-02-21 | 1985-09-09 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| US4658283A (en) * | 1984-07-25 | 1987-04-14 | Hitachi, Ltd. | Semiconductor integrated circuit device having a carrier trapping trench arrangement |

| DE3681490D1 (de) * | 1985-04-01 | 1991-10-24 | Nec Corp | Dynamische speicheranordnung mit wahlfreiem zugriff mit einer vielzahl von eintransistorspeicherzellen. |

-

1986

- 1986-05-02 JP JP61102456A patent/JPS62259464A/ja active Pending

-

1987

- 1987-04-28 US US07/043,444 patent/US4784969A/en not_active Expired - Lifetime

- 1987-04-29 DE DE19873714338 patent/DE3714338A1/de active Granted

- 1987-05-02 KR KR1019870004316A patent/KR910002039B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| DE3714338C2 (ko) | 1991-12-19 |

| US4784969A (en) | 1988-11-15 |

| DE3714338A1 (de) | 1987-11-05 |

| KR870011695A (ko) | 1987-12-26 |

| JPS62259464A (ja) | 1987-11-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP0444615B1 (en) | Dynamic random access memory having bit lines buried in semiconductor substrate | |

| KR100413277B1 (ko) | 다이내믹 랜덤 엑세스 메모리 | |

| KR910010167B1 (ko) | 스택 캐패시터 dram셀 및 그의 제조방법 | |

| KR100509210B1 (ko) | Dram셀장치및그의제조방법 | |

| KR20020045540A (ko) | 반도체 장치와 그 제조 방법 | |

| US4763180A (en) | Method and structure for a high density VMOS dynamic ram array | |

| KR100673673B1 (ko) | Dram 셀 장치 및 그 제조 방법 | |

| US5156993A (en) | Fabricating a memory cell with an improved capacitor | |

| KR920001635B1 (ko) | 반도체기억장치 및 그 제조방법 | |

| KR100417484B1 (ko) | Dram 셀 장치의 제조 방법 | |

| KR910002039B1 (ko) | 반도체기억장치의 제조방법 | |

| KR900000180B1 (ko) | 반도체 기억장치의 제조방법 | |

| KR940002393B1 (ko) | 반도체기억장치 | |

| KR20010020880A (ko) | 반도체 장치의 제조 방법 및 반도체 장치 | |

| US7241659B2 (en) | Volatile memory devices and methods for forming same | |

| US5049518A (en) | Method of making a trench dram cell | |

| JPH0793372B2 (ja) | 半導体記憶装置 | |

| KR20050045715A (ko) | 리세스 채널 모오스 트렌지스터를 갖는 반도체 장치의제조 방법 | |

| US5248891A (en) | High integration semiconductor device | |

| KR900000065B1 (ko) | 독출전용 반도체기억장치와 그 제조방법 | |

| JPH05226603A (ja) | 半導体装置および半導体装置の製造方法 | |

| JPS63199456A (ja) | 半導体集積回路装置 | |

| KR930003856B1 (ko) | 고집적 반도체장치 | |

| KR940009613B1 (ko) | 반도체 메모리 장치의 제조방법 및 그 구조 | |

| KR960001038B1 (ko) | 워드라인 매립형 디램 셀의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| LAPS | Lapse due to unpaid annual fee |