KR20080014833A - 반도체 발광 소자 - Google Patents

반도체 발광 소자 Download PDFInfo

- Publication number

- KR20080014833A KR20080014833A KR1020077028387A KR20077028387A KR20080014833A KR 20080014833 A KR20080014833 A KR 20080014833A KR 1020077028387 A KR1020077028387 A KR 1020077028387A KR 20077028387 A KR20077028387 A KR 20077028387A KR 20080014833 A KR20080014833 A KR 20080014833A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- light emitting

- wavelength

- type gan

- refractive index

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 117

- 239000000758 substrate Substances 0.000 claims abstract description 76

- 230000000737 periodic effect Effects 0.000 claims abstract description 62

- 238000000034 method Methods 0.000 claims description 24

- 238000000605 extraction Methods 0.000 abstract description 26

- 229910052594 sapphire Inorganic materials 0.000 abstract description 17

- 239000010980 sapphire Substances 0.000 abstract description 17

- 239000010410 layer Substances 0.000 description 273

- 229910002704 AlGaN Inorganic materials 0.000 description 15

- 238000001312 dry etching Methods 0.000 description 13

- 238000010586 diagram Methods 0.000 description 10

- 239000011347 resin Substances 0.000 description 9

- 229920005989 resin Polymers 0.000 description 9

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 8

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 6

- 230000000694 effects Effects 0.000 description 6

- 239000013078 crystal Substances 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 230000008569 process Effects 0.000 description 5

- 238000005530 etching Methods 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 229910052757 nitrogen Inorganic materials 0.000 description 4

- 238000001039 wet etching Methods 0.000 description 4

- 238000005253 cladding Methods 0.000 description 3

- 239000002019 doping agent Substances 0.000 description 3

- 125000005842 heteroatom Chemical group 0.000 description 3

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 238000004549 pulsed laser deposition Methods 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- NCGICGYLBXGBGN-UHFFFAOYSA-N 3-morpholin-4-yl-1-oxa-3-azonia-2-azanidacyclopent-3-en-5-imine;hydrochloride Chemical compound Cl.[N-]1OC(=N)C=[N+]1N1CCOCC1 NCGICGYLBXGBGN-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 238000000295 emission spectrum Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 229910001000 nickel titanium Inorganic materials 0.000 description 1

- 230000000644 propagated effect Effects 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 238000007493 shaping process Methods 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000003980 solgel method Methods 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- JOYRKODLDBILNP-UHFFFAOYSA-N urethane group Chemical group NC(=O)OCC JOYRKODLDBILNP-UHFFFAOYSA-N 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 235000020681 well water Nutrition 0.000 description 1

- 239000002349 well water Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/20—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular shape, e.g. curved or truncated substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

- H01L33/42—Transparent materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0083—Periodic patterns for optical field-shaping in or on the semiconductor body or semiconductor body package, e.g. photonic bandgap structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/38—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes with a particular shape

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Led Devices (AREA)

Abstract

반도체 발광 소자의 광 취출 효율을 향상시킨다. 반도체 발광 소자(10)는 사파이어 기판(12) 상에 버퍼층(14)과 n형 GaN층(16)과 InGaN 발광층(18)과 p형 GaN층(32)이 적층된다. p형 GaN층(32) 상에는 투명 전극으로서 기능하는 ZnO층(24)이 설치되고, ZnO층(24)의 표면에는 2차원의 주기적인 간격으로 오목부가 형성된다. InGaN 발광층(18)으로부터의 광의 공기 중에서의 파장을 λ로, 그 파장 λ에서의 ZnO층의 굴절률을 nzλ로, ZnO층과 거기에 접하는 매체의 계면에서의 전반사각을 θz로 했을 때에, 인접하는 오목부의 주기 간격 Lz가 λ/nz λ≤Lz≤λ/(nz λ×(1-sinθz))의 범위가 되도록 설정한다.

Description

본 발명은 반도체 발광 소자에 관한 것으로, 특히 GaN계 반도체 발광 소자에 관한 것이다.

최근, 청색의 반도체 발광 소자로서 GaN계 반도체를 이용한 반도체 발광 소자가 알려져 있다. 청색의 반도체 발광 소자와 황색의 발광체를 조합한 백색 LED는 휴대 전화 등의 LCD 백 라이트용으로서 수요가 증대하고 있다. 또한, 백색 LED는 저소비 전력, 긴 수명이라는 특징을 갖고 있기 때문에, 다음에는 형광등, 백열등 등으로 변하는 광원으로서의 이용이 기대되고 있다.

종래의 GaN계 반도체 발광 소자에서는, 사파이어 기판 상에 GaN 버퍼층, n형 GaN층, 발광층, p형 GaN층이 차례로 결정 성장된 구조가 되고 있다. 그러나, 종래의 이러한 구조에서는, p형 GaN층의 굴절률과 p형 GaN층에 접하는 공기나 수지의 굴절률과의 차이가 크고, p형 GaN층과 p형 GaN층에 접하는 공기나 수지와의 계면에서의 전반사각이 작아지기 때문에, 발광층에서 발생한 광의 대부분이 p형 GaN층에 접하는 공기나 수지와의 계면에서 전반사하여 광 취출 효율이 낮다는 문제가 있었다.

예를 들어, 반도체 발광 소자가 공기 중에서 발광하고 있다고 하면, GaN의 굴절률은 광의 파장이 450㎚일 때에 약 2.5이므로, p형 GaN층과 공기와의 계면에서의 전반사각은 약 24°로 작다. 발광층으로부터 방사되고 이 전반사각보다도 큰 각도로 p형 GaN층과 공기와의 계면에 입사한 광은, p형 GaN층과 공기와의 계면에서 전반사되기 때문에 반도체 발광 소자로부터 취출할 수 없다.

이 문제에 대해서, p형 GaN층에 발광 파장 정도의 간격으로 요철을 주기적으로 형성하는 방법이 제안되고 있다(예를 들어 특허 문헌 1). 이 구조에서는, 주기적으로 형성된 요철에 의한 회절 효과에 의해 발광층으로부터 방사되는 광의 진행 방향이 바뀌어 전반사가 되지 않는 각도로 광이 회절되기 때문에, 반도체 발광 소자의 광 취출 효율이 향상된다.

이러한 주기적으로 형성된 요철을 p형 GaN층에 형성하는 경우, 우선 결정 성장시킨 p형 GaN층 상에 레지스트를 형성하고 간섭 노광법 등에 의해 레지스트 패턴을 형성한다. 그 후, RIE법 등의 건식 에칭에 의해 레지스트 패턴에 덮여 있지 않은 부분을 제거함으로써 p형 GaN층에 요철이 형성된다.

[특허 문헌 1] 일본 공개특허공보 2005-5679호

그러나, p형 GaN층을 건식 에칭에 의해서 에칭한 경우, 플라즈마 손상에 의해 에칭된 p형 GaN층의 표면에 질소 공공(空孔)이 생긴다. 이 질소 공공은 도너로서 작용하기 때문에 에칭된 p형 GaN층의 표면에는 n형화된 부분이 생기게 된다. p형 GaN층의 표면의 일부에 n형화된 부분이 존재하면, 그 부분에 대해서는 n/p 접합이 존재함에도 n측으로부터 +바이어스되기 때문에 역바이어스 상태가 되고, 결과적으로 반도체 발광 소자의 순방향 전압이 상승되고 만다. 또한, n형화된 부분은 발광층에 주입되는 전류가 감소됨에 더하여, p형 GaN층의 저항은 높으며, 전류 퍼짐이 없기 때문에, 결국 반도체 발광 소자의 유효한 발광 영역이 감소되고 만다.

그 때문에, p형 GaN층의 n형화된 부분은 습식 에칭 등의 방법에 의해 제거할 필요가 있지만, GaN의 습식 에칭은 어렵고, 완전히 제거하는 것은 곤란하며, 또한 제조 공정이 증가하기 때문에 제조 비용이 증가한다.

본 발명은 이러한 상황을 감안하여 이루어진 것으로, 그 목적은 광 취출 효율을 향상시킨 반도체 발광 소자의 제공에 있다.

상기 과제를 해결하기 위해서, 본 발명의 일정 양태의 반도체 발광 소자는 기판 상에 n형 GaN층과 발광층과 p형 GaN층이 적층된 반도체 발광 소자로서, p형 GaN층 상에 MgxZn1 - xO층(0≤x≤0.5)이 설치되고, MgxZn1 - xO층(0≤x≤0.5)의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성된다.

이 양태에 의하면, MgxZn1-xO층(0≤x≤0.5)의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성되어 있기 때문에, 발광층으로부터의 광이 회절된다. 회절 광 중 MgxZn1 - xO층(0≤x≤0.5)과 거기에 접하는 매체와의 계면에서의 전반사각보다도 작은 각도로 계면에 입사한 회절 광은, 전반사되지 않고 반도체 발광 소자의 외부에 취출된다. p형 GaN층이 아니라 MgxZn1 - xO층(0≤x≤0.5)에 오목부 또는 볼록부를 형성하고 있기 때문에, 건식 에칭 시의 플라즈마는 p형 GaN층에 직접 노출되지 않고, 손상에 의한 p형 GaN층 표면의 n형화는 일어나지 않기 때문에 순방향 전압을 상승시키지 않고 광 취출 효율을 향상시킬 수 있다. 또한, 종래 필요하던 건식 에칭 후의 습식 에칭의 공정이 불필요해지므로 제조 비용을 삭감할 수 있다.

MgxZn1-xO층(0≤x≤0.5)에 형성되는 오목부 또는 볼록부는 정방 격자형상 또는 삼각 격자형상으로 배치되어도 좋다. 정방 격자형상으로 배치한 경우, 2차원의 주기적인 간격으로 오목부 또는 볼록부를 형성할 수 있다. 삼각 격자형상으로 배치한 경우에는, 2차원의 주기적인 간격으로 형성하는 오목부 또는 볼록부의 밀도를 높게할 수 있고 매우 적합하게 광 취출 효율을 향상시킬 수 있다.

본 발명의 다른 양태도 또한, 반도체 발광 소자이다. 이 반도체 발광 소자는 p형 GaN층과 발광층과 n형 GaN층이 적층된 반도체 발광 소자로서, n형 GaN층의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성된다.

이 양태에 의하면, n형 GaN층의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성되고 있기 때문에 발광층으로부터의 광이 회절된다. 회절 광 중 n형 GaN층과 거기에 접하는 매체와의 계면에서의 전반사각보다도 작은 각도로 계면에 입사한 회절 광은, 전반사 되지 않고 반도체 발광 소자의 외부에 취출된다. n형 GaN층을 건식 에칭함으로써도 질소 공공이 발생하고, n형 GaN층(16)의 표면이 n형화되지만, n형 GaN층은 원래 n형이기 때문에 역바이어스가 인가되는 상태는 되지 않고, 순방향 전압이 상승하지 않고 광 취출 효율을 향상시킬 수 있다. 이 경우에도, 종래 필요하던 건식 에칭 후의 습식 에칭의 공정이 불필요해지므로 제조 비용을 삭감할 수 있다.

n형 GaN층에 형성되는 오목부 또는 볼록부는 정방 격자형상 또는 삼각 격자형상으로 배치되어도 좋다. 정방 격자형상으로 배치한 경우, 2차원의 주기적인 간격으로 오목부 또는 볼록부를 형성할 수 있다. 삼각 격자형상으로 배치한 경우에는, 2차원의 주기적인 간격으로 형성하는 오목부 또는 볼록부의 밀도를 높게 할 수 있고, 매우 적합하게 광 취출 효율을 향상시킬 수 있다.

본 발명의 또 다른 양태도 또한 반도체 발광 소자이다. 이 반도체 발광 소자는, 기판 상에 n형 GaN층과 발광층과 p형 GaN층이 적층된 반도체 발광 소자로서, 기판은 SiC 기판이며, SiC 기판의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성된다.

이 양태에 의하면, SiC 기판의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성되고 있기 때문에, 발광층으로부터 SiC 기판 방향으로 방출된 광이 회절된다. 이것에 의해, 광의 취출 효율을 향상시킬 수 있다. SiC 기판을 건식 에칭해도, 플라즈마 손상에 의한 순방향 전압의 상승이라는 문제는 발생하지 않기 때문에 가공이 용이하다.

SiC 기판에 형성되는 오목부 또는 볼록부는 정방 격자형상 또는 삼각 격자형상으로 배치되어도 좋다. 정방 격자형상으로 배치한 경우, 2차원의 주기적인 간격으로 오목부 또는 볼록부를 형성할 수 있다. 삼각 격자형상으로 배치한 경우에는, 2차원의 주기적인 간격으로 형성하는 오목부 또는 볼록부의 밀도를 높게 할 수 있고 매우 적합하게 광 취출 효율을 향상시킬 수 있다.

p형 GaN층 상에 MgxZn1-xO층(0≤x≤0.5)이 설치되고, MgxZn1-xO층(0≤x≤0.5)의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성되어도 좋다. 이 경우, MgxZn1-xO층(0≤x≤0.5)의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성되어 있기 때문에, 발광층으로부터 MgxZn1 - xO층(0≤x≤0.5) 방향으로 방출된 광이 회절된다. 회절 광 중 MgxZn1 - xO층(0≤x≤0.5)과 거기에 접하는 매체와의 계면에서의 전반사각보다도 작은 각도로, MgxZn1-xO층(0≤x≤0.5)과 거기에 접하는 매체와의 계면에 입사한 회절 광은 전반사되지 않고 반도체 발광 소자의 외부에 취출할 수 있다.

MgxZn1-xO층(0≤x≤0.5)에 형성되는 오목부 또는 볼록부는 정방 격자형상 또는 삼각 격자형상으로 배치되어도 좋다. 정방 격자형상으로 배치한 경우, 2차원의 주기적인 간격으로 오목부 또는 볼록부를 형성할 수 있다. 삼각 격자형상으로 배치한 경우에는, 2차원의 주기적인 간격으로 형성하는 오목부 또는 볼록부의 밀도를 높일 수 있고 매우 적합하게 광 취출 효율을 향상시킬 수 있다.

본 발명에 따른 반도체 발광 소자에 의하면 광 취출 효율을 향상시킬 수 있다.

도 1은 본 발명의 제1 실시 형태에 따른 반도체 발광 소자의 단면도이다.

도 2는 오목부의 배치예를 나타내는 도면이다.

도 3은 오목부의 다른 배치예를 나타내는 도면이다.

도 4는 반도체 발광 소자의 전류-휘도 특성을 나타내는 도면이다.

도 5는 오목부의 주기 간격을 설명하기 위한 도면이다.

도 6은 본 발명의 제2 실시 형태에 따른 반도체 발광 소자의 단면도이다.

도 7은 본 발명의 제2 실시 형태에 따른 반도체 발광 소자의 변형예를 나타내는 도면이다.

도 8은 본 발명의 제3 실시 형태에 따른 반도체 발광 소자의 단면도이다.

도 9는 본 발명의 제4 실시 형태에 따른 반도체 발광 소자의 단면도이다.

<도면의 주요부분에 대한 부호의 설명>

10 : 반도체 발광 소자,

12 : 사파이어 기판,

14 : 버퍼층,

16 : n형 GaN층,

18 : InGaN 발광층,

24 : ZnO층,

26 : p측 전극,

28 : n측 전극,

30 : 오목부,

32 : p형 GaN층

(제1 실시 형태)

도 1은 본 발명의 제1 실시 형태에 따른 반도체 발광 소자의 단면도이다. 도 1에 나타내는 바와 같이, 반도체 발광 소자(10)는 컨택트층인 n형 GaN층(16)과 InGaN 발광층(18)과 클래드층인 p형 AlGaN층(20)과 컨택트층인 p형 GaN(22)로 구성되는 p형 GaN층(32)이 적층된 더블 헤테로 구조의 GaN계 반도체 발광 소자이다. 제1 실시 형태에 따른 반도체 발광 소자(10)의 발광 관측면은 투명 전극인 ZnO층(24)측이다. 한편, 각 도면은 각층 등의 위치 관계를 설명하는 것을 목적으로 하고 있기 때문에, 반드시 실제의 치수 관계를 나타내는 것은 아니다. 또한, 각 실시 형태에 있어서, 동일 또는 대응하는 구성 요소에는 동일한 부호를 부여함과 함께 중복하는 설명은 적절히 생략한다.

반도체 발광 소자(10)는 사파이어 기판(12) 상에 GaN계 반도체를 에피택셜 성장시킴으로써 형성된다.

사파이어 기판(12) 상에는 버퍼층(14)이 설치된다. 버퍼층(14)은 PLD(Pulsed Laser Deposition)법을 이용하여 550℃ 정도의 저온에서 형성된 AlGaN의 비정질층이다. 버퍼층(14)의 두께는 10~20㎚ 정도로 한다. 버퍼층(14)은 사파이어 기판(12) 상에 결정성이 좋은 GaN막을 성장시키기 위한 토대로, 사파이어 기판(12)과의 격자 부정에 의한 격자 결함의 증가를 막는 완충층으로서의 기능을 가진다. 또한, 버퍼층(14)은 결정성의 버퍼층이라도 좋다. 이 경우에는 800~1000℃ 정도에서 AlGaN을 결정 성장시킨다. 결정성의 버퍼층으로 한 경우의 두께는, 특별히 제한은 없지만 10㎚~100㎚ 정도이면 충분하다.

버퍼층(14) 상에는 MOCVD법을 이용하여 Si가 도프된 n형 GaN층(16)이 설치된다. n형 GaN층(16)은 컨택트층으로서 기능한다. 도펀트는 Ge라도 좋다. n형 GaN층(16) 형성 시의 사파이어 기판(12)의 온도는 1000~1200℃ 정도로 유지한다. n형 GaN층(16)이 얇은 경우, n형 GaN층(16)의 시트 저항이 높아지고, 동작 전압의 증가를 초래하므로 n형 GaN층(16)의 두께는 3~10㎛정도로 하는 것이 바람직하다. 이 n형 GaN층(16)은 n형 클래드층으로서의 기능도 갖는다.

n형 GaN층(16) 상에는 MOCVD법을 이용하여 InGaN 발광층(18)이 설치된다. InGaN 발광층(18) 형성 시의 사파이어 기판(12)의 온도는 700~1000℃ 정도로 유지한다. InGaN 발광층(18)은 InGaN층과 GaN층 혹은 발광하는 InGaN층보다 In 조성비가 작은 InGaN층이 교대로 적층된 다중 양자 우물(MQW:Multiple Quantum Well) 구조를 가진다. 우물수는 5~10 정도로 좋다. InGaN층의 두께는 1~10㎚ 정도, InGaN층은 3~30㎚정도로 한다. 예를 들어, InGaN층을 3㎚, GaN층을 10㎚로 한다. InGaN층의 In 조성비를 증가시키면 밴드 갭 에너지가 작아지고 발광 피크 파장은 길어진다. 따라서, 반도체 발광 소자(10)의 발광 파장을, InGaN층의 In 조성비 혹은 두께를 바꿈으로써 제어할 수 있다.

InGaN 발광층(18) 상에는 MOCVD법을 이용하여 언도프 GaN층(도시하지 않음)을 설치해도 좋다. 언도프 GaN층의 두께는 10~100㎚ 정도로 한다. 이 언도프 GaN층은 보호층으로서 기능하고, 결정 성장 프로세스 중에 InGaN 발광층(18)이 고온이 되는 것에 기인하여 InGaN 발광층(18)의 결정이 열화하는 것을 방지하는 기능을 가진다.

InGaN 발광층(18) 상에는 Mg가 도프된 p형 AlGaN층(20)이 설치된다. p형 AlGaN층(20)은 p형 GaN층이어도 좋다. p형 AlGaN층(20)은 클래드층으로서 기능한다. p형 AlGaN층(20) 형성 시의 사파이어 기판(12)의 온도는 1000~1200℃ 정도로 유지한다. p형 AlGaN층(20)의 두께는 0.1~0.3㎛, 예를 들어 0.15㎛ 정도로 한다.

p형 AlGaN층(20) 상에는 Mg가 도프된 p형 GaN층(22)이 설치된다. p형 GaN층(22)은 컨택트층으로서 기능한다. p형 GaN층(22) 형성 시의 사파이어 기판(12)의 온도는 700~1000℃ 정도로 유지한다. p형 GaN층(22)의 두께는 20㎚~0.2㎛ 정도로 한다.

p형 GaN층(22) 상에는 PLD법을 이용하여 Ga가 도프된 ZnO층(24)이 설치된다. ZnO층(24)은 졸·겔법이나 열CVD법 등을 이용하여 형성해도 좋다. ZnO층(24)의 두께는 1~2㎛ 정도로 한다. ZnO층(24)은 GaN계 반도체 발광 소자의 발광 파장대에 대해서 투과율이 높고 투명 전극으로서 기능한다. ZnO층(24)은 MgxZn1-xO층(0≤x≤0.5)이라도 좋다.

투명 전극으로서는, 그 밖에도 ITO(Indium Tin Oxide)가 널리 알려져 있지만, ITO를 스퍼터법 등에 의해 형성한 경우, ITO에 포함되는 Sn이 p형 GaN층(22)에 대해서 n형의 도펀트가 되고, p형 GaN층(22)의 표면이 n형화되는 결과, 반도체 발광 소자의 순방향 전압이 상승된다는 문제가 있다. 제1 실시 형태에서 이용하고 있는 ZnO층(24)은, Zn이 p형 GaN층(22)에 대해서 p형의 도펀트가 되므로, 이러한 문제는 생기지 않는다. 이에 더하여, GaN과 ZnO의 결정은 동일한 우르차이트 구조 를 취하기 때문에, 양호한 계면을 얻기 쉽다.

ZnO층(24)의 표면에는 2차원의 주기적인 간격으로 복수의 오목부(30)가 형성된다. ZnO층(24)의 표면이란 p형 GaN층(22)과 ZnO층(24)이 접하고 있는 면과 대향하는 면을 나타낸다. 도 2는 오목부(30)의 배치예를 나타내는 도면이다. 도 3은, 오목부(30)의 다른 배치예를 나타내는 도면이다. 오목부(30)는 도 2에 나타내는 바와 같이, 정방 격자형상으로 배치되어 형성되어도 좋다. 정방 격자형상으로 배치한 경우, 2차원의 주기적인 간격으로 오목부(30)를 형성할 수 있다. 또한, 오목부(30)는, 도 3에 나타내는 바와 같이, 삼각 격자형상으로 배치되어 형성되어도 좋다. 삼각 격자형상으로 배치한 경우에는, 2차원의 주기적인 간격으로 형성하는 오목부(30)의 밀도를 높게 할 수 있어 매우 적합하게 광 취출 효율을 향상시킬 수 있다.

오목부(30)의 평면에서 본 형상은 예를 들어 도 2 또는 도 3에 나타내는 바와 같이 원형으로 좋고, 또한 사각형이나 육각형이어도 좋다. 그 직경이나 1변의 길이는 100㎚ 정도로 좋다. 오목부(30)의 깊이는 500㎚ 정도로 좋다. 오목부(30)의 매우 적합한 주기 간격에 대해서는 후술한다.

이 오목부(30)는 ZnO층(24) 상에 레지스트를 형성한 후에, 전자빔 노광법이나, 나노 임프린트법 등의 방법에 의해 레지스트를 원하는 형상으로 패터닝하고, 레지스트를 마스크로 하여 RIE법 등의 건식 에칭을 행함으로써 형성한다.

그 후, ZnO층(24), p형 GaN층(22), p형 AlGaN층(20), InGaN 발광층(18) 및 n형 GaN층(16)의 일부의 영역을 에칭에 의해 제거한다. n형 GaN층(16)의 도중까지 에칭하고, 노출한 n형 GaN층(16)의 상면에 n측 전극(28)을 형성한다. n측 전극(28)은 오믹 컨택트이며, 접촉 비저항이 작고 열적으로 안정되는 것이 바람직하고, Al 또는 Ti/Al를 매우 적합하게 이용할 수 있다. 오믹 컨택트로 하기 위해서, n측 전극(28)을 형성한 후에 600℃ 정도로 신터를 행하는 것이 바람직하다. n측 전극(28)의 두께는 2500Å 정도로 좋다.

마지막으로, ZnO층(24) 상의 오목부가 설치되어 있지 않은 일부의 영역에 p측 전극(26)을 형성한다. p측 전극(26)은, 오믹 컨택트를 실현하기 위해서 Al, Ti, Ag등을 이용할 수 있다. p측 전극(26)의 두께는 Pt가 1000Å 정도, Au가 3000Å 정도로 좋다. p측 전극(26) 및 n측 전극(28)은 증착법이나 스퍼터법을 이용하여 형성할 수 있다.

도 4는, 반도체 발광 소자의 전류-휘도 특성을 나타내는 도면이다. 도 4의 횡축은, 반도체 발광 소자(10)의 순방향 전류를 나타내고, 세로축은 휘도를 나타낸다. 곡선(34)은 ZnO층(24)의 표면에 오목부(30)를 형성하지 않은 경우의 전류-휘도 특성을 나타내고, 곡선(36)은 ZnO층(24)의 표면에 오목부(30)를 형성한 경우의 전류-휘도 특성을 나타낸다. 도 4에 나타내는 바와 같이, ZnO층(24)의 표면에 오목부(30)를 형성함으로써 휘도가 향상되고 있다. 이것은 반도체 발광 소자(10)의 광 취출 효율이 향상되어 있는 것을 의미한다.

제1 실시 형태에 따른 반도체 발광 소자(10)는 ZnO층(24)의 표면에 2차원의 주기적인 간격으로 오목부가 형성되어 있기 때문에, InGaN 발광층(18)으로부터의 광이 회절된다. 회절 광 중 ZnO층(24)과 공기와의 계면에서의 전반사각 θz보다 작은 각도로 계면에 입사한 회절 광은, 전반사되지 않고 반도체 발광 소자(10)의 외부에 취출되기 때문에 광 취출 효율을 향상시킬 수 있다.

제1 실시 형태에 따른 반도체 발광 소자(10)에서는, p형 GaN층(22)이 아니라, ZnO층(24)에 오목부를 형성하고 있기 때문에, 건식 에칭 시의 플라즈마 손상에 의한 p형 GaN층(22) 표면의 n형화는 일어나지 않기 때문에, 순방향 전압을 상승시키지 않고 매우 적합하게 광 취출 효율을 향상시킬 수 있다.

도 5는, 오목부(30)의 주기 간격을 설명하기 위한 도면이다. 오목부(30)의 주기 간격이란, 2차원의 면 내에 있어서 세로 또는 가로 방향으로 인접하는 오목부의 중심간의 간격을 말한다. 주기 간격을 Lz로, InGaN 발광층(18)으로부터의 광의 공기 중에서의 피크 파장을 λ로, 파장 λ에서의 ZnO층(24)의 굴절률을 nzλ로, ZnO층(24)과 공기층과의 계면에 상기 발광층으로부터의 광이 입사할 때의 전반사각을 θz로 한다. 전반사각 θz는 θz=sin-1(1/nz λ)이 되므로, 예를 들어 파장 λ=450㎚ 일 때의 ZnO의 굴절률 nz λ를 2.3으로, 공기의 굴절률을 1.0으로 하면, 전반사각 θz는 약 25.8°이다.

도 5에 있어서, ZnO층(24)을 가로 방향으로 도파하는 광(48)으로부터, ZnO층(24)의 법선 방향에 대해서 θm의 방향으로 회절되는 회절 광(50)과 회절 광(52)이 서로 강화되는 조건은,

로 나타낼 수 있다. m은 정수이며 회절 광의 차수를 의미한다. (1)식에 있어서, 좌변은 회절 광(50)과 회절 광(52)의 위상차를 나타내고 있다. 위상차가 2π의 정수배일 때, 회절 광(50)과 회절 광(52)은 서로 강화된다. (1) 식을 Lz에 대해 변형하면,

와 같이 나타낼 수 있다.

회절 광(50)과 회절 광(52)이 서로 강화되는 각도 θm가 전반사각 θz보다 작을 때, 즉 θm가 0≤θm≤θz의 범위에 있을 때, 서로 강화되는 회절 광(50)과 회절 광(52)은 ZnO층(24)과 공기와의 계면에서 전반사하지 않고 반도체 발광 소자(10)의 외부에 취출할 수 있다. 즉, 주기 간격 Lz이,

의 범위에 있을 때, 서로 강화되는 회절 광(50)과 회절 광(52)은 반도체 발광 소자(10)의 외부에 방출된다. 실질적으로는 1차의 회절 광의 강도가 가장 강하기 때문에, m=1로서 주기 간격 Lz를 설정해도 좋다. 즉,

를 만족하는 주기 간격 Lz로 설정하는 것이 바람직하다. 예를 들어, 파장 λ=450㎚, ZnO의 굴절률 nzλ=2.3, m=1, θz=25.8°로서 상기의 (4)식을 이용하여 주기 간격 Lz를 계산하면, 196㎚≤Lz≤346㎚가 된다.

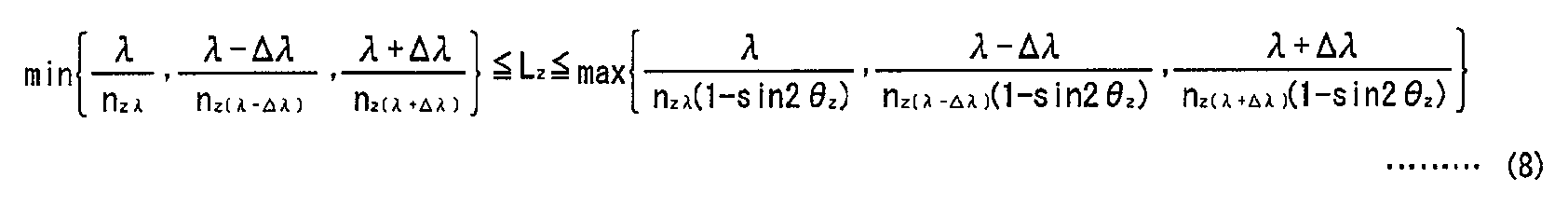

또한, 반도체 발광 소자에서는 반도체 레이저와 다른 발광 스펙트럼이 브로드이므로, 공기 중에서의 반값폭 Δλ을 고려하여 주기 간격 Lz를 설정해도 좋다. 즉, 발광 피크 파장 λ로부터 Δλ만큼 어긋난 파장 λ±Δλ에 맞추어 주기 간격 Lz를 설정해도 발광 효율의 개선 효과를 가진다. 여기서, 반값폭 Δλ이란, 발광 피크 파장 λ로부터 발광 강도가 1/2가 되는 파장까지의 파장폭을 말한다. 반값폭 Δλ을 고려한 경우의 주기 간격 Lz의 범위는,

로 나타낼 수 있다. nz (λ-Δλ)는 파장 λ-Δλ에서의 ZnO층의 굴절률을, nz (λ+Δλ)는 파장 λ+Δλ에서의 ZnO층의 굴절률을 나타낸다. 여기에서도, 실질적으로는 1차의 회절 광의 강도가 가장 강하기 때문에, m=1로서 주기 간격 Lz를 설정해도 좋다. 즉,

을 만족하는 주기 간격 Lz로 설정해도 좋다. 이 경우, 예를 들어, 파장 λ=450㎚, 반값폭 Δλ을 15㎚, θz=25.8°로 하고, 파장 λ에서의 ZnO의 굴절률 nzλ와 파장 λ±Δλ에서의 굴절률 nz(λ±Δλ)가 동일하게 2.3이라고 하면, (6)식으로부터 189㎚≤Lz≤358㎚가 된다.

또한, 상기와 같이, 회절 광(50)과 회절 광(52)이 서로 강화되는 각도 θm가 전반사각 θz보다도 작은 경우에 가장 바람직한 것이지만, 실질적으로는, θm가 θz의 2배보다 작아도 발광 효율의 개선 효과를 갖는다. 즉, θm가 0≤θm≤2θz의 범위라도 좋다. 이 때, 주기 간격 Lz의 범위는,

로 나타낼 수 있다. 여기에서도, 실질적으로는 1차의 회절 광의 강도가 가장 강하기 때문에, m=1로서 주기 간격 Lz를 설정해도 좋다. 즉,

를 만족하는 주기 간격 Lz로 설정해도 좋다. 이 경우, 파장 λ=450㎚, 반값폭 Δλ을 15㎚, θz=25.8°로 하고, 파장 λ에서의 ZnO의 굴절률 nzλ와 파장 λ±Δλ에서의 굴절률 nz(λ±Δλ)가 동일하게 2.3이라고 하면, (8)식으로부터 189㎚≤Lz≤935㎚가 된다.

제1 실시 형태에 있어서는, ZnO층(24)의 표면에 오목부를 형성하는 경우에 대해 설명했지만, 오목부는 아니고 볼록부를 ZnO층(24) 형성해도 동일하게 광 취출 효율의 개선 효과를 가진다. 또한, 상기에 있어서는 반도체 발광 소자(10)가 공기 중에서 발광하고 있는 경우에 대해 설명했지만, 반도체 발광 소자(10)는 형광체나 광 투과성 수지에 덮인 상태라도 좋다. 이 경우는, 전반사각 θz를 구할 때에 공기의 굴절률이 아니라, ZnO층(24)이 접하는 매체인 형광체나 광 투과성 수지의 굴절률을 이용하면, 상기의 (3)~(8)식을 적용할 수 있다.

(제2 실시 형태)

도 6은, 본 발명의 제2 실시 형태에 따른 반도체 발광 소자의 단면도이다. 도 6에 나타내는 바와 같이, 반도체 발광 소자(60)는 컨택트층인 p형 GaN(22)과 클래드층인 p형 AlGaN층(20)으로 구성되는 p형 GaN층(32)과 InGaN 발광층(18)과 컨택트층인 n형 GaN층(16)이 적층된 더블 헤테로 구조의 GaN계 반도체 발광 소자이다. 제2 실시 형태에 따른 반도체 발광 소자(60)의 발광 관측면은 n형 GaN층(16)측이다.

제2 실시 형태에 따른 반도체 발광 소자(60)는, 우선, 사파이어 기판 상에 n형 GaN층(16), InGaN 발광층(18), p형 AlGaN층(20), p형 GaN층(22)을 적층한다. 여기까지는, 제1 실시 형태에 따른 반도체 발광 소자(10)와 동일한 공정이지만, 그 후, 레이저·리프트·오프에 의해서 사파이어 기판 및 버퍼층을 박리한다. 레이저로서는, 파장 248㎚의 KrF 레이저를 이용할 수 있다.

사파이어 기판 및 버퍼층 박리에 의해서 노출한 n형 GaN층(16)의 표면에는 2 차원의 주기적인 간격으로 복수의 오목부(30)가 형성된다. n형 GaN층(16)의 표면이란, InGaN 발광층(18)과 n형 GaN층(16)이 접하고 있는 면과 대향하는 면을 나타낸다. 오목부(30)는 도 2에 나타내는 바와 같이 정방 격자형상으로 배치되어 형성되어도 좋다. 또한, 오목부(30)는 도 3에 나타내는 바와 같이 삼각 격자형상으로 배치되어 형성되어도 좋다.

오목부(30)의 평면에서 본 형상은, 예를 들어 도 2 또는 도 3에 나타내는 바와 같이 원형으로 좋고, 또한 사각형이나 육각형이어도 좋다. 그 직경이나 1변의 길이는 100㎚ 정도로 좋다. 오목부(30)의 깊이는 500㎚ 정도로 좋다.

오목부(30)는 제1 실시의 형태에 따른 반도체 발광 소자(10)와 동일하게, RIE법 등의 건식 에칭을 행함으로써 형성할 수 있다. n형 GaN층(16)을 건식 에칭함으로써도 질소 공공이 발생하고, n형 GaN층(16)의 표면이 n형화되지만, n형 GaN층(16)은 원래 n형이기 때문에 역바이어스가 인가되는 상태로는 되지 않고, 순방향 전압이 상승되는 일은 없다.

오목부(30)를 형성 후, p형 GaN층(22), p형 AlGaN층(20), InGaN 발광층(18) 및 n형 GaN층(16)의 일부의 영역을 에칭에 의해 제거한다. n형 GaN층(16)의 도중까지 에칭하고, 노출된 n형 GaN층(16)의 상면에 n측 전극(28)을 형성한다.

그 후, p형 GaN층(22) 상에 p측 전극(26)을 형성한다. 반도체 발광 소자(60)는, 발광 관측면이 n형 GaN층(16)측이기 때문에, p형 GaN층(22) 상에 ZnO의 투명 전극층은 형성할 필요는 없고, n형 GaN층(16) 상에 직접 p측 전극(26)을 형성한다. p측 전극(26)은 Pt/Au 등을 이용하는 것이 바람직하다. p측 전극(26)의 두께는 Pt가 1000Å 정도, Au가 3000Å 정도로 좋다.

제2 실시 형태에 따른 반도체 발광 소자(60)에 있어서는, n형 GaN층(16)의 표면에 2차원의 주기적인 간격으로 오목부가 형성되어 있기 때문에, InGaN 발광층(18)으로부터의 광이 회절된다. 회절 광 중, n형 GaN층(16)과 공기와의 계면에서의 전반사각 θg보다도 작은 각도로 계면에 입사한 회절 광은, 전반사되지 않고 반도체 발광 소자(60)의 외부에 취출되기 때문에 광 취출 효율을 향상시킬 수 있다.

오목부(30)의 주기 간격 Lg는

를 만족하는 범위에서 설정하는 것이 바람직하다. λ는 InGaN 발광층(18)으로부터의 광의 공기 중에서의 피크 파장을, ngλ는 그 파장 λ에서의 n형 GaN층(16)의 굴절률을 나타낸다.

(9)식을 만족하는 주기 간격 Lg으로 n형 GaN층(16)의 표면에 오목부(30)를 형성함으로써 회절 광을 반도체 발광 소자(60)의 외부에 취출할 수 있고, 광 취출 효율을 향상시킬 수 있다. 예를 들어, 파장 λ=450㎚, n형 GaN층(16)의 굴절률 ng λ=2.5, 전반사각 θg=23.6°로 하여 상기의 (9)식을 이용하여 주기 간격 Lg를 계산 하면, 180㎚≤Lg≤300㎚가 된다.

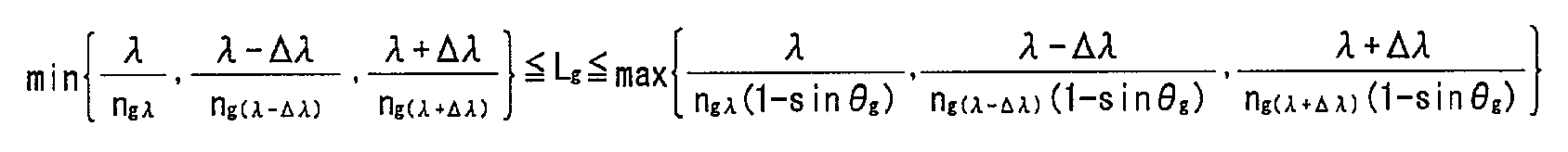

또한, 제1 실시 형태와 동일하게 반도체 발광 소자(60)의 반값폭 Δλ을 고려하여 주기 간격 Lg를 설정해도 광 취출 효율을 향상시킬 수 있다. 즉, 인접하는 오목부(30)의 주기 간격 Lg가,

의 범위에 있어도 좋다. ng (λ-Δλ)는 파장 λ-Δλ에서의 n형 GaN층(16)의 굴절률을, ng (λ+Δλ)는 파장 λ+Δλ에서의 n형 GaN층(16)의 굴절률을 나타낸다.

또한, 제1 실시 형태와 동일하게, 회절 광이 서로 강화되는 각도 θm이 0≤θm≤2θg의 범위라도 광 취출 효율을 향상시킬 수 있다. 즉, 인접하는 오목부(30)의 주기 간격 Lg가,

의 범위라도 좋다.

도 7은, 본 발명의 제2 실시 형태에 따른 반도체 발광 소자의 변형예를 나타내는 도면이다. 도 7에 나타내는 반도체 발광 소자(62)에서는, 사파이어 기판(12) 및 버퍼층(14)은 박리하지 않고, ZnO층(24)측으로부터 n형 GaN층(16)의 도중까지 에칭함으로써 노출한 n형 GaN층(16)의 표면으로서, n측 전극(28)을 형성하는 영역 이외의 장소에 오목부(30)를 형성하고 있다. 또한, 도 7에 있어서는 오목부(30)의 크기를 확대하여 그리고 있기 때문에, 오목부(30)는 1개 밖에 그려져 있지 않지만, 실제로는 복수의 오목부(30)가 형성된다.

InGaN 발광층(18)에서 발광하고, 버퍼층(14)과 사파이어 기판(12)과의 계면에서 반사한 광이 오목부(30)를 형성한 영역에 입사한 경우, 이 광은 오목부(30)에 의해서 회절되므로, 진행 방향이 바뀌어 전반사하지 않고 반도체 발광 소자(62)의 외부에 취출할 수 있다. 반도체 발광 소자(62)에 있어서도, n형 GaN층(16)에 오목부(30)를 형성하고 있기 때문에, n형 GaN층(16)의 표면이 n형화함으로써 순방향 전압이 상승하는 일은 없다.

제2 실시 형태에 있어서는, n형 GaN층(16)의 표면에 오목부를 형성하는 경우에 대해 설명했지만, 오목부는 아니라 볼록부를 n형 GaN층(16)의 표면에 형성해도 동일하게 광 취출 효율의 개선 효과를 가진다. 또한, 상기에 있어서는, 반도체 발광 소자(60 또는 62)가 공기 중에서 발광하고 있는 경우에 대해 설명했지만, 반도체 발광 소자(60 또는 62)는 형광체나 광 투과성 수지에 덮인 상태라도 좋다. 이 경우는, 전반사각 θg을 구할 때에 공기의 굴절률이 아니라 n형 GaN층(16)이 접하는 매체인 형광체나 광 투과성 수지의 굴절률을 이용하면, 상기의 (9)~(11)식을 적용할 수 있다.

(제3 실시 형태)

도 8은, 본 발명의 제3 실시 형태에 따른 반도체 발광 소자의 단면도이다. 도 8에 나타내는 바와 같이, 반도체 발광 소자(70)는 SiC 기판(40) 상에 컨택트층인 n형 GaN층(16)과 InGaN 발광층(18)과 클래드층인 p형 AlGaN층(20)과 컨택트층인 p형 GaN(22)으로 구성되는 p형 GaN층(32)이 적층된 더블 헤테로 구조의 GaN계 반도체 발광 소자이다. 반도체 발광 소자(70)의 발광 관측면은 ZnO층(24)측 또는 SiC 기판(40)측이다. ZnO층(24)측을 발광 관측면으로 하는 경우에는, 반도체 발광 소자(70)를 사용할 때에, SiC 기판(40)과 실장 기판 사이에 예를 들어 은(Ag)으로 이루어지는 반사판(도시하지 않음)을 설치하면 좋다. 반사판을 설치함으로써 SiC 기판(40)측으로부터 방출된 광을 발광 관측면인 ZnO층(24)측으로 반사시킬 수 있다.

제3 실시 형태에 따른 반도체 발광 소자(70)는, SiC 기판(40) 상에 GaN계 반도체를 에피택셜 성장시킴으로써 형성하고, 그 후, SiC 기판(40)의 표면에 오목부(30)를 형성하고 있다. ZnO층(24) 상에는 투명 전극으로서 기능하는 ZnO층(24)을 구비하지만, ZnO층(24)에 오목부는 형성하고 있지 않다.

SiC는 사파이어와 달리 도전성이기 때문에, 제1 또는 제2 실시 형태와 같이 p형 GaN층이나 InGaN 발광층 등을 에칭하여 n형 GaN층(16)에 접속하는 n측 전극을 형성하는 공정은 불필요하고, 제조 공정의 간이화와 신뢰성의 향상을 도모할 수 있다.

SiC 기판(40)의 표면에는 2차원의 주기적인 간격으로 복수의 오목부(30)가 형성된다. SiC 기판(40)의 표면이란 n형 GaN층(16)과 SiC 기판(40)이 접하고 있는 면과 대향하는 면을 나타낸다. 오목부(30)는, 도 2에 나타내는 바와 같이, 정방 격자형상으로 배치되어 형성되어도 좋다. 또한, 오목부(30)는 도 3에 나타내는 바와 같이 삼각 격자형상으로 배치되어 형성되어도 좋다.

오목부(30)의 평면에서 본 형상은, 예를 들어 도 2 또는 도 3에 나타내는 바와 같이 원형으로 좋고, 또한 사각형이나 육각형이어도 좋다. 그 직경이나 1변의 길이는 100㎚ 정도로 좋다. 오목부(30)의 깊이는 500㎚ 정도로 좋다.

오목부(30)는 제1 실시의 형태에 따른 반도체 발광 소자(10)와 동일하게, RIE법 등의 건식 에칭을 행함으로써 형성할 수 있다. SiC 기판(40)을 건식 에칭해도, 플라즈마 손상에 의한 순방향 전압의 상승이라는 문제는 발생하지 않는다.

SiC 기판(40) 상의 오목부(30)가 형성되어 있지 않은 일부의 영역에는, n측 전극(28)이 설치된다. n측 전극(28)은 SiC 기판(40)의 표면 중앙 부근에 형성하는 것이 바람직하다. n측 전극(28)은 반사층으로서 기능하고, Ni, Ti, Ni/Ti/Au, 또는 NiTi 합금 등을 이용할 수 있다. n측 전극(28)의 두께는 2500Å 정도로 좋다.

ZnO층(24) 상의 일부의 영역에는 p측 전극(26)이 형성된다. 기판으로서 SiC 기판(40)을 이용한 경우는, p측 전극(26)을 ZnO층(24)의 표면 중앙 부근에 형성하 는 것이 바람직하다. p측 전극(26)은 Pt/Au 등을 이용하는 것이 바람직하다. p측 전극(26)의 두께는 Pt가 1000Å 정도, Au가 3000Å 정도로 좋다.

제3 실시 형태에 따른 반도체 발광 소자(70)에 있어서는, SiC 기판(40)의 표면에 2차원의 주기적인 간격으로 오목부가 형성되어 있기 때문에, InGaN 발광층(18)으로부터 SiC 기판(40) 방향으로 방출된 광이 SiC 기판(40)과 공기와의 계면에서 회절된다. SiC 기판(40)의 법선에 대해서 전반사각 θs보다도 작은 각도 방향으로 회절된 광은, SiC 기판(40)과 공기와의 계면에서 전반사되지 않고 반도체 발광 소자(70)의 외부에 취출할 수 있어 광 취출 효율을 향상시킬 수 있다.

오목부(30)의 주기 간격 Ls는,

을 만족하는 범위에서 설정하는 것이 바람직하다. λ은 InGaN 발광층(18)으로부터의 광의 공기 중에서의 피크 파장을, nsλ는 그 파장 λ에서의 SiC 기판(40)의 굴절률을, θs는 SiC 기판과 공기와의 계면에서의 전반사각을 나타낸다.

(12)식을 만족하는 주기 간격 Ls에서 오목부(30)를 형성함으로써 회절 광을 반도체 발광 소자(70)의 외부에 취출할 수 있고, 광 취출 효율을 향상시킬 수 있다. 예를 들어, 파장 λ=450㎚, SiC 기판(40)의 굴절률 nsλ=2.65, θs=22.2°로 하 여 상기의 (12)식을 이용하여 주기 간격 Ls를 계산하면, 170㎚≤Ls≤273㎚가 된다.

또한, 반도체 발광 소자(70)의 반값폭 Δλ을 고려하여 주기 간격 Ls를 설정해도 광 취출 효율을 향상시킬 수 있다. 즉, 인접하는 오목부(30)의 주기 간격 Ls가,

의 범위에 있어도 좋다. ns(λ-Δλ)는 파장 λ-Δλ에서의 SiC 기판(40)의 굴절률을, ns(λ+Δλ)는 파장 λ+Δλ에서의 SiC 기판(40)의 굴절률을 나타낸다.

또한, 회절 광이 서로 강화되는 각도 θm가, 0≤θm≤2θs의 범위라도 광 취출 효율을 향상시킬 수 있다. 즉, 인접하는 오목부(30)의 주기 간격 Ls가,

의 범위에 있어도 좋다.

제3 실시 형태에 있어서는, SiC 기판(40)의 표면에 오목부를 형성하는 경우 에 대해 설명했지만, 오목부는 아니고 볼록부를 SiC 기판(40)의 표면에 형성해도 동일하게 광 취출 효율의 개선 효과를 갖는다. 또한, 상기에 있어서는, 반도체 발광 소자(70)가 공기 중에서 발광하고 있는 경우에 대해 설명했지만, 반도체 발광 소자(70)는 형광체나, 광 투과성 수지에 덮인 상태라도 좋다. 이 경우는, 공기가 아니라 SiC 기판(40)이 접하는 매체인 형광체나 광 투과성 수지의 굴절률을 이용하면, 상기의 (12)~(14)식을 적용할 수 있다.

(제4 실시 형태)

도 9는, 본 발명의 제4 실시 형태에 따른 반도체 발광 소자의 단면도이다. 도 9에 나타내는 바와 같이, 반도체 발광 소자(80)는 SiC 기판(40) 상에 컨택트층인 n형 GaN층(16)과 InGaN 발광층(18)과 클래드층인 p형 AlGaN층(20)과 컨택트층인 p형 GaN(22)으로 구성되는 p형 GaN층(32)이 적층된 더블 헤테로 구조의 GaN계 반도체 발광 소자이다. 제4 실시 형태에 따른 반도체 발광 소자(80)의 발광 관측면은 ZnO층(24)측 또는 SiC 기판(40)측이다. 제3 실시 형태와 동일하게, 실장할 때에는 반사판을 설치해도 좋다.

제4 실시 형태에 따른 반도체 발광 소자(80)는, p형 GaN층(22) 상에 설치된 ZnO층(24)의 표면에 오목부(38)를 형성하는 점이, 제3 실시 형태에 따른 반도체 발광 소자(70)와 상이하다. SiC 기판(40)의 표면에는 제3 실시 형태와 동일하게 오목부(30)가 형성된다.

ZnO층(24)의 표면에는 2차원의 주기적인 간격으로 복수의 오목부(38)가 형성된다. ZnO층(24)의 표면이란, ZnO층(24)과 p형 GaN층(22)이 접하고 있는 면과 대 향하는 면을 나타낸다. 오목부(38)의 배치, 형상 등은 제1 실시 형태에 따른 반도체 발광 소자(10)와 동일하고, 주기 간격 Lz은 (3)~(8)식을 적용하여 설정할 수 있다. 단, 기판으로서 SiC 기판(40)을 이용한 경우에는, p측 전극(26)을 ZnO층(24)의 표면 중앙 부근에 형성하는 것이 바람직하다.

제4 실시 형태에 따른 반도체 발광 소자(80)에서는, ZnO층(24)의 표면에 2차원의 주기적인 간격으로 오목부(38)가 형성되고 있기 때문에, InGaN 발광층(18)으로부터 ZnO층(24) 방향으로 방출된 광이 회절된다. 회절 광 중 ZnO층(24)과 공기와의 계면에서의 전반사각 θz보다도 작은 각도로 계면에 입사한 회절 광은, 전반사 되지 않고 반도체 발광 소자(80)의 외부에 취출할 수 있다. 또한, SiC 기판(40)의 표면에 형성한 오목부(30)의 효과는, 제3 실시 형태에 따른 반도체 발광 소자(70)의 경우와 동일하다.

제4 실시 형태에 따른 반도체 발광 소자(80)에 있어서도, 제1 실시 형태와 동일하게 p형 GaN층(22)이 아니라 ZnO층(24)에 오목부를 형성하고 있기 때문에, 건식 에칭 시의 플라즈마 손상에 의한 p형 GaN층(22) 표면의 n형화는 일어나지 않기 때문에 순방향 전압은 상승하지 않는다. 또한, 제3 실시 형태와 동일하게, SiC 기판(40)을 건식 에칭해도, 플라즈마 손상에 의한 순방향 전압의 상승은 일어나지 않는다.

이상, 본 발명을 실시의 형태를 기초로 설명하였다. 이 실시의 형태는 예시이며, 그러한 각 구성 요소나 각 처리 프로세스의 조합에 여러 가지 변형예가 가능 한 것, 또한 그러한 변형예도 본 발명의 범위에 있는 것은 당업자에게 이해되는 바이다.

본 발명은, 휴대 전화 등에 이용되는 반도체 발광 소자에 이용할 수 있다.

Claims (20)

- 기판 상에 n형 GaN층과 발광층과 p형 GaN층이 적층된 반도체 발광 소자로서,상기 p형 GaN층 상에 MgxZn1-xO층(0≤x≤0.5)이 설치되고,상기 MgxZn1-xO층(0≤x≤0.5)의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성되는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 1에 있어서, 상기 발광층으로부터의 광의 공기 중에서의 파장을 λ로, 그 파장 λ에서의 상기 MgxZn1-xO층(0≤x≤0.5)의 굴절률을 nzλ로, 상기 발광층 으로부터의 광의 공기 중에서의 반값폭을 Δλ로, 파장 λ-Δλ에서의 상기 MgxZn1 -xO층(0≤x≤0.5)의 굴절률을 nz (λ-Δλ)로, 파장 λ+Δλ에서의 상기 MgxZn1 - xO층(0≤x≤0.5)의 굴절률을 nz (λ+Δλ)로, 상기 MgxZn1 - xO층(0≤x≤0.5)과 거기에 접하는 매체와의 계면에서의 전반사각을 θz로 했을 때에, 인접하는 오목부의 주기 간격 또는 인접하는 볼록부의 주기 간격 Lz가,[수학식 2]의 범위에 있는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 1에 있어서, 상기 발광층으로부터의 광의 공기 중에서의 파장을 λ로, 그 파장 λ에서의 상기 MgxZn1-xO층(0≤x≤0.5)의 굴절률을 nzλ로, 상기 발광층으로부터의 광의 공기 중에서의 반값폭을 Δλ로, 파장 λ-Δλ에서의 상기 MgxZn1-xO층(0≤x≤0.5)의 굴절률을 nz(λ-Δλ)로, 파장 λ+Δλ에서의 상기 MgxZn1-xO층(0≤x≤0.5)의 굴절률을 nz (λ+Δλ)로, 상기 MgxZn1 - xO층(0≤x≤0.5)과 거기에 접하는 매체와의 계면에서의 전반사각을 θz로 했을 때에, 인접하는 오목부의 주기 간격 또는 인접하는 볼록부의 주기 간격 Lz가,[수학식 3]의 범위에 있는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 1 내지 청구항 4 중 어느 한 항에 있어서,상기 MgxZn1-xO층(0≤x≤0.5)에 형성되는 오목부 또는 볼록부는 정방 격자형상 또는 삼각 격자형상으로 배치되는 것을 특징으로 하는 반도체 발광 소자.

- p형 GaN층과 발광층과 n형 GaN층이 적층된 반도체 발광 소자로서,상기 n형 GaN층의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성되는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 6에 있어서, 상기 발광층으로부터의 광의 공기 중에서의 파장을 λ로, 그 파장 λ에서의 상기 n형 GaN층의 굴절률을 ngλ로, 상기 발광층으로부터의 광의 공기 중에서의 반값폭을 Δλ로, 파장 λ-Δλ에서의 상기 n형 GaN층의 굴절률을 ng(λ-Δλ)로, 파장 λ+Δλ에서의 상기 n형 GaN층의 굴절률을 ng(λ+Δλ)로, 상기 n형 GaN층과 거기에 접하는 매체와의 계면에서의 전반사각을 θg로 했을 때에, 인접하는 오목부의 주기 간격 또는 인접하는 볼록부의 주기 간격 Lg가,[수학식 5]의 범위에 있는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 6에 있어서, 상기 발광층으로부터의 광의 공기 중에서의 파장을 λ로, 그 파장 λ에서의 상기 n형 GaN층의 굴절률을 ngλ로, 상기 발광층으로부터의 광의 공기 중에서의 반값폭을 Δλ로, 파장 λ-Δλ에서의 상기 n형 GaN층의 굴절률을 ng (λ-Δλ)로, 파장 λ+Δλ에서의 상기 n형 GaN층의 굴절률을 ng (λ+Δλ)로, 상기 n형 GaN층과 거기에 접하는 매체와의 계면에서의 전반사각을 θg로 했을 때에, 인접하는 오목부의 주기 간격 또는 인접하는 볼록부의 주기 간격 Lg가,[수학식 6]의 범위에 있는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 6 내지 청구항 9 중 어느 한 항에 있어서, 상기 n형 GaN층에 형성되는 오목부 또는 볼록부는 정방 격자형상 또는 삼각 격자형상으로 배치되는 것을 특징으로 하는 반도체 발광 소자.

- 기판 상에 n형 GaN층과 발광층과 p형 GaN층이 적층된 반도체 발광 소자로서,상기 기판은 SiC 기판이며,상기 SiC 기판의 표면에, 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성되는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 11에 있어서, 상기 발광층으로부터의 광의 공기 중에서의 파장을 λ로, 그 파장 λ에서의 상기 SiC 기판의 굴절률을 nsλ로, 상기 발광층으로부터의 광의 공기 중에서의 반값폭을 Δλ로, 파장 λ-Δλ에서의 상기 SiC 기판의 굴절률을 ns(λ-Δλ)로, 파장 λ+Δλ에서의 상기 SiC 기판의 굴절률을 ns (λ+Δλ)로, 상기 SiC 기판과 거기에 접하는 매체와의 계면에서의 전반사각을 θs로 했을 때에 인접하는 오목부의 주기 간격 또는 인접하는 볼록부의 주기 간격 Ls가,[수학식 8]의 범위에 있는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 11에 있어서, 상기 발광층으로부터의 광의 공기 중에서의 파장을 λ로, 그 파장 λ에서의 상기 SiC 기판의 굴절률을 ns λ로, 상기 발광층으로부터의 광의 공기 중에서의 반값폭을 Δλ로, 파장 λ-Δλ에서의 상기 SiC 기판의 굴절률을 ns(λ-Δλ)로, 파장 λ+Δλ에서의 상기 SiC 기판의 굴절률을 ns(λ+Δλ)로, 상기 SiC 기판과 거기에 접하는 매체와의 계면에서의 전반사각을 θs로 했을 때에, 인접하는 오목부의 주기 간격 또는 인접하는 볼록부의 주기 간격 Ls가,[수학식 9]의 범위에 있는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 11 내지 청구항 14 중 어느 한 항에 있어서, 상기 SiC 기판에 형성되는 오목부 또는 볼록부는 정방 격자형상 또는 삼각 격자형상으로 배치되는 것을 특 징으로 하는 반도체 발광 소자.

- 청구항 11 내지 청구항 15 중 어느 한 항에 있어서, 상기 p형 GaN층 상에 MgxZn1-xO층(0≤x≤0.5)이 설치되고, 상기 MgxZn1-xO층(0≤x≤0.5)의 표면에 2차원의 주기적인 간격으로 오목부 또는 볼록부가 형성되는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 16에 있어서, 상기 발광층으로부터의 광의 공기 중에서의 파장을 λ로, 그 파장 λ에서의 상기 MgxZn1-xO층(0≤x≤0.5)의 굴절률을 nzλ로, 상기 발광층 으로부터의 광의 공기 중에서의 반값폭을 Δλ로, 파장 λ-Δλ에서의 상기 MgxZn1-xO층(0≤x≤0.5)의 굴절률을 nz(λ-Δλ)로, 파장 λ+Δλ에서의 상기 MgxZn1-xO층(0≤x≤0.5)의 굴절률을 nz(λ+Δλ)로, 상기 MgxZn1-xO층(0≤x≤0.5)과 거기에 접하는 매체와의 계면에서의 전반사각을 θz로 했을 때에, 인접하는 오목부의 주기 간격 또는 인접하는 볼록부의 주기 간격 Lz가,[수학식 11]의 범위에 있는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 16에 있어서, 상기 발광층으로부터의 광의 공기 중에서의 파장을 λ로, 그 파장 λ에서의 상기 MgxZn1 - xO층(0≤x≤0.5)의 굴절률을 nz λ로, 상기 발광층으로부터의 광의 공기 중에서의 반값폭을 Δλ로, 파장 λ-Δλ에서의 상기 MgxZn1-xO층(0≤x≤0.5)의 굴절률을 nz(λ-Δλ)로, 파장 λ+Δλ에서의 상기 MgxZn1-xO층(0≤x≤0.5)의 굴절률을 nz(λ+Δλ)로, 상기 MgxZn1 - xO층(0≤x≤0.5)과 거기에 접하는 매체와의 계면에서의 전반사각을 θz로 했을 때에, 인접하는 오목부의 주기 간격 또는 인접하는 볼록부의 주기 간격 Lz가,[수학식 12]의 범위에 있는 것을 특징으로 하는 반도체 발광 소자.

- 청구항 16 내지 청구항 19 중 어느 한 항에 있어서, 상기 MgxZn1-xO층(0≤x≤0.5)에 형성되는 오목부 또는 볼록부는 정방 격자형상 또는 삼각 격자형상으로 배치되는 것을 특징으로 하는 반도체 발광 소자.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005169056 | 2005-06-09 | ||

| JPJP-P-2005-00169056 | 2005-06-09 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20080014833A true KR20080014833A (ko) | 2008-02-14 |

Family

ID=37498222

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020077028387A KR20080014833A (ko) | 2005-06-09 | 2006-03-03 | 반도체 발광 소자 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US7906791B2 (ko) |

| EP (1) | EP1909335A1 (ko) |

| KR (1) | KR20080014833A (ko) |

| CN (1) | CN101180745A (ko) |

| TW (1) | TW200701522A (ko) |

| WO (1) | WO2006132013A1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9391248B2 (en) | 2010-02-01 | 2016-07-12 | Lg Innotek Co., Ltd | Light emitting device, light emitting device package |

Families Citing this family (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4954549B2 (ja) * | 2005-12-29 | 2012-06-20 | ローム株式会社 | 半導体発光素子およびその製法 |

| DE102007004304A1 (de) * | 2007-01-29 | 2008-07-31 | Osram Opto Semiconductors Gmbh | Dünnfilm-Leuchtdioden-Chip und Verfahren zur Herstellung eines Dünnfilm-Leuchtdioden-Chips |

| KR100926280B1 (ko) | 2007-12-14 | 2009-11-12 | 고려대학교 산학협력단 | 발광 효율 향상을 위한 질화물 발광 소자 및 그 제조 방법 |

| CN101257075B (zh) * | 2008-03-13 | 2010-05-12 | 鹤山丽得电子实业有限公司 | 一种发光二极管器件及其制造方法 |

| CN101281947B (zh) * | 2008-05-20 | 2010-04-14 | 上海大学 | 通过新结构提高出光效率的发光二极管芯片及其制造工艺 |

| US8188496B2 (en) * | 2008-11-06 | 2012-05-29 | Samsung Led Co., Ltd. | Semiconductor light emitting device including substrate having protection layers and method for manufacturing the same |

| CN101494269B (zh) * | 2008-12-18 | 2010-05-12 | 济南大学 | 一种用缓冲层制备氧化锌薄膜的方法 |

| JP4962743B2 (ja) * | 2008-12-19 | 2012-06-27 | セイコーエプソン株式会社 | 発光装置 |

| KR101210172B1 (ko) * | 2009-03-02 | 2012-12-07 | 엘지이노텍 주식회사 | 발광 소자 |

| KR100969160B1 (ko) * | 2009-03-10 | 2010-07-21 | 엘지이노텍 주식회사 | 발광소자 및 그 제조방법 |

| KR100969100B1 (ko) * | 2010-02-12 | 2010-07-09 | 엘지이노텍 주식회사 | 발광소자, 발광소자의 제조방법 및 발광소자 패키지 |

| CN101847677B (zh) * | 2010-04-07 | 2012-11-14 | 中国科学院半导体研究所 | 采用mvpe两步法制备氧化锌透明电极的方法 |

| KR101047739B1 (ko) | 2010-04-28 | 2011-07-07 | 엘지이노텍 주식회사 | 발광소자, 발광소자의 제조방법, 발광소자 패키지 및 조명시스템 |

| WO2011138851A1 (ja) | 2010-05-07 | 2011-11-10 | パナソニック株式会社 | 発光ダイオード |

| CN102255025A (zh) * | 2010-05-18 | 2011-11-23 | 展晶科技(深圳)有限公司 | 发光二极管 |

| JP4928651B2 (ja) * | 2010-08-06 | 2012-05-09 | パナソニック株式会社 | 半導体発光素子 |

| CN102064253A (zh) * | 2010-11-24 | 2011-05-18 | 映瑞光电科技(上海)有限公司 | 发光二极管及其制造方法 |

| US8912080B2 (en) * | 2011-01-12 | 2014-12-16 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of the semiconductor device |

| JP2013120829A (ja) * | 2011-12-07 | 2013-06-17 | Sharp Corp | 窒化物半導体紫外発光素子 |

| CN102623603A (zh) * | 2012-03-31 | 2012-08-01 | 华灿光电股份有限公司 | 半导体发光器件及其制备方法 |

| JP6059501B2 (ja) * | 2012-10-17 | 2017-01-11 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP6307703B2 (ja) | 2013-05-31 | 2018-04-11 | パナソニックIpマネジメント株式会社 | 波長変換素子、波長変換素子を備えた発光装置、発光装置を備えた車両、および波長変換素子の製造方法 |

| WO2015016150A1 (ja) | 2013-07-30 | 2015-02-05 | 独立行政法人情報通信研究機構 | 半導体発光素子およびその製造方法 |

| US10051724B1 (en) | 2014-01-31 | 2018-08-14 | Apple Inc. | Structural ground reference for an electronic component of a computing device |

| US9525222B2 (en) | 2014-04-11 | 2016-12-20 | Apple Inc. | Reducing or eliminating board-to-board connectors |

| US9666967B2 (en) * | 2014-07-28 | 2017-05-30 | Apple Inc. | Printed circuit board connector for non-planar configurations |

| CN104393127B (zh) * | 2014-11-18 | 2017-05-03 | 中国科学院半导体研究所 | 一种倒装结构发光二极管及其制作方法 |

| JP2016134501A (ja) * | 2015-01-20 | 2016-07-25 | スタンレー電気株式会社 | 半導体発光装置 |

| JP2017003697A (ja) * | 2015-06-08 | 2017-01-05 | パナソニックIpマネジメント株式会社 | 発光素子および発光装置 |

| US10727374B2 (en) * | 2015-09-04 | 2020-07-28 | Seoul Semiconductor Co., Ltd. | Transparent conductive structure and formation thereof |

| US10945664B1 (en) | 2015-09-30 | 2021-03-16 | Apple, Inc. | Protective case with coupling gasket for a wearable electronic device |

| JP2017112203A (ja) * | 2015-12-16 | 2017-06-22 | シャープ株式会社 | 半導体発光素子 |

| WO2018083877A1 (ja) * | 2016-11-02 | 2018-05-11 | ソニー株式会社 | 発光素子及びその製造方法 |

| JPWO2023037629A1 (ko) * | 2021-09-13 | 2023-03-16 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5889295A (en) * | 1996-02-26 | 1999-03-30 | Kabushiki Kaisha Toshiba | Semiconductor device |

| TW573372B (en) * | 2002-11-06 | 2004-01-21 | Super Nova Optoelectronics Cor | GaN-based III-V group compound semiconductor light-emitting diode and the manufacturing method thereof |

| US6878969B2 (en) * | 2002-07-29 | 2005-04-12 | Matsushita Electric Works, Ltd. | Light emitting device |

| JP4329374B2 (ja) | 2002-07-29 | 2009-09-09 | パナソニック電工株式会社 | 発光素子およびその製造方法 |

| JP2005005679A (ja) | 2003-04-15 | 2005-01-06 | Matsushita Electric Ind Co Ltd | 半導体発光素子およびその製造方法 |

| US7102175B2 (en) * | 2003-04-15 | 2006-09-05 | Matsushita Electric Industrial Co., Ltd. | Semiconductor light-emitting device and method for fabricating the same |

| JP4311173B2 (ja) * | 2003-11-20 | 2009-08-12 | パナソニック電工株式会社 | 半導体発光素子 |

| JP2006049855A (ja) * | 2004-06-28 | 2006-02-16 | Matsushita Electric Ind Co Ltd | 半導体発光素子およびその製造方法 |

-

2006

- 2006-03-03 EP EP06715185A patent/EP1909335A1/en not_active Withdrawn

- 2006-03-03 US US11/916,868 patent/US7906791B2/en not_active Expired - Fee Related

- 2006-03-03 CN CNA2006800181087A patent/CN101180745A/zh active Pending

- 2006-03-03 KR KR1020077028387A patent/KR20080014833A/ko not_active Application Discontinuation

- 2006-03-03 WO PCT/JP2006/304102 patent/WO2006132013A1/ja active Application Filing

- 2006-03-16 TW TW095108886A patent/TW200701522A/zh unknown

-

2011

- 2011-02-01 US US13/018,634 patent/US20110133208A1/en not_active Abandoned

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9391248B2 (en) | 2010-02-01 | 2016-07-12 | Lg Innotek Co., Ltd | Light emitting device, light emitting device package |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101180745A (zh) | 2008-05-14 |

| WO2006132013A1 (ja) | 2006-12-14 |

| EP1909335A1 (en) | 2008-04-09 |

| US7906791B2 (en) | 2011-03-15 |

| US20110133208A1 (en) | 2011-06-09 |

| TW200701522A (en) | 2007-01-01 |

| US20090267048A1 (en) | 2009-10-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20080014833A (ko) | 반도체 발광 소자 | |

| JP2007019488A (ja) | 半導体発光素子 | |

| KR101341374B1 (ko) | 광자결정 발광소자 및 그 제조방법 | |

| JP5391469B2 (ja) | 窒化物半導体発光素子およびその製造方法 | |

| JP4994758B2 (ja) | 窒化ガリウム系半導体発光素子及びその製造方法 | |

| KR100674862B1 (ko) | 질화물 반도체 발광 소자 | |

| JP2005277423A (ja) | 高効率発光素子 | |

| KR20090012493A (ko) | 광자결정 발광소자 | |

| KR20070088145A (ko) | 발광 다이오드 및 그 제조방법 | |

| KR20120092326A (ko) | 광 결정 구조를 갖는 비극성 발광 다이오드 및 그것을 제조하는 방법 | |

| KR20080087135A (ko) | 질화물 반도체 발광 소자 | |

| JP2005268601A (ja) | 化合物半導体発光素子 | |

| US20100224897A1 (en) | Semiconductor optoelectronic device and method for forming the same | |

| JP5116291B2 (ja) | 発光素子及び照明装置 | |

| JP2004356196A (ja) | 酸化物半導体発光素子 | |

| JP2008159894A (ja) | 発光素子及び照明装置 | |

| KR100721158B1 (ko) | 질화물 반도체 발광소자 및 그 제조방법 | |

| KR101158126B1 (ko) | 질화 갈륨계 발광 다이오드 | |

| KR20110093006A (ko) | 질화물 반도체 발광소자 | |

| JP4853150B2 (ja) | 窒化物半導体発光ダイオード素子 | |

| KR20110041683A (ko) | 반도체 발광소자 및 이를 제조하는 방법 | |

| KR100998013B1 (ko) | 반도체 발광소자 | |

| JP2007250714A (ja) | 発光素子 | |

| KR20110091245A (ko) | 반도체 발광소자 및 그 제조방법 | |

| KR20090103855A (ko) | 질화물계 반도체 발광소자 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |