JP7129397B2 - SiC半導体装置 - Google Patents

SiC半導体装置 Download PDFInfo

- Publication number

- JP7129397B2 JP7129397B2 JP2019221436A JP2019221436A JP7129397B2 JP 7129397 B2 JP7129397 B2 JP 7129397B2 JP 2019221436 A JP2019221436 A JP 2019221436A JP 2019221436 A JP2019221436 A JP 2019221436A JP 7129397 B2 JP7129397 B2 JP 7129397B2

- Authority

- JP

- Japan

- Prior art keywords

- sic semiconductor

- layer

- region

- sic

- main surface

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Dicing (AREA)

- Electrodes Of Semiconductors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Laser Beam Processing (AREA)

Description

特許文献1に係るSiC半導体装置が半導体組立装置に搬入された場合、ピックアップノズルによる吸着がSiC半導体層の傾斜面によって妨げられる虞がある。この場合、ピックアップノズルはSiC半導体装置を適切に保持できないため、ピックアップエラーが発生する。

本発明の一実施形態は、六方晶からなるSiC単結晶を含み、前記SiC単結晶のc面に面し、前記c面に対して傾斜したオフ角を有する素子形成面としての第1主面、前記第1主面の反対側の第2主面、および、前記SiC単結晶のa面に面し、前記第1主面の法線から前記SiC単結晶のc軸とは反対側の方向に向けて傾斜した傾斜部を有する側面を有するSiC半導体層を含む、SiC半導体装置を提供する。

本発明の一実施形態は、SiC半導体基板およびSiCエピタキシャル層を含む積層構造を有し、前記SiCエピタキシャル層からなり、SiC単結晶のc面に対してオフ方向に傾斜したオフ角が導入された素子形成面、および、前記オフ方向の直交方向に延び、前記素子形成面の法線を0°とした時、当該法線に対して前記オフ角未満の角度で傾斜した側面を有するSiC半導体層と、前記側面において前記SiCエピタキシャル層を露出させるように前記SiC半導体基板からなる部分に厚さ方向に間隔を空けて形成され、前記SiC半導体基板とは異なる性質に改質された複数の改質層と、を含む、SiC半導体装置を提供する。

本発明の実施形態では、六方晶からなるSiC(炭化シリコン)単結晶が適用される。六方晶からなるSiC単結晶は、原子配列の周期に応じて、2H(Hexagonal)-SiC単結晶、4H-SiC単結晶および6H-SiC単結晶を含む複数種のポリタイプを有している。本発明の実施形態では、4H-SiC単結晶が適用された例について説明するが、他のポリタイプを本発明から除外するものではない。

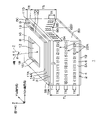

図1および図2を参照して、単位セルは、1つのSi原子に対して4つのC原子が四面体配列(正四面体配列)の関係で結合された四面体構造を含む。単位セルは、四面体構造が4周期積層された原子配列を有している。単位セルは、正六角形のシリコン面、正六角形のカーボン面、ならびに、シリコン面およびカーボン面を接続する6つの側面を有する六角柱構造を有している。

カーボン面は、C原子によって終端された終端面である。カーボン面では、正六角形の6つの頂点に1つのC原子がそれぞれ位置し、正六角形の中心に1つのC原子が位置している。

a1軸、a2軸およびa3軸は、シリコン面をc軸から見た平面視において、中心に位置するSi原子を基準に、最近接するSi原子の配列方向(以下、単に「最近接原子方向」という。)に沿ってそれぞれ設定されている。a1軸、a2軸およびa3軸は、それぞれ、Si原子の配列に倣って120°ずつ角度をずらして設定されている。

六角柱の側面は、シリコン面をc軸から見た平面視において、最近接原子方向に沿う6つの結晶面を含む。六角柱の側面は、より具体的には、シリコン面をc軸から見た平面視において、最近接する2つのSi原子をそれぞれ含む6つの結晶面を含む。

六角柱の対角線に沿う対角面は、シリコン面をc軸から見た平面視において、最近接原子方向に交差する交差方向に沿う6つの結晶面を含む。六角柱の対角面は、より具体的には、シリコン面をc軸から見た平面視において、最近接しない2つのSi原子をそれぞれ含む6つの結晶面を含む。中心に位置するSi原子を基準に見たとき、最近接原子方向の交差方向は、最近接原子方向に直交する直交方向となる。

単位セルの結晶方向は、結晶面の法線方向によって定義される。(1-100)面の法線方向は[1-100]方向である。(0-110)面の法線方向は[0-110]方向である。(-1010)面の法線方向は[-1010]方向である。(-1100)面の法線方向は[-1100]方向である。(01-10)面の法線方向は[01-10]方向である。(10-10)面の法線方向は[10-10]方向である。

また、[1-100]方向、[0-110]方向、[-1010]方向、[-1100]方向、[01-10]方向および[10-10]方向は、等価な結晶方向を形成している。また、[11-20]方向、[1-210]方向、[-2110]方向、[-1-120]方向、[-12-10]方向および[2-1-10]方向は、等価な結晶方向を形成している。

(0001)面および(000-1)面は、c面と総称される。[0001]方向および[000-1]方向は、c軸方向と総称される。(11-20)面および(-1-120)面は、a面と総称される。[11-20]方向および[-1-120]方向は、a軸方向と総称される。(1-100)面および(-1100)面は、m面と総称される。[1-100]方向および[-1100]方向は、m軸方向と総称される。

図5は、図3に示す領域Vの拡大図である。図6は、図3に示す領域VIの拡大図である。図7は、図3に示すSiC半導体装置1の平面図である。図8は、図7に示すVIII-VIII線に沿う断面図である。

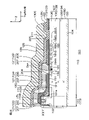

SiC半導体層2は、一方側の第1主面3、他方側の第2主面4、ならびに、第1主面3および第2主面4を接続する側面5A,5B,5C,5Dを有している。第1主面3および第2主面4は、それらの法線方向Zから見た平面視(以下、単に「平面視」という。)において四角形状(この形態では正方形状)に形成されている。

SiC半導体層2の厚さTLは、40μm以上200μm以下であってもよい。厚さTLは、40μm以上60μm以下、60μm以上80μm以下、80μm以上100μm以下、100μm以上120μm以下、120μm以上140μm以下、140μm以上160μm以下、160μm以上180μm以下または180μm以上200μm以下であってもよい。厚さTLは、60μm以上150μm以下であることが好ましい。

第1主面3および第2主面4は、SiC単結晶のc面に対して[11-20]方向(オフ方向)に10°以下の角度で傾斜したオフ角θを有している。法線方向Zは、SiC単結晶のc軸([0001]方向)に対してオフ角θ分だけ傾斜している。

オフ角θは、1.5°以上3.0°以下の角度の範囲に設定されていてもよい。この場合、オフ角θは、1.5°以上2.0°以下または2.0°以上2.5°以下の角度の範囲に設定されていることが好ましい。

側面5Aおよび側面5Cは、この形態では、第1方向Xに沿って延び、第1方向Xに交差する第2方向Yに互いに対向している。側面5Bおよび側面5Dは、この形態では、第2方向Yに沿って延び、第1方向Xに互いに対向している。第2方向Yは、より具体的には第1方向Xに直交する方向である。

側面5Aおよび側面5Cは、SiC単結晶のa面によって形成され、a軸方向に互いに対向している。側面5Aは、SiC単結晶の(-1-120)面によって形成されている。側面5Cは、SiC単結晶の(11-20)面によって形成されている。

側面5Aおよび側面5Cは、SiC半導体層2の第1主面3の法線を0°としたとき、SiC半導体層2の第1主面3の法線に対してオフ角θ未満の角度θa(θa<θ)を有している。

一方、側面5Bおよび側面5Dは、SiC半導体層2の第1主面3の法線に沿って平面的に延びている。側面5Bおよび側面5Dは、より具体的には、第1主面3および第2主面4に対して略垂直に形成されている。

SiCエピタキシャル層7によって、SiC半導体層2の第1主面3が形成されている。SiC半導体基板6およびSiCエピタキシャル層7によって、SiC半導体層2の側面5A~5Dが形成されている。

アクティブ領域8は、平面視においてSiC半導体層2の側面5A~5Dから内方領域に間隔を空けてSiC半導体層2の中央部に設定されている。アクティブ領域8は、平面視においてSiC半導体層2の側面5A~5Dに平行な4辺を有する四角形状に設定されている。

SiC半導体層2の第1主面3の上には、主面絶縁層10が形成されている。主面絶縁層10は、アクティブ領域8および外側領域9を選択的に被覆している。主面絶縁層10は、酸化シリコン(SiO2)層または窒化シリコン(SiN)層からなる単層構造を有していてもよい。

主面絶縁層10は、SiC半導体層2の側面5A~5Dから露出する絶縁側面11A,11B,11C,11Dを有している。絶縁側面11A~11Dは、側面5A~5Dに連なっている。絶縁側面11A~11Dは、側面5A~5Dに対して面一に形成されている。絶縁側面11A~11Dは、劈開面からなる。

主面絶縁層10の上には、第1主面電極層12が形成されている。第1主面電極層12は、平面視においてSiC半導体層2の側面5A~5Dから内方領域に間隔を空けてSiC半導体層2の中央部に形成されている。

パッシベーション層13は、酸化シリコン層および窒化シリコン層を含む積層構造を有していてもよい。酸化シリコン層は、窒化シリコン層の上に形成されていてもよい。窒化シリコン層は、酸化シリコン層の上に形成されていてもよい。パッシベーション層13は、この形態では、窒化シリコン層からなる単層構造を有している。

パッシベーション層13には、第1主面電極層12の一部をパッド領域として露出させるサブパッド開口15が形成されている。サブパッド開口15は、平面視においてSiC半導体層2の側面5A~5Dに平行な4辺を有する四角形状に形成されている。

パッシベーション層13の上には、樹脂層16(絶縁層)が形成されている。パッシベーション層13および樹脂層16は、1つの絶縁積層構造(絶縁層)を形成している。図7では、樹脂層16がハッチングによって示されている。

樹脂層16の樹脂側面17A,17B,17C,17Dは、平面視においてSiC半導体層2の側面5A~5Dから内方領域に間隔を空けて形成されている。樹脂層16は、平面視においてSiC半導体層2の第1主面3の周縁部を露出させている。樹脂層16は、パッシベーション層13と共に主面絶縁層10を露出させている。樹脂層16の樹脂側面17A~17Dは、この形態では、パッシベーション層13の側面14A~14Dに面一に形成されている。

側面5A~5Dおよび樹脂側面17A~17D(側面14A~14D)の間の距離は、1μm以上25μm以下であってもよい。側面5A~5Dおよび樹脂側面17A~17D(側面14A~14D)の間の距離は、1μm以上5μm以下、5μm以上10μm以下、10μm以上15μm以下、15μm以上20μm以下または20μm以上25μm以下であってもよい。むろん、パッシベーション層13の側面14A~14Dは、SiC半導体層2の側面5A~5Dに対して面一に形成されていてもよい。

パッド開口18は、サブパッド開口15に連通している。パッド開口18の内壁は、サブパッド開口15の内壁に面一に形成されている。パッド開口18の内壁は、サブパッド開口15の内壁に対してSiC半導体層2の側面5A~5D側に位置していてもよい。パッド開口18の内壁は、サブパッド開口15の内壁に対してSiC半導体層2の内方領域に位置していてもよい。樹脂層16は、サブパッド開口15の内壁を被覆していてもよい。

SiC半導体層2の第2主面4の上には、第2主面電極層19が形成されている。第2主面電極層19は、SiC半導体層2の第2主面4(SiC半導体基板6)との間でオーミック接触を形成している。

改質ライン22A~22Dは、溶融再硬化層、欠陥層、絶縁破壊層または屈折率変化層のうちの少なくとも1つの層を含んでいてもよい。溶融再硬化層は、SiC半導体層2の一部が溶融した後再度硬化した層である。欠陥層は、SiC半導体層2に形成された空孔や亀裂等を含む層である。絶縁破壊層は、SiC半導体層2の一部が絶縁破壊した層である。屈折率変化層は、SiC半導体層2の一部がSiC単結晶とは異なる屈折率に変化した層である。

図3を参照して、複数の改質ライン22Aは、側面5Aにおいてm軸方向に沿って直線状に延びる帯状にそれぞれ形成されている。複数の改質ライン22Aは、法線方向Zに互いにずれて形成されている。

複数の改質ライン22Aのうち第1主面3側の改質ライン22Aは、SiC半導体層2の第1主面3から第2主面4に間隔を空けて形成されている。第1主面3側の改質ライン22Aは、側面5AからSiC半導体層2の第1主面3の表層部を露出させている。

複数の改質ライン22Aは、SiC半導体基板6に形成されている。複数の改質ライン22Aは、SiC半導体基板6およびSiCエピタキシャル層7の間の境界から第2主面4に間隔を空けて形成されている。複数の改質ライン22Aは、SiC半導体層2の第1主面3の表層部においてSiCエピタキシャル層7を露出させている。

そこで、この形態では、図8を参照して、a軸方向に関して第1主面3の法線からSiC単結晶のc軸とは反対方向に向けて傾斜した1つまたは複数(この形態では1つ)の傾斜部を側面5Aに導入している。c軸の反対方向は、より具体的には、法線方向ZおよびSiC単結晶のa軸方向([11-20]方向)の間の方向である。

側面5Aには、SiC単結晶のc軸に沿う1つまたは複数の傾斜部も形成されている。SiC単結晶のc軸とは反対側に向かう傾斜部によってc軸に向かう傾斜部の形成領域の削減が図られている。

4個以上の改質ライン22Aが側面5Aに形成されている場合、全ての改質ライン22Aがa軸方向の一方側および他方側に交互にずれて形成されている必要はない。複数の改質ライン22Aは、a軸方向の一方側および他方側に交互にずれて形成された部分を含んでいてもよい。

この形態では、中間の改質ライン22Aが第2主面4側の改質ライン22Aに対してSiC半導体層2の内方にずれて形成された例が示されている。SiC単結晶のc軸とは反対側に向かう傾斜部は、第2主面4側の改質ライン22Aおよび中間の改質ライン22Aの間の領域に形成されている。第2主面4側の改質ライン22Aおよび中間の改質ライン22Aを結ぶ直線は、第1主面3の法線およびSiC単結晶のc軸に交差している。

この形態では、中間の改質ライン22Aが第1主面3側の改質ライン22Aに対してSiC半導体層2の内方にずれて形成された例が示されている。SiC単結晶のc軸に向かう傾斜部は、第1主面3側の改質ライン22Aおよび中間の改質ライン22Aの間の領域に形成されている。

3個以上の改質ライン22Aが形成されている場合、複数の改質ライン22Aは、任意の2個の改質ライン22Aを結ぶ直線に対してSiC半導体層2の内方([11-20]方向側)にずれて形成された1個または複数の改質ライン22Aを含むことが好ましい。

SiC単結晶のa軸方向に関して互いに隣り合う2つの改質ライン22Aの間の距離DRは、0μmを超えて20μm以下であってもよい。距離DRは、0μmを超えて5μm以下、5μm以上10μm以下、10μm以上15μm以下または15μm以上20μm以下であってもよい。

SiC半導体層2の側面5Aは、複数の改質ライン22Aを頂部または基部とする隆起部を有している。この形態では、第1主面3側の改質ライン22Aおよび第2主面4側の改質ライン22Aが隆起部の頂部を形成し、中間の改質ライン22Aが隆起部の基部を形成している例を示している。

改質ライン22Bは、SiC半導体基板6に形成されている。改質ライン22Bは、SiC半導体基板6およびSiCエピタキシャル層7の間の境界から第2主面4に間隔を空けて形成されている。改質ライン22Bは、SiC半導体層2の第1主面3の表層部においてSiCエピタキシャル層7を露出させている。

複数の改質ライン22Cは、法線方向Zに間隔を空けて形成されていることが好ましい。複数の改質ライン22Cは、法線方向Zに互いに重なっていてもよい。複数の改質ライン22Cは、法線方向Zに関して厚さTRをそれぞれ有している。複数の改質ライン22Cの厚さTRは、互いに等しくてもよいし、互いに異なっていてもよい。

複数の改質ライン22Cのうち第2主面4側の改質ライン22Cは、SiC半導体層2の第2主面4から第1主面3に間隔を空けて形成されている。第2主面4側の改質ライン22Cは、側面5CからSiC半導体層2の第2主面4の表層部を露出させている。

SiC単結晶のa面に面する側面5Cは、SiC単結晶のc軸を劈開方向として劈開する物性を有している。したがって、第1主面3の法線方向ZやSiC単結晶のc軸に沿って複数の改質ライン22Cを形成した場合には、側面5CはSiC単結晶のc軸に沿う傾斜面となる。

この形態では、断面視においてSiC単結晶のa軸方向に互いにずれて形成された複数の改質ライン22Cによって、SiC単結晶のc軸とは反対側(側面5Aとは反対側)に向かう傾斜部が側面5Cに導入されている。

複数の改質ライン22Cは、より具体的には、断面視において法線方向Zに関してa軸方向の一方側([11-20]方向側)および他方側([-1-120]方向側)に交互にずれて形成されている。

複数の改質ライン22Cは、任意の2個の改質ライン22Cを結ぶ直線が少なくとも第1主面3の法線に交差する態様で形成されていることが好ましい。任意の2個の改質ライン22Cを結ぶ直線は、SiC単結晶のc軸に交差することが好ましい。任意の2個の改質ライン22Cを結ぶ直線は、第1主面3の法線およびSiC単結晶のc軸に交差することが好ましい。

この形態では、中間の改質ライン22Cが第2主面4側の改質ライン22Cに対してSiC半導体層2の外方にずれて形成された例が示されている。SiC単結晶のc軸とは反対側に向かう傾斜部は、第2主面4側の改質ライン22Cおよび中間の改質ライン22Cの間の領域に形成されている。第2主面4側の改質ライン22Cおよび中間の改質ライン22Cを結ぶ直線は、第1主面3の法線およびSiC単結晶のc軸に交差している。

この形態では、中間の改質ライン22Cが第1主面3側の改質ライン22Cに対してSiC半導体層2の外方にずれて形成された例が示されている。SiC単結晶のc軸に向かう傾斜部は、第1主面3側の改質ライン22Cおよび中間の改質ライン22Cの間の領域に形成されている。

3個以上の改質ライン22Cが形成されている場合、複数の改質ライン22Cは、任意の2個の改質ライン22Aを結ぶ直線に対してSiC半導体層2の外方([11-20]方向側)にずれて形成された1個または複数の改質ライン22Cを含むことが好ましい。

SiC単結晶のa軸方向に関して互いに隣り合う2つの改質ライン22Cの間の距離DRは、0μmを超えて20μm以下であってもよい。距離DRは、0μmを超えて5μm以下、5μm以上10μm以下、10μm以上15μm以下または15μm以上20μm以下であってもよい。

SiC半導体層2の側面5Cは、複数の改質ライン22Cを頂部または基部とする隆起部を有している。この形態では、第1主面3側の改質ライン22Cおよび第2主面4側の改質ライン22Cが隆起部の基部を形成し、中間の改質ライン22Cが隆起部の頂部を形成している例を示している。

改質ライン22Dは、SiC半導体基板6に形成されている。改質ライン22Dは、SiC半導体基板6およびSiCエピタキシャル層7の間の境界から第2主面4に間隔を空けて形成されている。改質ライン22Dは、SiC半導体層2の第1主面3の表層部においてSiCエピタキシャル層7を露出させている。

改質ライン22Cおよび改質ライン22Dは、SiC半導体層2における側面5Cおよび側面5Dを接続する角部において互いに連なっていてもよい。改質ライン22Dおよび改質ライン22Aは、SiC半導体層2における側面5Dおよび側面5Aを接続する角部において互いに連なっていてもよい。

改質ライン22A~22Dは、SiC半導体層2の側面5A~5Dにおいて異なる専有割合RA,RB,RC,RDで形成されている。専有割合RAは、改質ライン22Aが側面5Aに占める割合である。専有割合RBは、改質ライン22Bが側面5Bに占める割合である。専有割合RCは、改質ライン22Cが側面5Cに占める割合である。専有割合RDは、改質ライン22Dが側面5Dに占める割合である。

専有割合RA~RDは、改質ライン22A~22Dの個数、厚さTR、総表面積等によって調整される。この形態では、一例として、改質ライン22A~22Dの個数および厚さTRを調節することによって、改質ライン22A~22Dの専有割合RA~RDを調整している。

法線方向Zに関して改質ライン22A~22Dの厚さTRは、SiC半導体層2の厚さTL以下(TR≦TL)であることが好ましい。改質ライン22A~22Dの厚さTRは、SiC半導体基板6の厚さTS未満(TR<TS)であることがさらに好ましい。

SiC半導体層2の厚さTLに対する改質ライン22A~22Dの厚さTRの比TR/TLは、0.1以上1.0未満であることが好ましい。比TR/TLは、0.1以上0.2以下、0.2以上0.4以下、0.4以上0.6以下、0.6以上0.8以下または0.8以上1.0未満であってもよい。

SiC半導体基板6の厚さTSに対する改質ライン22A~22Dの厚さTRの比TR/TSは、0.1以上1.0未満であることがさらに好ましい。比TR/TSは、0.1以上0.2以下、0.2以上0.4以下、0.4以上0.6以下、0.6以上0.8以下または0.8以上1.0未満であってもよい。

図5を参照して、改質ライン22Aは、複数のa面改質部28(改質部)を含む。換言すると、改質ライン22Aは、複数のa面改質部28の集合体によって形成されている。複数のa面改質部28は、側面5Aから露出するSiC単結晶がSiC単結晶とは異なる性質に改質された部分である。側面5Aにおいて各a面改質部28の周囲の領域は、SiC単結晶とは異なる性質に改質されていてもよい。

複数のa面改質部28は、法線方向Zに延びる線状にそれぞれ形成されている。これにより、複数のa面改質部28は、全体として縞状に形成されている。複数のa面改質部28は、m軸方向幅が一端部28a側から他端部28b側に向けて狭まる先細り形状に形成された複数のa面改質部28を含んでいてもよい。

m軸方向に関して、互いに隣り合う複数のa面改質部28の中央部間のピッチPRは、0μmを超えて20μm以下であってもよい。ピッチPRは、0μmを超えて5μm以下、5μm以上10μm以下、10μm以上15μm以下または15μm以上20μm以下であってもよい。

改質ライン22Cは、側面5Cに形成されている点を除いて、改質ライン22Aと同様の構造を有している。改質ライン22Aの説明は、「側面5A」を「側面5C」と読み替えて改質ライン22Cの説明に準用される。

複数のm面改質部29は、法線方向Zに延びる線状にそれぞれ形成されている。これにより、複数のm面改質部29は、全体として縞状に形成されている。複数のm面改質部29は、a軸方向幅が一端部29a側から他端部29b側に向けて狭まる先細り形状に形成された複数のm面改質部29を含んでいてもよい。

a軸方向に関して、互いに隣り合う複数のm面改質部29の中央部間のピッチPRは、0μm以上20μm以下であってもよい。ピッチPRは、0μm以上5μm以下、5μm以上10μm以下、10μm以上15μm以下または15μm以上20μm以下であってもよい。

改質ライン22Bは、側面5Bに形成されている点を除いて、改質ライン22Dと同様の構造を有している。改質ライン22Dの説明は、「側面5D」を「側面5B」と読み替えて改質ライン22Bの説明に準用される。

ガード領域36は、より具体的には、平面視においてダイオード領域35を取り囲む無端状(たとえば四角環状、角を面取りした四角環状または円環状)に形成されている。これにより、ガード領域36は、ガードリング領域として形成されている。ダイオード領域35は、この形態では、ガード領域36によって画定されている。また、アクティブ領域8は、ガード領域36によって画定されている。

SiC半導体層2の第1主面3の上には、前述の主面絶縁層10が形成されている。主面絶縁層10には、ダイオード領域35を露出させるダイオード開口37が形成されている。ダイオード開口37は、ダイオード領域35に加えてガード領域36の内周縁も露出させている。ダイオード開口37は、平面視においてSiC半導体層2の側面5A~5Dに平行な4辺を有する四角形状に形成されている。

第1主面電極層12は、より具体的には、ダイオード領域35との間でショットキー接合を形成している。これにより、第1主面電極層12をアノードとし、ダイオード領域35をカソードとするショットキーバリアダイオードDが形成されている。主面絶縁層10の上には、前述のパッシベーション層13および樹脂層16が形成されている。

SiC半導体ウエハ41は、SiC半導体基板6のベースとなる部材である。SiC半導体ウエハ41は、六方晶からなるSiC単結晶の一例としての4H-SiC単結晶を含む。SiC半導体ウエハ41は、この形態では、SiC半導体基板6のn型不純物濃度に対応したn型不純物濃度を有している。

SiC半導体ウエハ41の厚さTWは、SiC半導体基板6の厚さTSを超えている(TS<TW)。SiC半導体ウエハ41の厚さTWは、研削によってSiC半導体基板6の厚さTSに合わせ込まれる。

第1ウエハ主面42および第2ウエハ主面43は、SiC単結晶のc面に対して[11-20]方向に10°以下の角度で傾斜したオフ角θを有している。第1ウエハ主面42の法線方向Zは、SiC単結晶のc軸([0001]方向)に対してオフ角θ分だけ傾斜している。

オフ角θは、1.5°以上3.0°以下の角度の範囲に設定されていてもよい。この場合、オフ角θは、1.5°以上2.0°以下または2.0°以上2.5°以下の角度の範囲に設定されていることが好ましい。

SiC半導体ウエハ41のウエハ側面44には、SiC単結晶の結晶方位を示す目印の一例として1つのオリエンテーションフラット49が形成されている。オリエンテーションフラット49は、SiC半導体ウエハ41のウエハ側面44に形成された切欠部である。オリエンテーションフラット49は、この形態では、SiC単結晶のa軸方向([11-20]方向)に沿って直線状に延びている。

第1オリエンテーションフラットは、SiC単結晶のa軸方向([11-20]方向)に沿って直線状に延びる切欠部であってもよい。第2オリエンテーションフラットは、SiC単結晶のm軸方向([1-100]方向)に沿って直線状に延びる切欠部であってもよい。

各装置形成領域51は、SiC単結晶の結晶方位に沿った4つの辺52A,52B,52C,52Dを有している。4つの辺52A~52Dは、SiC半導体層2の4つの側面5A~5Dにそれぞれ対応している。つまり、4つの辺52A~52Dは、m軸方向([1-100]方向)に沿う2つの辺52A,52Cおよびa軸方向([11-20]方向)に沿う2つの辺52B,52Dを含む。

複数の第1切断予定ライン54は、m軸方向([1-100]方向)に沿ってそれぞれ延びている。複数の第2切断予定ライン55は、a軸方向([11-20]方向)に沿ってそれぞれ延びている。複数の装置形成領域51に所定の構造が作り込まれた後、切断予定ライン53に沿ってSiC半導体ウエハ41を切断することによって、複数のSiC半導体装置1が切り出される。

図10Aを参照して、SiC半導体装置1を製造するにあたり、まず、SiC半導体ウエハ41が用意される(図9も併せて参照)。次に、SiC半導体ウエハ41の第1ウエハ主面42にn型のSiCエピタキシャル層7が形成される。

これにより、SiC半導体ウエハ41およびSiCエピタキシャル層7を含むSiC半導体ウエハ構造61が形成される。SiC半導体ウエハ構造61は、第1主面62および第2主面63を含む。

次に、図10Bを参照して、SiC半導体ウエハ構造61の第1主面62にp+型のガード領域36が形成される。ガード領域36の形成工程は、イオン注入マスク(図示せず)を介してSiC半導体ウエハ構造61の第1主面62の表層部にp型不純物を選択的に導入する工程を含む。ガード領域36は、より具体的には、SiCエピタキシャル層7の表層部に形成される。

ダイオード領域35は、イオン注入マスク(図示せず)を介してSiC半導体ウエハ構造61の第1主面62の表層部にn型不純物を選択的に導入することによって形成されてもよい。

次に、図10Dを参照して、所定パターンを有するマスク64が、主面絶縁層10の上に形成される。マスク64は、複数の開口65を有している。複数の開口65は、主面絶縁層10においてダイオード開口37を形成すべき領域をそれぞれ露出させている。

次に、図10Eを参照して、SiC半導体ウエハ構造61の第1主面62の上に第1主面電極層12のベースとなるベース電極層66が形成される。ベース電極層66は、SiC半導体ウエハ構造61の第1主面62の全域に形成され、主面絶縁層10を被覆する。第1主面電極層12は、蒸着法、スパッタ法またはめっき法によって形成されてもよい。

次に、マスク67を介するエッチング法によって、ベース電極層66の不要な部分が除去される。これにより、ベース電極層66が複数の第1主面電極層12に分割される。第1主面電極層12の形成後、マスク67は除去される。

次に、図10Hを参照して、パッシベーション層13の上に、樹脂層16が塗布される。樹脂層16は、アクティブ領域8および外側領域9を一括して被覆する。樹脂層16は、ポジティブタイプの感光性樹脂の一例としてのポリベンゾオキサゾールを含んでいてもよい。

次に、パッシベーション層13の不要な部分が除去される。パッシベーション層13の不要な部分は、樹脂層16を介するエッチング法によって除去されてもよい。これにより、サブパッド開口15がパッシベーション層13に形成される。また、切断予定ライン53に沿うダイシングストリート69がパッシベーション層13に区画される。

この場合、樹脂層16の形成工程に先立って、マスクを介するエッチング法によってパッシベーション層13の不要な部分が除去され、サブパッド開口15が形成される。この工程によれば、パッシベーション層13を任意の形状に形成できる。

SiC半導体ウエハ構造61は、SiC半導体層2の厚さTLに対応する厚さTWSになるまで研削される。SiC半導体ウエハ構造61は、40μm以上200μm以下の厚さTWSになるまで研削されてもよい。

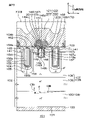

次に、図10Kを参照して、改質ライン22A~22Dのベースとなる複数の改質ライン70(改質層)が形成される。改質ライン70の形成工程では、レーザ光照射装置71からSiC半導体ウエハ構造61に向けてパルス状のレーザ光が照射される。

レーザ光の集光部(焦点)は、SiC半導体ウエハ構造61の厚さ方向途中部に設定される。SiC半導体ウエハ構造61に対するレーザ光の照射位置は、切断予定ライン53(各装置形成領域51の4つの辺52A~52D)に沿って移動される。

これにより、SiC半導体ウエハ構造61の厚さ方向途中部に、切断予定ライン53(各装置形成領域51の4つの辺52A~52D)に沿って延び、SiC単結晶の結晶状態が他の領域とは異なる性質に改質した複数の改質ライン70が形成される。

第1切断予定ライン54に形成された複数の改質ライン70は、改質ライン22A(改質ライン22C)に対応している。第2切断予定ライン55に形成された1層の改質ライン70は、改質ライン22B(改質ライン22D)に対応している。

複数の改質ライン70は、SiC半導体ウエハ構造61の厚さ方向途中部に形成されたレーザ加工痕でもある。より具体的には、改質ライン70のa面改質部28およびm面改質部29がレーザ加工痕である。

次に、図10Lを参照して、SiC半導体ウエハ構造61の第2主面63に第2主面電極層19が形成される。第2主面電極層19は、蒸着法、スパッタ法またはめっき法によって形成されてもよい。

レーザアニール処理法によれば、SiC半導体ウエハ構造61の第2主面63の表層部のSiC単結晶が改質されてSiアモルファス層が形成される。この場合、SiC半導体層2の第2主面4の表層部にSiアモルファス層を有するSiC半導体装置1が製造される。SiC半導体層2の第2主面4では、研削痕およびSiアモルファス層が併存する。レーザアニール処理法によれば、SiC半導体層2の第2主面4に対する第2主面電極層19のオーミック性を高めることができる。

次に、SiC半導体ウエハ構造61の第2主面63側から支持部材73を介して切断予定ライン53に外力が加えられる。切断予定ライン53に対する外力は、ブレード等の押圧部材によって加えられてもよい。

さらに他の形態において、SiC半導体ウエハ構造61の第1主面62側または第2主面63側に伸縮性の支持部材73が貼着されてもよい。この場合、SiC半導体ウエハ構造61は、伸縮性の支持部材73をm軸方向およびa軸方向に引き伸ばすことによって劈開されてもよい。

このようにして、SiC半導体ウエハ構造61が改質ライン70(改質ライン22A~22D)を起点に切断予定ライン53に沿って劈開され、複数のSiC半導体装置1が1枚のSiC半導体ウエハ構造61(SiC半導体ウエハ41)から切り出される。

また、SiC半導体ウエハ構造61の研削工程(図10J)は、SiC半導体ウエハ41の用意工程(図10A)の後、改質ライン70(改質ライン22A~22D)の形成工程(図10K)の前の任意のタイミングで複数回に分けて実施されてもよい。また、SiC半導体ウエハ構造61の研削工程(図10J)は、SiC半導体ウエハ41の用意工程(図10A)の後、第2主面電極層19の形成工程(図10L)の前の任意のタイミングで複数回に分けて実施されてもよい。

図11を参照して、半導体パッケージ74は、この形態では、所謂TO-220タイプである。半導体パッケージ74は、SiC半導体装置1、パッド部75、ヒートシンク76、複数(この形態では2本)の端子77、複数(この形態では2本)の導線78および封止樹脂79を含む。パッド部75、ヒートシンク76および複数の端子77は、接続対象物の一例としてのリードフレームを形成している。

SiC半導体装置1の第2主面電極層19は、導電接合材80を介してパッド部75に電気的に接続されている。導電接合材80は、第2主面電極層19およびパッド部75の間の領域に介在されている。

複数の端子77は、パッド部75に対してヒートシンク76とは反対側の辺に沿って配列されている。複数の端子77は、それぞれ金属板を含む。端子77は、鉄、金、銀、銅、アルミニウム等を含んでいてもよい。

複数の導線78は、ボンディングワイヤ等であってもよい。複数の導線78は、導線78Aおよび導線78Bを含む。導線78Aは、第1端子77AおよびSiC半導体装置1の第1主面電極層12に電気的に接続されている。これにより、第1端子77Aは、導線78Aを介してSiC半導体装置1の第1主面電極層12に電気的に接続されている。

封止樹脂79は、ヒートシンク76および複数の端子77の一部を露出させるように、SiC半導体装置1、パッド部75および複数の導線78を封止している。封止樹脂79は、直方体形状に形成されている。

SiC半導体装置1は、半導体組立装置を用いて半導体パッケージ74のパッド部75に実装される。半導体組立装置におけるSiC半導体装置1の搬送工程は、SiC半導体層2の第1主面3を吸着して保持するピックアップノズルPNによって行われる。

図13は、参考例に係るSiC半導体装置99の構造を説明するための図である。

SiC単結晶のa面に面する側面5A,5Cは、SiC単結晶のc軸を劈開方向として劈開する物性を有している。したがって、第1主面3の法線方向ZやSiC単結晶のc軸に沿って複数の改質ライン70(改質ライン22A,22C)を形成した場合には、側面5A,5CはSiC単結晶のc軸に沿う傾斜面となる。

S=SM+SI…(1)

SI=W×TL×tanθ…(2)

上記(1),(2)式において、「SM」は第1主面3の平面面積であり、「SI」は傾斜面によって増加した平面面積であり、「W」はSiC半導体層2の側面5A,5Cの長さであり、「θ」はオフ角である。

これに対して、SiC半導体装置1によれば、SiC半導体層2においてSiC単結晶のa面に面する側面5A,5Cは、第1主面3の法線を0°とした時、当該法線に対してオフ角θ未満の角度θaを有している。

また、SiC半導体装置1によれば、第1主面3の法線からSiC単結晶のc軸とは反対側の方向に向けて傾斜した1つまたは複数(この形態では1つ)の傾斜部が側面5A,5Cに導入されている。

また、SiC半導体装置1によれば、側面5A,5Cに形成された複数の改質ライン22A,22Cは、断面視においてSiC単結晶のa軸方向に互いにずれている。複数の改質ライン22A,22Cは、より具体的には、断面視において法線方向Zに関してa軸方向の一方側および他方側に交互にずれて形成されている。

また、複数の改質ライン22A,22Cのうちa軸方向に関してもっとも離れた2つの改質ライン22A,22Cの間の距離DDは、TL×tanθ未満の値(0<DD<TL×tanθ)である。これにより、側面5A,5Cの傾斜幅(TL×tanθ)を適切に低減できる。よって、上記(1)式において「SI」を適切に低減させることができる。

SiC単結晶は、c面(シリコン面)をc軸から見た平面視において最近接原子方向(図1および図2も併せて参照)に沿って割れ易く、最近接原子方向の交差方向に沿って割れ難いという物性を有している。最近接原子方向は、a軸方向およびその等価方向である。最近接原子方向の交差方向は、m軸方向およびその等価方向である。

つまり、改質ライン70の形成工程において、a軸方向に延びる第2切断予定ライン55に沿う改質ライン70の専有割合(個数)を、m軸方向に延びる第1切断予定ライン54に沿う改質ライン70の専有割合(個数)よりも小さくできる。最近接原子方向に沿う結晶面は、m面およびその等価面である。

漏れ電流特性の変動が、改質ラインに起因するSiC半導体層2の電気的特性の変動として例示される。SiC半導体装置は、図11に示されたように、封止樹脂79によって封止されることがある。

また、SiC半導体層2の各側面5A~5Dの全域に複数の改質ラインが法線方向Zに沿って形成された構造では、SiC半導体層2のクラックの発生リスクも高まる。したがって、SiC半導体装置1のように、改質ライン22A~22Dの形成領域を制限することによってSiC半導体層2の電気的特性の変動やクラックの発生を抑制できる。

換言すれば、薄化されたSiC半導体ウエハ構造61(SiC半導体ウエハ41)によれば、SiC半導体ウエハ構造61の厚さ方向全域に改質ライン70(改質ライン22A~22D)を法線方向Zに間隔を空けて形成せずに、SiC半導体ウエハ構造61(SiC半導体ウエハ41)を適切に劈開できる。

SiC半導体層2においてSiC半導体基板6の厚さTSは、40μm以上150μm以下であってもよい。SiC半導体層2においてSiCエピタキシャル層7の厚さTEは、1μm以上50μm以下であってもよい。SiC半導体層2の薄化は、抵抗値を低減する上でも有効である。

したがって、SiC半導体層2の第1主面3および側面5A~5Dを接続する角部から間隔を空けて改質ライン22A~22Dを形成することにより、SiC半導体層2の角部におけるクラックの発生を適切に抑制できる。

したがって、SiC半導体層2の第2主面4および側面5A~5Dを接続する角部から間隔を空けて改質ライン22A~22Dを形成することにより、SiC半導体層2の角部におけるクラックの発生を適切に抑制できる。

主面絶縁層10は、改質ライン22A~22Dが形成された構造において、SiC半導体層2の側面5A~5Dおよび第1主面電極層12の間の絶縁性を高める。これにより、SiC半導体層2の側面5A~5Dに改質ライン22A~22Dが形成された構造において、SiC半導体層2の電気的特性の安定性を高めることができる。

第1形態例に係る改質ライン22B,22Dは、SiC半導体層2の第1主面3の接線方向に沿って直線状に延びる帯状に形成されている。これに対して、第2形態例に係る改質ライン22B,22Dは、SiC半導体層2の第1主面3から第2主面4に向けて下り傾斜した傾斜状に延びる帯状に形成されている。第2形態例に係る改質ライン22B,22Dは、より具体的には、第1端部領域81、第2端部領域82および傾斜領域83をそれぞれ含む。

傾斜領域83は、第1端部領域81および第2端部領域82の間の領域を第1主面3から第2主面4に向けて下り傾斜している。改質ライン22B,22Dの傾斜方向および傾斜角度は任意であり、図14Aの形態に限定されない。

むろん、改質ライン22A,22Cも改質ライン22B,22Dと同様に、第1主面3から第2主面4に向けて下り傾斜した傾斜状に延びる帯状に形成されていてもよい。つまり、改質ライン22A,22Cは、第1端部領域81、第2端部領域82および傾斜領域83をそれぞれ含んでいてもよい。

図14Bは、図3に示すSiC半導体装置1を示す斜視図であって、改質ライン22A~22Dの第3形態例を示す斜視図である。以下では、SiC半導体装置1に対して述べた構造に対応する構造については同一の参照符号を付して説明を省略する。

湾曲領域86は、第1主面3から第2主面4に向かう凹湾曲状に下り傾斜し、第1端部領域84および第2端部領域85を接続している。改質ライン22B,22Dの傾斜方向および傾斜角度は任意であり、図14Bの形態に限定されない。

むろん、改質ライン22A,22Cも改質ライン22B,22Dと同様に、第1主面3から第2主面4に向かう凹湾曲状に下り傾斜していてもよい。つまり、改質ライン22A,22Cは、第1端部領域84、第2端部領域85および湾曲領域86をそれぞれ含んでいてもよい。

図14Cは、図3に示すSiC半導体装置1を示す斜視図であって、改質ライン22A~22Dの第4形態例を示す斜視図である。以下では、SiC半導体装置1に対して述べた構造に対応する構造については同一の参照符号を付して説明を省略する。

湾曲領域86は、第2主面4から第1主面3に向かう凸湾曲状に下り傾斜し、第1端部領域84および第2端部領域85を接続している。改質ライン22B,22Dの傾斜方向および傾斜角度は任意であり、図14Cの形態に限定されない。

むろん、改質ライン22A,22Cも改質ライン22B,22Dと同様に、第2主面4から第1主面3に向かう凸湾曲状に下り傾斜していてもよい。つまり、改質ライン22A,22Cは、第1端部領域84、第2端部領域85および湾曲領域86をそれぞれ含んでいてもよい。

図14Dは、図3に示すSiC半導体装置1を示す斜視図であって、改質ライン22A~22Dの第5形態例を示す斜視図である。以下では、SiC半導体装置1に対して述べた構造に対応する構造については同一の参照符号を付して説明を省略する。

改質ライン22B,22Dの蛇行周期は、任意である。改質ライン22B,22Dは、第1主面3から第2主面4に向けて凹湾曲状に延びる1つの帯状にそれぞれ形成されていてもよい。この場合、改質ライン22B,22Dは、2つの第1領域87、1つの第2領域88および2つの接続領域89をそれぞれ含んでいてもよい。

第5形態例に係る改質ライン22B,22Dは、改質ライン70(改質ライン22B,22D)の形成工程において、レーザ光の集光部(焦点)等を調節することによって形成される(図10Kも併せて参照)。第5形態例に係る改質ライン22B,22Dが形成される場合であっても、第1形態例に係る改質ライン22A~22Dが形成された場合と同様の効果を奏することができる。

むろん、改質ライン22A,22Cも改質ライン22B,22Dと同様に、SiC半導体層2の第1主面3および第2主面4に向けて蛇行した曲線状(湾曲状)に延びる帯状に形成されていてもよい。つまり、改質ライン22A,22Cは、第1領域87、第2領域88および接続領域89をそれぞれ含んでいてもよい。

第1形態例、第2形態例、第3形態例、第4形態例および第5形態例(以下、単に「第1~第5形態例」という。)に係る改質ライン22A~22Dのうちの少なくとも2種を同時に含むSiC半導体装置1が形成されてもよい。

図15は、本発明の第2実施形態に係るSiC半導体装置91を示す斜視図であって、第1形態例に係る改質ライン22A~22Dが適用された構造を示す斜視図である。以下では、SiC半導体装置1に対して述べた構造に対応する構造については同一の参照符号を付して説明を省略する。

主面絶縁層10は、樹脂層16およびパッシベーション層13と共にSiC半導体層2の第1主面3の周縁部を露出させている。主面絶縁層10の絶縁側面11A~11Dは、この形態では、樹脂層16の樹脂側面17A~17Dおよびパッシベーション層13の側面14A~14Dに面一に形成されている。この形態では、主面絶縁層10の絶縁側面11A~11Dもダイシングストリートを区画していた部分となる。

この場合、前述の図10Kの工程において、SiC半導体ウエハ構造61の第1主面62側から主面絶縁層10を介さずにSiC半導体ウエハ構造61の内部にレーザ光が直接照射されてもよい。

図16は、本発明の第3実施形態に係るSiC半導体装置101を1つの角度から見た斜視図であって、第1形態例に係る改質ライン22A~22Dが適用された構造を示す斜視図である。図17は、図16に示すSiC半導体装置101を別の角度から見た斜視図である。図18は、図16に示すSiC半導体装置101を示す平面図である。図19は、図18から樹脂層129を取り除いた平面図である。

SiC半導体装置101において、第1形態例に係る改質ライン22A~22Dに代えてまたはこれに加えて第2形態例、第3形態例、第4形態例または第5形態例に係る改質ライン22A~22Dが採用されてもよい。また、第1~第5形態例に係る改質ライン22A~22Dの特徴のうちの少なくとも2つの特徴が組み合わされた形態を有する改質ライン22A~22Dが採用されてもよい。

SiC半導体層102は、一方側の第1主面103、他方側の第2主面104、ならびに、第1主面103および第2主面104を接続する側面105A,105B,105C,105Dを有している。第1主面103および第2主面104は、それらの法線方向Zから見た平面視(以下、単に「平面視」という。)において四角形状(この形態では長方形状)に形成されている。

SiC半導体層102の厚さTLは、40μm以上200μm以下であってもよい。厚さTLは、40μm以上60μm以下、60μm以上80μm以下、80μm以上100μm以下、100μm以上120μm以下、120μm以上140μm以下、140μm以上160μm以下、160μm以上180μm以下または180μm以上200μm以下であってもよい。厚さTLは、60μm以上150μm以下であることが好ましい。

第1主面103および第2主面104は、SiC単結晶のc面に対して[11-20]方向に10°以下の角度で傾斜したオフ角θを有している。法線方向Zは、SiC単結晶のc軸([0001]方向)に対してオフ角θ分だけ傾斜している。

オフ角θは、1.5°以上3.0°以下の角度の範囲に設定されていてもよい。この場合、オフ角θは、1.5°以上2.0°以下または2.0°以上2.5°以下の角度の範囲に設定されていることが好ましい。

第1方向Xは、この形態では、SiC単結晶のm軸方向([1-100]方向)に設定されている。第2方向Yは、SiC単結晶のa軸方向([11-20]方向)に設定されている。

この場合、側面105Aおよび側面105Cは、SiC半導体層102の第1主面103の法線を0°としたとき、SiC半導体層102の第1主面103の法線に対してオフ角θに応じた角度で傾斜していてもよい。オフ角θに応じた角度は、オフ角θと等しくてもよいし、0°を超えてオフ角θ未満の角度であってもよい。

SiC半導体基板106の厚さTSは、40μm以上150μm以下であってもよい。厚さTSは、40μm以上50μm以下、50μm以上60μm以下、60μm以上70μm以下、70μm以上80μm以下、80μm以上90μm以下、90μm以上100μm以下、100μm以上110μm以下、110μm以上120μm以下、120μm以上130μm以下、130μm以上140μm以下または140μm以上150μm以下であってもよい。厚さTSは、40μm以上130μm以下であることが好ましい。SiC半導体基板106の薄化によって、電流経路の短縮による抵抗値の低減を図ることができる。

高濃度領域108は、SiC半導体層102の第1主面103側の領域に形成されている。低濃度領域109は、高濃度領域108に対してSiC半導体層102の第2主面104側の領域に形成されている。

高濃度領域108の厚さは、低濃度領域109の厚さ以下である。高濃度領域108の厚さは、より具体的には、低濃度領域109の厚さ未満である。高濃度領域108の厚さは、SiCエピタキシャル層107の総厚さの2分の1未満である。

アクティブ領域111は、平面視において、SiC半導体層102の側面105A~105Dから内方領域に間隔を空けてSiC半導体層102の中央部に設定されている。アクティブ領域111は、平面視においてSiC半導体層102の側面105A~105Dに平行な4辺を有する四角形状(この形態では長方形状)に設定されている。

SiC半導体層102の第1主面103の上には、主面絶縁層113が形成されている。主面絶縁層113は、アクティブ領域111および外側領域112を選択的に被覆している。主面絶縁層113は、酸化シリコン(SiO2)を含んでいてもよい。

主面絶縁層113の上には、第1主面電極層の1つとしての主面ゲート電極層115が形成されている。主面ゲート電極層115は、主面絶縁層113を貫通して、SiC半導体層102の任意の領域に電気的に接続されている。

ゲートパッド116は、平面視においてSiC半導体層102の側面105Aに沿って形成されている。ゲートパッド116は、平面視においてSiC半導体層102の側面105Aの中央領域に沿って形成されている。

ゲートフィンガー117,118は、外側ゲートフィンガー117および内側ゲートフィンガー118を含む。外側ゲートフィンガー117は、ゲートパッド116から引き出されており、アクティブ領域111の周縁に沿って帯状に延びている。

外側ゲートフィンガー117は、一対の開放端部119,120を有している。一対の開放端部119,120は、アクティブ領域111の内方領域を挟んでゲートパッド116と対向する領域に形成されている。一対の開放端部119,120は、この形態では、SiC半導体層102の側面105Cに沿って形成されている。

主面絶縁層113の上には、第1主面電極層の1つとしての主面ソース電極層121がさらに形成されている。主面ソース電極層121は、主面絶縁層113を貫通して、SiC半導体層102の任意の領域に電気的に接続されている。主面ソース電極層121は、この形態では、ソースパッド122、ソース引き回し配線123およびソース接続部124を含む。

そこで、SiC半導体装置101では、主面ソース電極層121の構造を利用して、外側領域112で生じたアバランシェ電流を吸収するアバランシェ電流吸収構造を形成している。

これにより、外側領域112で生じた不所望な電流によって寄生バイポーラトランジスタがオン状態になるのを抑制できる。よって、ラッチアップを抑制できるから、MISFETの制御の安定性を高めることができる。

主面絶縁層113の上には、パッシベーション層125(絶縁層)が形成されている。パッシベーション層125は、酸化シリコン層または窒化シリコン層からなる単層構造を有していてもよい。

パッシベーション層125の側面126A,126B,126C,126Dは、平面視においてSiC半導体層102の側面105A~105Dから内方領域に間隔を空けて形成されている。パッシベーション層125は、平面視においてSiC半導体層102の周縁部を露出させている。パッシベーション層125は、主面絶縁層113を露出させている。

パッシベーション層125の上には、樹脂層129(絶縁層)が形成されている。パッシベーション層125および樹脂層129は、1つの絶縁積層構造(絶縁層)を形成している。図18では、樹脂層129がハッチングによって示されている。

樹脂層129は、主面ゲート電極層115および主面ソース電極層121を選択的に被覆している。樹脂層129の樹脂側面130A,130B,130C,130Dは、SiC半導体層102の側面105A~105Dから内方領域に間隔を空けて形成されている。樹脂層129は、パッシベーション層125と共に主面絶縁層113を露出させている。樹脂層129の樹脂側面130A~130Dは、この形態では、パッシベーション層125の側面126A~126Dに面一に形成されている。

樹脂層129やパッシベーション層125からSiC半導体層102の周縁部を露出させることにより、樹脂層129やパッシベーション層125を物理的に切断する必要がなくなる。これにより、一枚のSiC半導体ウエハからSiC半導体装置101を円滑に切り出すことができる。また、SiC半導体層102の側面105A~105Dからの絶縁距離を増加させることができる。

樹脂層129のゲートパッド開口131は、パッシベーション層125のゲートサブパッド開口127に連通している。ゲートパッド開口131の内壁は、ゲートサブパッド開口127の内壁の外側に位置していてもよい。ゲートパッド開口131の内壁は、ゲートサブパッド開口127の内壁の内側に位置していてもよい。樹脂層129は、ゲートサブパッド開口127の内壁を被覆していてもよい。

SiC半導体層102の第2主面104には、第2主面電極層としてのドレイン電極層133が接続されている。オフ時において主面ソース電極層121およびドレイン電極層133の間に印加可能な最大電圧は、1000V以上10000V以下であってもよい。

ドレイン電極層133は、Ti層、Ni層、Au層、Ag層およびAl層のうちの少なくとも2つを任意の態様で積層させた積層構造を有していてもよい。ドレイン電極層133は、SiC半導体層102の第2主面104からこの順に積層されたTi層、Ni層、Au層およびAg層を含む4層構造を有していてもよい。

SiC半導体層102の側面105A~105Dには、第1形態例に係る複数の改質ライン22A~22Dが形成されている。第3実施形態に係る改質ライン22A~22Dの構造は、SiC半導体層2に代えてSiC半導体層102に形成されている点を除いて、第1実施形態に係る改質ライン22A~22Dの構造と同様である。

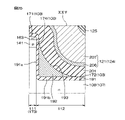

図20は、図19に示す領域XXの拡大図であって、SiC半導体層102の第1主面103の構造を説明するための図である。図21は、図20に示すXXI-XXI線に沿う断面図である。図22は、図20に示すXXII-XXII線に沿う断面図である。図23は、図21に示す領域XXIIIの拡大図である。図24は、図19に示すXXIV-XXIV線に沿う断面図である。図25は、図24に示す領域XXVの拡大図である。

ボディ領域141は、この形態では、SiC半導体層102の第1主面103においてアクティブ領域111を形成する領域の全域に形成されている。ボディ領域141のp型不純物濃度は、1.0×1017cm-3以上1.0×1019cm-3以下であってもよい。

各ゲートトレンチ142は、この形態では、アクティブ領域111において一方側(側面105B側)の周縁部から他方側(側面105D側)の周縁部に向けて延びている。複数のゲートトレンチ142は、平面視において全体としてストライプ状に形成されている。

各ゲートトレンチ142の長さは、0.5mm以上であってもよい。各ゲートトレンチ142の長さは、図22に示す断面において、各ゲートトレンチ142および外側ゲートフィンガー117の接続部分側の端部から、反対側の端部までの長さである。

各ゲートトレンチ142は、アクティブトレンチ部143およびコンタクトトレンチ部144を一体的に含む。アクティブトレンチ部143は、アクティブ領域111においてMISFETのチャネルに沿う部分である。

各ゲートトレンチ142の側壁は、法線方向Zに沿って延びていてもよい。各ゲートトレンチ142の側壁は、SiC半導体層102の第1主面103に対してほぼ垂直に形成されていてもよい。

各ゲートトレンチ142の底壁は、SiCエピタキシャル層107に位置している。各ゲートトレンチ142の底壁は、より具体的には、SiCエピタキシャル層107の高濃度領域108に位置している。

各ゲートトレンチ142の底壁は、SiC半導体層102の第1主面103に対して平行に形成されていてもよい。むろん、各ゲートトレンチ142の底壁は、SiC半導体層102の第2主面104に向かう凸湾曲状に形成されていてもよい。

各ゲートトレンチ142の第2方向Yに沿う幅は、0.1μm以上2μm以下であってもよい。各ゲートトレンチ142の幅は、0.1μm以上0.5μm以下、0.5μm以上1.0μm以下、1.0μm以上1.5μm以下または1.5μm以上2μm以下であってもよい。

傾斜部147は、この形態では、SiC半導体層102の内方に向かう凹湾曲状に形成されている。傾斜部147は、各ゲートトレンチ142の内方に向かう凸湾曲状に形成されていてもよい。傾斜部147は、各ゲートトレンチ142の開口エッジ部146に対する電界集中を緩和する。

ゲート絶縁層148は、酸化シリコン(SiO2)、窒化シリコン(SiN)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)または酸化タンタル(Ta2O3)のうちの少なくとも1種を含む。

第1領域148aは、ゲートトレンチ142の側壁に沿って形成されている。第2領域148bは、ゲートトレンチ142の底壁に沿って形成されている。第3領域148cは、SiC半導体層102の第1主面103に沿って形成されている。ゲート絶縁層148の第3領域148cは、主面絶縁層113の一部を形成している。

第1領域148aの厚さTaは、0.01μm以上0.2μm以下であってもよい。第2領域148bの厚さTbは、0.05μm以上0.5μm以下であってもよい。第3領域148cの厚さTcは、0.05μm以上0.5μm以下であってもよい。

これにより、第3領域148cの消失に起因して、第1領域148aがエッチング法によって除去されることを抑制できる。その結果、ゲート電極層149を、ゲート絶縁層148を挟んでSiC半導体層102(ボディ領域141)に適切に対向させることができる。

膨出部148dは、各ゲートトレンチ142の内方に向かって凸湾曲状に張り出している。膨出部148dは、各ゲートトレンチ142の開口エッジ部146において各ゲートトレンチ142の開口を狭めている。

ゲート電極層149は、ゲート絶縁層148を挟んで各ゲートトレンチ142に埋め込まれている。ゲート電極層149は、より具体的には、各ゲートトレンチ142においてゲート絶縁層148によって区画された凹状の空間に埋め込まれている。ゲート電極層149は、ゲート電圧によって制御される。

ゲート電極層149の断面積(各ゲートトレンチ142が延びる方向と直交する断面積)は、0.05μm2以上0.5μm2以下であってもよい。ゲート電極層149の断面積は、ゲート電極層149の深さおよびゲート電極層149の幅の積で定義される。

ゲート電極層149のp型不純物濃度は、ボディ領域141のp型不純物濃度以上である。ゲート電極層149のp型不純物濃度は、より具体的には、ボディ領域141のp型不純物濃度よりも大きい。

図20および図22を参照して、アクティブ領域111には、ゲート配線層150が形成されている。ゲート配線層150は、ゲートパッド116およびゲートフィンガー117,118に電気的に接続される。図22では、ゲート配線層150がハッチングによって示されている。

ゲート配線層150は、この形態では、外側ゲートフィンガー117に沿って形成されている。ゲート配線層150は、より具体的には、アクティブ領域111の内方領域を3方向から区画するように、SiC半導体層102の3つの側面105A,105B,105Dに沿って形成されている。

複数のソーストレンチ155は、第1方向X(SiC単結晶のm軸方向)に沿って延びる帯状にそれぞれ形成されている。複数のソーストレンチ155は、平面視において全体としてストライプ状に形成されている。第2方向Yに関して、互いに隣り合うソーストレンチ155の中央部間のピッチは、1.5μm以上3μm以下であってもよい。

各ソーストレンチ155の側壁は、法線方向Zに沿って延びていてもよい。各ソーストレンチ155の側壁は、SiC半導体層102の第1主面103に対してほぼ垂直に形成されていてもよい。

各ソーストレンチ155の底壁は、SiCエピタキシャル層107に位置している。各ソーストレンチ155の底壁は、より具体的には、SiCエピタキシャル層107の高濃度領域108に位置している。各ソーストレンチ155の底壁は、さらに具体的には、各ゲートトレンチ142の底壁および低濃度領域109の間の領域に位置している。

各ソーストレンチ155の底壁は、SiC半導体層102の第1主面103に対して平行に形成されていてもよい。むろん、各ソーストレンチ155の底壁は、SiC半導体層102の第2主面104に向かう凸湾曲状に形成されていてもよい。

各ソーストレンチ155の底壁は、各ゲートトレンチ142の底壁に対してSiC半導体層102の第2主面104側に位置している。むろん、各ソーストレンチ155の深さは、各ゲートトレンチ142の深さと等しくてもよい。

各ソーストレンチ155の第1方向幅は、各ゲートトレンチ142の第1方向幅とほぼ等しくてもよい。各ソーストレンチ155の第1方向幅は、各ゲートトレンチ142の第1方向幅以上であってもよい。各ソーストレンチ155の第1方向幅は、0.1μm以上2μm以下(たとえば0.5μm程度)であってもよい。

ソース絶縁層156は、酸化シリコン(SiO2)、窒化シリコン(SiN)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)または酸化タンタル(Ta2O3)のうちの少なくとも1種を含む。

第1領域156aは、各ソーストレンチ155の側壁に沿って形成されている。第2領域156bは、各ソーストレンチ155の底壁に沿って形成されている。第1領域156aの厚さTsaは、第2領域156bの厚さTsbよりも小さい。

第1領域156aの厚さTsaは、ゲート絶縁層148の第1領域156aの厚さTaとほぼ等しくてもよい。第2領域156bの厚さTsbは、ゲート絶縁層148の第2領域156bの厚さTbとほぼ等しくてもよい。むろん、一様な厚さを有するソース絶縁層156が形成されていてもよい。

ソース電極層157は、各ソーストレンチ155の開口側に位置する上端部を有している。ソース電極層157の上端部は、SiC半導体層102の第1主面103よりも下方に形成されている。ソース電極層157の上端部は、SiC半導体層102の第1主面103よりも上方に位置していてもよい。

ソース電極層157の上端部は、ソース絶縁層156の上端部よりも上方に突出していてもよい。ソース電極層157の上端部は、ソース絶縁層156の上端部よりも下方に位置していてもよい。ソース電極層157の厚さは、0.5μm以上10μm以下(たとえば1μm程度)であってもよい。

ソース電極層157のp型不純物濃度は、ボディ領域141のp型不純物濃度以上である。ソース電極層157のp型不純物濃度は、より具体的には、ボディ領域141のp型不純物濃度よりも大きい。ソース電極層157のp型不純物は、ホウ素(B)、アルミニウム(Al)、インジウム(In)またはガリウム(Ga)のうちの少なくとも1種を含んでいてもよい。

ソース電極層157のp型不純物濃度は、ゲート電極層149のp型不純物濃度とほぼ等しくてもよい。ソース電極層157のシート抵抗は、ゲート電極層149のシート抵抗とほぼ等しくてもよい。

このように、SiC半導体装置101は、複数のトレンチゲート構造161および複数のトレンチソース構造162を有している。各トレンチゲート構造161は、ゲートトレンチ142、ゲート絶縁層148、ゲート電極層149を含む。各トレンチソース構造162は、ソーストレンチ155、ソース絶縁層156およびソース電極層157を含む。

ソース領域163は、各ゲートトレンチ142の一方側の側壁および他方側の側壁に沿って複数形成されている。複数のソース領域163は、第1方向Xに沿って延びる帯状にそれぞれ形成されている。

このように、SiC半導体層102の第1主面103の表層部においてゲートトレンチ142の側壁に沿う領域には、SiC半導体層102の第1主面103から第2主面104に向けてソース領域163、ボディ領域141およびドリフト領域135がこの順に形成されている。

アクティブ領域111においてSiC半導体層102の第1主面103の表層部には、複数のp+型のコンタクト領域164が形成されている。各コンタクト領域164は、平面視において互いに隣り合う2つのゲートトレンチ142の間の領域に形成されている。各コンタクト領域164は、各ソース領域163に対してゲートトレンチ142とは反対側の領域に形成されている。

各コンタクト領域164のp型不純物濃度は、ボディ領域141のp型不純物濃度よりも大きい。各コンタクト領域164のp型不純物濃度は、1.0×1018cm-3以上1.0×1021cm-3以下であってもよい。各コンタクト領域164のp型不純物は、アルミニウム(Al)であってもよい。

第1表層領域164aは、ボディ領域141の表層部において、ソーストレンチ155の一方側の側壁を被覆している。第1表層領域164aは、ボディ領域141およびソース領域163に電気的に接続されている。

第1表層領域164aの底部は、この形態では、ボディ領域141の底部およびソース領域163の底部の間の領域に位置している。第1表層領域164aの底部は、SiC半導体層102の第1主面103およびボディ領域141の底部の間の領域に位置していてもよい。

第2表層領域164bは、ソース領域163の底部に対してSiC半導体層102の第1主面103側の領域に位置している。第2表層領域164bは、この形態では、SiC半導体層102の第1主面103に対して平行に延びる底部を有している。

第2表層領域164bは、この形態では、ソーストレンチ155の他方側の側壁から隣り合うゲートトレンチ142に向けて引き出されている。第2表層領域164bは、ソーストレンチ155およびゲートトレンチ142の間の中間領域まで延びていてもよい。第2表層領域164bは、ゲートトレンチ142からソーストレンチ155側に間隔を空けて形成されている。

SiC半導体層102の第1主面103の表層部には、複数のディープウェル領域165が形成されている。各ディープウェル領域165は、アクティブ領域111においてSiC半導体層102の耐圧を調整する耐圧調整領域(耐圧保持領域)とも称される。

各ディープウェル領域165は、各コンタクト領域164を被覆するように、各ソーストレンチ155の内壁に沿って形成されている。各ディープウェル領域165は、各コンタクト領域164に電気的に接続されている。

各ディープウェル領域165は、各ソーストレンチ155の側壁および底壁を接続する角部を被覆している。各ディープウェル領域165は、各ソーストレンチ155の側壁から角部を介して各ソーストレンチ155の底壁を被覆している。各ディープウェル領域165は、各ソーストレンチ155の側壁においてボディ領域141に連なっている。

各ディープウェル領域165のp型不純物濃度は、ボディ領域141のp型不純物濃度とほぼ等しくてもよい。各ディープウェル領域165のp型不純物濃度は、ボディ領域141のp型不純物濃度を超えていてもよい。各ディープウェル領域165のp型不純物濃度は、ボディ領域141のp型不純物濃度未満であってもよい。

図20および図22を参照して、アクティブ領域111の周縁部には、p型の周縁ディープウェル領域166が形成されている。周縁ディープウェル領域166は、SiCエピタキシャル層107に形成されている。周縁ディープウェル領域166は、より具体的には、SiCエピタキシャル層107の高濃度領域108に形成されている。

周縁ディープウェル領域166は、より具体的には、アクティブ領域111の周縁部において、各ゲートトレンチ142のコンタクトトレンチ部144の内壁に沿う領域に形成されている。

周縁ディープウェル領域166は、各コンタクトトレンチ部144の側壁から角部を介して各コンタクトトレンチ部144の底壁を被覆している。各ディープウェル領域165は、各コンタクトトレンチ部144の側壁においてボディ領域141に連なっている。周縁ディープウェル領域166の底部は、各コンタクトトレンチ部144の底壁に対してSiC半導体層102の第2主面104側に位置している。

周縁ディープウェル領域166は、各コンタクトトレンチ部144から各アクティブトレンチ部143に引き出された引き出し部166aを含む。引き出し部166aは、SiCエピタキシャル層107の高濃度領域108に形成されている。引き出し部166aは、各アクティブトレンチ部143の側壁に沿って延び、角部を通ってアクティブトレンチ部143の底壁を被覆している。

引き出し部166aは、各アクティブトレンチ部143の側壁から角部を介して各アクティブトレンチ部143の底壁を被覆している。引き出し部166aは、各アクティブトレンチ部143の側壁においてボディ領域141に連なっている。引き出し部166aの底部は、各アクティブトレンチ部143の底壁に対してSiC半導体層102の第2主面104側に位置している。

周縁ディープウェル領域166のp型不純物濃度は、各ディープウェル領域165のp型不純物濃度とほぼ等しくてもよい。周縁ディープウェル領域166のp型不純物濃度は、各ディープウェル領域165のp型不純物濃度を超えていてもよい。周縁ディープウェル領域166のp型不純物濃度は、各ディープウェル領域165のp型不純物濃度未満であってもよい。

これにより、トレンチゲート型のMISFETにおいて、SiC半導体層102内における電界を緩和できる。したがって、互いに隣り合う複数のディープウェル領域165の間のピッチを狭めることは、電界集中を緩和する上で有効である。

各ディープウェル領域165の底部およびSiC半導体層102の第2主面104の間の距離は、ほぼ一定であることが好ましい。これにより、各ディープウェル領域165の底部およびSiC半導体層102の第2主面104の間の距離にバラツキが生じるのを抑制できる。

この形態では、互いに隣り合う複数のディープウェル領域165の間の領域に、SiCエピタキシャル層107の高濃度領域108が介在している。これにより、互いに隣り合う複数のディープウェル領域165の間の領域において、JFET(Junction Field Effect Transistor)抵抗を低減できる。

低抵抗電極層167は、ゲート電極層149のシート抵抗未満のシート抵抗を有する導電材料を含む。低抵抗電極層167のシート抵抗は、0.01Ω/□以上10Ω/□以下であってもよい。

低抵抗電極層167の接続部167aは、SiC半導体層102の第1主面103よりも上方に位置する部分を含んでいてもよい。低抵抗電極層167の接続部167aは、SiC半導体層102の第1主面103よりも下方に位置する部分を含んでいてもよい。

低抵抗電極層167の非接続部167bの全体がSiC半導体層102の第1主面103よりも上方に位置していてもよい。低抵抗電極層167の非接続部167bの全体がSiC半導体層102の第1主面103よりも下方に位置していてもよい。

たとえば、低抵抗電極層167の非接続部167bの中央部がSiC半導体層102の第1主面103よりも下方に位置し、低抵抗電極層167の非接続部167bの周縁部がSiC半導体層102の第1主面103よりも上方に位置していてもよい。

低抵抗電極層167の縁部167cは、ゲート絶縁層148の第3領域148cに接している。低抵抗電極層167の縁部167cは、より具体的には、ゲート絶縁層148の膨出部148dに接している。

したがって、低抵抗電極層167の縁部167cは、ゲート絶縁層148を挟んでソース領域163に対向している。低抵抗電極層167の縁部167cは、ゲート絶縁層148を挟んでボディ領域141とは対向していない。

特に、低抵抗電極層167の縁部167cを、比較的厚いゲート絶縁層148の第3領域148c(ゲート絶縁層148の角部)に接続させる設計は、電流パスが形成されるリスクを低減する上で有効である。

各ゲートトレンチ142内に供給された電流は、比較的低いシート抵抗を有する低抵抗電極層167を流れ、ゲート電極層149の全体に伝達される。これにより、ゲート電極層149の全体(アクティブ領域111の全域)を速やかにオフ状態からオン状態に移行させることができるから、スイッチング応答の遅延を抑制できる。

また、セル構造の微細化が進むと、ゲート電極層149の幅、深さ、断面積等が小さくなるため、各ゲートトレンチ142内における電気抵抗の増加に起因するスイッチング応答の遅延が懸念される。

図22を参照して、低抵抗電極層167は、この形態では、ゲート配線層150の上端部も被覆している。低抵抗電極層167においてゲート配線層150の上端部を被覆する部分は、低抵抗電極層167においてゲート電極層149の上端部を被覆する部分と一体的に形成されている。これにより、低抵抗電極層167は、ゲート電極層149の全域およびゲート配線層150の全域を被覆している。

これにより、ゲート配線層150を介してゲート電極層149の全体(アクティブ領域111の全域)を速やかにオフ状態からオン状態に移行させることができるから、スイッチング応答の遅延を抑制できる。

低抵抗電極層167は、ポリサイド層を含む。ポリサイド層は、ゲート電極層149の表層部を形成する部分が金属材料によってシリサイド化されることによって形成されている。ポリサイド層は、より具体的には、ゲート電極層149(p型ポリシリコン)に添加されたp型不純物を含むp型ポリサイド層からなる。ポリサイド層は、10μΩ・cm以上110μΩ・cm以下の比抵抗を有していることが好ましい。

ゲートトレンチ142内のシート抵抗は、低抵抗電極層167のシート抵抗に近似される。つまり、ゲートトレンチ142内のシート抵抗は、0.01Ω/□以上10Ω/□以下であってもよい。ゲートトレンチ142内のシート抵抗は、10Ω/□未満であることが好ましい。

SiC半導体層102の第1主面103において、ソース電極層157の上端部に沿う領域には、各ソーストレンチ155に連通するソースサブトレンチ168が形成されている。ソースサブトレンチ168は、各ソーストレンチ155の側壁の一部を形成している。

ソースサブトレンチ168は、ソース絶縁層156の一部を掘り下げることによって形成されている。ソースサブトレンチ168は、より具体的には、SiC半導体層102の第1主面103からソース絶縁層156の上端部およびソース電極層157の上端部を掘り下げることによって形成されている。

ソースサブトレンチ168は、断面視において底面積が開口面積よりも小さい先細り形状に形成されている。ソースサブトレンチ168の底壁は、SiC半導体層102の第2主面104に向かう凸湾曲状に形成されていてもよい。

ソースサブトレンチ168の底壁からは、少なくともソース絶縁層156の第1領域156aが露出している。ソース絶縁層156において第1領域156aの上端部は、SiC半導体層102の第1主面103よりも下方に位置している。

図24および図25を参照して、アクティブ領域111は、SiC半導体層102の第1主面103の一部を形成するアクティブ主面171を有している。外側領域112は、SiC半導体層102の第1主面103の一部を形成する外側主面172を有している。外側主面172は、この形態では、SiC半導体層102の側面105A~105Dに接続されている。

外側主面172は、アクティブ主面171に対してSiC半導体層102の第2主面104側に位置している。外側領域112は、この形態では、SiC半導体層102の第1主面103を第2主面104側に掘り下げることによって形成されている。したがって、外側主面172は、アクティブ主面171に対してSiC半導体層102の第2主面104側に窪んだ領域に形成されている。

外側主面172およびSiC半導体層102の第2主面104の間の距離は、各ソーストレンチ155の底壁およびSiC半導体層102の第2主面104の間の距離とほぼ等しくてもよい。

SiCエピタキシャル層107は、外側主面172から露出している。より具体的には、SiCエピタキシャル層107の高濃度領域108が、外側領域112の外側主面172から露出している。外側主面172は、SiCエピタキシャル層107の高濃度領域108を挟んでSiCエピタキシャル層107の低濃度領域109と対向している。

アクティブ台地173は、アクティブ主面171および外側主面172を接続するアクティブ側壁174を含む。アクティブ側壁174は、アクティブ領域111および外側領域112の間の境界領域を区画している。SiC半導体層102の第1主面103は、アクティブ主面171、外側主面172およびアクティブ側壁174によって形成されている。

アクティブ側壁174は、アクティブ主面171から外側主面172に向かって下り傾斜した傾斜面を有していてもよい。アクティブ側壁174の傾斜角度は、SiC半導体層102内においてアクティブ側壁174がアクティブ主面171との間で形成する角度である。

アクティブ側壁174においてアクティブ主面171側の領域からは、少なくともボディ領域141が露出している。図24および図25では、アクティブ側壁174からボディ領域141およびソース領域163が露出している形態例が示されている。

ダイオード領域181は、外側領域112においてアクティブ側壁174およびSiC半導体層102の側面105A~105Dの間の領域に形成されている。ダイオード領域181は、アクティブ側壁174および側面105A~105Dから間隔を空けて形成されている。

ダイオード領域181は、平面視においてソース引き回し配線123と重なっている。ダイオード領域181は、ソース引き回し配線123に電気的に接続されている。ダイオード領域181は、アバランシェ電流吸収構造の一部を形成している。

ダイオード領域181は、さらに具体的には、SiCエピタキシャル層107の高濃度領域108内に位置している。したがって、ダイオード領域181は、高濃度領域108との間でpn接合部を形成する。これにより、ダイオード領域181をアノードとし、SiC半導体層102をカソードとするpn接合ダイオードDpnが形成されている。

ダイオード領域181の底部は、コンタクト領域164の底部とほぼ等しい深さ位置に形成されていてもよい。ダイオード領域181の底部は、コンタクト領域164の底部とほぼ同一平面上に位置していてもよい。

外側ディープウェル領域182は、平面視においてアクティブ側壁174およびダイオード領域181の間の領域に形成されている。外側ディープウェル領域182は、この形態では、アクティブ側壁174からダイオード領域181側に向けて間隔を空けて形成されている。外側ディープウェル領域182は、外側領域112においてSiC半導体層102の耐圧を調整する耐圧調整領域(耐圧保持領域)とも称される。

外側ディープウェル領域182は、ダイオード領域181を介してソース引き回し配線123に電気的に接続されている。外側ディープウェル領域182は、pn接合ダイオードDpnの一部を形成していてもよい。外側ディープウェル領域182は、アバランシェ電流吸収構造の一部を形成していてもよい。

外側ディープウェル領域182の底部は、ダイオード領域181の底部に対してSiC半導体層102の第2主面104側に位置している。外側ディープウェル領域182の底部は、各ディープウェル領域165の底部とほぼ等しい深さ位置に形成されていてもよい。外側ディープウェル領域182の底部は、各ディープウェル領域165の底部とほぼ同一平面上に位置していてもよい。

外側ディープウェル領域182の底部およびSiC半導体層102の第2主面104の間の距離は、各ディープウェル領域165の底部およびSiC半導体層102の第2主面104の間の距離とほぼ等しくてもよい。

よって、SiC半導体層102の耐圧(たとえば破壊耐量)が、外側ディープウェル領域182の形態および各ディープウェル領域165の形態によって制限を受けることを抑制できるから、耐圧の向上を適切に図ることができる。

外側ディープウェル領域182の内周縁は、アクティブ領域111および外側領域112の境界領域近傍まで延びていてもよい。外側ディープウェル領域182は、アクティブ領域111および外側領域112の境界領域を横切っていてもよい。

外側ディープウェル領域182の外周縁は、この形態では、SiC半導体層102の第2主面104側からダイオード領域181を被覆している。外側ディープウェル領域182は、平面視においてソース引き回し配線123と重なっていてもよい。外側ディープウェル領域182の外周縁は、ダイオード領域181からアクティブ側壁174側に間隔を空けて形成されていてもよい。

外側ディープウェル領域182のp型不純物濃度は、各ディープウェル領域165のp型不純物濃度とほぼ等しくてもよい。外側ディープウェル領域182のp型不純物濃度は、ボディ領域141のp型不純物濃度とほぼ等しくてもよい。

外側ディープウェル領域182のp型不純物濃度は、コンタクト領域164のp型不純物濃度以下であってもよい。外側ディープウェル領域182のp型不純物濃度は、コンタクト領域164のp型不純物濃度未満であってもよい。外側ディープウェル領域182のp型不純物濃度は、1.0×1017cm-3以上1.0×1019cm-3以下であってもよい。

フィールドリミット構造183は、1個または複数(たとえば2個以上20個以下)のフィールドリミット領域184を含む。フィールドリミット構造183は、この形態では、複数(5個)のフィールドリミット領域184A,184B,184C,184D,184Eを有するフィールドリミット領域群を含む。

フィールドリミット領域184A~184Eは、より具体的には、平面視においてアクティブ領域111を取り囲む無端状(この形態では四角環状)にそれぞれ形成されている。フィールドリミット領域184A~184Eは、それぞれ、FLR(Field Limiting Ring)領域とも称される。

フィールドリミット領域184A~184Eのうち最内側のフィールドリミット領域184Aは、この形態では、SiC半導体層102の第2主面104側からダイオード領域181を被覆している。フィールドリミット領域184Aは、平面視において前述のソース引き回し配線123と重なっていてもよい。

フィールドリミット領域184A~184Eの全体は、各ゲートトレンチ142の底壁に対してSiC半導体層102の第2主面104側に位置している。フィールドリミット領域184A~184Eの底部は、各ソーストレンチ155の底壁に対してSiC半導体層102の第2主面104側に位置している。

フィールドリミット領域184A~184Eの底部は、各ディープウェル領域165(外側ディープウェル領域182)の底部に対して外側主面172側に位置していてもよい。フィールドリミット領域184A~184Eの底部は、各ディープウェル領域165(外側ディープウェル領域182)の底部に対してSiC半導体層102の第2主面104側に位置していてもよい。

フィールドリミット領域184A~184Eのp型不純物濃度は、ダイオード領域181のp型不純物濃度以下であってもよい。フィールドリミット領域184A~184Eのp型不純物濃度は、ダイオード領域181のp型不純物濃度よりも小さくてもよい。

フィールドリミット領域184A~184Eのp型不純物濃度は、外側ディープウェル領域182のp型不純物濃度以上であってもよい。フィールドリミット領域184A~184Eのp型不純物濃度は、外側ディープウェル領域182のp型不純物濃度よりも大きくてもよい。

フィールドリミット構造183は、外側領域112において電界集中を緩和する。フィールドリミット領域184の個数、幅、深さ、p型不純物濃度等は、緩和すべき電界に応じて種々の値を取り得る。

しかし、フィールドリミット構造183は、ダイオード領域181およびSiC半導体層102の側面105A~105Dの間の領域に代えて、平面視においてアクティブ側壁174およびダイオード領域181の間の領域に形成された1つまたは複数のフィールドリミット領域184を含んでいてもよい。

外側絶縁層191は、外側領域112においてダイオード領域181、外側ディープウェル領域182およびフィールドリミット構造183を選択的に被覆している。外側絶縁層191は、アクティブ側壁174および外側主面172に沿って膜状に形成されている。外側絶縁層191は、アクティブ主面171の上において、ゲート絶縁層148に連なっている。外側絶縁層191は、より具体的には、ゲート絶縁層148の第3領域148cに連なっている。

外側絶縁層191は、第1領域191aおよび第2領域191bを含む。外側絶縁層191の第1領域191aは、アクティブ側壁174を被覆している。外側絶縁層191の第2領域191bは、外側主面172を被覆している。

外側絶縁層191の第1領域191aの厚さは、ゲート絶縁層148の第1領域191aの厚さとほぼ等しくてもよい。外側絶縁層191の第2領域191bの厚さは、ゲート絶縁層148の第3領域148cの厚さとほぼ等しくてもよい。むろん、一様な厚さを有する外側絶縁層191が形成されていてもよい。

また、サイドウォール192は、アクティブ主面171および外側主面172の間に形成された段差を緩和する段差緩和構造を形成する。アクティブ領域111および外側領域112の間の境界領域を被覆する上層構造(被覆層)が形成される場合、上層構造は、サイドウォール192を被覆する。サイドウォール192は、上層構造の平坦性を高める。

サイドウォール192の傾斜部193は、SiC半導体層102側に向かう凹湾曲状に形成されていてもよい。サイドウォール192の傾斜部193は、SiC半導体層102とは反対側に向かう凸湾曲状に形成されていてもよい。

サイドウォール192の傾斜部193は、アクティブ主面171から外側主面172に向かう下り階段状に形成されていてもよい。つまり、サイドウォール192の傾斜部193は、外側主面172側に向かって窪んだ1つまたは複数の段部を有していてもよい。複数の段部は、サイドウォール192の傾斜部193の表面積を増加させ、上層構造に対する密着力を高める。

サイドウォール192の傾斜部193は、サイドウォール192の内側に向かって窪んだ複数の窪みを含んでいてもよい。複数の窪みは、サイドウォール192の傾斜部193の表面積を増加させ、上層構造に対する密着力を高める。

サイドウォール192は、p型不純物が添加されたp型ポリシリコンを含むことが好ましい。この場合、ゲート電極層149やソース電極層157と同時に、サイドウォール192を形成できる。

サイドウォール192のp型不純物濃度は、ゲート電極層149のp型不純物濃度とほぼ等しくてもよい。サイドウォール192のシート抵抗は、ゲート電極層149のシート抵抗とほぼ等しくてもよい。

サイドウォール192は、絶縁材料を含んでいてもよい。この場合、サイドウォール192によって外側領域112に対するアクティブ領域111の絶縁性を高めることができる。

層間絶縁層201は、アクティブ主面171および外側主面172に沿って膜状に形成されている。層間絶縁層201は、アクティブ領域111においてトレンチゲート構造161、ゲート配線層150およびトレンチソース構造162を選択的に被覆している。層間絶縁層201は、外側領域112においてダイオード領域181、外側ディープウェル領域182およびフィールドリミット構造183を選択的に被覆している。

層間絶縁層201は、酸化シリコンまたは窒化シリコンを含んでいてもよい。層間絶縁層201は、酸化シリコンの一例としてのPSG(Phosphor Silicate Glass)および/またはBPSG(Boron Phosphor Silicate Glass)を含んでいてもよい。

層間絶縁層201には、ゲートコンタクト孔202、ソースコンタクト孔203およびダイオードコンタクト孔204が形成されている。また、層間絶縁層201には、アンカー孔205が形成されている。

ソースコンタクト孔203は、アクティブ領域111において、ソース領域163、コンタクト領域164およびトレンチソース構造162を露出させている。ソースコンタクト孔203は、トレンチソース構造162等に沿う帯状に形成されていてもよい。ソースコンタクト孔203の開口エッジ部は、ソースコンタクト孔203内に向かう凸湾曲状に形成されている。

ダイオードコンタクト孔204は、外側ディープウェル領域182および/またはフィールドリミット構造183を露出させていてもよい。ダイオードコンタクト孔204の開口エッジ部は、ダイオードコンタクト孔204内に向かう凸湾曲状に形成されている。

図19を参照して、アンカー孔205は、平面視においてアクティブ領域111に沿って帯状に延びている。アンカー孔205は、この形態では、平面視においてアクティブ領域111を取り囲む無端状(この形態では四角環状)に形成されている。

層間絶縁層201の上には、主面ゲート電極層115および主面ソース電極層121が形成されている。主面ゲート電極層115および主面ソース電極層121は、それぞれ、SiC半導体層102の第1主面103側からこの順に積層されたバリア電極層206および主電極層207を含む積層構造を有している。

主電極層207の厚さは、バリア電極層206の厚さよりも大きい。主電極層207は、バリア電極層206の抵抗値よりも小さい抵抗値を有する導電材料を含む。主電極層207は、アルミニウム、銅、アルミニウム合金または銅合金のうちの少なくとも1つを含んでいてもよい。

主面ゲート電極層115のうちの外側ゲートフィンガー117は、層間絶縁層201の上からゲートコンタクト孔202に入り込んでいる。外側ゲートフィンガー117は、ゲートコンタクト孔202内において、ゲート配線層150に電気的に接続されている。これにより、ゲートパッド116からの電気信号は、外側ゲートフィンガー117を介してゲート電極層149に伝達される。

主面ソース電極層121のうちのソース引き回し配線123は、層間絶縁層201の上からダイオードコンタクト孔204に入り込んでいる。ソース引き回し配線123は、ダイオードコンタクト孔204内において、ダイオード領域181に電気的に接続されている。

層間絶縁層201の上には、前述のパッシベーション層125が形成されている。パッシベーション層125は、層間絶縁層201に沿って膜状に形成されている。パッシベーション層125は、層間絶縁層201を介して、アクティブ領域111および外側領域112を選択的に被覆している。

図24を参照して、パッシベーション層125は、外側領域112において、層間絶縁層201の上からアンカー孔205に入り込んでいる。パッシベーション層125は、アンカー孔205内において、SiC半導体層102の第1主面103(外側主面172)に接続されている。パッシベーション層125の外面においてアンカー孔205の上に位置する領域には、アンカー孔205に倣って窪んだリセス211が形成されている。

樹脂層129は、アクティブ領域111からサイドウォール192を横切って外側領域112に引き出されている。樹脂層129は、サイドウォール192を被覆する上層構造の一部を形成している。

アンカー構造は、外側領域112においてSiC半導体層102の第1主面103に形成された凹凸構造(Uneven Structure)を含む。凹凸構造(アンカー構造)は、より具体的には、外側主面172を被覆する層間絶縁層201を利用して形成された凹凸を含む。さらに具体的には、凹凸構造(アンカー構造)は、層間絶縁層201に形成されたアンカー孔205を含む。

以上、SiC半導体装置101によってもSiC半導体装置1に対して述べた効果と同様の効果を奏することができる。また、SiC半導体装置101によれば、SiC半導体層102およびディープウェル領域165の間の境界領域(pn接合部)から、ゲートトレンチ142の底壁に対してSiC半導体層102の第2主面104側の領域に向けて空乏層を拡げることができる。

また、SiC半導体装置101によれば、SiC半導体層102において空乏層が占める領域を増加させることができるから、帰還容量Crssを反比例的に低減できる。帰還容量Crssは、ゲート電極層149およびドレイン電極層133の間の静電容量である。

よって、SiC半導体層102の耐圧(たとえば破壊耐量)が、ディープウェル領域165の形態によって制限を受けることを抑制できるから、耐圧の向上を適切に図ることができる。

つまり、外側領域112で生じたアバランシェ電流を、ダイオード領域181および主面ソース電極層121によって吸収できる。その結果、MISFETの動作の安定性を高めることができる。

特に、SiC半導体装置101によれば、外側ディープウェル領域182は、ディープウェル領域165とほぼ等しい深さ位置に形成されている。より具体的には、外側ディープウェル領域182の底部は、ディープウェル領域165の底部とほぼ同一平面上に位置している。

これにより、外側ディープウェル領域182の底部およびSiC半導体層102の第2主面104の間の距離と、ディープウェル領域165の底部およびSiC半導体層102の第2主面104の間の距離との間で、バラツキが生じるのを抑制できる。

特に、SiC半導体装置101では、外側領域112をアクティブ領域111に対してSiC半導体層102の第2主面104側の領域に形成している。これにより、外側ディープウェル領域182の底部の位置を、適切に、ディープウェル領域165の底部の位置に近づけることができる。

しかも、SiC半導体装置101では、外側領域112の外側主面172が、ソーストレンチ155の底壁とほぼ同一平面上に位置している。これにより、等しいエネルギによってソーストレンチ155の底壁および外側領域112の外側主面172に対してp型不純物を導入する場合には、ディープウェル領域165および外側ディープウェル領域182をほぼ等しい深さ位置に形成できる。

また、SiC半導体装置101によれば、外側領域112にフィールドリミット構造183が形成されている。これにより、外側領域112において、フィールドリミット構造183による電界緩和効果を得ることができる。よって、SiC半導体層102の破壊耐量を適切に向上できる。

アクティブ主面171および外側主面172の間の領域には、アクティブ主面171および外側主面172の間の段差を緩和する段差緩和構造が形成されている。段差緩和構造は、サイドウォール192を含む。

凹凸構造(アンカー構造)は、より具体的には、外側領域112においてSiC半導体層102の第1主面103に形成された層間絶縁層201を利用して形成された凹凸を含む。さらに具体的には、凹凸構造(アンカー構造)は、層間絶縁層201に形成されたアンカー孔205を含む。

また、SiC半導体装置101によれば、ゲートトレンチ142にゲート絶縁層148を挟んでゲート電極層149が埋め込まれたトレンチゲート構造161が形成されている。このトレンチゲート構造161では、ゲート電極層149が、ゲートトレンチ142という限られたスペースにおいて低抵抗電極層167によって被覆されている。このような構造によれば、図26を用いて説明される効果を奏することができる。

第1棒グラフBL1は、n型ポリシリコンが埋め込まれたゲートトレンチ142内のシート抵抗を表している。第2棒グラフBL2は、p型ポリシリコンが埋め込まれたゲートトレンチ142内のシート抵抗を表している。

第1棒グラフBL1を参照して、n型ポリシリコンが埋め込まれたゲートトレンチ142内のシート抵抗は、10Ω/□であった。第2棒グラフBL2を参照して、p型ポリシリコンが埋め込まれたゲートトレンチ142内のシート抵抗は、200Ω/□であった。第3棒グラフBL3を参照して、ゲート電極層149(p型ポリシリコン)および低抵抗電極層167が埋め込まれたゲートトレンチ142内のシート抵抗は、2Ω/□であった。

しかし、p型ポリシリコンは、n型ポリシリコンのシート抵抗よりも数十倍(ここでは20倍)高いシート抵抗を有している。そのため、ゲート電極層149の材料としてp型ポリシリコンを採用した場合、ゲートトレンチ142内の寄生抵抗(以下、単に「ゲート抵抗」という。)の増加に伴ってエネルギ損失が著しく増大する。

低抵抗電極層167は、TiSi、TiSi2、NiSi、CoSi、CoSi2、MoSi2またはWSi2のうちの少なくとも1種を含むことができる。とりわけ、これらの種のうちのNiSi、CoSi2およびTiSi2は、比抵抗の値および温度依存性が比較的小さいことから、低抵抗電極層167を形成するポリサイド層として適している。

特に、ゲート電極層149およびゲート配線層150が低抵抗電極層167によって被覆されている構造では、トレンチゲート構造161に沿って電流を効率的に拡散させることができる。よって、スイッチング遅延の短縮を適切に図ることができる。

図27および図28を参照して、SiC半導体装置221は、アクティブ領域111においてSiC半導体層102の第1主面103に形成された外側ゲートトレンチ222を含む。外側ゲートトレンチ222は、アクティブ領域111の周縁部に沿って帯状に延びる。

外側ゲートトレンチ222は、より具体的には、アクティブ領域111の内方領域を3方向から区画するように、SiC半導体層102の3つの側面105A,105B,105Dに沿って形成されている。外側ゲートトレンチ222は、アクティブ領域111の内方領域を取り囲む無端状(たとえば四角環状)に形成されていてもよい。

外側ゲートトレンチ222には、ゲート配線層150が埋め込まれている。ゲート配線層150は、ゲートトレンチ142および外側ゲートトレンチ222の連通部においてゲート電極層149に接続されている。

以上、SiC半導体装置221によっても、SiC半導体装置101に対して述べた効果と同様の効果を奏することができる。また、SiC半導体装置221によれば、ゲート配線層150をSiC半導体層102の第1主面103の上に引き出す必要がない。

図29は、図23に対応する領域の拡大図であって、本発明の第5実施形態に係るSiC半導体装置231を示す拡大図である。以下では、SiC半導体装置101に対して述べた構造に対応する構造については、同一の参照符号を付して説明を省略する。

濃度勾配領域232は、SiCエピタキシャル層107において、アクティブ領域111に加えて外側領域112にも形成されている。濃度勾配領域232は、SiCエピタキシャル層107の全域に形成されている。

濃度勾配領域232の厚さは、0.5μm以上2.0μm以下であってもよい。濃度勾配領域232の厚さは、0.5μm以上1.0μm以下、1.0μm以上1.5μm以下または1.5μm以上2.0μm以下であってもよい。

つまり、前述のゲートトレンチ142、ソーストレンチ155、ディープウェル領域165、外側ディープウェル領域182等は、SiC半導体層102において高濃度領域108および濃度勾配領域232の境界領域に対して第1主面103側の領域に形成されている。

図30は、図20に対応する領域の拡大図であって、本発明の第6実施形態に係るSiC半導体装置241を示す拡大図である。以下では、SiC半導体装置101に対して述べた構造に対応する構造については、同一の参照符号を付して説明を省略する。

各第1ゲートトレンチ242において長辺を形成する側壁は、SiC単結晶のa面によって形成されている。各第1ゲートトレンチ242において短辺を形成する側壁は、SiC単結晶のm面によって形成されている。

各第2ゲートトレンチ243において長辺を形成する側壁は、SiC単結晶のm面によって形成されている。各第2ゲートトレンチ243において短辺を形成する側壁は、SiC単結晶のa面によって形成されている。

複数のセル領域244は、平面視において第1方向Xおよび第2方向Yに間隔を空けて行列状に配列されている。複数のセル領域244は、平面視において四角形状に形成されている。各セル領域244においてボディ領域141は、ゲートトレンチ142の側壁から露出している。ボディ領域141は、ゲートトレンチ142においてSiC単結晶のm面およびa面によって形成された側壁から露出している。

各ソーストレンチ155は、平面視において各セル領域244の中央部に形成されている。各ソーストレンチ155は、各セル領域244を第1方向Xに沿って切断したときに現れる切断面に1つ現れるパターンで形成されている。また、各ソーストレンチ155は、各セル領域244を第2方向Yに沿って切断したときに現れる切断面に1つ現れるパターンで形成されている。

各ソーストレンチ155の平面形状は任意である。各ソーストレンチ155は、平面視において三角形状、五角形状、六角形状等の多角形状、もしくは、円形状または楕円形状に形成されていてもよい。

以上、SiC半導体装置241によっても、SiC半導体装置101に対して述べた効果と同様の効果を奏することができる。

本発明の実施形態について説明したが、本発明の実施形態は、さらに他の形態で実施することもできる。

しかし、SiC単結晶のa軸方向([11-20]方向)に沿って延びる複数のゲートトレンチ142(第1ゲートトレンチ242)が形成されてもよい。この場合、SiC単結晶のa軸方向([11-20]方向)に沿って延びる複数のソーストレンチ155が形成される。

前述の第3~第6実施形態では、ソース絶縁層156がソーストレンチ155の側壁および底壁に沿って形成された例について説明した。

また、ソース絶縁層156は、ソーストレンチ155の側壁を露出させるように、ソーストレンチ155の底壁に沿って形成されていてもよい。ソース絶縁層156は、ソーストレンチ155の側壁の一部を露出させるように、ソーストレンチ155の側壁および底壁に沿って形成されていてもよい。

前述の第3~第6実施形態において、n+型のSiC半導体基板106に代えてp+型のSiC半導体基板(106)が採用されてもよい。この構造によれば、MISFETに代えて、IGBT(Insulated Gate Bipolar Transistor)を提供できる。この場合、前述の各実施形態において、MISFETの「ソース」がIGBTの「エミッタ」に読み替えられ、MISFETの「ドレイン」がIGBTの「コレクタ」に読み替えられる。

前述の各実施形態は、SiCとは異なる半導体材料を用いた半導体装置にも適用できる。SiCとは異なる半導体材料は、化合物半導体材料であってもよい。化合物半導体材料は、窒化ガリウム(GaN)および酸化ガリウム(Ga2O3)のいずれか一方または双方であってもよい。

[A1]六方晶からなるSiC単結晶を含み、前記SiC単結晶のc面に対してa軸方向に傾斜したオフ角を有する素子形成面としての第1主面、前記第1主面の反対側の第2主面、および、前記SiC単結晶のa面に面し、前記第1主面の法線を0°とした時、前記法線に対して前記オフ角未満の角度を有する劈開面からなる側面を有するSiC半導体層であって、前記第2主面および前記側面の一部を形成するSiC半導体基板、ならびに、前記第1主面および前記側面の一部を形成するSiCエピタキシャル層を含む積層構造を有するSiC半導体層と、前記側面において前記SiCエピタキシャル層から前記第2主面側に間隔を空けて前記SiC半導体基板からなる部分に厚さ方向に間隔を空けて形成され、前記SiC単結晶とは異なる性質に改質された複数の改質層と、を含む、SiC半導体装置。

[A4]前記SiC半導体層は、40μm以上200μm以下の厚さを有している、A1~A3のいずれか一つに記載のSiC半導体装置。

[A5]複数の前記改質層は、前記SiC単結晶のm軸方向に沿って延びる帯状にそれぞれ形成されている、A1~A4のいずれか一つに記載のSiC半導体装置。

[A7]前記SiC単結晶のa軸方向に関して、複数の前記改質層のうちの最も外方に位置する前記改質層および最も内方に位置する前記改質層の間の距離は、前記SiC半導体層の厚さにtanθ(θ:前記オフ角)を乗じた値未満である、A6に記載のSiC半導体装置。

[A9]複数の前記改質層は、前記SiC半導体層の前記第2主面から前記第1主面側に間隔を空けて形成されている、A1~A8のいずれか一つに記載のSiC半導体装置。

[A10]2個以上6個以下の前記改質層を含む、A1~A9のいずれか一つに記載のSiC半導体装置。

[A12]前記第2側面において前記SiCエピタキシャル層から前記第2主面側に間隔を空けて前記SiC半導体基板からなる部分に形成され、前記SiC単結晶とは異なる性質に改質された1つまたは複数の第2改質層をさらに含む、A11に記載のSiC半導体装置。

[A14]前記SiC単結晶は、2H(Hexagonal)-SiC単結晶、4H-SiC単結晶または6H-SiC単結晶からなる、A1~A13のいずれか一つに記載のSiC半導体装置。

[A16]前記第1主面の上において前記SiCエピタキシャル層を被覆し、前記側面に連なる絶縁側壁を有する絶縁層と、前記側面から内方に間隔を空けて前記絶縁層の上に形成された第1電極と、をさらに含む、A1~A15のいずれか一つに記載のSiC半導体装置。

[A18]前記第2主面を被覆する第2電極をさらに含む、A1~A17のいずれか一つに記載のSiC半導体装置。

この明細書は、第1~第6実施形態に示された特徴の如何なる組み合わせ形態をも制限しない。第1~第6実施形態は、それらの間で任意の態様および任意の形態において組み合わせられることができる。つまり、第1~第6実施形態に示された特徴が任意の態様および任意の形態で組み合わされた形態が採用されてもよい。

2 SiC半導体層

3 SiC半導体層の第1主面

4 SiC半導体層の第2主面

5A SiC半導体層の側面

5B SiC半導体層の側面

5C SiC半導体層の側面

5D SiC半導体層の側面

6 SiC半導体基板

7 SiCエピタキシャル層

22A 改質ライン

22B 改質ライン

22C 改質ライン

22D 改質ライン

81 SiC半導体装置

101 SiC半導体装置

102 SiC半導体層

103 SiC半導体層の第1主面

104 SiC半導体層の第2主面

105A SiC半導体層の側面

105B SiC半導体層の側面

105C SiC半導体層の側面

105D SiC半導体層の側面

106 SiC半導体基板

107 SiCエピタキシャル層

θ オフ角

Z 法線方向

X 第1方向(m軸方向)

Y 第2方向(a軸方向)

Claims (19)

- SiC半導体基板およびSiCエピタキシャル層を含む積層構造を有し、前記SiCエピタキシャル層からなり、SiC単結晶のc面に対してオフ方向に傾斜したオフ角が導入された素子形成面、および、前記オフ方向の直交方向に延び、前記素子形成面の法線を0°とした時、当該法線に対して前記オフ角未満の角度で傾斜した側面を有するSiC半導体層と、

前記側面において前記SiCエピタキシャル層を露出させるように前記SiC半導体基板からなる部分に厚さ方向に間隔を空けて形成され、前記SiC半導体基板とは異なる性質に改質された複数の改質層と、を含む、SiC半導体装置。 - 複数の前記改質層は、断面視において前記オフ方向に互いにずれて形成されている、請求項1に記載のSiC半導体装置。

- 前記SiC半導体層の前記側面は、複数の前記改質層を頂部または基部とする隆起部を有している、請求項1または2に記載のSiC半導体装置。

- 前記SiC半導体基板は、第1導電型不純物を含み、

前記SiCエピタキシャル層は、第1導電型不純物を含み、前記SiC半導体基板の不純物濃度未満の不純物濃度を有している、請求項1~3のいずれか一項に記載のSiC半導体装置。 - 前記SiCエピタキシャル層は、前記SiC半導体基板の厚さ未満の厚さを有している、請求項1~4のいずれか一項に記載のSiC半導体装置。

- 前記SiC半導体層の前記側面は、劈開面からなる、請求項1~5のいずれか一項に記載のSiC半導体装置。

- 複数の前記改質層は、前記SiC半導体基板および前記SiCエピタキシャル層の境界に沿って帯状に延びている、請求項1~6のいずれか一項に記載のSiC半導体装置。

- 前記オフ方向は、SiC単結晶のシリコン面をc軸から見た平面視において最近接するSi原子の配列方向に設定されている、請求項1~7のいずれか一項に記載のSiC半導体装置。

- 前記SiC半導体層は、前記オフ方向に延びる第2側面を含む、請求項1~8のいずれか一項に記載のSiC半導体装置。

- 前記第2側面において前記SiCエピタキシャル層から間隔を空けて前記SiC半導体基板からなる部分に厚さ方向に形成され、前記SiC半導体基板とは異なる性質に改質された第2改質層をさらに含む、請求項9に記載のSiC半導体装置。

- 前記第2側面は、劈開面からなる、請求項9または10に記載のSiC半導体装置。

- 前記SiCエピタキシャル層を被覆する絶縁層と、

前記絶縁層の上に形成され、前記SiCエピタキシャル層に電気的に接続された第1電極と、をさらに含む、請求項1~11のいずれか一項に記載のSiC半導体装置。 - 前記絶縁層は、前記SiC半導体層の前記側面に連なる絶縁側面を有している、請求項12に記載のSiC半導体装置。

- 前記絶縁側面は、劈開面からなる、請求項13に記載のSiC半導体装置。

- 前記第1電極は、前記SiC半導体層の前記側面から間隔を空けて前記絶縁層の上に形成されている、請求項12~14のいずれか一項に記載のSiC半導体装置。

- 前記絶縁層の上において前記第1電極を部分的に被覆するパッシベーション層と、

前記パッシベーション層を被覆する樹脂層と、をさらに含む、請求項12~15のいずれか一項に記載のSiC半導体装置。 - 前記SiCエピタキシャル層とは反対側において前記SiC半導体基板を被覆し、前記SiC半導体基板に電気的に接続された第2電極さらに含む、請求項1~16のいずれか一項に記載のSiC半導体装置。

- 前記SiC半導体層は、2H(Hexagonal)-SiC単結晶、4H-SiC単結晶または6H-SiC単結晶からなる、請求項1~17のいずれか一項に記載のSiC半導体装置。

- 前記素子形成面に形成されたダイオードまたは電界効果トランジスタをさらに含む、請求項1~18のいずれか一項に記載のSiC半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019221436A JP7129397B2 (ja) | 2019-12-06 | 2019-12-06 | SiC半導体装置 |

| JP2022132065A JP7401615B2 (ja) | 2019-12-06 | 2022-08-22 | SiC半導体装置 |

| JP2023206936A JP7631487B2 (ja) | 2019-12-06 | 2023-12-07 | SiC半導体装置 |

| JP2025017733A JP2025062104A (ja) | 2019-12-06 | 2025-02-05 | SiC半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019221436A JP7129397B2 (ja) | 2019-12-06 | 2019-12-06 | SiC半導体装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018151453A Division JP6630411B1 (ja) | 2018-08-10 | 2018-08-10 | SiC半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022132065A Division JP7401615B2 (ja) | 2019-12-06 | 2022-08-22 | SiC半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020036048A JP2020036048A (ja) | 2020-03-05 |

| JP7129397B2 true JP7129397B2 (ja) | 2022-09-01 |

Family

ID=69668966

Family Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019221436A Active JP7129397B2 (ja) | 2019-12-06 | 2019-12-06 | SiC半導体装置 |

| JP2022132065A Active JP7401615B2 (ja) | 2019-12-06 | 2022-08-22 | SiC半導体装置 |

| JP2023206936A Active JP7631487B2 (ja) | 2019-12-06 | 2023-12-07 | SiC半導体装置 |

| JP2025017733A Pending JP2025062104A (ja) | 2019-12-06 | 2025-02-05 | SiC半導体装置 |

Family Applications After (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022132065A Active JP7401615B2 (ja) | 2019-12-06 | 2022-08-22 | SiC半導体装置 |

| JP2023206936A Active JP7631487B2 (ja) | 2019-12-06 | 2023-12-07 | SiC半導体装置 |

| JP2025017733A Pending JP2025062104A (ja) | 2019-12-06 | 2025-02-05 | SiC半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (4) | JP7129397B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2022044894A (ja) * | 2020-09-08 | 2022-03-18 | ソニーセミコンダクタソリューションズ株式会社 | 半導体チップ、製造方法 |

| JP7611668B2 (ja) | 2020-10-23 | 2025-01-10 | ラピスセミコンダクタ株式会社 | 半導体装置および半導体ウェハ |

| CN117941077A (zh) | 2021-09-22 | 2024-04-26 | 三菱电机株式会社 | 半导体装置以及电力转换装置 |

| JPWO2023058509A1 (ja) | 2021-10-08 | 2023-04-13 | ||

| WO2025197692A1 (ja) * | 2024-03-18 | 2025-09-25 | ローム株式会社 | 半導体装置 |

| CN118746710B (zh) * | 2024-06-12 | 2025-09-23 | 上海积塔半导体有限公司 | 扩展电阻测试结构及其制作方法、扩展电阻测试方法 |

Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003338468A (ja) | 2002-03-12 | 2003-11-28 | Hamamatsu Photonics Kk | 発光素子の製造方法、発光ダイオード、及び半導体レーザ素子 |

| JP2011100967A (ja) | 2009-07-21 | 2011-05-19 | Rohm Co Ltd | 半導体装置 |

| JP2012146878A (ja) | 2011-01-13 | 2012-08-02 | Hamamatsu Photonics Kk | レーザ加工方法 |

| JP2015146406A (ja) | 2014-02-04 | 2015-08-13 | 住友電気工業株式会社 | 縦型電子デバイスの製造方法および縦型電子デバイス |

| JP2015216140A (ja) | 2014-05-07 | 2015-12-03 | 株式会社ディスコ | 光デバイスの加工方法 |

| JP2016163049A (ja) | 2015-03-03 | 2016-09-05 | インフィネオン テクノロジーズ アクチエンゲゼルシャフトInfineon Technologies AG | ダイオード領域用のゲート電極とコンタクト構造とを含んでいるトレンチ構造を備えた半導体デバイス |

| JP2017028145A (ja) | 2015-07-24 | 2017-02-02 | 住友電気工業株式会社 | 炭化珪素半導体装置 |

| JP2017041502A (ja) | 2015-08-18 | 2017-02-23 | 浜松ホトニクス株式会社 | 加工対象物切断方法及び加工対象物切断装置 |

| JP2017041482A (ja) | 2015-08-18 | 2017-02-23 | 株式会社ディスコ | ウエーハの加工方法 |

| JP2017130696A (ja) | 2010-05-26 | 2017-07-27 | 三菱電機株式会社 | 半導体装置 |

| JP2018125520A (ja) | 2016-12-20 | 2018-08-09 | インフィネオン テクノロジーズ アーゲーInfineon Technologies Ag | 炭化ケイ素上への金属接触層の形成及び金属接触構造を有する半導体デバイス |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2216128B1 (en) * | 2002-03-12 | 2016-01-27 | Hamamatsu Photonics K.K. | Method of cutting object to be processed |

| WO2011090024A1 (ja) | 2010-01-19 | 2011-07-28 | シャープ株式会社 | 機能素子およびその製造方法 |

| JP2012000636A (ja) * | 2010-06-16 | 2012-01-05 | Showa Denko Kk | レーザ加工方法 |

| WO2013058222A1 (ja) * | 2011-10-18 | 2013-04-25 | 富士電機株式会社 | 固相接合ウエハの支持基板の剥離方法および半導体装置の製造方法 |

| JP5812029B2 (ja) * | 2012-06-13 | 2015-11-11 | 株式会社デンソー | 炭化珪素半導体装置およびその製造方法 |

| JP2015041638A (ja) | 2013-08-20 | 2015-03-02 | 住友電気工業株式会社 | 炭化珪素半導体装置およびその製造方法 |

| JP6224292B2 (ja) | 2015-04-08 | 2017-11-01 | 株式会社日立製作所 | 半導体装置および半導体モジュール |

| JP2017174969A (ja) | 2016-03-24 | 2017-09-28 | 株式会社日立製作所 | 半導体装置およびその製造方法並びに電力変換装置 |

| JP6919159B2 (ja) | 2016-07-29 | 2021-08-18 | 富士電機株式会社 | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 |

| JP6809218B2 (ja) | 2016-12-28 | 2021-01-06 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| JP6828449B2 (ja) | 2017-01-17 | 2021-02-10 | 株式会社デンソー | 半導体装置およびその製造方法 |

-

2019

- 2019-12-06 JP JP2019221436A patent/JP7129397B2/ja active Active

-

2022

- 2022-08-22 JP JP2022132065A patent/JP7401615B2/ja active Active

-

2023

- 2023-12-07 JP JP2023206936A patent/JP7631487B2/ja active Active

-

2025

- 2025-02-05 JP JP2025017733A patent/JP2025062104A/ja active Pending

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003338468A (ja) | 2002-03-12 | 2003-11-28 | Hamamatsu Photonics Kk | 発光素子の製造方法、発光ダイオード、及び半導体レーザ素子 |

| JP2011100967A (ja) | 2009-07-21 | 2011-05-19 | Rohm Co Ltd | 半導体装置 |

| JP2017130696A (ja) | 2010-05-26 | 2017-07-27 | 三菱電機株式会社 | 半導体装置 |

| JP2012146878A (ja) | 2011-01-13 | 2012-08-02 | Hamamatsu Photonics Kk | レーザ加工方法 |

| JP2015146406A (ja) | 2014-02-04 | 2015-08-13 | 住友電気工業株式会社 | 縦型電子デバイスの製造方法および縦型電子デバイス |

| JP2015216140A (ja) | 2014-05-07 | 2015-12-03 | 株式会社ディスコ | 光デバイスの加工方法 |

| JP2016163049A (ja) | 2015-03-03 | 2016-09-05 | インフィネオン テクノロジーズ アクチエンゲゼルシャフトInfineon Technologies AG | ダイオード領域用のゲート電極とコンタクト構造とを含んでいるトレンチ構造を備えた半導体デバイス |

| JP2017028145A (ja) | 2015-07-24 | 2017-02-02 | 住友電気工業株式会社 | 炭化珪素半導体装置 |

| JP2017041502A (ja) | 2015-08-18 | 2017-02-23 | 浜松ホトニクス株式会社 | 加工対象物切断方法及び加工対象物切断装置 |

| JP2017041482A (ja) | 2015-08-18 | 2017-02-23 | 株式会社ディスコ | ウエーハの加工方法 |

| JP2018125520A (ja) | 2016-12-20 | 2018-08-09 | インフィネオン テクノロジーズ アーゲーInfineon Technologies Ag | 炭化ケイ素上への金属接触層の形成及び金属接触構造を有する半導体デバイス |

Also Published As

| Publication number | Publication date |

|---|---|

| JP7401615B2 (ja) | 2023-12-19 |

| JP2022161998A (ja) | 2022-10-21 |

| JP2020036048A (ja) | 2020-03-05 |

| JP2024015272A (ja) | 2024-02-01 |

| JP7631487B2 (ja) | 2025-02-18 |

| JP2025062104A (ja) | 2025-04-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7129397B2 (ja) | SiC半導体装置 | |

| US12471339B2 (en) | SiC semiconductor device | |

| JP6563093B1 (ja) | SiC半導体装置 | |

| US12255227B2 (en) | SiC semiconductor device | |

| JP6664446B2 (ja) | SiC半導体装置 | |

| JP2026003014A (ja) | SiC半導体装置 | |

| JP2025098268A (ja) | SiC半導体装置 | |

| JP6664445B2 (ja) | SiC半導体装置 | |

| JP6630410B1 (ja) | SiC半導体装置 | |

| JP6647352B1 (ja) | SiC半導体装置 | |

| JP7129437B2 (ja) | SiC半導体装置 | |

| JP6630411B1 (ja) | SiC半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210806 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20220613 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20220721 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20220822 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7129397 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |