JP7023637B2 - 磁気トンネル接合素子の製造方法 - Google Patents

磁気トンネル接合素子の製造方法 Download PDFInfo

- Publication number

- JP7023637B2 JP7023637B2 JP2017153003A JP2017153003A JP7023637B2 JP 7023637 B2 JP7023637 B2 JP 7023637B2 JP 2017153003 A JP2017153003 A JP 2017153003A JP 2017153003 A JP2017153003 A JP 2017153003A JP 7023637 B2 JP7023637 B2 JP 7023637B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- magnetic

- ferromagnetic

- ferromagnetic layer

- laminated

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

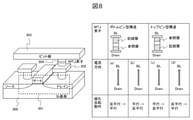

- H10B61/00—Magnetic memory devices, e.g. magnetoresistive RAM [MRAM] devices

- H10B61/20—Magnetic memory devices, e.g. magnetoresistive RAM [MRAM] devices comprising components having three or more electrodes, e.g. transistors

- H10B61/22—Magnetic memory devices, e.g. magnetoresistive RAM [MRAM] devices comprising components having three or more electrodes, e.g. transistors of the field-effect transistor [FET] type

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/10—Magnetoresistive devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/80—Constructional details

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/80—Constructional details

- H10N50/85—Materials of the active region

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Mram Or Spin Memory Techniques (AREA)

- Hall/Mr Elements (AREA)

Description

Claims (6)

- 磁気トンネル接合素子の製造方法において、

第1の強磁性層と、前記第1の強磁性層の下方に配置された障壁層と、第1の磁化方向を有し前記障壁層の下方に配置された第2の強磁性層と、前記第2の強磁性層の下方に配置された第1の非磁性層と、前記第1の磁化方向と反平行である第2の磁化方向を有し前記第1の非磁性層の下方に配置された第3の強磁性層とを有しハードマスク層が前記第1の強磁性層の上方に形成された積層膜を形成し、

前記ハードマスク層を円柱形状にパターニングし、

前記パターニングされたハードマスク層をマスクとして前記積層膜を前記第3の強磁性層表面または前記第1の非磁性層の途中までプラズマエッチングし、

前記パターニングされた前記積層膜に側壁堆積層を化学気相成長により積層し、

金属層を前記側壁堆積層に積層して前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとして前記第3の強磁性層をプラズマエッチングし、

前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとしてプラズマエッチングを行った後、前記金属層を除去し、

前記第1の磁化方向は、前記積層膜の積層方向と平行であり、

前記第1の非磁性層の材料および膜厚は、前記第3の強磁性層の磁化方向が前記第2の強磁性層の磁化方向と反平行となる材料および膜厚とされ、

前記パターニングされた第2の強磁性層、第1の非磁性層および第3の強磁性層により前記磁気トンネル接合素子の積層フェリ型参照層が構成され、

前記第3の強磁性層の直径は、前記積層フェリ型参照層から前記第1の強磁性層への漏れ磁場の絶対値が概ね0となる直径とされていることを特徴とする磁気トンネル接合素子の製造方法。 - 磁気トンネル接合素子の製造方法において、

上層から順に第1の強磁性層、障壁層、第2の強磁性層、第1の非磁性層および第3の強磁性層を有しハードマスク層が前記第1の強磁性層の上方に形成された積層膜を形成し、

前記ハードマスク層を円柱形状にパターニングし、

前記パターニングされたハードマスク層をマスクとして前記積層膜を前記第2の強磁性層表面または途中までプラズマエッチングし、

前記パターニングされたハードマスク層よりも外側領域の磁化を消失させることにより磁化消失層を前記第2の強磁性層に形成し、

パターニングされた前記積層膜に側壁堆積層を化学気相成長により積層し、

金属層を前記側壁堆積層に積層して前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとして前記磁化消失層、前記第1の非磁性層および前記第3の強磁性層をプラズマエッチングし、

前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとしてプラズマエッチングを行った後、前記金属層を除去し、

前記第2の強磁性層の材料および膜厚は、磁化方向が積層方向に対して平行となる材料および膜厚とされ、

前記第1の非磁性層の材料および膜厚は、前記第3の強磁性層の磁化方向が前記第2の強磁性層の磁化方向と反平行となる材料および膜厚とされ、

前記パターニングされた第2の強磁性層、第1の非磁性層および第3の強磁性層により前記磁気トンネル接合素子の積層フェリ型参照層が構成され、

前記磁化消失層の幅は、前記積層フェリ型参照層から前記第1の強磁性層への漏れ磁場の絶対値が概ね0となる幅とされていることを特徴とする磁気トンネル接合素子の製造方法。 - 磁気トンネル接合素子の製造方法において、

上層から順に第1の強磁性層、障壁層、第2の強磁性層、第2の非磁性層、第2の磁性多層膜層、第1の非磁性層および第1の磁性多層膜層を有しハードマスク層が前記第1の強磁性層の上方に形成された積層膜を形成し、

前記ハードマスク層を円柱形状にパターニングし、

前記パターニングされたハードマスク層をマスクとして前記積層膜を前記第1の磁性多層膜層表面または前記第1の非磁性層の途中までプラズマエッチングし、

前記パターニングされた積層膜に側壁堆積層を化学気相成長により積層し、

金属層を前記側壁堆積層に積層して前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとして前記第1の磁性多層膜層をプラズマエッチングし、

前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとしてプラズマエッチングを行った後、前記金属層を除去し、

前記第1の非磁性層の材料および膜厚は、前記第1の磁性多層膜層の磁化方向が前記第2の磁性多層膜層の磁化方向と反平行となる材料及び膜厚とされ、

前記第2の非磁性層の材料および膜厚は、前記第2の強磁性層の磁化方向が前記第2の磁性多層膜層の磁化方向と平行となる材料及び膜厚とされ、

前記パターニングされた第2の強磁性層、第2の非磁性層、第2の磁性多層膜層、第1の非磁性層および第1の磁性多層膜層により前記磁気トンネル接合素子の積層フェリ型参照層が構成され、

前記第1の磁性多層膜層の直径は、前記積層フェリ型参照層から前記第1の強磁性層への漏れ磁場の絶対値が概ね0となる直径とされていることを特徴とする磁気トンネル接合素子の製造方法。 - 磁気トンネル接合素子の製造方法において、

上層から順に第1の強磁性層、障壁層、第2の強磁性層、第2の非磁性層、第2の磁性多層膜層、第1の非磁性層および第1の磁性多層膜層を有しハードマスク層が前記第1の強磁性層の上方に形成された積層膜を形成し、

前記ハードマスク層を円柱形状にパターニングし、

前記パターニングされたハードマスク層をマスクとして前記積層膜を前記第2の磁性多層膜層表面または途中までプラズマエッチングし、

前記パターニングされたハードマスク層よりも外側領域の磁化を消失させることにより磁化消失層を前記第2の磁性多層膜層に形成し、

前記パターニングされた積層膜に側壁堆積層を化学気相成長により積層し、

金属層を前記側壁堆積層に積層して前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとして前記磁化消失層、前記第1の非磁性層および前記第1の磁性多層膜層をプラズマエッチングし、

前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとしてプラズマエッチングを行った後、前記金属層を除去し、

前記第1の非磁性層の材料および膜厚は、前記第1の磁性多層膜層の磁化方向が前記第2の磁性多層膜層の磁化方向と反平行となる材料及び膜厚とされ、

前記第2の非磁性層の材料および膜厚は、前記第2の強磁性層の磁化方向が前記第2の磁性多層膜層の磁化方向と平行となる材料及び膜厚とされ、

前記パターニングされた第2の強磁性層、第2の非磁性層、第2の磁性多層膜層、第1の非磁性層および第1の磁性多層膜層により前記磁気トンネル接合素子の積層フェリ型参照層が構成され、

前記磁化消失層の幅は、前記積層フェリ型参照層から前記第1の強磁性層への漏れ磁場の絶対値が概ね0となる幅とされていることを特徴とする磁気トンネル接合素子の製造方法。 - 請求項1ないし請求項4のいずれか一項に記載の磁気トンネル接合素子の製造方法において、

前記側壁堆積層は、シリコン酸化物またはシリコン窒化物であることを特徴とする磁気トンネル接合素子の製造方法。 - 請求項2または請求項4に記載の磁気トンネル接合素子の製造方法において、

酸化またはイオン注入により前記磁化消失層を形成することを特徴とする磁気トンネル接合素子の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017153003A JP7023637B2 (ja) | 2017-08-08 | 2017-08-08 | 磁気トンネル接合素子の製造方法 |

| KR1020170181971A KR102285125B1 (ko) | 2017-08-08 | 2017-12-28 | 자기 터널 접합 소자, 그것을 사용한 자기 메모리 및 자기 터널 접합 소자의 제조 방법 |

| TW107103019A TWI716666B (zh) | 2017-08-08 | 2018-01-29 | 磁性穿隧接合元件、使用此之磁性記憶體及磁性穿隧接合元件之製造方法 |

| US15/906,775 US11165015B2 (en) | 2017-08-08 | 2018-02-27 | Magnetic tunnel junction device, magnetoresistive random access memory using same and manufacturing method of magnetic tunnel junction device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017153003A JP7023637B2 (ja) | 2017-08-08 | 2017-08-08 | 磁気トンネル接合素子の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019033167A JP2019033167A (ja) | 2019-02-28 |

| JP2019033167A5 JP2019033167A5 (ja) | 2020-06-11 |

| JP7023637B2 true JP7023637B2 (ja) | 2022-02-22 |

Family

ID=65275889

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017153003A Active JP7023637B2 (ja) | 2017-08-08 | 2017-08-08 | 磁気トンネル接合素子の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US11165015B2 (ja) |

| JP (1) | JP7023637B2 (ja) |

| KR (1) | KR102285125B1 (ja) |

| TW (1) | TWI716666B (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2018125634A1 (en) * | 2016-12-27 | 2018-07-05 | Everspin Technologies, Inc. | Data storage in synthetic antiferromagnets included in magnetic tunnel junctions |

| CN109904309B (zh) * | 2019-03-19 | 2023-04-18 | 中国科学院微电子研究所 | 一种多态磁存储器及其制造方法 |

| CN112531106A (zh) * | 2019-09-18 | 2021-03-19 | 中电海康集团有限公司 | 磁性隧道结的制备方法 |

| US12063867B2 (en) * | 2021-08-05 | 2024-08-13 | International Business Machines Corporation | Dual spacer for double magnetic tunnel junction devices |

| WO2025197974A1 (ja) * | 2024-03-22 | 2025-09-25 | 国立大学法人東北大学 | 垂直磁化膜、垂直磁化磁気抵抗効果素子 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009514211A (ja) | 2005-10-28 | 2009-04-02 | インターナショナル・ビジネス・マシーンズ・コーポレーション | マルチコンポーネント自由層を有する磁気トンネル・ジャンクションのための調整されたピン留め層 |

| JP2013093349A (ja) | 2011-10-24 | 2013-05-16 | Toshiba Corp | 磁気記憶素子 |

| JP2014229758A (ja) | 2013-05-22 | 2014-12-08 | ソニー株式会社 | 半導体装置およびその製造方法 |

| JP2017059690A (ja) | 2015-09-16 | 2017-03-23 | 株式会社東芝 | 磁気素子及び記憶装置 |

| US20170222132A1 (en) | 2016-01-28 | 2017-08-03 | Spin Transfer Technologies, Inc. | Memory cell having magnetic tunnel junction and thermal stability enhancement layer |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6781173B2 (en) * | 2002-08-29 | 2004-08-24 | Micron Technology, Inc. | MRAM sense layer area control |

| JP2006261592A (ja) | 2005-03-18 | 2006-09-28 | Fujitsu Ltd | 磁気抵抗効果素子及びその製造方法 |

| JP2007266498A (ja) * | 2006-03-29 | 2007-10-11 | Toshiba Corp | 磁気記録素子及び磁気メモリ |

| JP2008283018A (ja) * | 2007-05-11 | 2008-11-20 | Tdk Corp | トンネル型磁気検出素子及びその製造方法 |

| JP5157268B2 (ja) * | 2007-06-13 | 2013-03-06 | 株式会社日立製作所 | スピン蓄積磁化反転型のメモリ素子及びスピンram |

| JP5260040B2 (ja) * | 2007-12-19 | 2013-08-14 | 株式会社日立製作所 | 単一方向電流磁化反転磁気抵抗効果素子と磁気記録装置 |

| US8223533B2 (en) * | 2008-09-26 | 2012-07-17 | Kabushiki Kaisha Toshiba | Magnetoresistive effect device and magnetic memory |

| US8344433B2 (en) * | 2009-04-14 | 2013-01-01 | Qualcomm Incorporated | Magnetic tunnel junction (MTJ) and methods, and magnetic random access memory (MRAM) employing same |

| US8362580B2 (en) * | 2009-12-08 | 2013-01-29 | Qualcomm Incorporated | Spin-transfer switching magnetic element utilizing a composite free layer comprising a superparamagnetic layer |

| US8981502B2 (en) * | 2010-03-29 | 2015-03-17 | Qualcomm Incorporated | Fabricating a magnetic tunnel junction storage element |

| JP5725735B2 (ja) | 2010-06-04 | 2015-05-27 | 株式会社日立製作所 | 磁気抵抗効果素子及び磁気メモリ |

| JP5492144B2 (ja) | 2011-05-27 | 2014-05-14 | 株式会社日立製作所 | 垂直磁化磁気抵抗効果素子及び磁気メモリ |

| US9054030B2 (en) * | 2012-06-19 | 2015-06-09 | Micron Technology, Inc. | Memory cells, semiconductor device structures, memory systems, and methods of fabrication |

| US8747680B1 (en) * | 2012-08-14 | 2014-06-10 | Everspin Technologies, Inc. | Method of manufacturing a magnetoresistive-based device |

| US9231191B2 (en) * | 2012-08-20 | 2016-01-05 | Industrial Technology Research Institute | Magnetic tunnel junction device and method of making same |

| US9373775B2 (en) * | 2012-09-13 | 2016-06-21 | Micron Technology, Inc. | Methods of forming magnetic memory cells |

| JP5571142B2 (ja) | 2012-09-25 | 2014-08-13 | 株式会社東芝 | 磁気メモリ |

| DE112013007149T5 (de) * | 2013-06-21 | 2016-02-25 | Intel Corporation | MTJ-Spin-Hall-MRAM-Bit-Zelle und -Anordnung |

| JP5752831B2 (ja) | 2014-05-07 | 2015-07-22 | 株式会社東芝 | 磁気メモリ |

| US9576636B1 (en) * | 2015-04-03 | 2017-02-21 | Everspin Technologies, Inc. | Magnetic memory having ROM-like storage and method therefore |

| JP2018073913A (ja) * | 2016-10-26 | 2018-05-10 | 株式会社デンソー | 磁気センサおよびその製造方法 |

| WO2018125634A1 (en) * | 2016-12-27 | 2018-07-05 | Everspin Technologies, Inc. | Data storage in synthetic antiferromagnets included in magnetic tunnel junctions |

| US10794968B2 (en) * | 2017-08-24 | 2020-10-06 | Everspin Technologies, Inc. | Magnetic field sensor and method of manufacture |

-

2017

- 2017-08-08 JP JP2017153003A patent/JP7023637B2/ja active Active

- 2017-12-28 KR KR1020170181971A patent/KR102285125B1/ko active Active

-

2018

- 2018-01-29 TW TW107103019A patent/TWI716666B/zh active

- 2018-02-27 US US15/906,775 patent/US11165015B2/en active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009514211A (ja) | 2005-10-28 | 2009-04-02 | インターナショナル・ビジネス・マシーンズ・コーポレーション | マルチコンポーネント自由層を有する磁気トンネル・ジャンクションのための調整されたピン留め層 |

| JP2013093349A (ja) | 2011-10-24 | 2013-05-16 | Toshiba Corp | 磁気記憶素子 |

| JP2014229758A (ja) | 2013-05-22 | 2014-12-08 | ソニー株式会社 | 半導体装置およびその製造方法 |

| JP2017059690A (ja) | 2015-09-16 | 2017-03-23 | 株式会社東芝 | 磁気素子及び記憶装置 |

| US20170222132A1 (en) | 2016-01-28 | 2017-08-03 | Spin Transfer Technologies, Inc. | Memory cell having magnetic tunnel junction and thermal stability enhancement layer |

Also Published As

| Publication number | Publication date |

|---|---|

| US20190051819A1 (en) | 2019-02-14 |

| TW201911536A (zh) | 2019-03-16 |

| KR102285125B1 (ko) | 2021-08-04 |

| US11165015B2 (en) | 2021-11-02 |

| KR20190016420A (ko) | 2019-02-18 |

| TWI716666B (zh) | 2021-01-21 |

| JP2019033167A (ja) | 2019-02-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5537791B2 (ja) | Mtj素子の製造方法 | |

| JP5571142B2 (ja) | 磁気メモリ | |

| JP7023637B2 (ja) | 磁気トンネル接合素子の製造方法 | |

| JP4458703B2 (ja) | 磁気抵抗効果素子、その製造方法、磁気ランダムアクセスメモリ、携帯端末装置、磁気ヘッド及び磁気再生装置 | |

| TWI575788B (zh) | 磁性記憶體及製造磁性記憶體之方法 | |

| JP2013058521A (ja) | 記憶装置及びその製造方法 | |

| KR102447763B1 (ko) | 자기 터널 접합 소자, 그것을 이용한 자기 메모리 및 자기 터널 접합 소자의 제조 방법 | |

| US20140217487A1 (en) | Stt-mram and method of manufacturing the same | |

| JP2017510995A (ja) | マルチステップ磁気トンネル接合(mtj)エッチングのための置換導電性ハードマスク | |

| KR20130069097A (ko) | 반도체 장치의 제조방법 | |

| CN110010637B (zh) | 一种自旋轨道矩磁阻式随机存储器及制备方法 | |

| JP5019344B2 (ja) | 均一な厚さのトンネル膜を有するmtj層を含む磁気抵抗メモリ及びその製造方法 | |

| JP2005064075A (ja) | 磁気記憶装置及びその製造方法 | |

| CN108780780B (zh) | 非易失性存储器装置和制造非易失性存储器装置的方法 | |

| US20130113058A1 (en) | Magnetic memory element, magnetic memory and manufacturing method of the same | |

| WO2019077661A1 (ja) | トンネル磁気抵抗効果素子、磁気メモリ、内蔵型メモリ、及びトンネル磁気抵抗効果素子を作製する方法 | |

| WO2006092849A1 (ja) | 磁気抵抗効果素子及び磁気メモリ装置 | |

| CN104471646B (zh) | 制造磁电阻的装置的方法 | |

| US20160087004A1 (en) | Magnetic memory and method of manufacturing the same | |

| JP5752831B2 (ja) | 磁気メモリ | |

| JP2005166896A (ja) | 磁気メモリ | |

| JP2002151660A (ja) | 磁気ランダム・アクセス・メモリ及びその磁気情報書き込み方法 | |

| JP3935049B2 (ja) | 磁気記憶装置及びその製造方法 | |

| CN108376690A (zh) | 一种用于制造高密度mram的自对准互联方法 | |

| JP2018147933A (ja) | 半導体素子の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200122 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200122 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200422 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20201201 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20201130 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20210126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210325 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20210824 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20211118 |

|

| C60 | Trial request (containing other claim documents, opposition documents) |

Free format text: JAPANESE INTERMEDIATE CODE: C60 Effective date: 20211118 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20211129 |

|

| C21 | Notice of transfer of a case for reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C21 Effective date: 20211130 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20220118 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20220209 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7023637 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |