JP6950737B2 - 絶縁膜の成膜方法、絶縁膜の成膜装置及び基板処理システム - Google Patents

絶縁膜の成膜方法、絶縁膜の成膜装置及び基板処理システム Download PDFInfo

- Publication number

- JP6950737B2 JP6950737B2 JP2019513266A JP2019513266A JP6950737B2 JP 6950737 B2 JP6950737 B2 JP 6950737B2 JP 2019513266 A JP2019513266 A JP 2019513266A JP 2019513266 A JP2019513266 A JP 2019513266A JP 6950737 B2 JP6950737 B2 JP 6950737B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- film

- substrate

- forming

- coating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H10P14/6927—

-

- H10P14/69215—

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B05—SPRAYING OR ATOMISING IN GENERAL; APPLYING FLUENT MATERIALS TO SURFACES, IN GENERAL

- B05D—PROCESSES FOR APPLYING FLUENT MATERIALS TO SURFACES, IN GENERAL

- B05D3/00—Pretreatment of surfaces to which liquids or other fluent materials are to be applied; After-treatment of applied coatings, e.g. intermediate treating of an applied coating preparatory to subsequent applications of liquids or other fluent materials

- B05D3/06—Pretreatment of surfaces to which liquids or other fluent materials are to be applied; After-treatment of applied coatings, e.g. intermediate treating of an applied coating preparatory to subsequent applications of liquids or other fluent materials by exposure to radiation

- B05D3/061—Pretreatment of surfaces to which liquids or other fluent materials are to be applied; After-treatment of applied coatings, e.g. intermediate treating of an applied coating preparatory to subsequent applications of liquids or other fluent materials by exposure to radiation using U.V.

- B05D3/065—After-treatment

- B05D3/067—Curing or cross-linking the coating

-

- H10P14/6342—

-

- H10P14/6538—

-

- H10P14/668—

-

- H10P14/6689—

-

- H10P72/0402—

-

- H10P72/0431—

-

- H10P72/0432—

-

- H10P72/0448—

-

- H10P72/0458—

-

- H10P72/0602—

-

- H10P72/3302—

-

- H10P72/3406—

-

- H10P72/7612—

-

- H10P95/90—

-

- H10W10/014—

-

- H10W10/17—

-

- H10W20/01—

-

- H10P14/6686—

-

- H10P14/6922—

-

- H10P50/283—

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Plasma & Fusion (AREA)

- Formation Of Insulating Films (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Element Separation (AREA)

- Robotics (AREA)

Description

酸化シリコンを含む絶縁膜を形成するための前駆体を溶媒に溶解させた塗布液を基板に塗布して塗布膜を形成する工程と、

前記塗布膜中の溶媒を揮発させる溶媒揮発工程と、

この工程の後、前記前駆体を構成する分子団に未結合手を生成するために、大気よりも酸素濃度が低い低酸素雰囲気で前記塗布膜にエネルギーを供給するエネルギー供給工程と、

その後、前記基板を加熱し、前記前駆体を架橋させて絶縁膜を形成するキュア工程と、を含むことを特徴とする。

酸化シリコンを含む絶縁膜を形成するための前駆体を溶媒に溶解させた塗布液を基板に塗布して塗布膜を形成するための塗布モジュールと、

前記塗布膜中の溶媒を揮発させるための溶媒揮発モジュールと、

前記前駆体を活性化させるために、溶媒が揮発された塗布膜に対して、大気よりも酸素濃度が低い低酸素雰囲気でエネルギーを供給するためのエネルギー供給モジュールと、

前記エネルギー供給モジュールにて処理された後の基板を加熱し、前記前駆体を架橋させて絶縁膜を形成するためのキュアモジュールと、

各モジュールの間で基板を搬送するための基板搬送機構と、を備えたことを特徴とする。

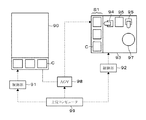

基板を搬送容器に入れて搬入出するための搬入出ポートと、酸化シリコンを含む絶縁膜を形成するための前駆体を溶媒に溶解させた塗布液を基板に塗布して塗布膜を形成するための塗布モジュールと、前記塗布膜中の溶媒を揮発させるための溶媒揮発モジュールと、前記前駆体を活性化させるために、溶媒が揮発された塗布膜に対して、大気よりも酸素濃度が低い低酸素雰囲気でエネルギーを供給するためのエネルギー供給モジュールと、各モジュール及び前記搬入出ポートの間で基板を搬送するための基板搬送機構と、を備えた基板処理装置と、

前記エネルギー供給モジュールにて処理された後の基板を加熱し、前記前駆体を架橋させて絶縁膜を形成するためのキュア装置と、

前記基板処理装置の前記搬入出ポートと前記キュア装置との間で前記搬送容器を搬送するための容器搬送機構と、を備えたことを特徴とする。

本発明の実施形態の詳細について説明する前に、本発明の概要について述べておく。本発明の絶縁膜の成膜方法の一例として、酸化シリコンを含む絶縁膜の前駆体を含む塗布液を基板に塗布し、得られた塗布膜を加熱して塗布膜中の溶媒を揮発させ、次いで基板を加熱して塗布膜中の分子団の再配列を行い、その後、塗布膜に紫外線を照射し、しかる後、塗布膜をキュアする工程が挙げられる。

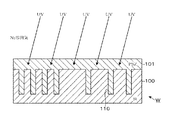

この工程が行われる雰囲気において酸素濃度が高いと、紫外線の照射により生成された未結合手を有するオリゴマー同士が瞬時で結合し、結合されたオリゴマーの中に、孤立したオリゴマーが閉じ込められ、結果として絶縁膜の緻密性が低くなる。

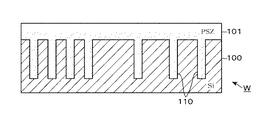

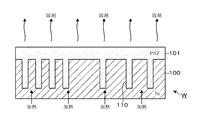

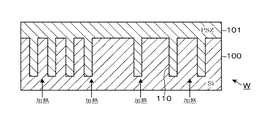

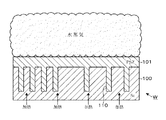

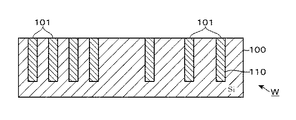

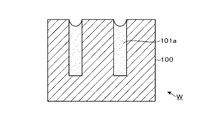

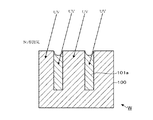

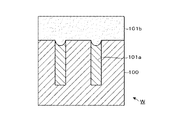

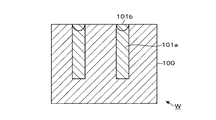

次に本発明の絶縁膜の成膜方法の実施の形態について詳述する。この例では、被処理基板に対してSTIを行うプロセスについて説明する。図3に示すように被処理基板であるウエハWには、シリコン膜100に溝部(トレンチ)110が形成されており、そしてSOG膜の前駆体を有機溶剤に溶解した塗布液をウエハWに塗布することにより、トレンチ110を埋めるように塗布膜101が形成される。前駆体としては、例えば−(SiH2NH)‐を基本構造とするポリマーであるポリシラザンが用いられる。塗布液は、例えば流動性を良くするためにポリシラザンの分子団がオリゴマーの状態で溶解している。そのため図3に示すように、例えばスピンコーティングによりウエハWに塗布したときに塗布液が細いトレンチ110内に進入しやすく埋め込み性の良好な塗布膜101が得られる。なお図3〜図10では、塗布膜101にPSZ(ポリシラザン)と記載している。

なお絶縁膜の成膜装置は、CMPを行う研磨装置を備えてもよく、例えば一方のキュアモジュール6に代えて研磨装置を設けてもよい。そしてキュアモジュール6にてキュア処理を行った後のウエハWをCMPにより研磨するように構成してもよい。

またリフローモジュール4は、加熱機構34により、ウエハWが200〜300℃に加熱するように構成されたことを除いて溶媒揮発モジュール3とほぼ同様に構成されている。

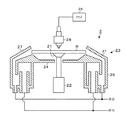

筐体50の内部は、搬入出口51から見て手前側にウエハWを搬送する搬送アーム53が設けられている。搬送アーム53は、クーリングプレートとして構成され、例えばリフロー工程後、紫外線照射処理の前に、ウエハWを常温(25℃)まで冷却できるように構成されている。搬入出口71から見て奥側には、ウエハWの載置台54が配置されている。載置台54及び搬送アーム53の下方にはウエハの受け渡しを行うための昇降ピン56、58が夫々設けられ、昇降ピン56、58は、夫々昇降機構57、59により昇降するように構成されている。

そして載置台54に載置されたウエハWに紫外線を照射するときには、ガス供給部73からN2ガスを供給すると共に排気を行い、ウエハWの雰囲気を例えば400ppm以下より好ましくは50ppm以下の低酸素雰囲気、例えばN2ガス雰囲気とするように構成されている。搬送アームに53にて常温まで冷却されたウエハWが載置台54に載置されると、N2ガス供給源75からN2ガスを供給し、低酸素雰囲気とした状態でウエハWに例えば4000mJ/cm2のエネルギーが照射される

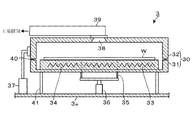

そして既述のように紫外線照射処理を行ったウエハWが載置台63に載置されると、処理容器60内に水蒸気を満たすと共にウエハWを400℃で30分、450℃で120分段階的に加熱した後、水蒸気の供給を停止し、窒素ガス雰囲気下で450℃で30分加熱する。

また本発明は、低誘電率膜などの層間絶縁膜の成膜に適用してもよい。層間絶縁膜の成膜にあたっては、配線材料である銅のマイグレーションや拡散を抑えるために、加熱温度は、450℃以下、例えば400℃以下にすることが要請されている。また層間絶縁膜を十分な硬度に構成する観点から300℃以上出ることが好ましい。本発明ではキュア温度が低温であっても良質な膜質の絶縁膜が得られることから、層間絶縁膜の成膜に適用することが期待できる。また例えば細い溝部が形成された基板に絶縁膜を形成する例としてPMD(Pre Metal Dielectric)に適用してもよい。

さらに1回目の塗布処理及び2回目の塗布処理における溶剤を揮発させた後に、例えばウエハWを250℃で加熱するリフロー工程を行うようにしてもよい。

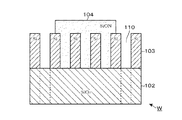

SiON膜104を成膜するにあたっては、例えば前駆体としてポリシラザンを含んだ塗布液をウエハWに向けて塗布する。その後図3〜図6に示したように、塗布膜101を例えば150℃で3分加熱して塗布膜101中の溶剤を揮発させた後、250℃で加熱して塗布膜101のリフローを行う。次いで塗布膜101に向けて、低酸素雰囲気下で5000J/cm2以下の紫外線を照射する。その後、キュアモジュール6において、N2ガス雰囲気下でウエハWを400℃、450℃で段階的に加熱するキュア工程を行う。

そのため紫外線を照射する温度は、350℃以下であることが好ましい。また紫外線照射時に架橋の進行しない温度であることが要件であることから、リフロー工程において紫外線を照射するようにしてもよい。しかしながら溶剤揮発工程においては、溶媒である溶剤が紫外線の照射により変質するおそれもある。そのため、溶剤揮発工程以後である必要がある。

また溶剤揮発工程に用いる塗布膜101中の溶剤を揮発させる装置は、例えば密閉した処理容器内を例えば大気圧の半分まで減圧し、処理容器内に載置したウエハWにおける溶剤の揮発を促進して溶剤を揮発させる装置でも良い。

本発明の実施の形態の効果を検証するために以下の試験を行った。図17に示した基板処理システムを用い、評価用のウエハWに絶縁膜を成膜し、絶縁膜のエッチング強度について評価した。

[実施例1]

絶縁膜の成膜方法における紫外線照射工程においてN2ガス雰囲気下で主たる波長が172nmの紫外線をドーズ量が2000mJ/cm2となるように照射した例を実施例1−1とした。なおウエハWは、実施の形態に示した塗布液を塗布した後、溶剤揮発工程において、ウエハWを150℃で3分加熱し、その後リフロー工程を行わずに、紫外線照射工程を行った。続くキュア工程においては、熱処理炉内において、水蒸気を供給した状態で、400℃で30分、450℃で120分の2段階の加熱を行った後、N2ガス雰囲気下で450℃で30分加熱した。なお塗布膜の目標膜厚は100nmとした。

[比較例1、2]

また紫外線照射工程において、大気雰囲気にて2000mJ/cm2の紫外線を照射したことを除いて、実施例1−1と同様に処理した例を比較例1とした。また紫外線照射を行わないことを除いて、実施例1−1と同様に処理した例を比較例2とした。

比較例1、2における相対的エッチングレートは、夫々3.74、5.55であった。これに対して、実施例1における相対的エッチングレートは、2.04であった。

この結果によれば、ポリシラザンを含む塗布液をウエハWに塗布し絶縁膜を成膜するにあたって、キュア工程前の塗布膜にN2ガス雰囲気下で紫外線のエネルギーを照射することにより、エッチング強度を高めることができるといえる。

また紫外線をドーズ量を3000及び4000mJ/cm2に設定した場合において、相対的エッチングレートを評価したところ各々2.70.2.42であり、4000mJ/cm2程度の紫外線のドーズ量においても強度の高い絶縁膜を得ることができた。

またウエハWへの塗布液の塗布と、塗布膜への紫外線照射処理と、を複数回繰り返した後、キュア処理を行うことの効果を検証するため、以下の実施例に従って図17に示した基板処理システムを用い、ウエハWに絶縁膜を成膜し、実施例1と同様に相対的エッチングレートを求め、絶縁膜のエッチング強度について評価した。

[実施例2−1]

評価用のウエハWに1回目の塗布液を塗布した後、溶剤揮発工程において、ウエハWを150℃で3分加熱し、その後リフロー工程を行わずに、実施の形態と同様に紫外線照射工程を行った。紫外線照射工程においてN2ガス雰囲気下で照射する波長172nmの紫外線のドーズ量を4000mJ/cm2に設定した。さらに2回目の塗布液の塗布として、1回目の塗布液と同量の塗布液を塗布した後、溶剤揮発工程において、ウエハWを150℃で3分加熱し、その後リフロー工程を行わずに、実施の形態と同様に紫外線照射工程を行った。その後実施例1と同様のキュア工程を行った例を実施例2−1とした。なお1回目の塗布液を塗布及び2回目の塗布液の塗布における塗布液の供給量は、凡そ実施例1と同様であり、キュア処理後の塗布膜の目標膜厚は200nmとした。

塗布液の塗布量を実施例1の凡そ2倍の量として、塗布膜の目標膜厚を200nmとして成膜し、紫外線照射工程においてN2ガス雰囲気下で照射する波長172nmの紫外線のドーズ量を4000mJ/cm2に設定したことを除いて、実施例1と同様に処理した例を実施例2−2とした。

実施例2−1及び2−2における相対的エッチングレートは、夫々2.27、2.56であった。実施例2−1及び2−2のいずれにおいても相対的エッチングレートが低くなっており、エッチング強度が高いことが分かる。また実施例2−2と比較して、実施例2−1はさらに相対的エッチングレートが低くなっていることが分かる。

この結果によれば、ウエハWへの塗布液の塗布と、塗布膜への紫外線照射処理と、を複数回繰り返すことにより、より緻密で良好な絶縁膜を得ることができると言える。

また溶剤揮発工程におけるウエハWの加熱温度による効果を検証するため、以下の実施例に従って図17に示した基板処理システムを用い、ウエハWに絶縁膜を成膜し、絶縁膜のエッチング強度について評価した。

[実施例3−1]

ウエハWは、実施の形態に示した塗布液を塗布した後、溶剤揮発工程において、ウエハWを150℃で3分加熱し、その後リフロー工程を行わずに、紫外線照射工程を行った。続くキュア工程においては、熱処理炉内において、水蒸気を供給した状態で、400℃で30分、450℃で120分の2段階の加熱を行った後、N2ガス雰囲気下で450℃で30分加熱した。なお塗布膜の目標膜厚は100nmとした。

[実施例3−2、3−3]

溶剤揮発工程におけるウエハWの加熱温度を200℃、250℃に設定したことを除いて実施例3−1と同様に処理した例を、夫々実施例3−2〜3−3とした。

3 溶媒揮発モジュール

4 リフローモジュール

5 紫外線照射モジュール

6 キュアモジュール

9、90、92 制御部

99 上位コンピュータ

100 シリコン膜

101 塗布膜

W ウエハ

Claims (16)

- シャロートレンチアイソレーションの溝部に絶縁膜を成膜する方法において、

酸化シリコンを含む絶縁膜を形成するための前駆体を溶媒に溶解させた塗布液を基板に塗布して塗布膜を形成する工程と、

前記塗布膜中の溶媒を揮発させる溶媒揮発工程と、

この工程の後、前記前駆体を構成する分子団に未結合手を生成するために、大気よりも酸素濃度が低い低酸素雰囲気で前記塗布膜にエネルギーを供給するエネルギー供給工程と、

その後、前記基板を加熱し、前記前駆体を架橋させて絶縁膜を形成するキュア工程と、を含むことを特徴とする絶縁膜の成膜方法。 - 前記溶媒を揮発させる工程の後、塗布膜中の分子団を再配列するために基板を加熱するリフロー工程を行うことを特徴とする請求項1に記載の絶縁膜の成膜方法。

- 前記エネルギー供給工程は、前記リフロー工程の後、基板の温度を降温させた状態で行われることを特徴とする請求項2記載の絶縁膜の成膜方法。

- 前記エネルギー供給工程が行われる低酸素雰囲気は、酸素濃度が400ppm以下であることを特徴とする請求項1に記載の絶縁膜の成膜方法。

- 前記低酸素雰囲気は、不活性ガスを含む雰囲気であることを特徴とする請求項1に記載の絶縁膜の成膜方法。

- 前記エネルギーは、主たる波長が200nmよりも短い紫外線のエネルギーであることを特徴とする請求項1に記載の絶縁膜の成膜方法。

- 前記塗布膜に供給される紫外線のエネルギーは、5000mJ/cm2以下のエネルギーであることを特徴とする請求項6に記載の絶縁膜の成膜方法。

- 前記塗布膜を形成する工程から前記エネルギーを供給する工程までの工程群を複数回繰り返し、その後前記キュア工程を行うことを特徴とする請求項1の絶縁膜の成膜方法。

- 前記キュア工程は、基板を水蒸気雰囲気下で加熱することを特徴とする請求項1に記載の絶縁膜の成膜方法。

- 前記キュア工程における基板の加熱温度は300℃以上450℃以下であることを特徴とする請求項1に記載の絶縁膜の成膜方法。

- 基板である半導体ウエハ上のシャロートレンチアイソレーションの溝部に絶縁膜を成膜するための成膜装置において、

酸化シリコンを含む絶縁膜を形成するための前駆体を溶媒に溶解させた塗布液を基板に塗布して塗布膜を形成するための塗布モジュールと、

前記塗布膜中の溶媒を揮発させるための溶媒揮発モジュールと、

前記前駆体を活性化させるために、溶媒が揮発された塗布膜に対して、大気よりも酸素濃度が低い低酸素雰囲気でエネルギーを供給するためのエネルギー供給モジュールと、

前記エネルギー供給モジュールにて処理された後の基板を加熱し、前記前駆体を架橋させて絶縁膜を形成するためのキュアモジュールと、

各モジュールの間で基板を搬送するための基板搬送機構と、を備えたことを特徴とする絶縁膜の成膜装置。 - 前記溶媒揮発モジュールは、基板を加熱する溶媒加熱用の加熱モジュールであることを特徴とする請求項11に記載の絶縁膜の成膜装置。

- 溶媒が揮発された塗布膜中の分子団を再配列するために基板を加熱するリフロー用の加熱モジュールを備えていることを特徴とする請求項11に記載の絶縁膜の成膜装置。

- 前記エネルギー供給モジュールは、主たる波長が200nmよりも短い紫外線を塗布膜に照射するためのモジュールであることを特徴とする請求項11に記載の絶縁膜の成膜装置。

- 前記キュアモジュールは、基板に水蒸気を供給して加熱することを特徴とする請求項11に記載の絶縁膜の成膜装置。

- 基板である半導体ウエハ上のシャロートレンチアイソレーションの溝部に絶縁膜を成膜するための基板処理システム-において、

基板を搬送容器に入れて搬入出するための搬入出ポートと、酸化シリコンを含む絶縁膜を形成するための前駆体を溶媒に溶解させた塗布液を基板に塗布して塗布膜を形成するための塗布モジュールと、前記塗布膜中の溶媒を揮発させるための溶媒揮発モジュールと、前記前駆体を活性化させるために、溶媒が揮発された塗布膜に対して、大気よりも酸素濃度が低い低酸素雰囲気でエネルギーを供給するためのエネルギー供給モジュールと、各モジュール及び前記搬入出ポートの間で基板を搬送するための基板搬送機構と、を備えた基板処理装置と、

前記エネルギー供給モジュールにて処理された後の基板を加熱し、前記前駆体を架橋させて絶縁膜を形成するためのキュア装置と、

前記基板処理装置の前記搬入出ポートと前記キュア装置との間で前記搬送容器を搬送するための容器搬送機構と、を備えたことを特徴とする基板処理システム。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017081595 | 2017-04-17 | ||

| JP2017081595 | 2017-04-17 | ||

| PCT/JP2018/009752 WO2018193753A1 (ja) | 2017-04-17 | 2018-03-13 | 絶縁膜の成膜方法、絶縁膜の成膜装置及び基板処理システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2018193753A1 JPWO2018193753A1 (ja) | 2020-02-20 |

| JP6950737B2 true JP6950737B2 (ja) | 2021-10-13 |

Family

ID=63855699

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019513266A Active JP6950737B2 (ja) | 2017-04-17 | 2018-03-13 | 絶縁膜の成膜方法、絶縁膜の成膜装置及び基板処理システム |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US11631581B2 (ja) |

| JP (1) | JP6950737B2 (ja) |

| KR (1) | KR102595053B1 (ja) |

| CN (1) | CN110546744B (ja) |

| TW (1) | TWI793115B (ja) |

| WO (1) | WO2018193753A1 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11387138B2 (en) * | 2018-09-25 | 2022-07-12 | Taiwan Semiconductor Manufacturing Co., Ltd. | Integrated circuit isolation feature and method of forming the same |

| CN116508131A (zh) * | 2020-11-20 | 2023-07-28 | 默克专利有限公司 | 制造硅质含氮膜的方法 |

| KR20250007571A (ko) * | 2022-04-18 | 2025-01-14 | 메르크 파텐트 게엠베하 | 홈을 갖는 기판 상에 질화규소 필름을 제조하는 방법 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5747623A (en) * | 1994-10-14 | 1998-05-05 | Tonen Corporation | Method and composition for forming ceramics and article coated with the ceramics |

| JP4398580B2 (ja) * | 2000-10-18 | 2010-01-13 | グンゼ株式会社 | パタ−ン状二酸化ケイ素転化膜の形成方法 |

| JP4542977B2 (ja) * | 2005-10-27 | 2010-09-15 | 東京エレクトロン株式会社 | 塗布膜の成膜方法及びその装置 |

| JP2009076869A (ja) * | 2007-08-24 | 2009-04-09 | Tokyo Electron Ltd | 基板の処理方法、プログラム及びコンピュータ記憶媒体 |

| US7588968B1 (en) * | 2008-03-31 | 2009-09-15 | Intel Corporation | Linked chip attach and underfill |

| US8466067B2 (en) * | 2009-10-05 | 2013-06-18 | Applied Materials, Inc. | Post-planarization densification |

| CN102569060B (zh) * | 2010-12-22 | 2015-03-11 | 第一毛织株式会社 | 形成硅氧层的组合物及其生产方法、利用其的硅氧层及生产硅氧层的方法 |

| JP5710308B2 (ja) | 2011-02-17 | 2015-04-30 | メルクパフォーマンスマテリアルズIp合同会社 | 二酸化ケイ素膜の製造方法 |

| KR101736888B1 (ko) * | 2011-06-22 | 2017-05-17 | 메르크 파텐트 게엠베하 | 실리콘 옥시나이트라이드 막의 형성 방법 및 이 방법에 의해 제조된 실리콘 옥시나이트라이드 막을 가지는 기판 |

| CN103999198B (zh) * | 2011-11-01 | 2016-08-24 | 株式会社日立国际电气 | 半导体器件的制造方法、半导体器件的制造装置及记录介质 |

| WO2013161809A1 (ja) * | 2012-04-26 | 2013-10-31 | コニカミノルタ株式会社 | ガスバリア性フィルム、およびこれを用いる電子デバイス |

| JPWO2014104295A1 (ja) * | 2012-12-28 | 2017-01-19 | コニカミノルタ株式会社 | 発光装置 |

| JP5929775B2 (ja) * | 2013-02-08 | 2016-06-08 | コニカミノルタ株式会社 | ガスバリア性フィルムおよびその製造方法、ならびに前記ガスバリア性フィルムを含む電子デバイス |

| CN105246683A (zh) * | 2013-05-28 | 2016-01-13 | 柯尼卡美能达株式会社 | 阻气性膜及其制造方法 |

| US9691935B2 (en) * | 2013-07-04 | 2017-06-27 | Toray Industries, Inc. | Impurity-diffusing composition and method for producing semiconductor element |

| US10113236B2 (en) * | 2014-05-14 | 2018-10-30 | Applied Materials, Inc. | Batch curing chamber with gas distribution and individual pumping |

| US9847245B1 (en) * | 2016-06-16 | 2017-12-19 | Samsung Electronics Co., Ltd. | Filling processes |

| JP6807236B2 (ja) * | 2017-01-13 | 2021-01-06 | 東京応化工業株式会社 | 組成物及びシリカ質膜の製造方法 |

| CN111052321B (zh) * | 2017-09-11 | 2023-10-24 | 东京毅力科创株式会社 | 绝缘膜的成膜方法、基板处理装置和基板处理系统 |

-

2018

- 2018-03-13 JP JP2019513266A patent/JP6950737B2/ja active Active

- 2018-03-13 KR KR1020197032595A patent/KR102595053B1/ko active Active

- 2018-03-13 WO PCT/JP2018/009752 patent/WO2018193753A1/ja not_active Ceased

- 2018-03-13 US US16/604,744 patent/US11631581B2/en active Active

- 2018-03-13 CN CN201880025732.2A patent/CN110546744B/zh active Active

- 2018-04-12 TW TW107112470A patent/TWI793115B/zh active

Also Published As

| Publication number | Publication date |

|---|---|

| KR102595053B1 (ko) | 2023-10-30 |

| US11631581B2 (en) | 2023-04-18 |

| JPWO2018193753A1 (ja) | 2020-02-20 |

| TW201903901A (zh) | 2019-01-16 |

| CN110546744A (zh) | 2019-12-06 |

| WO2018193753A1 (ja) | 2018-10-25 |

| KR20190139921A (ko) | 2019-12-18 |

| US20200211838A1 (en) | 2020-07-02 |

| CN110546744B (zh) | 2023-10-20 |

| TWI793115B (zh) | 2023-02-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10068765B2 (en) | Multi-step system and method for curing a dielectric film | |

| TWI613724B (zh) | 使用有機胺基矽烷退火形成SiOCH膜的方法 | |

| TWI464805B (zh) | 低介電常數介電質之整合方法 | |

| US20140235068A1 (en) | Method of manufacturing semiconductor device, apparatus for manufacturing semiconductor device, and non-transitory computer-readable recording medium | |

| WO2009111473A2 (en) | Method for curing a porous low dielectric constant dielectric film | |

| JP6950737B2 (ja) | 絶縁膜の成膜方法、絶縁膜の成膜装置及び基板処理システム | |

| KR20120025543A (ko) | 성막 방법, 전 처리 장치 및 처리 시스템 | |

| KR101131640B1 (ko) | 폴리실라잔막의 처리 방법 | |

| US11823897B2 (en) | Method for forming insulating film, apparatus for processing substrate, and system for processing substrate | |

| TWI851635B (zh) | 在溝槽上面形成低k可流動介電膜的方法 | |

| CN1276480C (zh) | 有机硅氧烷膜的处理方法及装置 | |

| JP2009076869A (ja) | 基板の処理方法、プログラム及びコンピュータ記憶媒体 | |

| US20090226695A1 (en) | Method for treating a dielectric film with infrared radiation |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20191009 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20201208 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20210205 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210316 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210824 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210906 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6950737 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |