以下、本発明を具体化した実施形態を図面に基づいて説明する。

[第1実施形態]

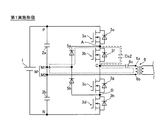

図1〜図8を参照して、第1実施形態による3レベル電力変換装置100の構成について説明する。

(3レベル電力変換装置の構成)

まず、図1を参照して、3レベル電力変換装置100の構成について説明する。図1に示すように、3レベル電力変換装置100は、直流電源1を備える。また、3レベル電力変換装置100は、直流電源1に並列に接続されるコンデンサ回路2を備える。コンデンサ回路2は、互いに直列に接続されたコンデンサ2aとコンデンサ2bとを含む。なお、直流電源1は、直流電圧Eを出力する。

また、3レベル電力変換装置100は、コンデンサ回路2に並列に接続されるスイッチング回路3を備える。スイッチング回路3において、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、第4半導体スイッチング素子3dがこの順に正電圧側から負電圧側に向かって直列に接続されている。また、スイッチング回路3は、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、および、第4半導体スイッチング素子3dの各々に逆並列に接続された、ダイオード3e、ダイオード3f、ダイオード3g、および、ダイオード3hを含む。なお、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、および、第4半導体スイッチング素子3dの各々は、多層配線基板4(図2参照)上に実装されている。

また、3レベル電力変換装置100には、ダイオード5aとダイオード5bとが設けられている。ダイオード5aは、コンデンサ2aとコンデンサ2bとの間の直流中点M(M1)と、第1半導体スイッチング素子3aと第2半導体スイッチング素子3bとの間の接続点Aとの間に設けられている。具体的には、ダイオード5aのアノードと直流中点M(M1)とが接続されている。また、ダイオード5aのカソードと接続点Aとが接続されている。

また、ダイオード5bは、直流中点M1と、第3半導体スイッチング素子3cおよび第4半導体スイッチング素子3dの間の接続点Bとの間に設けられている。具体的には、ダイオード5bのカソードと直流中点M1とが接続されている。また、ダイオード5bのアノードと接続点Bとが接続されている。また、ダイオード5aのアノードとダイオード5bのカソードとは接続されている。

また、3レベル電力変換装置100には、絶縁トランス6が設けられている。絶縁トランス6の一方側の端子6aは、第2半導体スイッチング素子3bと第3半導体スイッチング素子3cとの間の接続点Cに接続されている。また、絶縁トランス6の他方側の端子6bは、コンデンサ2aとコンデンサ2bとの間の直流中点M(M2)に接続されている。なお、絶縁トランス6の端子6aと接続点Cとの間には、直流カット用コンデンサ6cが設けられている。

また、3レベル電力変換装置100は、絶縁トランス6の2次側に設けられる整流回路101を含む。スイッチング回路3に含まれる各半導体スイッチング素子のスイッチングにより絶縁トランス6に印加される電圧Vt(高周波交流)は、絶縁トランス6により整流回路101に伝達される。そして、整流回路101により交流から直流に変換された電圧が、整流回路101に並列に接続されている負荷102に印加される。すなわち、3レベル電力変換装置100は、DC/DCコンバータとして機能する。なお、整流回路101は、ダイオード、リアクタンス、および、コンデンサからなる回路であるが、整流回路101の回路構成はこれに限られない。

なお、第1半導体スイッチング素子3aおよび第2半導体スイッチング素子3bがオンで、かつ、第3半導体スイッチング素子3cおよび第4半導体スイッチング素子3dがオフである場合には、Vt=E/2となる。また、第3半導体スイッチング素子3cおよび第4半導体スイッチング素子3dがオンで、かつ、第1半導体スイッチング素子3aおよび第2半導体スイッチング素子3bがオフである場合には、Vt=−E/2となる。また、第2半導体スイッチング素子3bおよび第3半導体スイッチング素子3cがオンで、かつ、第1半導体スイッチング素子3aおよび第4半導体スイッチング素子3dがオフである場合には、Vt=0となる。

Vt=E/2である期間、Vt=0である期間、および、Vt=−E/2である期間の比率が制御(PWM制御)されることにより、負荷102に印加される電圧が制御される。

図2に示すように、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、および、第4半導体スイッチング素子3dは、多層配線基板4の実装面4a上において、所定の方向(X方向)に並んで配置されている。なお、図2は概略図である。

また、多層配線基板4は、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、および、第4半導体スイッチング素子3dの各々のソース端子Sに接続されている、ソース端子側基板配線10a、ソース端子側基板配線10b、ソース端子側基板配線10c、および、ソース端子側基板配線10dを含む。また、多層配線基板4は、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、および、第4半導体スイッチング素子3dの各々のドレイン端子D(図2(b)参照)に接続されている、ドレイン端子側基板配線20a、ドレイン端子側基板配線20b、ドレイン端子側基板配線20c、および、ドレイン端子側基板配線20dを含む。なお、上記の各ソース端子側基板配線(10a、10b、10c、10d)および各ドレイン端子側基板配線(20a、20b、20c、20d)により、接続されている半導体スイッチング素子(3a、3b、3c、3d)の放熱(冷却)がされている。

また、ソース端子側基板配線10aとドレイン端子側基板配線20bとの組、ソース端子側基板配線10bとドレイン端子側基板配線20cとの組、および、ソース端子側基板配線10cとドレイン端子側基板配線20dとの組の各々は、一体的に形成されている。

また、第1半導体スイッチング素子3aのソース端子側基板配線10aとドレイン端子側基板配線20aとの間には、寄生容量Cs1(図4参照)が生じる。また、第2半導体スイッチング素子3bのソース端子側基板配線10bとドレイン端子側基板配線20bとの間には、寄生容量Cs2(図6参照)が生じる。第3半導体スイッチング素子3cのソース端子側基板配線10cとドレイン端子側基板配線20cとの間には、寄生容量Cs3(図示せず)が生じる。また、第4半導体スイッチング素子3dのソース端子側基板配線10dとドレイン端子側基板配線20dとの間には、寄生容量Cs4(図示せず)が生じる。

ここで、第1実施形態では、寄生容量Cs1と寄生容量Cs4とが互いに等しいとともに、寄生容量Cs2と寄生容量Cs3とが互いに等しくなるように、多層配線基板4の実装面4aに略垂直な方向(Z1方向側)から見て、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、および、第4半導体スイッチング素子3dの各々の、ソース端子側基板配線(10a、10b、10c、10d)とドレイン端子側基板配線(20a、20b、20c、20d)との重なり具合が調整されている。なお、重なり具合とは、たとえば多層配線基板4の実装面に略垂直な方向(Z1方向側)から見て、ソース端子側基板配線(10a、10b、10c、10d)とドレイン端子側基板配線(20a、20b、20c、20d)とが重なっている面積のことである。ただし、ソース端子側基板配線(10a、10b、10c、10d)とドレイン端子側基板配線(20a、20b、20c、20d)とが重なることで形成される寄生容量が等しく調整されていればこれに限らない。

具体的には、寄生容量Cs1と寄生容量Cs4とが互いに等しくなるように、多層配線基板4の実装面4aに略垂直な方向(Z1方向側)から見て、第1半導体スイッチング素子3aのソース端子側基板配線10aおよびドレイン端子側基板配線20aの重なり具合と、第4半導体スイッチング素子3dのソース端子側基板配線10dおよびドレイン端子側基板配線20dの重なり具合とが同一になるように調整されている。また、寄生容量Cs2と寄生容量Cs3とが互いに等しくなるように、多層配線基板4の実装面4aに略垂直な方向(Z1方向側)から見て、第2半導体スイッチング素子3bのソース端子側基板配線10bおよびドレイン端子側基板配線20bの重なり具合と、第3半導体スイッチング素子3cのソース端子側基板配線10cおよびドレイン端子側基板配線20cの重なり具合とが同一になるように調整されている。

詳細には、多層配線基板4の実装面4aに略垂直な方向(Z1方向側)から見て、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、および、第4半導体スイッチング素子3dの各々の、ソース端子側基板配線(10a、10b、10c、10d)とドレイン端子側基板配線(20a、20b、20c、20d)とは互いに重ならないように調整されている。すなわち、寄生容量Cs1、Cs2、Cs3、および、Cs4は互いに略等しい。

また、第1実施形態では、図2(b)に示すように、第1半導体スイッチング素子3aのドレイン端子側基板配線20aのうちの一部は、第1半導体スイッチング素子3aのソース端子側基板配線10aが配線されている多層配線基板4内の配線層とは異なる層の配線層を含んでいる。また、第4半導体スイッチング素子3dのソース端子側基板配線10dのうちの一部は、第4半導体スイッチング素子3dのドレイン端子側基板配線20dが配線されている多層配線基板4内の配線層とは異なる層の配線層を含んでいる。

具体的には、第1半導体スイッチング素子3aのドレイン端子側基板配線20a、および、第4半導体スイッチング素子3dのソース端子側基板配線10dの各々は、互いに異なる4層の配線層からなる。また、第1半導体スイッチング素子3aのソース端子側基板配線10a、および、第4半導体スイッチング素子3dのドレイン端子側基板配線20dの各々は、互いに異なる2層の配線層からなる。なお、互いに異なる配線層に配線されている共通の基板配線は、ビア103により電気的に接続されている。

詳細には、第1半導体スイッチング素子3aのドレイン端子側基板配線20aのZ2方向側の2つの配線層は、第1半導体スイッチング素子3aのソース端子側基板配線10aが配線されている配線層とは異なる。また、第4半導体スイッチング素子3dのソース端子側基板配線10dのZ2方向側の2つの配線層は、第4半導体スイッチング素子3dのドレイン端子側基板配線20dが配線されている配線層とは異なる。

これにより、第1半導体スイッチング素子3aのソース端子側基板配線10aとドレイン端子側基板配線20aとの間の寄生容量Cs1が増加するのを抑制しながら、ソース端子側基板配線10aが配線されている配線層とは異なる層に配線されているドレイン端子側基板配線20aを設けることによって、第1半導体スイッチング素子3aのドレイン容量(ドレイン側の容量)を増加させることが可能である。また、同様に、第4半導体スイッチング素子3dのソース端子側基板配線10dとドレイン端子側基板配線20dとの間の寄生容量Cs4が増加するのを抑制しながら、第4半導体スイッチング素子3dのソース容量(ソース側の容量)を増加させることが可能である。

なお、第2半導体スイッチング素子3bのソース端子側基板配線10b(第3半導体スイッチング素子3cのドレイン端子側基板配線20c)は、第1半導体スイッチング素子3aのソース端子側基板配線10a(第4半導体スイッチング素子3dのドレイン端子側基板配線20d)が配線されている2つの配線層と同じ層に配線されている。なお、各半導体スイッチング素子(3a、3b、3c、3d)のソース端子側基板配線(10a、10b、10c、10d)およびドレイン端子側基板配線(20a、20b、20c、20d)の配線層数および配線層の高さ位置などは一例であり、上記した構成に限られない。

(3レベル電力変換装置の動作)

まず、図3〜図8を参照して、3レベル電力変換装置100の動作について説明する。図3に示すように、第1半導体スイッチング素子3aおよび第2半導体スイッチング素子3bがオンで、かつ、第3半導体スイッチング素子3cおよび第4半導体スイッチング素子3dがオフである状態(正電圧モード)では、コンデンサ2aの放電により、電流(図3の破線の矢印)が、コンデンサ2a、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、直流カット用コンデンサ6c、絶縁トランス6のルートを流れる。なお、コンデンサ2aに流れる電流波形(図7の実線を参照)、および、コンデンサ2bに流れる電流波形(図7の破線を参照)に示すように、この正電圧モード中(図7参照)では、コンデンサ2aは放電されているとともにコンデンサ2bは充電されている。

次に、図4に示すように、正電圧モード中に第1半導体スイッチング素子3aだけがオフされる。この場合、コンデンサ2aの放電により、電流(図4の破線の矢印)が、コンデンサ2a、寄生容量Cs1、第2半導体スイッチング素子3b、直流カット用コンデンサ6c、絶縁トランス6のルートを流れる。これにより、第1半導体スイッチング素子3aの寄生容量Cs1が、コンデンサ2aの放電により充電される。なお、第1半導体スイッチング素子3aがオフされて所定の時間後(または略同時)に第3半導体スイッチング素子3cがオンされる。

この場合、寄生容量Cs1の電圧がPM間の電圧(E/2)に達するまで、コンデンサ2aの放電が継続されるとともに、正電圧モードが継続される。そして、寄生容量Cs1の電圧がPM間の電圧(E/2)に達したら、還流モード(図7参照)に遷移する。すなわち、寄生容量Cs1が大きいほど、正電圧モードの時間が長くなるとともに、その分、還流モードの時間が短くなる。

次に、図5に示すように、還流モード(図7参照)中において第2半導体スイッチング素子3bがオンされている間は、電流(図5の破線の矢印)は、ダイオード5a、第2半導体スイッチング素子3b、直流カット用コンデンサ6c、絶縁トランス6のルートを流れる。なお、還流モード中は、コンデンサ2aおよびコンデンサ2bの充放電は行われない。

次に、図6に示すように、還流モード中において、第2半導体スイッチング素子3bがオフされる。この場合、電流(図6の破線の矢印)は、ダイオード5a、寄生容量Cs2、直流カット用コンデンサ6c、絶縁トランス6のルートを流れる。この電流により、第2半導体スイッチング素子3bの寄生容量Cs2が充電される。

この場合、寄生容量Cs2の電圧がMN間の電圧(E/2)に達するまで電流が流れ続け、還流モードが継続される。そして、寄生容量Cs2の電圧がMN間の電圧(E/2)に達したら、負電圧モード(第1半導体スイッチング素子3aおよび第2半導体スイッチング素子3bがオフで、かつ、第3半導体スイッチング素子3cおよび第4半導体スイッチング素子3dがオンである状態)に遷移する。すなわち、寄生容量Cs2が大きいほど、還流モードの時間が長くなるとともに、その分、負電圧モードの時間が短くなる。

また、図8に示すように、負電圧モードから正電圧モードに遷移する場合でも、上記した動作原理と略同じであるので詳細な説明は省略するが、寄生容量Cs4が大きいほど、負電圧モードの時間が長くなるとともに、その分、還流モードの時間が短くなる。また、寄生容量Cs3が大きいほど、還流モードの時間が長くなるとともに、その分、正電圧モードの時間が短くなる。

したがって、寄生容量Cs1の大きさと寄生容量Cs4の大きさを等しくするとともに、寄生容量Cs2の大きさと寄生容量Cs3の大きさを等しくすることによって、コンデンサ2aおよびコンデンサ2bの充放電の時間(および充電電圧)のアンバランスを解消することが可能である。その結果、正電圧モードと負電圧モードとを複数回(高速で)スイッチングする場合においても、コンデンサ2aおよびコンデンサ2bの充電電圧のばらつきが蓄積されるのを抑制することが可能である。

(第1実施形態の効果)

第1実施形態では、以下のような効果を得ることができる。

第1実施形態では、上記のように、多層配線基板4の実装面4aに略垂直な方向から見て、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、および、第4半導体スイッチング素子3dの各々の、ソース端子側基板配線(10a、10b、10c、10d)とドレイン端子側基板配線(20a、20b、20c、20d)との重なり具合が調整されるように、3レベル電力変換装置100を構成する。

ここで、各半導体スイッチング素子の寄生容量の充電に要する時間の長さが互いに異なる場合、各半導体スイッチング素子のオンオフに要する時間にも互いに差異が生じる。このため、第1半導体スイッチング素子3aおよび第4半導体スイッチング素子3dの寄生容量(Cs1、Cs4)が互いに異なるか、または、第2半導体スイッチング素子3bおよび第3半導体スイッチング素子3cの寄生容量(Cs2、Cs3)が互いに異なる場合、コンデンサ2aを充放電する時間と、コンデンサ2bを充放電する時間との間に差異が生じる。これに対して、ソース端子側基板配線(10a、10b、10c、10d)とドレイン端子側基板配線(20a、20b、20c、20d)との重なり具合を調整することによって、第1半導体スイッチング素子3aおよび第4半導体スイッチング素子3dの寄生容量(Cs1、Cs4)を略等しくすることができるとともに、第2半導体スイッチング素子3bおよび第3半導体スイッチング素子3cの寄生容量(Cs2、Cs3)を略等しくすることができる。これにより、コンデンサ2aを充放電する時間と、コンデンサ2bを充放電する時間との間に差が生じるのを抑制することができる。その結果、コンデンサ2aに充電される電圧と、コンデンサ2bに充電される電圧との間に差が生じるのを抑制することができるとともに、コンデンサ2aおよびコンデンサ2bの充電電圧が過大になるのを抑制することができる。これにより、コンデンサ2aおよびコンデンサ2bに並列に接続されている、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、および、第4半導体スイッチング素子3dの各々に過大な電圧が印加されるのを抑制することができる。

また、ソース端子側基板配線(10a、10b、10c、10d)とドレイン端子側基板配線(20a、20b、20c、20d)との重なり具合という可視的なパラメータを調整すればよいので、比較的容易に寄生容量の調整を行うことができる。

また、第1実施形態では、上記のように、多層配線基板4の実装面4aに略垂直な方向から見て、第1半導体スイッチング素子3aのソース端子側基板配線10aおよびドレイン端子側基板配線20aの重なり具合と、第4半導体スイッチング素子3dのソース端子側基板配線10dおよびドレイン端子側基板配線20dの重なり具合とが同一である。また、多層配線基板4の実装面4aに略垂直な方向から見て、第2半導体スイッチング素子3bのソース端子側基板配線10bおよびドレイン端子側基板配線20bの重なり具合と、第3半導体スイッチング素子3cのソース端子側基板配線10cおよびドレイン端子側基板配線20cの重なり具合とが同一となるように、3レベル電力変換装置100を構成する。これにより、第1半導体スイッチング素子3a(第2半導体スイッチング素子3b)のソース端子側基板配線10a(10b)およびドレイン端子側基板配線20a(20b)の重なり具合と、第4半導体スイッチング素子3d(第3半導体スイッチング素子3c)のソース端子側基板配線10d(10c)およびドレイン端子側基板配線20d(20c)の重なり具合とを同一にすることによって、互いに異なる重なり具合を別個に設定する場合に比べて、比較的容易に寄生容量の調整を行うことができる。その結果、比較的容易に、第1半導体スイッチング素子3aおよび第4半導体スイッチング素子3dの寄生容量(Cs1、Cs4)を略等しくすることができるとともに、第2半導体スイッチング素子3bおよび第3半導体スイッチング素子3cの寄生容量(Cs2、Cs3)を略等しくすることができる。

また、第1実施形態では、上記のように、多層配線基板4の実装面4aに略垂直な方向から見て、第1半導体スイッチング素子3a、第2半導体スイッチング素子3b、第3半導体スイッチング素子3c、および、第4半導体スイッチング素子3dの各々の、ソース端子側基板配線(10a、10b、10c、10d)とドレイン端子側基板配線(20a、20b、20c、20d)とが互いに重ならないように、3レベル電力変換装置100を構成する。これにより、ソース端子側基板配線(10a、10b、10c、10d)とレイン端子側基板配線(20a、20b、20c、20d)とを重ねるとともに重なり量(重なり部分の面積)の調整をする必要がないので、配線位置の調整作業をさらに簡易化することができる。

[第2実施形態]

次に、図1および図9を参照して、第2実施形態による3レベル電力変換装置300の構成について説明する。この第2実施形態における3レベル電力変換装置300では、ソース端子側基板配線とドレイン端子側基板配線とが重ならないように配線されている第1実施形態とは異なり、ソース端子側基板配線とドレイン端子側基板配線とは重なっている。なお、上記第1実施形態と同様の構成は、第1実施形態と同じ符号を付して図示するとともに説明を省略する。

図9に示すように、3レベル電力変換装置300は、第1半導体スイッチング素子13aと、第2半導体スイッチング素子13bと、第3半導体スイッチング素子13cと、第4半導体スイッチング素子13dとを含むスイッチング回路13(図1参照)を備える。なお、図9は概略図である。

第1半導体スイッチング素子13a、第2半導体スイッチング素子13b、第3半導体スイッチング素子13c、および、第4半導体スイッチング素子13dの各々は、多層配線基板14上において実装されている。

多層配線基板14は、第1半導体スイッチング素子13a、第2半導体スイッチング素子13b、第3半導体スイッチング素子13c、および、第4半導体スイッチング素子13dの各々のソース端子Sに接続されている、ソース端子側基板配線30a、ソース端子側基板配線30b、ソース端子側基板配線30c、および、ソース端子側基板配線30dを含む。

また、多層配線基板14は、第1半導体スイッチング素子13a、第2半導体スイッチング素子13b、第3半導体スイッチング素子13c、および、第4半導体スイッチング素子13dの各々のドレイン端子D(図9(b)参照)に接続されている、ドレイン端子側基板配線40a、ドレイン端子側基板配線40b、ドレイン端子側基板配線40c、および、ドレイン端子側基板配線40dを含む。

ソース端子側基板配線30aとドレイン端子側基板配線40bとの組、ソース端子側基板配線30bとドレイン端子側基板配線40cとの組、ソース端子側基板配線30cとドレイン端子側基板配線40dとの組の各々は、一体的に形成されている。

ソース端子側基板配線30b(ドレイン端子側基板配線40c)、および、ドレイン端子側基板配線40d(ソース端子側基板配線30c)の各々は、互いに異なる3層の配線層からなる。また、ソース端子側基板配線30b(ドレイン端子側基板配線40c)、および、ドレイン端子側基板配線40d(ソース端子側基板配線30c)の各々の最下層(Z2方向側から1番目の層)は、ドレイン端子側基板配線40aおよびソース端子側基板配線30dの最下層(Z2方向側から1番目の層)と同じ層である。なお、各半導体スイッチング素子(13a、13b、13c、13d)のソース端子側基板配線(30a、30b、30c、30d)およびドレイン端子側基板配線(40a、40b、40c、40d)の配線層数および配線層の高さ位置などは一例であり、上記した構成に限られない。

ここで、第2実施形態では、多層配線基板14の実装面14aに略垂直な方向(Z1方向側)から見て、第1半導体スイッチング素子13a、第2半導体スイッチング素子13b、第3半導体スイッチング素子13c、および、第4半導体スイッチング素子13dの各々の、ソース端子側基板配線(30a、30b、30c、30d)およびドレイン端子側基板配線(40a、40b、40c、40d)の重なり量および重なり部分の配線間距離は互いに略等しい。

具体的には、各半導体スイッチング素子において、ソース端子側基板配線(30a、30b、30c、30d)およびドレイン端子側基板配線(40a、40b、40c、40d)の重なり部分の、X方向の幅は幅W1(図9(b)参照)を有するとともにY方向の幅は幅W2(図9(a)参照)を有する。すなわち、各半導体スイッチング素子において、多層配線基板14の実装面14aに略垂直な方向(Z1方向側)から見た、ソース端子側基板配線(30a、30b、30c、30d)およびドレイン端子側基板配線(40a、40b、40c、40d)の重なり部分(図9(a)のハッチング部分)の面積はW1×W2である。

また、各半導体スイッチング素子において、ソース端子側基板配線(30a、30b、30c、30d)およびドレイン端子側基板配線(40a、40b、40c、40d)の重なり部分の配線間距離は距離dを有する。具体的には、各半導体スイッチング素子の重なり部分において、ソース端子側基板配線(30a、30b、30c、30d)およびドレイン端子側基板配線(40a、40b、40c、40d)は、Z1方向側から2層目の配線層とZ1方向側から4番目の配線層との間の距離dだけ離間している。

第2実施形態のその他の構成は、上記第1実施形態と同様である。

(第2実施形態の効果)

第2実施形態では、以下のような効果を得ることができる。

第2実施形態では、上記のように、多層配線基板14の実装面14aに略垂直な方向から見て、第1半導体スイッチング素子13a、第2半導体スイッチング素子13b、第3半導体スイッチング素子13c、および、第4半導体スイッチング素子13dの各々の、ソース端子側基板配線(30a、30b、30c、30d)およびドレイン端子側基板配線(40a、40b、40c、40d)の重なり量および重なり部分の配線間距離が互いに略等しくなるように、3レベル電力変換装置300を構成する。これにより、各々の半導体スイッチング素子の、ソース端子側基板配線(30a、30b、30c、30d)およびドレイン端子側基板配線(40a、40b、40c、40d)が重ならないように構成する場合に比べて、多層配線基板14の実装面14aに略垂直な方向から見て、基板配線が設けられる領域の面積を小さくすることができる。その結果、3レベル電力変換装置300の小型化を容易に図ることができる。

なお、第2実施形態のその他の効果は、上記第1実施形態と同様である。

[変形例]

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更(変形例)が含まれる。

たとえば、上記第1実施形態では、第1半導体スイッチング素子、第2半導体スイッチング素子、第3半導体スイッチング素子、および、第4半導体スイッチング素子の各々の、ソース端子側基板配線とドレイン端子側基板配線とが重なっていない例を示したが、本発明はこれに限られない。たとえば、多層配線基板の実装面に略垂直な方向から見て、第1半導体スイッチング素子および第4半導体スイッチング素子の組と、第2半導体スイッチング素子および第3半導体スイッチング素子の組とのうちのいずれか一方の組が、各々のソース端子側基板配線とドレイン端子側基板配線とが互いに重ならないように構成されていてもよい。

たとえば、図10に示すように、3レベル電力変換装置500には、第1半導体スイッチング素子23a、第2半導体スイッチング素子23b、第3半導体スイッチング素子23c、および、第4半導体スイッチング素子23dが設けられている。

多層配線基板14は、第1半導体スイッチング素子23a、第2半導体スイッチング素子23b、第3半導体スイッチング素子23c、および、第4半導体スイッチング素子23dの各々のソース端子Sに接続されている、ソース端子側基板配線50a、ソース端子側基板配線50b、ソース端子側基板配線50c、および、ソース端子側基板配線50dを含む。また、多層配線基板24は、第1半導体スイッチング素子23a、第2半導体スイッチング素子23b、第3半導体スイッチング素子23c、および、第4半導体スイッチング素子23dの各々のドレイン端子D(図2(b)参照)に接続されている、ドレイン端子側基板配線60a、ドレイン端子側基板配線60b、ドレイン端子側基板配線60c、および、ドレイン端子側基板配線60dを含む。

多層配線基板24の実装面24aに略垂直な方向(Z1方向側)から見て、ドレイン端子側基板配線60aと、ソース端子側基板配線50aとは重なっていない。また、多層配線基板24の実装面24aに略垂直な方向(Z1方向側)から見て、ドレイン端子側基板配線60dと、ソース端子側基板配線50dとは重なっていない。

また、ドレイン端子側基板配線60bとソース端子側基板配線50bとの重なり部分(図10(a)のハッチング部分参照)の重なり量(W1×W2)および重なり部分の配線間距離(d)は、ドレイン端子側基板配線60cとソース端子側基板配線50cとの重なり部分(図10(a)のハッチング部分参照)の重なり量(W1×W2)および重なり部分の配線間距離(d)と等しい。

なお、第1半導体スイッチング素子および第4半導体スイッチング素子の、各々のソース端子側基板配線とドレイン端子側基板配線との重なり量および重なり部分の配線間距離が互いに等しく、第2半導体スイッチング素子および第3半導体スイッチング素子の、各々のソース端子側基板配線とドレイン端子側基板配線とが互いに重ならないように構成されていてもよい。

これにより、第1半導体スイッチング素子23aおよび第4半導体スイッチング素子23dの組と、第2半導体スイッチング素子23bおよび第3半導体スイッチング素子23cの組との両方において、各々のソース端子側基板配線とドレイン端子側基板配線とを重ねるとともに重なり量(重なり部分の面積)を調整する場合に比べて、ソース端子側基板配線(50a、50b、50c、50d)およびドレイン端子側基板配線(60a、60b、60c、60d)の配線位置の調整作業を簡易化することができる。

また、上記第2実施形態では、ソース端子側基板配線とドレイン端子側基板配線との重なり部分の、X方向の幅(W1)およびY方向の幅(W2)の各々が、半導体スイッチング素子ごとに等しい例を示したが、本発明はこれに限られない。たとえば、重なり部分の面積が半導体スイッチング素子ごとに等しければ、X方向およびY方向の各々の幅が半導体スイッチング素子ごとに互いに異なっていてもよい。

また、上記第2実施形態では、ソース端子側基板配線とドレイン端子側基板配線との重なり量および重なり部分の配線間距離が等しい例を示したが、本発明はこれに限られない。たとえば、ソース端子側基板配線とドレイン端子側基板配線との間の寄生容量が半導体スイッチング素子ごとに等しければ、ソース端子側基板配線とドレイン端子側基板配線との重なり量および重なり部分の配線間距離が、半導体スイッチング素子ごとに互いに異なっていてもよい。

また、上記第1および第2実施形態では、4つの半導体スイッチング素子が一列に配列されている構成の例を示したが、本発明はこれに限られない。たとえば、4つの半導体スイッチング素子が、マトリクス状に配置されていてもよい。