JP6812781B2 - 遅延回路、カウント値生成回路および物理量センサー - Google Patents

遅延回路、カウント値生成回路および物理量センサー Download PDFInfo

- Publication number

- JP6812781B2 JP6812781B2 JP2016246005A JP2016246005A JP6812781B2 JP 6812781 B2 JP6812781 B2 JP 6812781B2 JP 2016246005 A JP2016246005 A JP 2016246005A JP 2016246005 A JP2016246005 A JP 2016246005A JP 6812781 B2 JP6812781 B2 JP 6812781B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- signal

- output

- latch

- count value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000001514 detection method Methods 0.000 claims description 26

- 125000004122 cyclic group Chemical group 0.000 claims description 6

- 230000000630 rising effect Effects 0.000 description 56

- 238000003708 edge detection Methods 0.000 description 34

- 230000001133 acceleration Effects 0.000 description 19

- 238000010586 diagram Methods 0.000 description 13

- 238000000034 method Methods 0.000 description 10

- 230000001360 synchronised effect Effects 0.000 description 7

- 230000001351 cycling effect Effects 0.000 description 6

- 238000013139 quantization Methods 0.000 description 6

- 238000004364 calculation method Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 230000003111 delayed effect Effects 0.000 description 4

- 230000001934 delay Effects 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 238000007493 shaping process Methods 0.000 description 1

- 230000001960 triggered effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K23/00—Pulse counters comprising counting chains; Frequency dividers comprising counting chains

- H03K23/40—Gating or clocking signals applied to all stages, i.e. synchronous counters

- H03K23/50—Gating or clocking signals applied to all stages, i.e. synchronous counters using bi-stable regenerative trigger circuits

- H03K23/54—Ring counters, i.e. feedback shift register counters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/14—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals by the use of delay lines

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01D—MEASURING NOT SPECIALLY ADAPTED FOR A SPECIFIC VARIABLE; ARRANGEMENTS FOR MEASURING TWO OR MORE VARIABLES NOT COVERED IN A SINGLE OTHER SUBCLASS; TARIFF METERING APPARATUS; MEASURING OR TESTING NOT OTHERWISE PROVIDED FOR

- G01D5/00—Mechanical means for transferring the output of a sensing member; Means for converting the output of a sensing member to another variable where the form or nature of the sensing member does not constrain the means for converting; Transducers not specially adapted for a specific variable

- G01D5/12—Mechanical means for transferring the output of a sensing member; Means for converting the output of a sensing member to another variable where the form or nature of the sensing member does not constrain the means for converting; Transducers not specially adapted for a specific variable using electric or magnetic means

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/20—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits characterised by logic function, e.g. AND, OR, NOR, NOT circuits

- H03K19/21—EXCLUSIVE-OR circuits, i.e. giving output if input signal exists at only one input; COINCIDENCE circuits, i.e. giving output only if all input signals are identical

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K21/00—Details of pulse counters or frequency dividers

- H03K21/08—Output circuits

- H03K21/10—Output circuits comprising logic circuits

Landscapes

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Nonlinear Science (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- Mathematical Physics (AREA)

- General Physics & Mathematics (AREA)

- Pulse Circuits (AREA)

- Compression, Expansion, Code Conversion, And Decoders (AREA)

- Manipulation Of Pulses (AREA)

- Measuring Frequencies, Analyzing Spectra (AREA)

- Measuring Phase Differences (AREA)

Description

複数の遅延素子が電気的に直列に接続され、前記複数の遅延素子の出力のうちのいずれか1つの出力をフィードバックすることでループを形成し、前記第3の信号を初段の前記遅延素子に入力するループ回路と、

ラッチ信号で前記複数の遅延素子の出力値をラッチするラッチ回路と、を備え、

前記第2の信号は、前記複数の遅延素子の出力のうちのいずれかの出力であり、

前記ループ回路は、前記ループの巡回数が規定の巡回数に達すると、前記フィードバックを停止することを特徴とする。

これにより、2のべき乗の巡回数を簡易に実現することができる。

前記ループ回路は、前記選択部により選択された前記出力をフィードバックすることが好ましい。

これにより、遅延量を微細に調整することができる。

電気的に並列に接続され、位相の異なる複数の前記被測定信号がそれぞれ入力され、前記基準クロックを用いて、前記複数の被測定信号のレベルの反転を表す反転エッジを検出する複数のカウンターと、

前記複数のカウンターの出力に基づいて、カウント値を生成するカウント値生成部と、

本発明の遅延回路と、を備え、

前記遅延回路により、前記位相の異なる複数の被測定信号を生成することを特徴とする。

これにより、精度を向上させることができる。

前記検出部から出力された被測定信号が入力される本発明のカウント値生成回路と、を備えることを特徴とする。

これにより、振動に関する物理量を精度良く検出することができる。

図1は、本発明のカウント値生成回路の1例であるレシプロカルカウント値生成回路の第1実施形態を示すブロック図である。図2は、図1に示すレシプロカルカウント値生成回路の遅延回路を示すブロック図である。

また、信号のレベルが「ロー(Low)」の場合を「0」、信号のレベルが「ハイ(High)」の場合を「1」とも言う。

遅延回路50は、トリガー信号の1例である被検出信号(Fx)に基づいて生成される第1の信号と、第2の信号とに基づいて第3の信号を生成する巡回数制御回路59と、複数の遅延素子51が電気的に直列に接続され、複数の遅延素子51の出力のうちのいずれか1つの出力をフィードバックすることでループを形成し、第3の信号を初段の遅延素子51に入力するループ回路58と、ラッチ信号の1例であるクロック信号(Fs)で複数の遅延素子51の出力値をラッチするラッチ回路310とを備えている(図2参照)。第2の信号は、複数の遅延素子51の出力のうちのいずれかの出力、すなわち、インバーター53への入力信号(またはインバーター53の出力信号)である。また、ループ回路58は、そのループ回路58のループの巡回数が規定の巡回数に達すると、フィードバックを停止する。このような構成により、回路規模を小さくすることができる。すなわち、ループ回路58のループを複数回、巡回させることにより、回路規模を増大させずに、その巡回数倍の機能を発揮することができる。なお、排他的論理和回路56から出力される信号は、第1の信号の1例であり、論理積回路57から出力される信号は、第3の信号の1例である。

なお、本実施形態では、1例として、遅延回路繰り返し回数を「4」とした場合について説明する。

図2に示すように、被測定信号は、排他的論理和回路56の一方の入力端子に入力される。また、初期状態では、例えば、カウンター54のカウント値出力は「0」であり、マルチプレクサー55から排他的論理和回路56の他方の入力端子に入力される信号は、下位2ビット目の値である「0」とする。

(1)カウンター3およびカウンター5としては、それぞれ、前記の構成に限定されず、他の構成のカウンターを用いることができる。他のカウンターとしては、例えば、リプルカウンター等が挙げられる。

(3)差分演算器8(エッジ検出数演算回路)よりも後段(出力側)の回路については、動作クロックとして、基準クロックを用いてもよく、また、被測定信号を用いてもよい。

図3は、本発明のカウント値生成回路の1例であるレシプロカルカウント値生成回路の第2実施形態を示すブロック図である。図4は、図3に示すレシプロカルカウント値生成回路の遅延回路を示すブロック図である。図5は、図3に示すレシプロカルカウント値生成回路の動作を説明するためのタイミングチャートである。なお、図3では、回路中のバスを太線で示す(他の図も同様)。

なお、遅延回路50の動作については、第1実施形態と同様であるので、その説明は省略する。

図6は、本発明のカウント値生成回路の1例であるレシプロカルカウント値生成回路1の第3実施形態を示すブロック図である。

図6に示すように、途中までは、第2実施形態と同様であり、カウンター30の排他的論理和回路330からは、被測定信号の立ち上がりおよび立ち下がりに対応してそれぞれ「1」が出力され、その他は「0」が出力される。

図7は、本発明のカウント値生成回路の1例であるレシプロカルカウント値生成回路の第4実施形態を示すブロック図である。

図7に示すように、途中までは、第2実施形態と同様であり、各カウンター3からは、被測定信号の立ち上がりおよび立ち下がりに対応してそれぞれ「1」が出力され、その他は「0」が出力される。

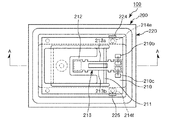

図8は、本発明の物理量センサーの1例である加速度センサーの実施形態における検出部の内部構造を示す図である。図9は、図8中のA−A線での断面図である。

Claims (8)

- トリガー信号に基づいて生成される第1の信号と、第2の信号とに基づいて第3の信号を生成する巡回数制御回路と、

複数の遅延素子が電気的に直列に接続され、前記複数の遅延素子の出力のうちのいずれか1つの出力をフィードバックすることでループを形成し、前記第3の信号を初段の前記遅延素子に入力するループ回路と、

ラッチ信号で前記複数の遅延素子の出力値をラッチするラッチ回路と、

複数のスイッチを有し、前記複数の遅延素子の出力のうちの所定の前記出力を選択する選択部と、を備え、

前記巡回数制御回路は、カウンターと、マルチプレクサーと、排他的論理和回路と、論理積回路と、インバーターと、を備え、

前記第2の信号は、前記複数の遅延素子の出力から、前記選択部によって選択された出力であり、

前記トリガー信号は、前記排他的論理和回路に入力され、

前記排他的論理和回路から、前記第1の信号が出力され、

前記論理積回路から、前記第3の信号が出力され、

前記論理積回路から出力された前記第3の信号は、前記インバーターで反転され、

前記カウンターによるカウント値が前記マルチプレクサーに入力され、前記マルチプレクサーの出力が前記排他的論理和回路に入力されることによって前記排他的論理和回路から出力される前記第1の信号と、前記インバーターから出力される前記第2の信号とが、前記論理積回路に入力され、

前記ループ回路は、前記ループの巡回数が規定の巡回数に達すると、前記論理積回路によって、前記フィードバックを停止することを特徴とする遅延回路。 - 前記カウンターは、バイナリカウンターである請求項1に記載の遅延回路。

- 前記ループ回路は、前記選択部により選択された前記出力をフィードバックする請求項1または2に記載の遅延回路。

- 前記ループを1巡するのに要する時間は、前記ラッチ回路のラッチ間隔よりも長い請求項1ないし3のいずれか1項に記載の遅延回路。

- 被測定信号で規定されるタイミングで基準クロックをカウントするカウント値生成回路であって、

電気的に並列に接続され、位相の異なる複数の前記被測定信号がそれぞれ入力され、前記基準クロックを用いて、前記複数の被測定信号のレベルの反転を表す反転エッジを検出する複数のカウンターと、

前記複数のカウンターの出力に基づいて、カウント値を生成するカウント値生成部と、

請求項1ないし4のいずれか1項に記載の遅延回路と、を備え、

前記遅延回路により、前記位相の異なる複数の被測定信号を生成することを特徴とするカウント値生成回路。 - 前記カウント値は、レシプロカルカウント値である請求項5に記載のカウント値生成回路。

- 物理量を検出する検出部と、

前記検出部から出力された被測定信号が入力される請求項5または6に記載のカウント値生成回路と、を備えることを特徴とする物理量センサー。 - 前記物理量は振動に関する物理量である請求項7に記載の物理量センサー。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016246005A JP6812781B2 (ja) | 2016-12-19 | 2016-12-19 | 遅延回路、カウント値生成回路および物理量センサー |

| CN201711316963.2A CN108206691B (zh) | 2016-12-19 | 2017-12-11 | 延迟电路、计数值生成电路以及物理量传感器 |

| US15/840,203 US10491201B2 (en) | 2016-12-19 | 2017-12-13 | Delay circuit, count value generation circuit, and physical quantity sensor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016246005A JP6812781B2 (ja) | 2016-12-19 | 2016-12-19 | 遅延回路、カウント値生成回路および物理量センサー |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020155375A Division JP7040572B2 (ja) | 2020-09-16 | 2020-09-16 | 遅延回路、カウント値生成回路および物理量センサー |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018101869A JP2018101869A (ja) | 2018-06-28 |

| JP6812781B2 true JP6812781B2 (ja) | 2021-01-13 |

Family

ID=62562864

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016246005A Active JP6812781B2 (ja) | 2016-12-19 | 2016-12-19 | 遅延回路、カウント値生成回路および物理量センサー |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US10491201B2 (ja) |

| JP (1) | JP6812781B2 (ja) |

| CN (1) | CN108206691B (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7087517B2 (ja) * | 2018-03-22 | 2022-06-21 | セイコーエプソン株式会社 | 遷移状態取得装置、時間デジタル変換器及びa/d変換回路 |

| US11041722B2 (en) * | 2018-07-23 | 2021-06-22 | Analog Devices, Inc. | Systems and methods for sensing angular motion in the presence of low-frequency noise |

| CN109799450B (zh) * | 2018-12-27 | 2021-01-12 | 大唐微电子技术有限公司 | 一种逻辑电路延迟差异比较装置和方法 |

| US11664813B2 (en) | 2019-09-30 | 2023-05-30 | Seiko Epson Corporation | Delay circuit, time to digital converter, and A/D conversion circuit |

| JP7408981B2 (ja) | 2019-09-30 | 2024-01-09 | セイコーエプソン株式会社 | 状態遷移器、時間デジタル変換器及びa/d変換回路 |

| CN111262579A (zh) * | 2020-03-31 | 2020-06-09 | 杭州国彪超声设备有限公司 | 基于fpga的二维超声装置频率跟踪与相位控制电路 |

| US11621669B2 (en) * | 2021-01-27 | 2023-04-04 | The Regents Of The University Of California | Fast startup of crystal and other high-Q oscillators |

| US11595032B2 (en) * | 2021-05-27 | 2023-02-28 | Skyworks Solutions, Inc. | Signal delay control using a recirculating delay loop and a phase interpolator |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4458165A (en) | 1983-03-23 | 1984-07-03 | Tektronix, Inc. | Programmable delay circuit |

| JPH0483413A (ja) * | 1990-07-26 | 1992-03-17 | Seiko Epson Corp | 発振回路及び集積回路 |

| JP3455982B2 (ja) * | 1993-01-14 | 2003-10-14 | 株式会社デンソー | 偶数段リングオシレータ及びパルス位相差符号化回路 |

| JP3986572B2 (ja) * | 1995-03-23 | 2007-10-03 | 株式会社デンソー | 周波数逓倍装置 |

| JPH09246924A (ja) * | 1996-03-12 | 1997-09-19 | Hitachi Ltd | 逓倍回路 |

| JP3175600B2 (ja) * | 1996-08-09 | 2001-06-11 | 株式会社デンソー | 時間測定装置 |

| JPH11177399A (ja) * | 1997-12-15 | 1999-07-02 | Mitsubishi Electric Corp | クロック遅延回路およびこれを用いた発振回路、位相同期回路、クロック生成回路 |

| JP2000357951A (ja) * | 1999-06-15 | 2000-12-26 | Mitsubishi Electric Corp | 遅延回路、クロック生成回路及び位相同期回路 |

| JP3625400B2 (ja) | 1999-09-22 | 2005-03-02 | 株式会社東芝 | 可変遅延素子のテスト回路 |

| JP2007243667A (ja) * | 2006-03-09 | 2007-09-20 | Hitachi Ulsi Systems Co Ltd | 半導体集積回路装置 |

| KR100921815B1 (ko) * | 2007-06-18 | 2009-10-16 | 주식회사 애트랩 | 지연시간 측정회로 및 지연시간 측정 방법 |

| KR100944497B1 (ko) * | 2007-06-25 | 2010-03-03 | 삼성전자주식회사 | 디지털 주파수 검출기 및 이를 이용한 디지털 pll |

| JP5158764B2 (ja) | 2007-09-27 | 2013-03-06 | 川崎マイクロエレクトロニクス株式会社 | 位相シフト方法および回路 |

| KR20120005290A (ko) * | 2010-07-08 | 2012-01-16 | 주식회사 하이닉스반도체 | 지연 동기 회로 |

| JP5753013B2 (ja) * | 2011-07-06 | 2015-07-22 | オリンパス株式会社 | リングオシュレータ回路、a/d変換回路、および固体撮像装置 |

| JP5948195B2 (ja) * | 2012-09-14 | 2016-07-06 | ザインエレクトロニクス株式会社 | クロック生成装置およびクロックデータ復元装置 |

| JP6387676B2 (ja) | 2014-05-15 | 2018-09-12 | セイコーエプソン株式会社 | アイドルトーン分散装置及び周波数計測装置 |

-

2016

- 2016-12-19 JP JP2016246005A patent/JP6812781B2/ja active Active

-

2017

- 2017-12-11 CN CN201711316963.2A patent/CN108206691B/zh active Active

- 2017-12-13 US US15/840,203 patent/US10491201B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US10491201B2 (en) | 2019-11-26 |

| US20180175840A1 (en) | 2018-06-21 |

| CN108206691A (zh) | 2018-06-26 |

| CN108206691B (zh) | 2023-06-27 |

| JP2018101869A (ja) | 2018-06-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6812781B2 (ja) | 遅延回路、カウント値生成回路および物理量センサー | |

| US6906562B1 (en) | Counter-based clock multiplier circuits and methods | |

| CN100530967C (zh) | 时钟分频电路 | |

| US7953782B2 (en) | Digital forced oscillation by direct digital synthesis | |

| JP4806631B2 (ja) | タイミング発生器および半導体試験装置 | |

| JP2014052282A (ja) | 周波数測定回路 | |

| JP2018163030A (ja) | 時間デジタル変換器 | |

| JP7040572B2 (ja) | 遅延回路、カウント値生成回路および物理量センサー | |

| JP6782193B2 (ja) | 情報処理装置、半導体装置および情報処理方法 | |

| JP6812780B2 (ja) | レシプロカルカウント値生成回路および物理量センサー | |

| CN102045042A (zh) | 使用于半导体元件测试的频率信号产生方法 | |

| JP6787105B2 (ja) | デジタルフィルター、レシプロカルカウント値生成回路および物理量センサー | |

| RU2260830C1 (ru) | Устройство для измерения интервала времени | |

| JP5854003B2 (ja) | デジタル制御発振器および周波数可変発振器 | |

| JP6809201B2 (ja) | サンプリングレート変換回路、レシプロカルカウント値生成回路および物理量センサー | |

| JP6972604B2 (ja) | カウンター回路、測定装置および物理量センサー | |

| JP2009152886A (ja) | クロック生成回路およびその使用方法 | |

| JP6862901B2 (ja) | 周波数比測定装置および物理量センサー | |

| JP2017163378A (ja) | 周波数デルタシグマ変調信号出力装置 | |

| JP6957901B2 (ja) | 周波数比測定装置および物理量センサー | |

| JP2018132461A5 (ja) | ||

| JP2011252788A (ja) | 電圧測定装置および電圧測定方法 | |

| JP2012052913A (ja) | 試験装置および信号発生装置 | |

| TW201624919A (zh) | 時脈產生裝置 | |

| JP2021089292A (ja) | 時間デジタル変換器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190910 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20200811 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200818 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201016 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20201117 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20201130 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6812781 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |