JP6576306B2 - 電圧電流変換回路および負荷駆動回路 - Google Patents

電圧電流変換回路および負荷駆動回路 Download PDFInfo

- Publication number

- JP6576306B2 JP6576306B2 JP2016127559A JP2016127559A JP6576306B2 JP 6576306 B2 JP6576306 B2 JP 6576306B2 JP 2016127559 A JP2016127559 A JP 2016127559A JP 2016127559 A JP2016127559 A JP 2016127559A JP 6576306 B2 JP6576306 B2 JP 6576306B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- terminal

- voltage

- resistor

- current

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F1/00—Automatic systems in which deviations of an electric quantity from one or more predetermined values are detected at the output of the system and fed back to a device within the system to restore the detected quantity to its predetermined value or values, i.e. retroactive systems

- G05F1/10—Regulating voltage or current

- G05F1/46—Regulating voltage or current wherein the variable actually regulated by the final control device is DC

- G05F1/56—Regulating voltage or current wherein the variable actually regulated by the final control device is DC using semiconductor devices in series with the load as final control devices

- G05F1/561—Voltage to current converters

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F3/00—Non-retroactive systems for regulating electric variables by using an uncontrolled element, or an uncontrolled combination of elements, such element or such combination having self-regulating properties

- G05F3/02—Regulating voltage or current

- G05F3/08—Regulating voltage or current wherein the variable is DC

- G05F3/10—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics

- G05F3/16—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics being semiconductor devices

- G05F3/20—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics being semiconductor devices using diode- transistor combinations

- G05F3/26—Current mirrors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/56—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices

- H03K17/687—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors

- H03K17/6871—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors the output circuit comprising more than one controlled field-effect transistor

- H03K17/6872—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors the output circuit comprising more than one controlled field-effect transistor using complementary field-effect transistors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B45/00—Circuit arrangements for operating light-emitting diodes [LED]

- H05B45/30—Driver circuits

- H05B45/37—Converter circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B45/00—Circuit arrangements for operating light-emitting diodes [LED]

- H05B45/30—Driver circuits

- H05B45/395—Linear regulators

- H05B45/397—Current mirror circuits

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B20/00—Energy efficient lighting technologies, e.g. halogen lamps or gas discharge lamps

- Y02B20/30—Semiconductor lamps, e.g. solid state lamps [SSL] light emitting diodes [LED] or organic LED [OLED]

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Radar, Positioning & Navigation (AREA)

- Automation & Control Theory (AREA)

- Electromagnetism (AREA)

- General Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Circuit Arrangement For Electric Light Sources In General (AREA)

- Led Devices (AREA)

- Control Of Electrical Variables (AREA)

- Continuous-Control Power Sources That Use Transistors (AREA)

- Electronic Switches (AREA)

Description

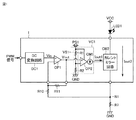

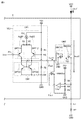

図1は、実施の形態1に係る負荷駆動回路の一例であるLED駆動回路1の回路図である。図1に示されるように、発光ダイオードLED1は、電源VCCと接地点GNDとの間に接続され、通過する電流に応じて発光する電流負荷である。LED駆動回路1は、接地点GNDと発光ダイオードLED1との間に接続されている。LED駆動回路1は、PWM(Pulse Width Modulation)信号を受けて、発光ダイオードLED1に流れる電流を制御する。LED駆動回路1は、DC(Direct Current)変換回路DC1と、差動増幅回路であるオペアンプOP1と、電圧電流変換回路VC1と、カレントミラー回路CM2とを備える。

…(1)

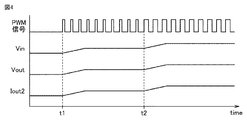

式(1)より、電流Iout2が大きくなると電圧Voutが小さくなり、その結果、電流Iout2が小さくなるように制御される。逆に電流Iout2が小さくなると電圧Voutが大きくなり、その結果、電流Iout2は大きくなるように制御される。すなわち、電流Iout2には負のフィードバック制御が行なわれる。なお、Iout2が0である場合、電圧Voutは以下の式(2)となる。

式(2)の電圧Vinの係数(1+R11/R10)は、オペアンプOP1の増幅率を表す。

出力端子Poutは、トランジスタBPT12のコレクタとトランジスタBPT22のコレクタとの接続点N3に接続される。

電流Iout1とIout2との比であるカレントミラー比をk2とすると、電流Iout2は式(4)のように表すことができる。

式(4)の電流Iout1に式(3)を代入することにより、電流Iout2は電圧Voutを用いて式(5)のように表すことができる。式(5)において、k3=k2・k1である。変換係数k3は、電圧Voutと電流Iout2との比(変換係数)である。

式(5)から変換係数k3は、式(6)のように表すことができる。抵抗R3およびR5の抵抗値が大きくなると、オペアンプOP2を流れる電流は小さくなる。電流Iout1が小さくなって、電流Iout2が小さくなる。その結果、式(6)より、変換係数k3は小さくなる。逆に抵抗R3およびR5の抵抗値が小さくなると、オペアンプOP2を流れる電流は大きくなる。電流Iout1が大きくなって、電流Iout2が大きくなる。その結果、式(6)より変換係数k3は大きくなる。このように、抵抗R3およびR5の値を変化させることにより、変換係数k3を調節することができる。

カレントミラー回路CM2は、電圧電流変換回路VC1から出力された電流Iout1を受けて、電流Iout1を増幅して発光ダイオードLED1に流れる電流を電流Iout2とする。カレントミラー回路CM2は、トランジスタNMOS3と、トランジスタNMOS4とを含む。トランジスタNMOS3およびトランジスタNMOS4の各々は、ゲート、ソース、およびドレインを有する。トランジスタNMOS3のゲートは、トランジスタNMOS4のゲートおよびトランジスタNMOS3のドレインに接続される。トランジスタNMOS3のソースは、接地点GNDに接続される。トランジスタNMOS3のドレインは、電圧電流変換回路VC1の出力端子Poutに接続される。トランジスタNMOS4のソースは、抵抗R7を介して接地点GNDに接続される。トランジスタNMOS4のドレインは、発光ダイオードLED1を介して電源VCCに接続される。

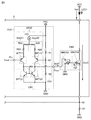

実施の形態1においては、各調節部が、1つの抵抗を含んでいる場合について説明した。抵抗は温度によって抵抗値が変化する場合がある。抵抗値が変化すると電圧Voutと電流Iout2との間の変換係数が変化してしまい、発光ダイオードLED1の制御の精度が低下し得る。そこで、実施の形態2では、変換係数のこのような温度依存性を抑制する構成について説明する。

実施の形態1においては、電圧電流変換回路VC1から電流Iout1が入力されるトランジスタNMOS3のソースの電圧が、トランジスタNMOS4のソースの電圧よりも抵抗R7の分だけ低い場合について説明した。このような構成により、上述したようにカレントミラー回路CM2が動作することのできる電圧の範囲を広くすることができる。しかし、トランジスタNMOS3のソースの電圧と、トランジスタNMOS4のソースの電圧とが異なると、トランジスタNMOS3のゲート−ソース間の電圧と、トランジスタNMOS4のゲート−ソース間の電圧との間に差異が生じる。また、トランジスタNMOS3のドレイン−ソース間の電圧と、トランジスタNMOS4のドレイン−ソース間の電圧との間にも差異が生じる。その結果、カレントミラー回路CM2のカレントミラー比の精度が低下してしまう可能性がある。したがって、カレントミラー回路CM2を動作させる電圧の範囲が限定されている場合には、トランジスタNMOS3のソースとトランジスタNMOS4のソースとは同電位であることが望ましい。

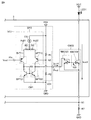

図1に示されたLED駆動回路1において、発光ダイオードLED1に過電流が流れる異常、あるいは電源電圧が低下する異常などが発生する場合がある。このような場合に発光ダイオードLED1の駆動を継続していると、発光ダイオードLED1あるいはLED駆動回路1が故障して停止してしまうおそれがある。そこで、実施の形態4においては、このような異常を検出する異常検出回路を備える負荷駆動回路について説明する。

Claims (7)

- 第1電源と接地点との間に接続され、入力端子に印加された入力電圧に応じた出力電流を出力端子から出力するように構成された電圧電流変換回路であって、

前記入力端子から前記入力電圧を受けて、前記入力電圧と閾値電圧との差に応じた電圧を出力するように構成された差動増幅回路と、

前記差動増幅回路からの電圧を受け、前記出力端子に前記出力電流を出力するように構成された第1カレントミラー回路と、

前記閾値電圧を設定するように構成された電圧設定部とを備え、

前記差動増幅回路は、前記第1電源に接続された定電流源と、第1トランジスタと、第2トランジスタとを含み、

前記第1カレントミラー回路は、前記第1トランジスタに接続された第3トランジスタと、前記第2トランジスタに接続された第4トランジスタとを含み、

前記電圧設定部は、前記第1電源と前記接地点との間に直列に接続された第1抵抗と第2抵抗とを含み、

前記第1トランジスタおよび前記第2トランジスタの各々は第1導電型トランジスタであり、

前記第3トランジスタおよび前記第4トランジスタの各々は第2導電型トランジスタであり、

前記第1トランジスタおよび前記第2トランジスタならびに前記第3トランジスタおよび前記第4トランジスタの各々は、制御端子、第1端子、および第2端子を有し、

前記第1トランジスタの制御端子は、前記入力端子に接続され、

前記第1トランジスタの第1端子は、前記定電流源に接続され、

前記第1トランジスタの第2端子は、前記第3トランジスタの第2端子に接続され、

前記第3トランジスタの制御端子は、前記第4トランジスタの制御端子および前記第3トランジスタの第2端子に接続され、

前記第3トランジスタの第1端子は、前記接地点に接続され、

前記第2トランジスタの制御端子は、前記第1抵抗と前記第2抵抗との接続点に接続され、

前記第2トランジスタの制御端子の電圧は、前記第1抵抗および前記第2抵抗により前記第2トランジスタの動作電圧となるように設定され、

前記第2トランジスタの第1端子は、前記定電流源に接続され、

前記第2トランジスタの第2端子は、前記第4トランジスタの第2端子に接続され、

前記第4トランジスタの第1端子は、前記接地点に接続され、

前記出力端子は、前記第2トランジスタの第2端子と前記第4トランジスタの第2端子との接続点に接続される、電圧電流変換回路。 - 前記差動増幅回路は、前記入力電圧と前記出力電流との間の変換係数を調節するための第1調節部および第2調節部をさらに含み、

前記第1調節部は、前記定電流源と前記第1トランジスタの第1端子との間に接続され、

前記第2調節部は、前記定電流源と前記第2トランジスタの第1端子との間に接続され、

前記第1調節部の抵抗値は、前記第2調節部の抵抗値に等しい、請求項1に記載の電圧電流変換回路。 - 前記第1調節部は、直列に接続された第3抵抗と第4抵抗とを含み、

前記第2調節部は、直列に接続された第5抵抗と第6抵抗とを含み、

前記第3抵抗の抵抗値は、前記第5抵抗の抵抗値に等しく、

前記第3抵抗および前記第5抵抗は、正の温度特性を有し、

前記第4抵抗の抵抗値は、前記第6抵抗の抵抗値に等しく、

前記第4抵抗および前記第6抵抗は、負の温度特性を有する、請求項2に記載の電圧電流変換回路。 - 負荷を駆動する負荷駆動回路であって、

請求項1に記載の電圧電流変換回路と、

第5トランジスタと、第6トランジスタとを含む第2カレントミラー回路とを備え、

前記負荷は、第2電源と前記接地点との間に接続されており、

前記第5トランジスタおよび前記第6トランジスタの各々は、制御端子、第1端子、および第2端子を有し、

前記第5トランジスタの制御端子は、前記第6トランジスタの制御端子および前記第5トランジスタの第2端子に接続され、

前記第5トランジスタの第1端子の電圧は、前記第6トランジスタの第1端子の電圧以下であり、

前記第5トランジスタの第2端子は、前記電圧電流変換回路の出力端子に接続され、

前記第6トランジスタの第1端子は、第7抵抗を介して前記接地点に接続され、

前記第6トランジスタの第2端子は、前記負荷を介して前記第2電源に接続される、負荷駆動回路。 - 前記第5トランジスタの第1端子は、前記第6トランジスタの第1端子に接続される、請求項4に記載の負荷駆動回路。

- 前記負荷駆動回路に異常が発生した場合に、前記第5トランジスタの第2端子の電圧を前記第5トランジスタの動作電圧よりも低下させるように構成された異常検出回路をさらに備える、請求項4に記載の負荷駆動回路。

- 前記異常検出回路は、

反転入力端子、非反転入力端子、および出力端子を有するコンパレータと、

前記コンパレータの出力端子に接続された制御端子と、前記接地点に接続された第1端子と、前記第5トランジスタの第2端子に接続された第2端子とを有する第7トランジスタと、

前記第1電源と前記接地点との間に直列に接続された第8抵抗と第9抵抗とを含み、

前記非反転入力端子は、前記第6トランジスタの第1端子に接続され、

前記反転入力端子は、前記第8抵抗と前記第9抵抗との接続点に接続される、請求項6に記載の負荷駆動回路。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016127559A JP6576306B2 (ja) | 2016-06-28 | 2016-06-28 | 電圧電流変換回路および負荷駆動回路 |

| US15/453,747 US10345833B2 (en) | 2016-06-28 | 2017-03-08 | Voltage-current converter and load driver |

| CN201710508382.2A CN107548202B (zh) | 2016-06-28 | 2017-06-28 | 电压电流变换电路及负载驱动电路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016127559A JP6576306B2 (ja) | 2016-06-28 | 2016-06-28 | 電圧電流変換回路および負荷駆動回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018005323A JP2018005323A (ja) | 2018-01-11 |

| JP2018005323A5 JP2018005323A5 (ja) | 2018-07-12 |

| JP6576306B2 true JP6576306B2 (ja) | 2019-09-18 |

Family

ID=60677318

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016127559A Active JP6576306B2 (ja) | 2016-06-28 | 2016-06-28 | 電圧電流変換回路および負荷駆動回路 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US10345833B2 (ja) |

| JP (1) | JP6576306B2 (ja) |

| CN (1) | CN107548202B (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10263573B2 (en) * | 2016-08-30 | 2019-04-16 | Macom Technology Solutions Holdings, Inc. | Driver with distributed architecture |

| JP6797849B2 (ja) * | 2018-01-26 | 2020-12-09 | 株式会社東芝 | 電圧電流変換回路 |

| WO2019153171A1 (en) * | 2018-02-08 | 2019-08-15 | Dialog Semiconductor (Uk) Limited | A method and apparatus for operating a semiconductor light source |

| KR101973070B1 (ko) * | 2018-11-22 | 2019-04-26 | 울산과학기술원 | 저항 측정 장치 및 방법 |

| CN113056851B (zh) | 2018-11-27 | 2024-02-13 | 索尼半导体解决方案公司 | 驱动装置和发光装置 |

| EP4055708A1 (en) * | 2019-11-08 | 2022-09-14 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | Method for controlling a driver circuit, driver circuit, system comprising a driver circuit and method for manufacturing an integrated circuit |

| TWI719826B (zh) * | 2020-02-06 | 2021-02-21 | 香港商億奇生物科技責任有限公司 | 負載控制裝置與手作電路板 |

| CN114637366B (zh) * | 2022-05-18 | 2022-08-23 | 成都本原聚能科技有限公司 | 与工艺、温度无关的检测电路、芯片及流明检测用途 |

| CN115134963B (zh) * | 2022-06-28 | 2023-04-14 | 无锡市益明光电有限公司 | 一种防led灯低温闪烁的调节电路 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5266887A (en) * | 1988-05-24 | 1993-11-30 | Dallas Semiconductor Corp. | Bidirectional voltage to current converter |

| JP2763393B2 (ja) * | 1990-09-26 | 1998-06-11 | 富士通株式会社 | 定電流回路および発振回路 |

| US5619125A (en) * | 1995-07-31 | 1997-04-08 | Lucent Technologies Inc. | Voltage-to-current converter |

| JP4353667B2 (ja) | 1999-12-14 | 2009-10-28 | 株式会社タキオン | Ledランプ装置 |

| JP2002026666A (ja) * | 2000-07-06 | 2002-01-25 | Matsushita Electric Ind Co Ltd | 電圧電流変換器 |

| DE60327120D1 (de) * | 2002-02-25 | 2009-05-20 | Nec Corp | Differentialschaltung, Verstärkerschaltung, Treiberschaltung und Anzeigevorrichtung mit diesen Schaltungen |

| JP4411199B2 (ja) * | 2002-04-26 | 2010-02-10 | 株式会社ルネサステクノロジ | 半導体装置及びicカード |

| JP4237219B2 (ja) * | 2006-11-10 | 2009-03-11 | Necエレクトロニクス株式会社 | データ受信回路とデータドライバ及び表示装置 |

| JP2008171070A (ja) * | 2007-01-09 | 2008-07-24 | Rohm Co Ltd | 電源装置およびそれを用いた電子機器 |

| JP2008283110A (ja) * | 2007-05-14 | 2008-11-20 | Seiko Epson Corp | 電流負荷駆動回路 |

| JP4408935B2 (ja) | 2008-02-07 | 2010-02-03 | 日本テキサス・インスツルメンツ株式会社 | ドライバ回路 |

| JP5486259B2 (ja) * | 2009-09-29 | 2014-05-07 | セイコーインスツル株式会社 | 差動増幅器 |

| JP5442558B2 (ja) * | 2010-08-06 | 2014-03-12 | ルネサスエレクトロニクス株式会社 | 出力回路及びデータドライバ及び表示装置 |

| JP4975856B2 (ja) | 2010-09-24 | 2012-07-11 | シャープ株式会社 | 照明装置用集積回路および照明装置 |

| JP2012160287A (ja) | 2011-01-31 | 2012-08-23 | Sharp Corp | 発光ダイオード点灯回路 |

| JP5897938B2 (ja) * | 2012-03-09 | 2016-04-06 | 新日本無線株式会社 | Led駆動装置 |

| JP5739834B2 (ja) | 2012-04-26 | 2015-06-24 | アイエムエル インターナショナルIML International | Led照明装置及び二端子電流コントローラ |

| JP6132091B2 (ja) | 2013-05-10 | 2017-05-24 | 豊田合成株式会社 | Led駆動回路および配線基板 |

-

2016

- 2016-06-28 JP JP2016127559A patent/JP6576306B2/ja active Active

-

2017

- 2017-03-08 US US15/453,747 patent/US10345833B2/en active Active

- 2017-06-28 CN CN201710508382.2A patent/CN107548202B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20170371363A1 (en) | 2017-12-28 |

| US10345833B2 (en) | 2019-07-09 |

| CN107548202B (zh) | 2019-06-25 |

| CN107548202A (zh) | 2018-01-05 |

| JP2018005323A (ja) | 2018-01-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6576306B2 (ja) | 電圧電流変換回路および負荷駆動回路 | |

| JP5168910B2 (ja) | 定電流回路及び定電流回路を使用した発光ダイオード駆動装置 | |

| TWI780282B (zh) | 過電流限制電路、過電流限制方法及電源電路 | |

| CN108933380B (zh) | 激光器装置 | |

| JP2018005323A5 (ja) | ||

| KR20210014079A (ko) | 기준 전압 회로 | |

| JP5506281B2 (ja) | 電源回路及び電子機器 | |

| US20070222422A1 (en) | Power supply device and electrical device equipped with the same | |

| JP5502719B2 (ja) | 負荷装置 | |

| KR101068075B1 (ko) | 발광 다이오드용 정전류 제어 장치 | |

| KR101207254B1 (ko) | 스위칭 레귤레이터 | |

| JP2013250222A (ja) | ハイサイド電流検出回路 | |

| KR101443178B1 (ko) | 전압제어회로 | |

| CN110120627B (zh) | 发光元件驱动电路 | |

| JP4720209B2 (ja) | 基準電圧発生回路及び駆動回路 | |

| JP6257536B2 (ja) | 電流出力装置および電流出力方法 | |

| KR102204117B1 (ko) | Bjt 베이스 전류 보상 회로 및 이를 이용하는 led 구동 장치 | |

| KR100882753B1 (ko) | 정전류 공급 회로 | |

| JP3043248B2 (ja) | 光検出器 | |

| JP5789427B2 (ja) | ドライブ回路 | |

| EP2385438B1 (en) | Current output stage and method for providing an output current | |

| JP4814064B2 (ja) | 駆動電流制御回路、及び電磁比例弁制御システム | |

| EP3729910B1 (en) | Arrangement and method for delivering a current-controlled voltage | |

| JP6495670B2 (ja) | Led駆動回路 | |

| KR101263671B1 (ko) | 피드백 회로 및 이를 적용한 led 백라이트 구동장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180528 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180528 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190320 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190409 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190516 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190723 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190820 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6576306 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |