JP6364956B2 - リニアライザ - Google Patents

リニアライザ Download PDFInfo

- Publication number

- JP6364956B2 JP6364956B2 JP2014107357A JP2014107357A JP6364956B2 JP 6364956 B2 JP6364956 B2 JP 6364956B2 JP 2014107357 A JP2014107357 A JP 2014107357A JP 2014107357 A JP2014107357 A JP 2014107357A JP 6364956 B2 JP6364956 B2 JP 6364956B2

- Authority

- JP

- Japan

- Prior art keywords

- linearizer

- diode

- transmission line

- circuit

- branch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/32—Modifications of amplifiers to reduce non-linear distortion

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/32—Modifications of amplifiers to reduce non-linear distortion

- H03F1/3241—Modifications of amplifiers to reduce non-linear distortion using predistortion circuits

- H03F1/3258—Modifications of amplifiers to reduce non-linear distortion using predistortion circuits based on polynomial terms

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/189—High frequency amplifiers, e.g. radio frequency amplifiers

- H03F3/19—High frequency amplifiers, e.g. radio frequency amplifiers with semiconductor devices only

- H03F3/195—High frequency amplifiers, e.g. radio frequency amplifiers with semiconductor devices only in integrated circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/20—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers

- H03F3/21—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers with semiconductor devices only

- H03F3/211—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers with semiconductor devices only using a combination of several amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/20—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers

- H03F3/24—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers of transmitter output stages

- H03F3/245—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers of transmitter output stages with semiconductor devices only

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/60—Amplifiers in which coupling networks have distributed constants, e.g. with waveguide resonators

- H03F3/602—Combinations of several amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/68—Combinations of amplifiers, e.g. multi-channel amplifiers for stereophonics

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/387—A circuit being added at the output of an amplifier to adapt the output impedance of the amplifier

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2201/00—Indexing scheme relating to details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements covered by H03F1/00

- H03F2201/32—Indexing scheme relating to modifications of amplifiers to reduce non-linear distortion

- H03F2201/3215—To increase the output power or efficiency

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Algebra (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Amplifiers (AREA)

- Microwave Amplifiers (AREA)

Description

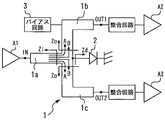

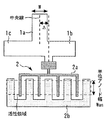

図1は、本発明の実施の形態1に係るリニアライザを示す図である。図2は、図1のリニアライザの一部を拡大した図である。前段の増幅器A1と後段の増幅器A2,A3の段間にリニアライザが挿入されている。リニアライザの分岐回路1は入力伝送線路1aと出力伝送線路1b,1cを有する。入力伝送線路1aは入力端子INと分岐点との間に接続されている。出力伝送線路1bは分岐点と出力端子OUT1との間に接続され、出力伝送線路1cは分岐点と出力端子OUT2との間に接続されている。

図6は、本発明の実施の形態2に係るリニアライザを示す図である。ダイオード2のカソードがビアホール4を介してグランドに接続される。高周波数帯では、ビアホール4のインダクタンスを無視できなくなる。そこで、本実施の形態ではダイオード2のカソードとグランドとの間にインダクタ5を接続する。そして、ビアホール4のインダクタンスをLVHとし、インダクタ5のインダクタンスをLcとして式(4)を満たすように設計する。

図8は、本発明の実施の形態3に係るリニアライザを示す図である。ダイオード2のカソードとグランドとの間に抵抗6が接続されている。この抵抗6の抵抗値を含めて適切な整合回路設計を行うことにより所望の特性が得られる。その他の構成及び効果は実施の形態1と同様である。

図9は、本発明の実施の形態4に係るリニアライザの一部を拡大した図である。ダイオード2のアノードが分岐回路1に接続される接続点は、入力伝送線路1aの中央線の延長線から入力伝送線路1aの幅Wの3倍の範囲内で延長線からずれている。

Claims (6)

- 入力端子と分岐点との間に接続された入力伝送線路と、前記分岐点と第1の出力端子との間に接続された第1の出力伝送線路と、前記分岐点と第2の出力端子との間に接続された第2の出力伝送線路とを有する分岐回路と、

前記分岐点に直接的に接続されたアノードと、カソードとを持つダイオードと、

前記ダイオードをバイアスするバイアス回路とを備えることを特徴とするリニアライザ。 - 前記ダイオードの前記カソードに接続されたインダクタを更に備えることを特徴とする請求項1又は2に記載のリニアライザ。

- 前記ダイオードの前記カソードに接続されたビアホールを更に備えることを特徴とする請求項3に記載のリニアライザ。

- 前記ダイオードの前記カソードに接続された抵抗を更に備えることを特徴とする請求項1又は2に記載のリニアライザ。

- 前記ダイオードの前記アノードが前記分岐回路に接続される接続点は、前記入力伝送線路の中央線の延長線から前記入力伝送線路の幅の3倍の範囲内で前記延長線からずれていることを特徴とする請求項1〜5の何れか1項に記載のリニアライザ。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014107357A JP6364956B2 (ja) | 2014-05-23 | 2014-05-23 | リニアライザ |

| US14/638,212 US9935589B2 (en) | 2014-05-23 | 2015-03-04 | Linearizer |

| KR1020150065099A KR20150135084A (ko) | 2014-05-23 | 2015-05-11 | 리니어라이저 |

| CN201510266552.1A CN105099376B (zh) | 2014-05-23 | 2015-05-22 | 线性化电路 |

| DE102015209435.9A DE102015209435A1 (de) | 2014-05-23 | 2015-05-22 | Linearisierer |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014107357A JP6364956B2 (ja) | 2014-05-23 | 2014-05-23 | リニアライザ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015222921A JP2015222921A (ja) | 2015-12-10 |

| JP2015222921A5 JP2015222921A5 (ja) | 2017-01-26 |

| JP6364956B2 true JP6364956B2 (ja) | 2018-08-01 |

Family

ID=54432021

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014107357A Active JP6364956B2 (ja) | 2014-05-23 | 2014-05-23 | リニアライザ |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9935589B2 (ja) |

| JP (1) | JP6364956B2 (ja) |

| KR (1) | KR20150135084A (ja) |

| CN (1) | CN105099376B (ja) |

| DE (1) | DE102015209435A1 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015222912A (ja) * | 2014-05-23 | 2015-12-10 | 三菱電機株式会社 | リニアライザ |

| US10734330B2 (en) | 2015-01-30 | 2020-08-04 | Taiwan Semiconductor Manufacturing Company Limited | Semiconductor devices having an electro-static discharge protection structure |

| CN111313845B (zh) * | 2019-12-09 | 2022-05-17 | 电子科技大学 | 基于波导电桥的可调谐毫米波行波管用模拟预失真器 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5282072A (en) * | 1991-11-19 | 1994-01-25 | Harmonic Lightwaves, Inc. | Shunt-expansive predistortion linearizers for optical analog transmitters |

| US5424680A (en) * | 1993-11-30 | 1995-06-13 | Harmonic Lightwaves, Inc. | Predistorter for high frequency optical communications devices |

| US5523716A (en) * | 1994-10-13 | 1996-06-04 | Hughes Aircraft Company | Microwave predistortion linearizer |

| JP3439344B2 (ja) * | 1998-06-18 | 2003-08-25 | 日本電気株式会社 | 半導体増幅器 |

| WO2006046294A1 (ja) * | 2004-10-28 | 2006-05-04 | Mitsubishi Denki Kabushiki Kaisha | リニアライザ |

| CA2611756C (en) * | 2005-06-13 | 2014-11-04 | Ccor Solutions | Four quadrant linearizer |

| KR100877504B1 (ko) | 2005-07-07 | 2009-01-07 | 삼성전자주식회사 | 고출력 트랜지스터의 드레인 모듈레이션 감소를 위한 장치 및 방법 |

| DE112009002482T5 (de) * | 2008-10-17 | 2012-01-19 | Triquint Semiconductor, Inc. | Vorrichtung und Verfahren zur Breitbandverstärker-Linearisierung |

| JP5235750B2 (ja) * | 2009-03-27 | 2013-07-10 | 三菱電機株式会社 | 歪補償回路 |

| JP2012244545A (ja) | 2011-05-23 | 2012-12-10 | Mitsubishi Electric Corp | リニアライザ |

| JP2013223116A (ja) * | 2012-04-17 | 2013-10-28 | Mitsubishi Electric Corp | 歪み補償回路及び増幅器 |

| JP2014107357A (ja) | 2012-11-26 | 2014-06-09 | Shin Etsu Handotai Co Ltd | Soiウェーハの製造方法 |

| CN103414435B (zh) | 2013-06-24 | 2016-03-09 | 中国电子科技集团公司第十研究所 | 毫米波功放预失真线性化器 |

| CN103715997B (zh) * | 2013-12-20 | 2017-06-13 | 惠州市正源微电子有限公司 | 一种改善功率放大器线性度的电路 |

-

2014

- 2014-05-23 JP JP2014107357A patent/JP6364956B2/ja active Active

-

2015

- 2015-03-04 US US14/638,212 patent/US9935589B2/en active Active

- 2015-05-11 KR KR1020150065099A patent/KR20150135084A/ko active Search and Examination

- 2015-05-22 CN CN201510266552.1A patent/CN105099376B/zh active Active

- 2015-05-22 DE DE102015209435.9A patent/DE102015209435A1/de active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US9935589B2 (en) | 2018-04-03 |

| CN105099376A (zh) | 2015-11-25 |

| KR20150135084A (ko) | 2015-12-02 |

| DE102015209435A1 (de) | 2015-11-26 |

| CN105099376B (zh) | 2018-01-23 |

| JP2015222921A (ja) | 2015-12-10 |

| US20150341000A1 (en) | 2015-11-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7847630B2 (en) | Amplifier | |

| US9543914B2 (en) | Doherty amplifier structure | |

| US10601380B2 (en) | Band-reconfigurable and load-adaptive power amplifier | |

| JP7071860B2 (ja) | 増幅回路 | |

| CN108933574B (zh) | 功率放大电路 | |

| JP5479284B2 (ja) | 電子回路 | |

| JP5361934B2 (ja) | 電力増幅器 | |

| CN108292652B (zh) | 高功率分布式放大器单片微波集成电路mmic芯片的芯片外分布式漏极偏置 | |

| CN111181496B (zh) | 具有复组合负载匹配电路的多尔蒂放大器 | |

| JP6364956B2 (ja) | リニアライザ | |

| JP2021512565A (ja) | 周波数選択インピーダンス整合ネットワークを備えるrfパワー増幅器 | |

| CN113949346A (zh) | 用于多路径功率放大器的一体地形成的分离器和其制造方法 | |

| US9972588B2 (en) | Semiconductor device | |

| US20220020873A1 (en) | Monolithic semiconductor device and hybrid semiconductor device | |

| JP6305657B1 (ja) | ダイオードリニアライザ | |

| JP4905448B2 (ja) | 半導体回路 | |

| JP6837602B2 (ja) | 分布型増幅器 | |

| JP2015222912A (ja) | リニアライザ | |

| US9887676B2 (en) | High frequency semiconductor amplifier | |

| JP2008236354A (ja) | 増幅器 | |

| JP2013223116A (ja) | 歪み補償回路及び増幅器 | |

| JP5719467B1 (ja) | 低雑音増幅器 | |

| JP2023150803A (ja) | 電力増幅回路 | |

| JPWO2019186881A1 (ja) | モノリシックマイクロ波集積回路の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161208 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161208 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20171025 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171107 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171212 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180605 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180618 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6364956 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |