JP6219224B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6219224B2 JP6219224B2 JP2014087027A JP2014087027A JP6219224B2 JP 6219224 B2 JP6219224 B2 JP 6219224B2 JP 2014087027 A JP2014087027 A JP 2014087027A JP 2014087027 A JP2014087027 A JP 2014087027A JP 6219224 B2 JP6219224 B2 JP 6219224B2

- Authority

- JP

- Japan

- Prior art keywords

- conductivity type

- semiconductor layer

- type region

- semiconductor device

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/40—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00 with at least one component covered by groups H10D10/00 or H10D18/00, e.g. integration of IGFETs with BJTs

- H10D84/401—Combinations of FETs or IGBTs with BJTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D10/00—Bipolar junction transistors [BJT]

- H10D10/01—Manufacture or treatment

- H10D10/051—Manufacture or treatment of vertical BJTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D10/00—Bipolar junction transistors [BJT]

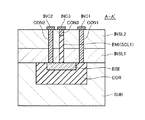

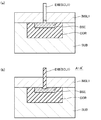

- H10D10/40—Vertical BJTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

- H10D30/6211—Fin field-effect transistors [FinFET] having fin-shaped semiconductor bodies integral with the bulk semiconductor substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/117—Shapes of semiconductor bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/13—Semiconductor regions connected to electrodes carrying current to be rectified, amplified or switched, e.g. source or drain regions

- H10D62/133—Emitter regions of BJTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0107—Integrating at least one component covered by H10D12/00 or H10D30/00 with at least one component covered by H10D8/00, H10D10/00 or H10D18/00, e.g. integrating IGFETs with BJTs

- H10D84/0109—Integrating at least one component covered by H10D12/00 or H10D30/00 with at least one component covered by H10D8/00, H10D10/00 or H10D18/00, e.g. integrating IGFETs with BJTs the at least one component covered by H10D12/00 or H10D30/00 being a MOS device

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

Landscapes

- Bipolar Transistors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014087027A JP6219224B2 (ja) | 2014-04-21 | 2014-04-21 | 半導体装置 |

| US14/679,051 US9461036B2 (en) | 2014-04-21 | 2015-04-06 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014087027A JP6219224B2 (ja) | 2014-04-21 | 2014-04-21 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015207649A JP2015207649A (ja) | 2015-11-19 |

| JP2015207649A5 JP2015207649A5 (enExample) | 2016-11-10 |

| JP6219224B2 true JP6219224B2 (ja) | 2017-10-25 |

Family

ID=54322662

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014087027A Active JP6219224B2 (ja) | 2014-04-21 | 2014-04-21 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9461036B2 (enExample) |

| JP (1) | JP6219224B2 (enExample) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10665702B2 (en) | 2017-12-27 | 2020-05-26 | Samsung Electronics Co., Ltd. | Vertical bipolar transistors |

| FR3087047B1 (fr) | 2018-10-08 | 2021-10-22 | St Microelectronics Sa | Transistor bipolaire |

| FR3087048B1 (fr) | 2018-10-08 | 2021-11-12 | St Microelectronics Sa | Transistor bipolaire |

| FR3113539B1 (fr) | 2020-08-24 | 2022-09-23 | St Microelectronics Crolles 2 Sas | Transistor bipolaire |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2768719B2 (ja) * | 1988-11-21 | 1998-06-25 | 株式会社日立製作所 | 半導体装置及び半導体記憶装置 |

| US4868135A (en) * | 1988-12-21 | 1989-09-19 | International Business Machines Corporation | Method for manufacturing a Bi-CMOS device |

| JPH0344937A (ja) * | 1989-07-13 | 1991-02-26 | Nippon Telegr & Teleph Corp <Ntt> | バイポーラトランジスタ及びその製造方法 |

| JPH0590278A (ja) | 1991-09-30 | 1993-04-09 | Nec Corp | 半導体装置 |

| JP2005236084A (ja) | 2004-02-20 | 2005-09-02 | Toshiba Corp | 縦型バイポーラトランジスタ及びその製造方法 |

| US7288829B2 (en) * | 2004-11-10 | 2007-10-30 | International Business Machines Corporation | Bipolar transistor with self-aligned retrograde extrinsic base implant profile and self-aligned silicide |

| JP2007165780A (ja) | 2005-12-16 | 2007-06-28 | Toshiba Corp | 半導体装置 |

| JP2011119344A (ja) | 2009-12-01 | 2011-06-16 | Panasonic Corp | 半導体装置及びその製造方法 |

| US20110147840A1 (en) | 2009-12-23 | 2011-06-23 | Cea Stephen M | Wrap-around contacts for finfet and tri-gate devices |

-

2014

- 2014-04-21 JP JP2014087027A patent/JP6219224B2/ja active Active

-

2015

- 2015-04-06 US US14/679,051 patent/US9461036B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015207649A (ja) | 2015-11-19 |

| US20150303189A1 (en) | 2015-10-22 |

| US9461036B2 (en) | 2016-10-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8497548B2 (en) | Semiconductor device including a MOS transistor and production method therefor | |

| KR101393917B1 (ko) | Cmos 디바이스 및 그 형성 방법 | |

| CN104835743B (zh) | 半导体器件和制造半导体器件的方法 | |

| CN103378153A (zh) | 用于集成有电容器的FinFET的结构和方法 | |

| TW201419545A (zh) | 元件與其形成方法 | |

| JP2010171055A (ja) | 半導体装置およびその製造方法 | |

| CN101794736A (zh) | 制造半导体器件的方法 | |

| JP6219224B2 (ja) | 半導体装置 | |

| KR20130083923A (ko) | 반도체 장치의 제조 방법과 반도체 장치 | |

| US9000513B2 (en) | Method for manufacturing a semiconductor device and semiconductor device with surrounding gate transistor | |

| CN103563058A (zh) | 半导体器件 | |

| JP5692886B1 (ja) | 半導体装置の製造方法、及び、半導体装置 | |

| US7442619B2 (en) | Method of forming substantially L-shaped silicide contact for a semiconductor device | |

| CN102130125B (zh) | 半导体装置及其制造方法 | |

| US8664050B2 (en) | Structure and method to improve ETSOI MOSFETS with back gate | |

| JP5596245B1 (ja) | 半導体装置の製造方法、及び、半導体装置 | |

| US9502508B2 (en) | Method for manufacturing isolation structure integrated with semiconductor device | |

| JP4565847B2 (ja) | 半導体装置およびその製造方法 | |

| JP2013045953A (ja) | 半導体装置およびその製造方法 | |

| US10290728B2 (en) | Semiconductor device and manufacturing method thereof | |

| TW201301442A (zh) | 導電接觸物之製造方法 | |

| CN103794508A (zh) | 在半导体器件中使用氧化物层板来增加本体氧化物厚度 | |

| JP5286318B2 (ja) | 半導体装置 | |

| TW201419548A (zh) | 半導體裝置的製造方法以及半導體裝置 | |

| JP5749818B2 (ja) | 半導体装置の製造方法、及び、半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160923 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160923 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170518 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170530 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170721 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170905 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170927 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6219224 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |