JP6207460B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6207460B2 JP6207460B2 JP2014102998A JP2014102998A JP6207460B2 JP 6207460 B2 JP6207460 B2 JP 6207460B2 JP 2014102998 A JP2014102998 A JP 2014102998A JP 2014102998 A JP2014102998 A JP 2014102998A JP 6207460 B2 JP6207460 B2 JP 6207460B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- pattern

- diode

- electrode region

- terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 71

- 239000000463 material Substances 0.000 claims description 4

- 230000017525 heat dissipation Effects 0.000 description 11

- 230000000694 effects Effects 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- 238000010586 diagram Methods 0.000 description 8

- 239000000758 substrate Substances 0.000 description 5

- 238000004904 shortening Methods 0.000 description 4

- 229910002601 GaN Inorganic materials 0.000 description 2

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 229910001219 R-phase Inorganic materials 0.000 description 1

- 230000018199 S phase Effects 0.000 description 1

- 230000003796 beauty Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L24/46—Structure, shape, material or disposition of the wire connectors prior to the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/07—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L29/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/07—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L29/00

- H01L25/072—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L29/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/18—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different subgroups of the same main group of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/181—Printed circuits structurally associated with non-printed electric components associated with surface mounted components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05553—Shape in top view being rectangular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/0601—Structure

- H01L2224/0603—Bonding areas having different sizes, e.g. different heights or widths

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/4501—Shape

- H01L2224/45012—Cross-sectional shape

- H01L2224/45015—Cross-sectional shape being circular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4911—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain

- H01L2224/49111—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain the connectors connecting two common bonding areas, e.g. Litz or braid wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49175—Parallel arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19107—Disposition of discrete passive components off-chip wires

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10007—Types of components

- H05K2201/10166—Transistor

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10007—Types of components

- H05K2201/10174—Diode

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10227—Other objects, e.g. metallic pieces

- H05K2201/10363—Jumpers, i.e. non-printed cross-over connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10431—Details of mounted components

- H05K2201/10507—Involving several components

- H05K2201/10522—Adjacent components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10431—Details of mounted components

- H05K2201/10507—Involving several components

- H05K2201/1053—Mounted components directly electrically connected to each other, i.e. not via the PCB

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Inverter Devices (AREA)

- Rectifiers (AREA)

- Dc-Dc Converters (AREA)

Description

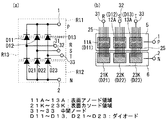

図1はこの発明の半導体装置であるパワーモジュールの原理を示す説明図である。同図(a) に示すように、コンバータ回路は直列接続されたダイオードD1及びD2(第1及び第2の半導体素子)の組合せ(破線で囲んでいる箇所)により構成される。具体的には、ダイオードD1(第1のダイオード)のカソード(第1の他方電極領域)がP端子1に接続され、ダイオードD1のアノード(第1の一方電極領域)とダイオードD2(第2のダイオード)のカソード(第2の他方電極領域)とが電気的に接続され、ダイオードD2のアノード(第2の一方電極領域)がN端子2に接続される。そして、ダイオードD1のアノード,ダイオードD2のカソード間の中間接続点に中間端子3が設けられる。

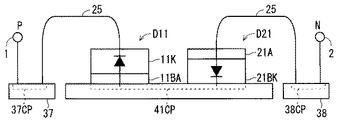

図2はこの発明による実施の形態1であるコンバータ回路を有するパワーモジュールの構成を示す説明図である。なお、以下では、製品の構成によりチップ(半導体素子)からワイヤなどを用いて直接電極部に接続する場合もあるため、回路パターンは最低限必要と考える箇所のみを示している。

図3はこの発明による実施の形態2であるコンバータ回路を有するパワーモジュールの構成を示す説明図である。なお、以下では、製品の構成によりチップからワイヤなどを用いて直接電極部に接続する場合もあるため、回路パターンは最低限必要と考えるパターンのみを示している。

図5はこの発明による実施の形態3である降圧チョッパ回路を有するパワーモジュールの構成を示す説明図である。なお、以下では、製品の構成によりチップからワイヤなどを用いて直接電極部に接続する場合もあるため、回路パターンは最低限必要と考えるパターンのみを示している。

図6はこの発明による実施の形態4である昇圧チョッパ回路を有するパワーモジュールの構成を示す説明図である。なお、以下では、製品の構成によりチップからワイヤなどを用いて直接電極部に接続する場合もあるため、回路パターンは最低限必要と考えるパターンのみを示している。

実施の形態1〜実施の形態4で示した、ダイオード、IGBT等のチップ(半導体素子)は構成材料としてSi(シリコン)に限らず、SiC(炭化珪素),GaN(窒化ガリウム)などのワイドバンドギャップ(半導体)材料からなる半導体素子であっても良い。

Claims (5)

- 第1の回路パターン上に搭載され、第1の一方及び他方電極領域を有する第1の半導体素子と、

第2の回路パターン上に前記第1の半導体素子から独立して搭載され、第2の一方及び他方電極領域を有する第2の半導体素子とを備え、前記第1の半導体素子の前記第1の一方電極領域及び前記第2の半導体素子の前記第2の他方電極領域は中間接続点に電気的に接続され、

前記第1及び第2の半導体素子のうち少なくとも一つの半導体素子はダイオードであり、

前記第1半導体素子がダイオードである場合、前記第1の一方電極領域はアノード領域であり、前記第1の他方電極領域はカソード領域であり、前記第2半導体素子がダイオードである場合、前記第2の一方電極領域はアノード領域であり、前記第2の他方電極領域はカソード領域であり、

前記第1の半導体素子がIGBTである場合、前記第1の一方電極領域はエミッタ領域であり、前記第1の他方電極領域はコレクタ領域であり、前記第2の半導体素子がIGBTである場合、前記第2の一方電極領域はエミッタ領域であり、前記第2の他方電極領域はコレクタ領域であり、

前記第1の一方電極領域の前記第1の他方電極領域に対する第1の上下関係と、前記第2の他方電極領域の前記第2の一方電極領域に対する第2の上下関係とが一致するように、前記第1及び第2の半導体素子を形成し、

前記第1及び第2の回路パターンは同一の共通回路パターンを含み、

前記第1及び第2の上下関係は、前記第1の一方電極領域及び前記第2の他方電極領域が共に下方に配置される上下関係を含み、前記第1の一方電極領域及び前記第2の他方電極領域間は前記共通回路パターンの表面に設けられた電気的接続部を介して電気的に接続されることを特徴とする、

半導体装置。 - 請求項1記載の半導体装置であって、

前記第1及び第2の半導体素子は第1及び第2のダイオードであり、

前記中間接続点から前記第1の他方電極領域にかけて通電する、

半導体装置。 - 請求項2記載の半導体装置であって、

前記第1のダイオードは複数の第1のダイオードを含み、

前記第2のダイオードは前記複数の第1のダイオードに対応して設けられる複数の第2のダイオードを含み、

前記中間接続点は前記複数の第1及び第2のダイオードに対応して設けられる複数の中間接続点を含む、

半導体装置。 - 請求項1記載の半導体装置であって、

前記第1の半導体素子はダイオードであり、前記第2の半導体素子はIGBTであり、

前記中間接続点から前記第1の他方電極領域にかけて通電する、

半導体装置。 - 請求項1から請求項4のうち、いずれか1項に記載の半導体装置であって、

前記第1及び第2の半導体素子はワイドバンドギャップ材料を用いて形成されることを特徴とする、

半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014102998A JP6207460B2 (ja) | 2014-05-19 | 2014-05-19 | 半導体装置 |

| US14/640,425 US20150333043A1 (en) | 2014-05-19 | 2015-03-06 | Semiconductor device |

| DE102015208589.9A DE102015208589A1 (de) | 2014-05-19 | 2015-05-08 | Halbleitervorrichtung |

| CN201510257741.2A CN105097738B (zh) | 2014-05-19 | 2015-05-19 | 半导体装置 |

| US15/950,484 US20180233434A1 (en) | 2014-05-19 | 2018-04-11 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014102998A JP6207460B2 (ja) | 2014-05-19 | 2014-05-19 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015220344A JP2015220344A (ja) | 2015-12-07 |

| JP2015220344A5 JP2015220344A5 (ja) | 2016-06-16 |

| JP6207460B2 true JP6207460B2 (ja) | 2017-10-04 |

Family

ID=54361885

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014102998A Active JP6207460B2 (ja) | 2014-05-19 | 2014-05-19 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US20150333043A1 (ja) |

| JP (1) | JP6207460B2 (ja) |

| CN (1) | CN105097738B (ja) |

| DE (1) | DE102015208589A1 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6723469B2 (ja) * | 2017-09-28 | 2020-07-15 | 三菱電機株式会社 | 2in1型チョッパモジュール |

| JP7170272B2 (ja) * | 2019-03-27 | 2022-11-14 | ネクスファイ・テクノロジー株式会社 | パワー基板とそれを備えた高電圧モジュール |

| JP7156155B2 (ja) * | 2019-04-19 | 2022-10-19 | 三菱電機株式会社 | 半導体モジュール |

| DE102022208031A1 (de) * | 2022-08-03 | 2024-02-08 | Siemens Aktiengesellschaft | Halbleiterbauelement |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2580804B2 (ja) * | 1989-06-23 | 1997-02-12 | 富士電機株式会社 | 電力変換装置用トランジスタモジュール |

| DE19639279C2 (de) * | 1996-09-25 | 2002-01-17 | Daimlerchrysler Rail Systems | Stromrichterschaltung |

| US5874826A (en) * | 1997-10-29 | 1999-02-23 | Lucent Technologies Inc. | Encapsulated modular boost converter and method of manufacture therefor |

| US6335548B1 (en) * | 1999-03-15 | 2002-01-01 | Gentex Corporation | Semiconductor radiation emitter package |

| JP4004715B2 (ja) * | 2000-05-31 | 2007-11-07 | 三菱電機株式会社 | パワーモジュール |

| DE60217478D1 (en) * | 2001-03-28 | 2007-02-22 | Koninkl Philips Electronics Nv | Sychrongleichrichter |

| US6975023B2 (en) * | 2002-09-04 | 2005-12-13 | International Rectifier Corporation | Co-packaged control circuit, transistor and inverted diode |

| JP4239580B2 (ja) * | 2002-12-13 | 2009-03-18 | 株式会社デンソー | 半導体装置 |

| JP2005197554A (ja) * | 2004-01-09 | 2005-07-21 | Mitsubishi Electric Corp | 半導体装置 |

| JP2007027432A (ja) | 2005-07-15 | 2007-02-01 | Sanken Electric Co Ltd | 半導体装置 |

| JP2008244388A (ja) | 2007-03-29 | 2008-10-09 | Nec Electronics Corp | 半導体装置 |

| JP2009043820A (ja) * | 2007-08-07 | 2009-02-26 | Rohm Co Ltd | 高効率モジュール |

| US7781872B2 (en) * | 2007-12-19 | 2010-08-24 | Fairchild Semiconductor Corporation | Package with multiple dies |

| US8237260B2 (en) * | 2008-11-26 | 2012-08-07 | Infineon Technologies Ag | Power semiconductor module with segmented base plate |

| JP5921055B2 (ja) * | 2010-03-08 | 2016-05-24 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| KR101192181B1 (ko) * | 2010-03-31 | 2012-10-17 | (주)포인트엔지니어링 | 광 소자 디바이스 및 그 제조 방법 |

| US9433075B2 (en) * | 2012-08-27 | 2016-08-30 | Mitsubishi Electric Corporation | Electric power semiconductor device |

| US8963303B2 (en) * | 2013-02-22 | 2015-02-24 | Stmicroelectronics S.R.L. | Power electronic device |

| US9536800B2 (en) * | 2013-12-07 | 2017-01-03 | Fairchild Semiconductor Corporation | Packaged semiconductor devices and methods of manufacturing |

-

2014

- 2014-05-19 JP JP2014102998A patent/JP6207460B2/ja active Active

-

2015

- 2015-03-06 US US14/640,425 patent/US20150333043A1/en not_active Abandoned

- 2015-05-08 DE DE102015208589.9A patent/DE102015208589A1/de not_active Withdrawn

- 2015-05-19 CN CN201510257741.2A patent/CN105097738B/zh active Active

-

2018

- 2018-04-11 US US15/950,484 patent/US20180233434A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| US20180233434A1 (en) | 2018-08-16 |

| CN105097738A (zh) | 2015-11-25 |

| CN105097738B (zh) | 2018-01-23 |

| US20150333043A1 (en) | 2015-11-19 |

| JP2015220344A (ja) | 2015-12-07 |

| DE102015208589A1 (de) | 2015-11-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9899328B2 (en) | Power semiconductor module | |

| US9418975B1 (en) | Semiconductor module, power conversion device, and method for manufacturing semiconductor module | |

| US9941255B2 (en) | Power semiconductor module | |

| US9515061B2 (en) | Semiconductor module and semiconductor device | |

| US20220302075A1 (en) | Power semiconductor module | |

| JP3941728B2 (ja) | 電力用半導体装置 | |

| US10727213B2 (en) | Power semiconductor module and power semiconductor device | |

| JP6154104B2 (ja) | 少なくとも一つの電子部品を、第1および第2端子の間のループインダクタンスを低減する手段を含む電力供給装置に電気的に相互接続するための装置 | |

| US20160141284A1 (en) | Semiconductor device | |

| JP6207460B2 (ja) | 半導体装置 | |

| CN108336055B (zh) | 用于均匀分布的电流流动的引线框架上的交指器件 | |

| JP6603676B2 (ja) | ハーフブリッジパワー半導体モジュール及びその製造方法 | |

| CN107851637A (zh) | 功率半导体模块 | |

| KR101946074B1 (ko) | 3 레벨 컨버터 하프 브리지 | |

| EP3443588A1 (en) | Robust low inductance power module package | |

| US20130242631A1 (en) | Power converter apparatus | |

| US11923266B2 (en) | Semiconductor module circuit structure | |

| JP6647189B2 (ja) | 半導体モジュール、半導体装置および電力装置 | |

| JP2015220344A5 (ja) | ||

| US9445497B2 (en) | Semiconductor device | |

| CN107039408B (zh) | 半导体装置及半导体装置的制造方法 | |

| JP2005236108A (ja) | 半導体装置 | |

| US11323041B2 (en) | Semiconductor device | |

| JP2015201947A (ja) | パワー半導体デバイス | |

| US10855196B2 (en) | Semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160425 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160425 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170329 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170523 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170705 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170808 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170905 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6207460 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |